- Article

Efficient mmWave PA in 90 nm CMOS: Stacked-Inverter Topology, L/T Matching, and EM-Validated Results

- Nusrat Jahan,

- Ramisha Anan and

- Jannatul Maua Nazia

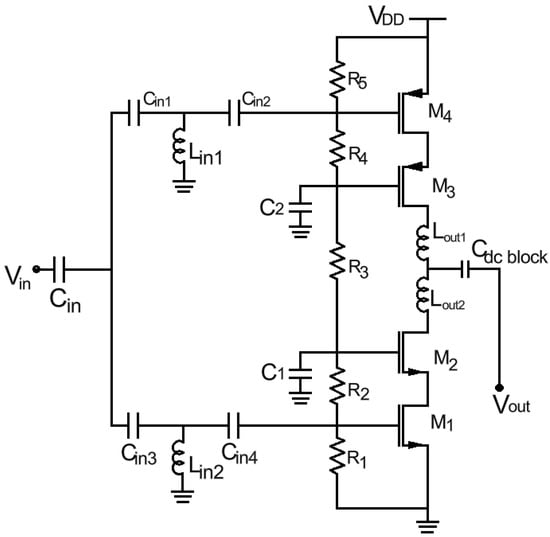

In this study, we present the design and analysis of a stacked inverter-based millimeter-wave (mmWave) power amplifier (PA) in 90 nm CMOS-targeting wideband Q-band operation. The PA employs two PMOS and two NMOS devices in a fully stacked inverter topology to distribute device stress, remove the need for an RF choke, and increase effective transconductance while preserving compact layout. A resistor ladder biases the stack near per device, and capacitive division steers intermediate-node swings to enable class-E-like voltage shaping at the output. Closed-form models are developed for gain, output power, drain efficiency/PAE, and linearity, alongside a small-signal stacked-ladder formulation that quantifies stress sharing and the impedance presented to the matching networks; L/T network synthesis relations are provided to co-optimize bandwidth and insertion loss. Post-layout simulation in 90 nm CMOS shows = 10 dB at 39.84 GHz with 3 dB bandwidth from 36.8 to 42.4 GHz, peak PAE of 18.38% near 41 GHz, and saturated output power dBm at V, with dB and reverse isolation dB. The layout occupies mm2 and draws 31.08 mW. Robustness is validated via a 200-run Monte Carlo showing tight clustering of and PAE, sensitivity sweeps identifying sizing/tolerance trade-offs ( devices/passives), and EM co-simulation of on-chip passives indicating only minor loss/shift relative to schematic while preserving the target bandwidth and efficiency. The results demonstrate a balanced gain–efficiency–power trade-off with layout-aware resilience, positioning stacked-inverter CMOS PAs as a power- and area-efficient solution for mmWave front-ends.

15 December 2025

![Logic locking-based modeling of a saf [22]: transform a sa0 to AND key gate (

k

=

1

), (a) successful propagation of key k with logic 1, (b) failed propagation of k with 0; a sa1 to OR key gate (

k

=

0

), (c) successful propagation of k with logic 0, and (d) failed propagation of k with 1.](https://mdpi-res.com/chips/chips-04-00051/article_deploy/html/images/chips-04-00051-g001-550.jpg)