Optimised Extension of an Ultra-Low-Power RISC-V Processor to Support Lightweight Neural Network Models

Abstract

1. Introduction

- A RISC-V processor optimised for BNN inference that embeds custom instructions to accelerate key layers while minimising hardware cost.

- Extensive validation through two case studies, one on MNIST dataset classification and another on an automotive in-vehicle network intrusion detection system, demonstrating efficiency across diverse workloads.

- A comprehensive comparison and analysis of the implementations, which reveal a power-efficient, resource-aware design suited for edge AI applications. The design significantly reduces on-chip resource usage and power consumption compared with existing FPGA-based solutions, all while maintaining real-time performance.

2. Background and Related Works

2.1. Binary Neural Networks

2.2. RISC-V Architecture

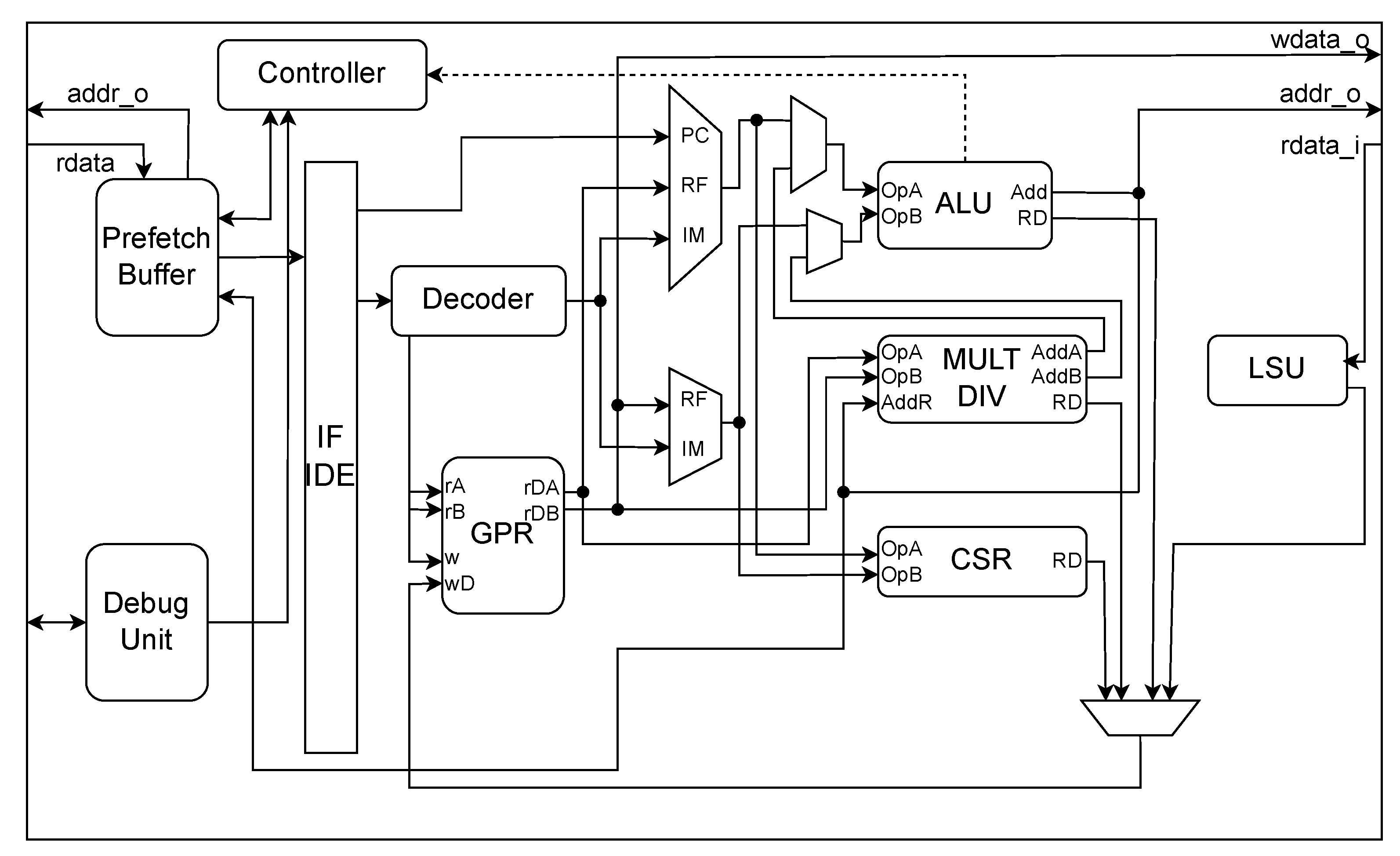

2.3. Zero-Riscy: A Lightweight and Ultra-Low Power RISC-V Processor

3. Proposed Ultra-Low-Power RISC-V Processor with BNN Support

3.1. Zero-Riscy with the Proposed BNN Unit

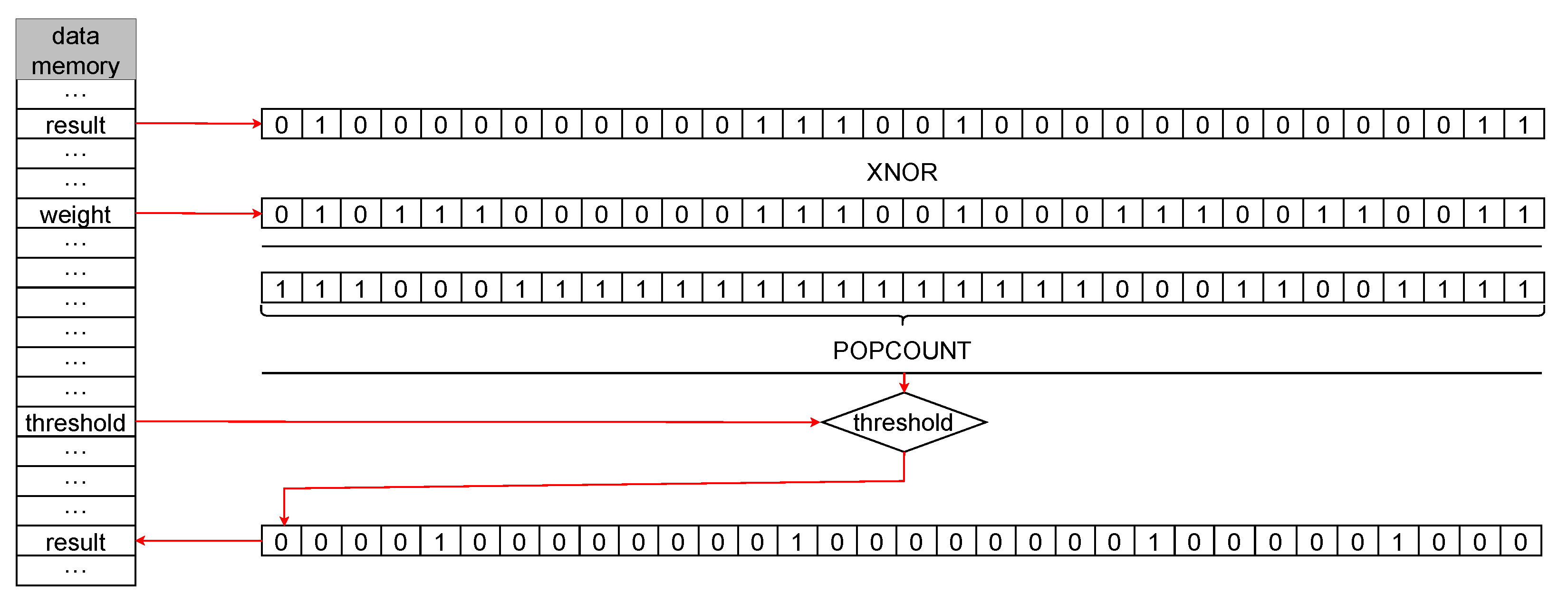

3.2. Proposed Custom Instructions

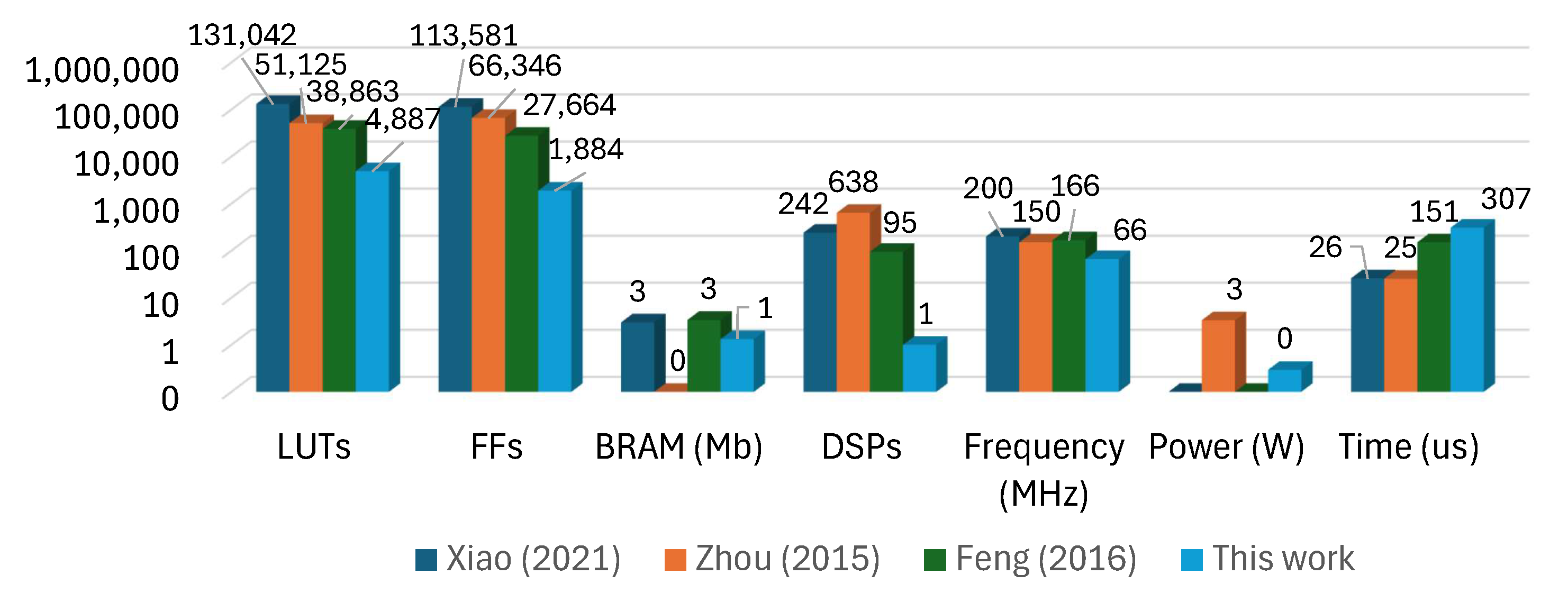

4. Experimental Results

4.1. BNN Inference on the MNIST Dataset Using the Proposed RISC-V Processor

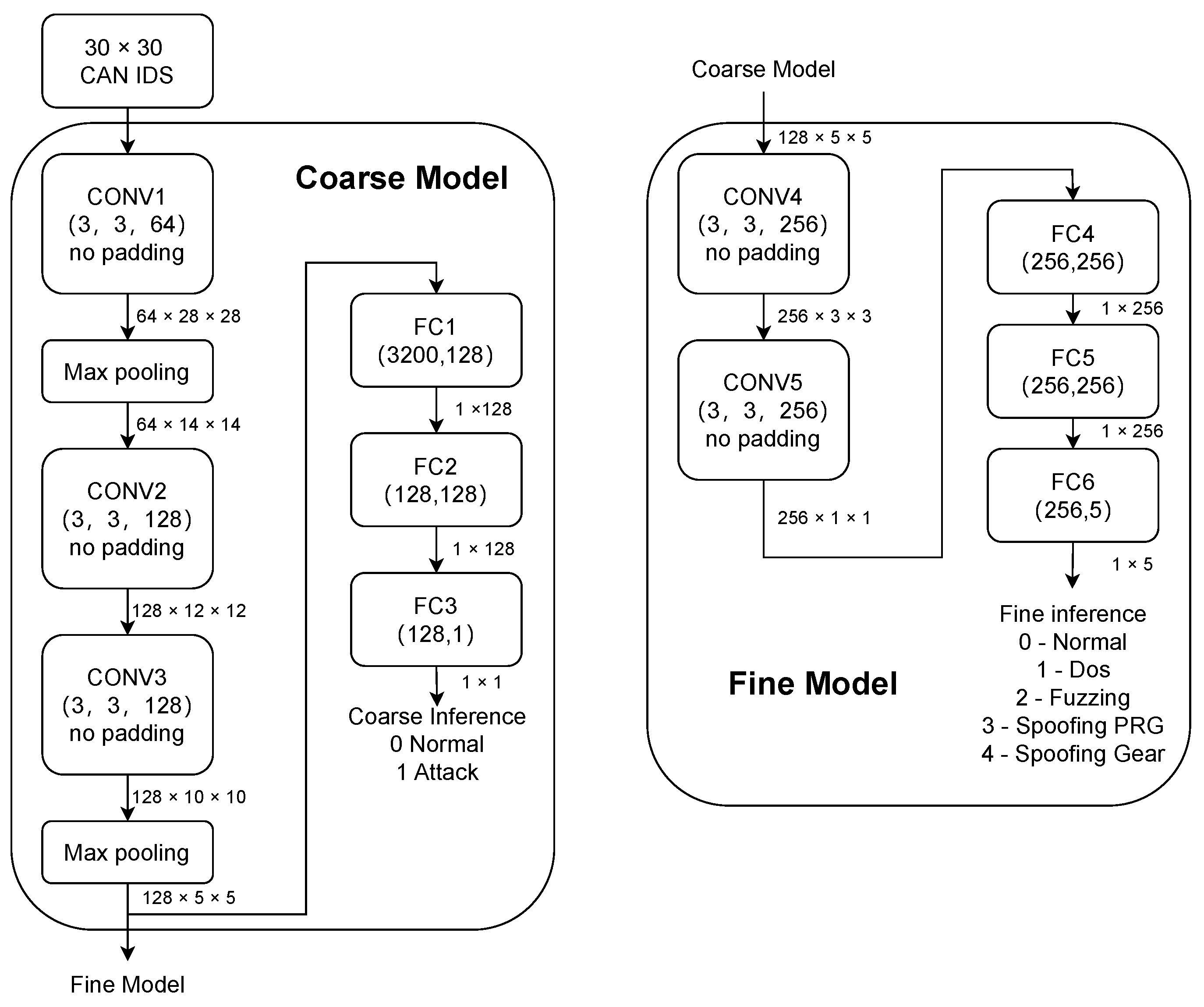

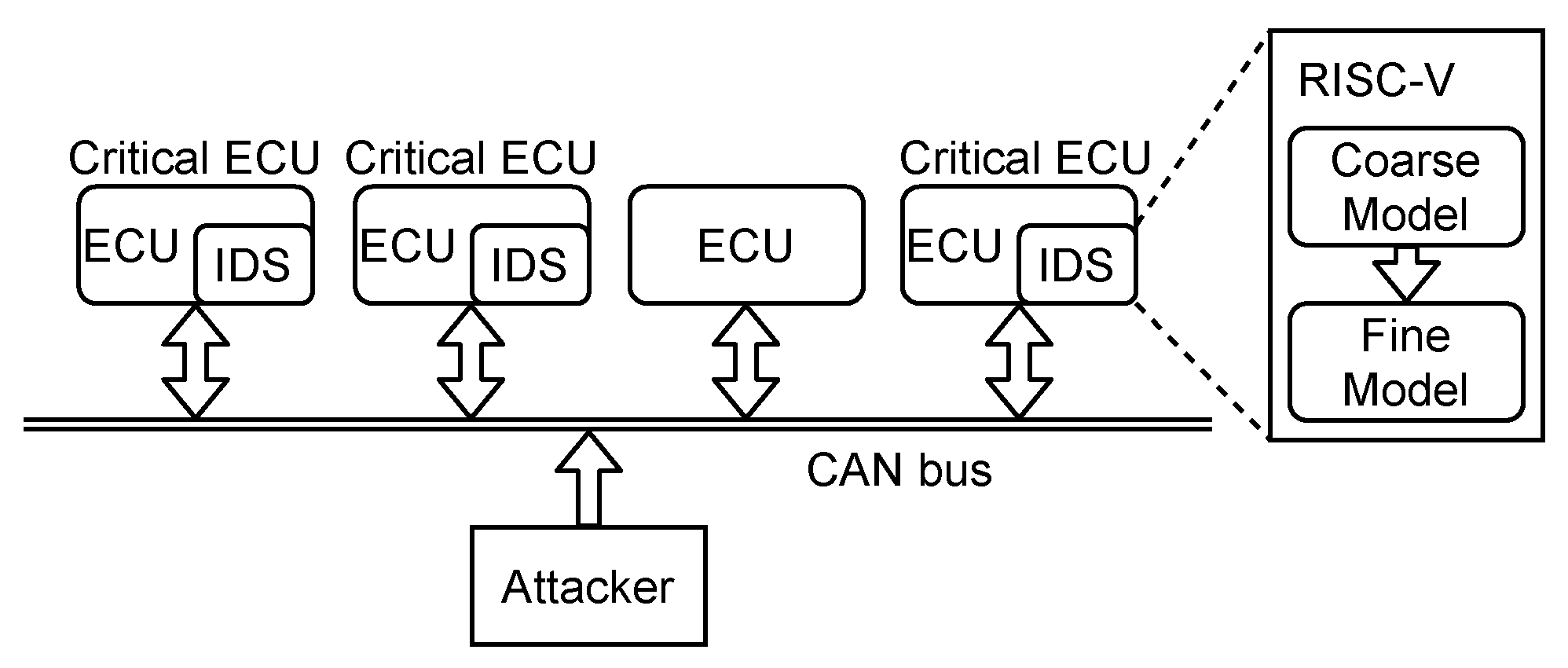

4.2. Implementing a Low-Cost IDS for In-Vehicle Networks Using BNN

4.2.1. CAN Bus Message

4.2.2. Model Structure and Performance

4.2.3. Resource Utilisation and Power Consumption

5. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Han, S.; Liu, X.; Mao, H.; Pu, J.; Pedram, A.; Horowitz, M.A.; Dally, W.J. EIE: Efficient inference engine on compressed deep neural network. Acm Sigarch Comput. Archit. News 2016, 44, 243–254. [Google Scholar] [CrossRef]

- Sze, V.; Chen, Y.H.; Yang, T.J.; Emer, J.S. Efficient processing of deep neural networks: A tutorial and survey. Proc. IEEE 2017, 105, 2295–2329. [Google Scholar]

- Horowitz, M. 1.1 computing’s energy problem (and what we can do about it). In Proceedings of the 2014 IEEE International Solid-State Circuits Conference Digest of Technical Papers (ISSCC), San Francisco, CA, USA, 9–13 February 2014; pp. 10–14. [Google Scholar]

- Umuroglu, Y.; Fraser, N.J.; Gambardella, G.; Blott, M.; Leong, P.; Jahre, M.; Vissers, K. Finn: A framework for fast, scalable binarized neural network inference. In Proceedings of the 2017 ACM/SIGDA International Symposium on Field-Programmable Gate Arrays, Monterey, CA, USA, 22–24 February 2017; pp. 65–74. [Google Scholar]

- Garofalo, A.; Tagliavini, G.; Conti, F.; Benini, L.; Rossi, D. Xpulpnn: Enabling energy efficient and flexible inference of quantized neural networks on risc-v based iot end nodes. IEEE Trans. Emerg. Top. Comput. 2021, 9, 1489–1505. [Google Scholar]

- Courbariaux, M.; Hubara, I.; Soudry, D.; El-Yaniv, R.; Bengio, Y. Binarized neural networks: Training deep neural networks with weights and activations constrained to +1 or −1. arXiv 2016, arXiv:1602.02830. [Google Scholar]

- Liu, Q.; Amiri, S.; Ost, L. Exploring RISC-V Based DNN Accelerators. In Proceedings of the 2024 IEEE International Conference on Omni-Layer Intelligent Systems (COINS), London, UK, 29–31 July 2024; pp. 1–6. [Google Scholar]

- Wang, C.; Fang, C.; Wu, X.; Wang, Z.; Lin, J. A Scalable RISC-V Vector Processor Enabling Efficient Multi-Precision DNN Inference. arXiv 2024, arXiv:2401.16872. [Google Scholar]

- Reggiani, E.; Pappalardo, A.; Doblas, M.; Moreto, M.; Olivieri, M.; Unsal, O.S.; Cristal, A. Mix-gemm: An efficient hw-sw architecture for mixed-precision quantized deep neural networks inference on edge devices. In Proceedings of the 2023 IEEE International Symposium on High-Performance Computer Architecture (HPCA), Montreal, QC, Canada, 25 February–1 March 2023; pp. 1085–1098. [Google Scholar]

- Andri, R.; Cavigelli, L.; Rossi, D.; Benini, L. YodaNN: An ultra-low power convolutional neural network accelerator based on binary weights. In Proceedings of the 2016 IEEE Computer Society Annual Symposium on VLSI (ISVLSI), Pittsburgh, PA, USA, 11–13 July 2016; pp. 236–241. [Google Scholar]

- Rossi, D.; Conti, F.; Marongiu, A.; Pullini, A.; Loi, I.; Gautschi, M.; Tagliavini, G.; Capotondi, A.; Flatresse, P.; Benini, L. PULP: A parallel ultra low power platform for next generation IoT applications. In Proceedings of the 2015 IEEE Hot Chips 27 Symposium (HCS), IEEE Computer Society, Cupertino, CA, USA, 22–25 August 2015; pp. 1–39. [Google Scholar]

- Khandelwal, S.; Shreejith, S. A Lightweight FPGA-based IDS-ECU Architecture for Automotive CAN. In Proceedings of the 2022 International Conference on Field-Programmable Technology (ICFPT), Hong Kong, 5–9 December 2022; pp. 1–9. [Google Scholar]

- Kwon, H.; Samajdar, A.; Krishna, T. Maeri: Enabling flexible dataflow mapping over dnn accelerators via reconfigurable interconnects. Acm Sigarch Notices 2018, 53, 461–475. [Google Scholar]

- Garofalo, A.; Ottavi, G.; Conti, F.; Karunaratne, G.; Boybat, I.; Benini, L.; Rossi, D. A heterogeneous in-memory computing cluster for flexible end-to-end inference of real-world deep neural networks. IEEE J. Emerg. Sel. Top. Circuits Syst. 2022, 12, 422–435. [Google Scholar]

- Zhang, H.; Liu, J.; Bai, J.; Li, S.; Luo, L.; Wei, S.; Wu, J.; Kang, W. HD-CIM: Hybrid-device computing-in-memory structure based on MRAM and SRAM to reduce weight loading energy of neural networks. IEEE Trans. Circuits Syst. Regul. Pap. 2022, 69, 4465–4474. [Google Scholar]

- Rastegari, M.; Ordonez, V.; Redmon, J.; Farhadi, A. Xnor-net: Imagenet classification using binary convolutional neural networks. In Proceedings of the European Conference on Computer Vision, Amsterdam, The Netherlands, 11–14 October 2016; pp. 525–542. [Google Scholar]

- Bulat, A.; Martinez, B.; Tzimiropoulos, G. High-capacity expert binary networks. arXiv 2020, arXiv:2010.03558. [Google Scholar]

- Qin, H.; Gong, R.; Liu, X.; Shen, M.; Wei, Z.; Yu, F.; Song, J. Forward and backward information retention for accurate binary neural networks. In Proceedings of the IEEE/CVF Conference on Computer Vision and Pattern Recognition, Seattle, WA, USA, 14–19 June 2020; pp. 2250–2259. [Google Scholar]

- Martinez, B.; Yang, J.; Bulat, A.; Tzimiropoulos, G. Training binary neural networks with real-to-binary convolutions. arXiv 2020, arXiv:2003.11535. [Google Scholar]

- Waterman, A.; Lee, Y.; Patterson, D.A.; Asanovic, K. The Risc-v Instruction Set Manual, Volume I: Base User-Level Isa; Technical Report No. UCB/EECS-2016-118; EECS Department, University of California at Berkeley: Berkeley, CA, USA, 2011; Volume 116, pp. 1–32. [Google Scholar]

- Davide Schiavone, P.; Conti, F.; Rossi, D.; Gautschi, M.; Pullini, A.; Flamand, E.; Benini, L. Slow and steady wins the race? A comparison of ultra-low-power RISC-V cores for Internet-of-Things applications. In Proceedings of the 2017 27th International Symposium on Power and Timing Modeling, Optimization and Simulation (PATMOS), Thessaloniki, Greece, 25–27 September 2017; pp. 1–8. [Google Scholar]

- Pullini, A.; Rossi, D.; Loi, I.; Tagliavini, G.; Benini, L. Mr. Wolf: An energy-precision scalable parallel ultra low power SoC for IoT edge processing. IEEE J.-Solid-State Circuits 2019, 54, 1970–1981. [Google Scholar]

- Elsadek, I.; Tawfik, E.Y. RISC-V resource-constrained cores: A survey and energy comparison. In Proceedings of the 2021 19th IEEE International New Circuits and Systems Conference (NEWCAS), Toulon, France, 13–16 June 2021; pp. 1–5. [Google Scholar]

- Song, H.M.; Woo, J.; Kim, H.K. In-vehicle network intrusion detection using deep convolutional neural network. Veh. Commun. 2020, 21, 100198. [Google Scholar]

- Rangsikunpum, A.; Amiri, S.; Ost, L. A Reconfigurable Coarse-to-Fine Approach for the Execution of CNN Inference Models in Low-Power Edge Devices. Iet Comput. Digit. Tech. 2024, 2024, 6214436. [Google Scholar]

- LeCun, Y.; Bottou, L.; Bengio, Y.; Haffner, P. Gradient-based learning applied to document recognition. Proc. IEEE 1998, 86, 2278–2324. [Google Scholar]

- Xu, L.; Krzyzak, A.; Suen, C.Y. Methods of combining multiple classifiers and their applications to handwriting recognition. IEEE Trans. Syst. Man. Cybern. 2002, 22, 418–435. [Google Scholar]

- Cohen, G.; Afshar, S.; Tapson, J.; Van Schaik, A. EMNIST: Extending MNIST to handwritten letters. In Proceedings of the 2017 International Joint Conference on Neural Networks (IJCNN), Anchorage, AL, USA, 14–19 May 2017; pp. 2921–2926. [Google Scholar]

- Xiao, H.; Li, K.; Zhu, M. FPGA-based scalable and highly concurrent convolutional neural network acceleration. In Proceedings of the 2021 IEEE International Conference on Power Electronics, Computer Applications (ICPECA), Shenyang, China, 22–24 January 2021; pp. 367–370. [Google Scholar]

- Feng, G.; Hu, Z.; Chen, S.; Wu, F. Energy-efficient and high-throughput FPGA-based accelerator for Convolutional Neural Networks. In Proceedings of the 2016 13th IEEE International Conference on Solid-State and Integrated Circuit Technology (ICSICT), Hangzhou, China, 25–28 October 2016; pp. 624–626. [Google Scholar]

- Zhou, Y.; Jiang, J. An FPGA-based accelerator implementation for deep convolutional neural networks. In Proceedings of the 2015 4th International Conference on Computer Science and Network Technology (ICCSNT), Harbin, China, 19–20 December 2015; Volume 1, pp. 829–832. [Google Scholar]

- Liu, Q.; Amiri, S.; Ost, L. Low-Cost Intrusion Detection System for CAN Bus Networks Using RISC-V with Binarised Neural Networks. In Proceedings of the 2025 IEEE International Conference on Industrial Technology (ICIT), Yantai, China, 3–6 August 2025. [Google Scholar]

- Al-Jarrah, O.Y.; Maple, C.; Dianati, M.; Oxtoby, D.; Mouzakitis, A. Intrusion detection systems for intra-vehicle networks: A review. IEEE Access 2019, 7, 21266–21289. [Google Scholar]

- Pan, L.; Zheng, X.; Chen, H.; Luan, T.; Bootwala, H.; Batten, L. Cyber security attacks to modern vehicular systems. J. Inf. Secur. Appl. 2017, 36, 90–100. [Google Scholar]

- Miller, C.; Valasek, C. Remote exploitation of an unaltered passenger vehicle. In Proceedings of the Black Hat USA, Las Vegas, NV, USA, 1–6 August 2015; Volume 2015, pp. 1–91. [Google Scholar]

- Palaniswamy, B.; Camtepe, S.; Foo, E.; Pieprzyk, J. An efficient authentication scheme for intra-vehicular controller area network. IEEE Trans. Inf. Forensics Secur. 2020, 15, 3107–3122. [Google Scholar]

- Yorozu, T.; Hirano, M.; Oka, K.; Tagawa, Y. Electron spectroscopy studies on magneto-optical media and plastic substrate interface. IEEE Transl. J. Magn. Jpn. 1987, 2, 740–741. [Google Scholar]

- Rangsikunpum, A.; Amiri, S.; Ost, L. An FPGA-Based Intrusion Detection System Using Binarised Neural Network for CAN Bus Systems. In Proceedings of the 2024 IEEE International Conference on Industrial Technology (ICIT), Bristol, UK, 25–27 March 2024; pp. 1–6. [Google Scholar]

- Rangsikunpum, A.; Amiri, S.; Ost, L. BIDS: An efficient Intrusion Detection System for in-vehicle networks using a two-stage Binarised Neural Network on low-cost FPGA. J. Syst. Archit. 2024, 156, 103285. [Google Scholar]

- Zhao, Q.; Chen, M.; Gu, Z.; Luan, S.; Zeng, H.; Chakrabory, S. CAN bus intrusion detection based on auxiliary classifier GAN and out-of-distribution detection. Acm Trans. Embed. Comput. Syst. 2022, 21, 1–30. [Google Scholar]

- Hoang, T.N.; Kim, D. Detecting in-vehicle intrusion via semi-supervised learning-based convolutional adversarial autoencoders. Veh. Commun. 2022, 38, 100520. [Google Scholar]

- Tariq, S.; Lee, S.; Woo, S.S. CANTransfer: Transfer learning based intrusion detection on a controller area network using convolutional LSTM network. In Proceedings of the 35th Annual ACM Symposium on Applied Computing, Brno, Czech Republic, 30 March–3 April 2020; pp. 1048–1055. [Google Scholar]

- Yang, L.; Moubayed, A.; Shami, A. MTH-IDS: A multitiered hybrid intrusion detection system for internet of vehicles. IEEE Internet Things J. 2021, 9, 616–632. [Google Scholar]

| 31:25 | 24:20 | 19:15 | 14:12 | 11:7 | 6:0 | |

| CONV | funct7 (0000000) | rs2 | rs1 | funct3 (011) | rd | op (1111011) |

| Max Pooling | funct7 (0000000) | rs2 | rs1 | funct3 (100) | rd | op (1111011) |

| FC | funct7 (0000000) | rs2 | rs1 | funct3 (101) | rd | op (1111011) |

| Normal Instruction Cycles | Proposed Instruction Cycles |

|---|---|

| 135,551 | 20,276 (↓ 85.1%) |

| Model | Accuracy (%) | Precision (%) | Recall (%) | F1 (%) |

|---|---|---|---|---|

| ACGAN [40] | - | 99.23 | 99.24 | 99.23 |

| DCNN [24] | 99.94 | 99.98 | 99.87 | 99.92 |

| CAAE [41] | 99.90 | 99.97 | 99.72 | 99.84 |

| CANTransfer [42] | 99.37 | 94.84 | 95.57 | 95.25 |

| MTH-IDS [43] | 99.99 | 99.99 | 99.99 | 99.99 |

| QMLP [12] | 99.96 | 99.91 | 99.92 | 99.91 |

| Coarse [39] | 99.83 | 99.88 | 99.64 | 99.76 |

| Dataset | Attack | Mean (ms) | Standard Deviation (ms) |

|---|---|---|---|

| CH [25] | Normal | 0.512 | 0.712 |

| DoS | 0.767 | 1.446 | |

| Fuzzy | 0.768 | 1.465 | |

| Spoofing RPM | 0.547 | 0.896 | |

| Spoofing gear | 0.527 | 0.889 |

| Normal Instruction Cycles | Proposed Instruction Cycles |

|---|---|

| 864.6 k | 88.3 k (↓ 89.8%) |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Liu, Q.; Amiri, S. Optimised Extension of an Ultra-Low-Power RISC-V Processor to Support Lightweight Neural Network Models. Chips 2025, 4, 13. https://doi.org/10.3390/chips4020013

Liu Q, Amiri S. Optimised Extension of an Ultra-Low-Power RISC-V Processor to Support Lightweight Neural Network Models. Chips. 2025; 4(2):13. https://doi.org/10.3390/chips4020013

Chicago/Turabian StyleLiu, Qiankun, and Sam Amiri. 2025. "Optimised Extension of an Ultra-Low-Power RISC-V Processor to Support Lightweight Neural Network Models" Chips 4, no. 2: 13. https://doi.org/10.3390/chips4020013

APA StyleLiu, Q., & Amiri, S. (2025). Optimised Extension of an Ultra-Low-Power RISC-V Processor to Support Lightweight Neural Network Models. Chips, 4(2), 13. https://doi.org/10.3390/chips4020013