Abstract

This paper presents NeuroAdaptiveNet, an FPGA-based neural network framework that dynamically self-adjusts its architectural configurations in real time to maximize performance across diverse datasets. The core innovation is a Dynamic Classifier Selection mechanism, which harnesses the k-Nearest Centroid algorithm to identify the most competent neural network model for each incoming data sample. By adaptively selecting the most suitable model configuration, NeuroAdaptiveNet achieves significantly improved classification accuracy and optimized resource usage compared to conventional, statically configured neural networks. Experimental results on four datasets demonstrate that NeuroAdaptiveNet can reduce FPGA resource utilization by as much as 52.85%, increase classification accuracy by 4.31%, and lower power consumption by up to 24.5%. These gains illustrate the clear advantage of real-time, per-input reconfiguration over static designs. These advantages are particularly crucial for edge computing and embedded applications, where computational constraints and energy efficiency are paramount. The ability of NeuroAdaptiveNet to tailor its neural network parameters and architecture on a per-input basis paves the way for more efficient and accurate AI solutions in resource-constrained environments.

1. Introduction

Neural networks [1] have emerged as a central pillar of machine learning [2], capable of detecting nuanced patterns in complex, large-scale datasets by emulating certain structural and functional characteristics of the human brain. Constructed from interconnected computational elements analogous to biological neurons, these networks excel in processing and relaying information across multiple layers. Crucially, the depth, configuration, and number of these layers significantly influence a network’s capacity to generalize and perform effectively in myriad real-world tasks.

This remarkable flexibility and performance have positioned neural networks as indispensable tools in diverse fields, including autonomous vehicles [3], healthcare [4], robotics [5], and telecommunications [6]. Despite their extensive applicability, deploying neural networks on resource-constrained platforms remains a formidable challenge, largely due to their high computational and memory requirements. These limitations can hinder their efficiency and broad adoption, particularly when rapid inference or low power consumption is demanded.

In addressing these computational constraints, researchers have increasingly focused on reconfigurable architectures [7], which offer a compelling balance between adaptability and performance. By enabling post-manufacturing modifications, reconfigurable systems provide hardware-level flexibility akin to that of software environments, allowing design parameters such as throughput, latency, and resource utilization to be fine-tuned to specific application demands. This adaptability is particularly well-suited for optimizing the performance of neural networks while minimizing hardware overhead.

Recent efforts to implement neural networks on Field-Programmable Gate Arrays (FPGAs) highlight the promise of reconfigurable solutions. For instance, [8] introduces a pragmatic method for shrinking hardware-based neural networks by employing adaptable layers in Artificial Neural Networks, wherein each layer can execute two distinct functions. This approach achieves a remarkable 41% reduction in the FPGA footprint compared with alternative designs and demonstrates a straightforward, Verilog-based implementation on the Altera Arria 10 GX FPGA. Concurrently, ref. [9] proposes an adaptive parallelism strategy for Binary Neural Networks (BNNs) on a Xilinx XCZU7EV FPGA, thereby streamlining resource usage while preserving high throughput across varying BNN layers. This dynamic allocation of computational parallelism enables a substantial improvement in area–speed efficiency relative to previous FPGAs and VLSI accelerators, which is especially pertinent for real-time inference on edge devices.

Along similar lines, ref. [10] demonstrated a fully reconfigurable multilayer perceptron on a Cyclone IV FPGA that supports run-time adjustment of key network parameters, including number of inputs, neurons per layer, total layers, bias inclusion, and choice of activation function, entirely without re-synthesis. Their architecture reuses a fixed bank of 20 hardware neurons as virtual layers under the control of a finite-state machine, and replaces vendor-specific DSP blocks with custom VEDIC multipliers to ensure portability to ASIC implementations. Although the design operates at a lower peak clock rate (approximately 77 MHz), it achieves competitive performance, achieving 99.3% accuracy on the Iris classification task in 1.16 µs and sub-microsecond latency on function approximation, while consuming only 37% of logic elements and 1% of memory bits on the FPGA.

Prior FPGA-based accelerators have typically optimized only one or two metrics. For example, ref. [8] achieved a 41% reduction in footprint, ref. [9] reported a 24% improvement in area–speed efficiency, and [10] enabled per-task reconfiguration. In contrast, NeuroAdaptiveNet employs per-input reconfiguration to achieve simultaneous improvements in power consumption, hardware resource utilization, and classification accuracy.

At runtime, NeuroAdaptiveNet evaluates each input and switches to the most suitable compact neural model, resulting in up to 24.5% lower power consumption, up to 52.85% lower resource utilization, and up to 4.31% higher classification accuracy compared with the best static design. Unlike prior designs that use a fixed single network or adapt only at the task level, NeuroAdaptiveNet’s input-level flexibility incurs only microseconds of overhead while delivering maximum accuracy with minimal hardware and energy requirements. Its efficient performance and high accuracy make it an ideal solution for Edge AI systems constrained by limited power and resources. The primary goal of this study is to introduce a novel FPGA-based neural network implementation that departs from the conventional static design.

The remainder of this paper is structured as follows. Section 2 details the dynamic classifier selection framework, Section 3 explains the FPGA design, Section 4 reports accuracy, resource-use, power, and latency results, Section 5 analyzes trade-offs and future work, and Section 6 concludes the paper.

2. Dynamic Classifier Selection Mechanism

2.1. Background

Dynamic classifier selection (DCS) [11,12,13] is a specialized machine learning technique that, for each incoming data instance, selects the single most appropriate classifier from a larger ensemble of candidates. Unlike traditional methods relying on a fixed, one-size-fits-all model, DCS adaptively evaluates multiple classifiers in real time, choosing the one best suited to handle the current data point. Typically, the selection process gauges each classifier’s competence based on past performance metrics, similarity to the query instance, or a combination of such factors. By leveraging the diverse strengths of different classifiers, DCS enhances the overall accuracy and adaptability of the system—particularly in scenarios with highly variable data distributions or stringent accuracy requirements.

In our work, we employ a clustering-based framework for DCS, diverging from the widely used k-nearest neighbors (k-NN) method. Specifically, we implement the k-Nearest Centroid (k-NC) technique, building upon our earlier research with heterogeneous classifier ensembles [14] and a k-NN accelerator [15]. Here, however, we apply k-NC to a homogeneous set of neural network classifiers, each configured with different hyperparameters, while retaining the underlying insights from our hardware-centric ensemble research. A key advancement in this approach is its flexibility regarding the number of clusters, rather than directly coupling the number of centroids to the number of classes. This design choice facilitates more precise grouping of similar data points, thus improving competence estimation across varying data regions.

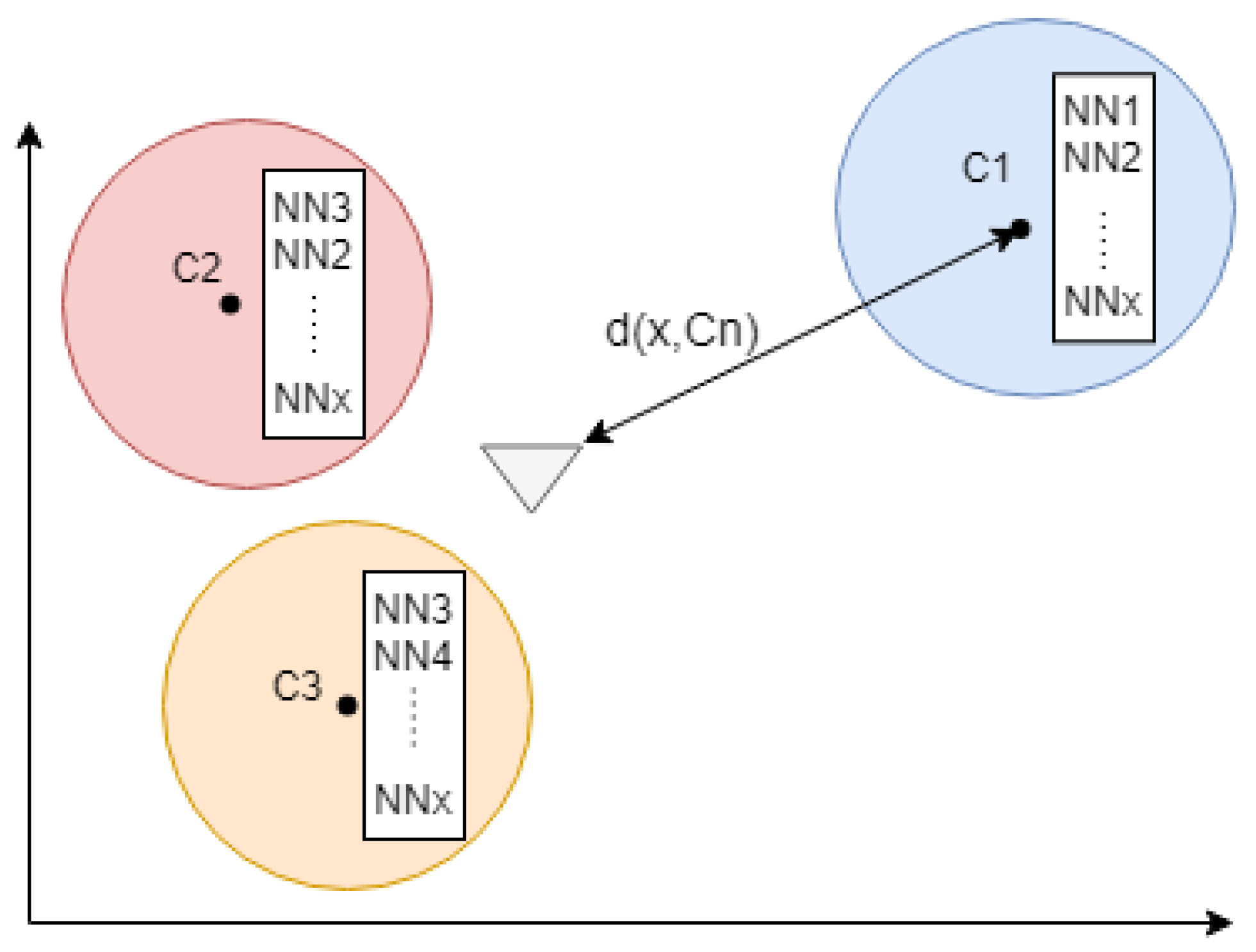

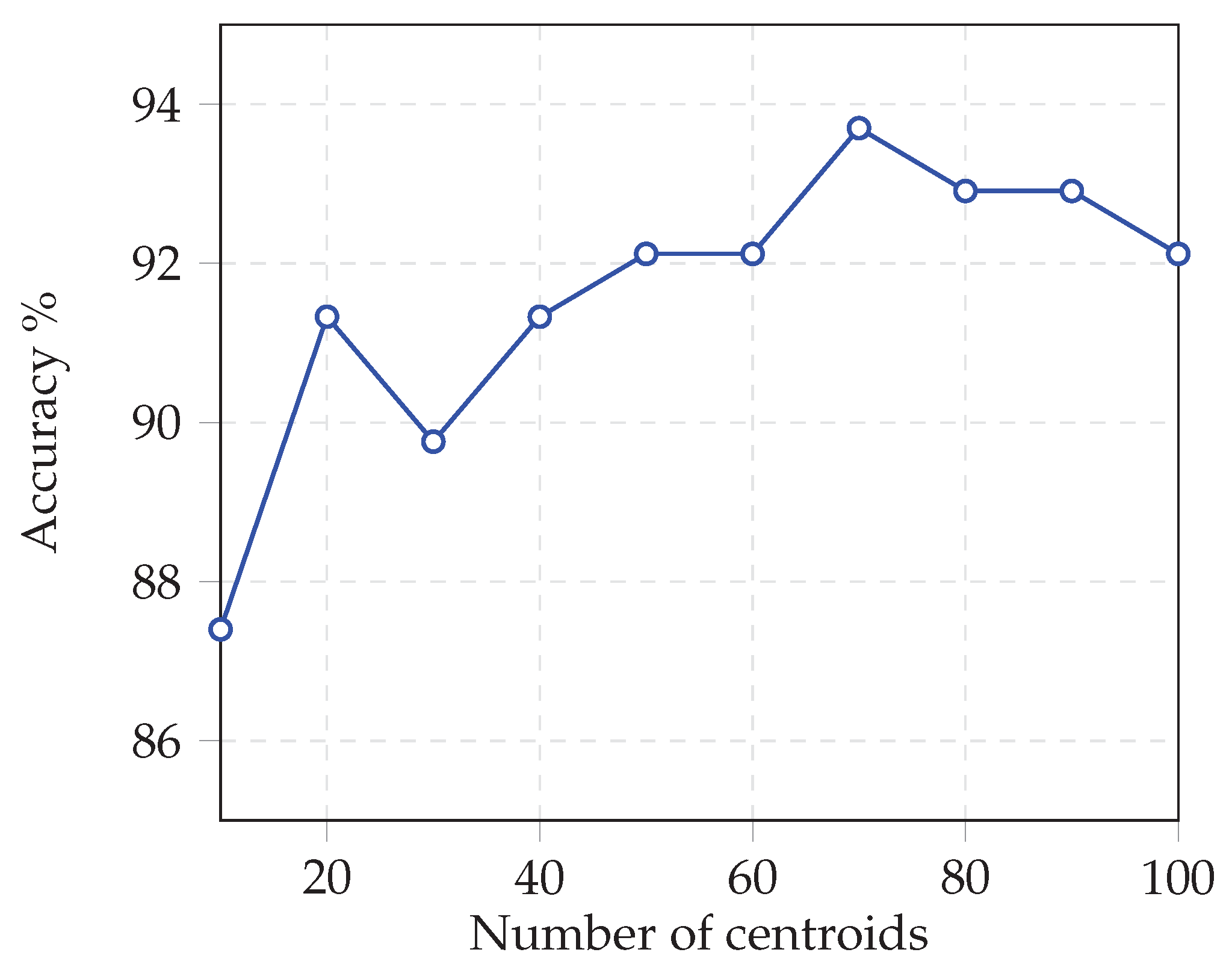

To realize this implementation, we pre-compute the centroids via the k-means algorithm (using Python’s scikit-learn library) and store them in a dedicated memory file for subsequent FPGA-based execution. We then evaluate all neural network configurations on each cluster within Python, thereby mapping each centroid to the network model that consistently delivers the highest accuracy for that cluster. As illustrated in Figure 1, this results in a refined selection mechanism wherein each cluster is paired with the top-performing classifier, yielding both improved accuracy and streamlined hardware utilization.

Figure 1.

Diagram of K-NC for the DNN Configuration Selector.

Upon receiving new test data, the system swiftly assigns it to the closest cluster, subsequently engaging the preselected, most efficient neural network model for that cluster’s classification task.

2.2. Methodology

In this methodology, we improve the diversity of the classifier by splitting the training dataset into two distinct subsets. The first subset is used to train the first half of our neural network models, while the second subset trains the remaining models. By doing so, each group of neural network configurations is exposed to different data patterns, thereby increasing the overall variety of learned representations and boosting the collective predictive accuracy.

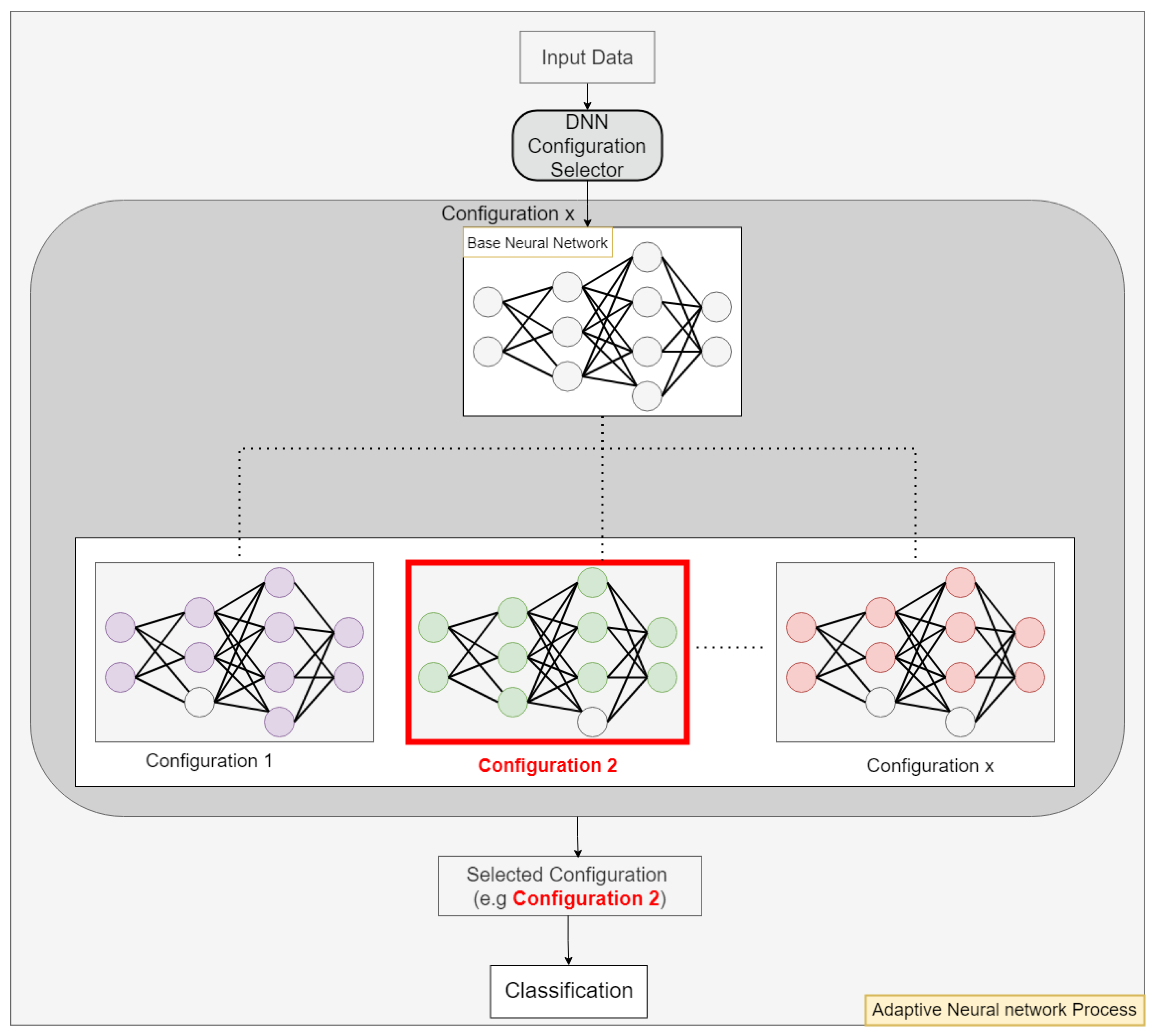

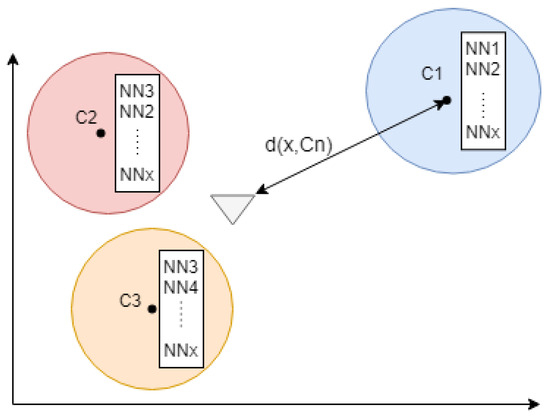

Once a configuration is selected, its corresponding parameters (weights and biases) are applied to the base neural network, which is depicted in Figure 2 as a densely connected network of neurons. Around this core structure, multiple configurations, designated as Configuration 1 through Configuration x, offer alternative architectures by varying the number of neurons and other settings. Critically, when choosing which model to deploy, the system also loads the relevant weights and biases for that specific configuration, ensuring optimal alignment between the chosen architecture and its parameters. The DNN Configuration Selector oversees this dynamic selection process, applying the most suitable configuration to each incoming data sample for efficient, high-accuracy inference.

Figure 2.

Diagram of the adaptive parameter neural network process.

Figure 2 illustrates the operational flow of our adaptive neural network design. First, the input data are directed to the DNN Configuration Selector, which identifies the optimal configuration, designated Configuration x, for that particular data instance. The parameters of the selected configuration are then loaded into the base neural network, represented by a dense network of interconnected neurons. Each configuration (from Configuration 1 through Configuration x) reflects a possible adaptation of the base network, featuring different neuron counts and other hyperparameters. Crucially, selecting the corresponding weights and biases ensures that the chosen network is precisely tuned to the incoming data. This adaptive selection mechanism maximizes accuracy while maintaining operational efficiency, as each input is processed using the most appropriate model variant.

3. NeuroAdaptiveNet Design

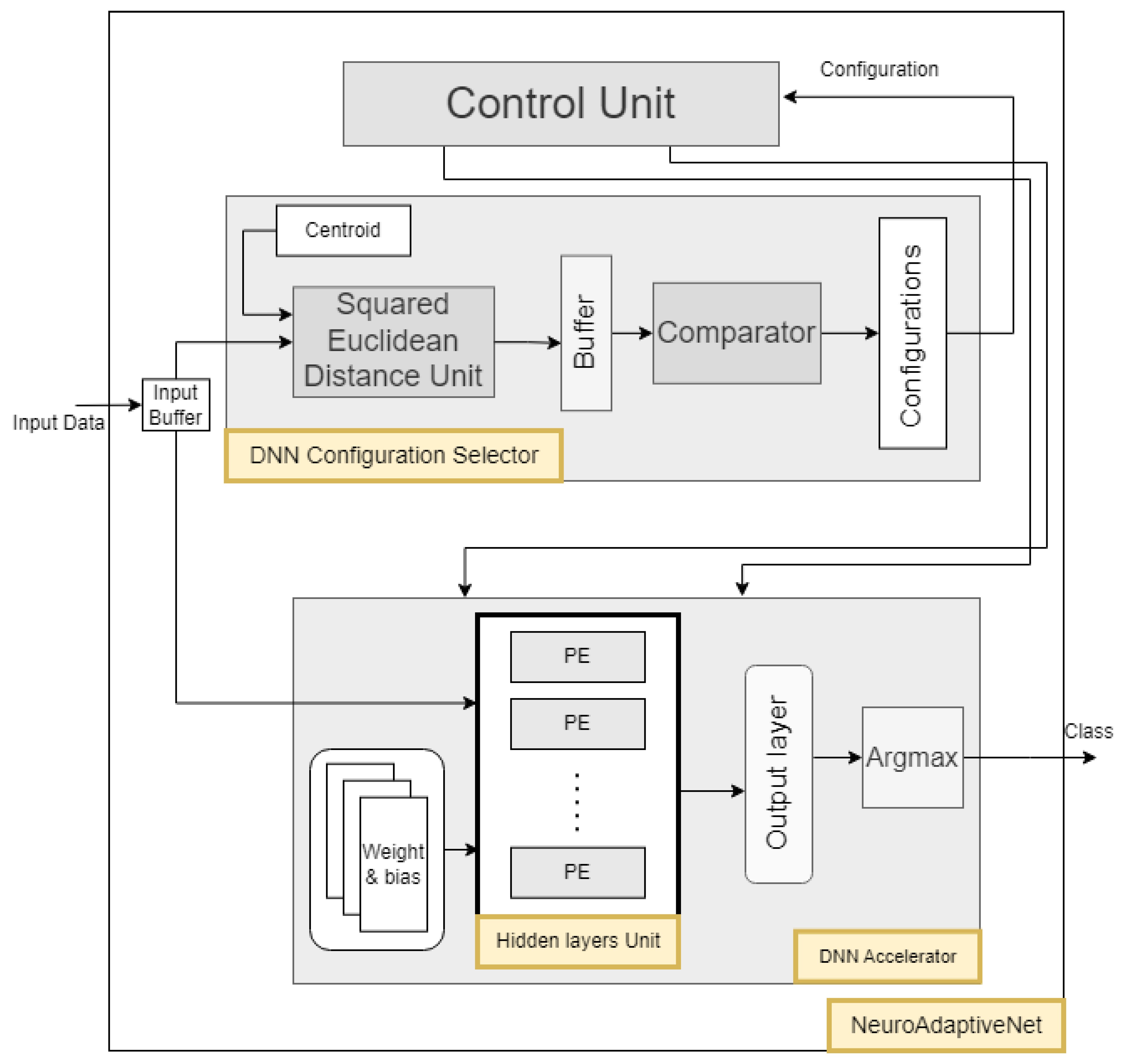

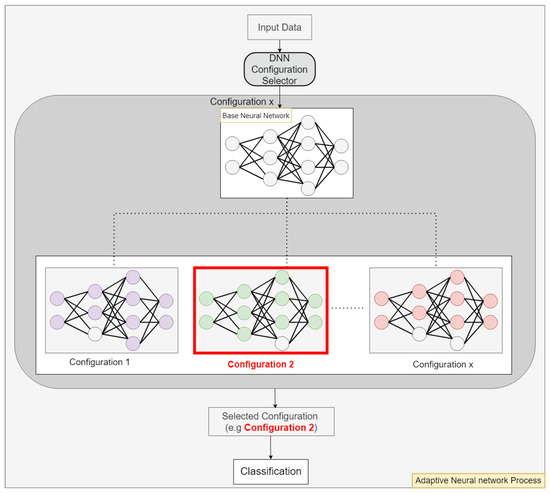

We implemented the design using Verilog, creating two primary modules as depicted in Figure 3: the DNN Configuration Selector module and the DNN Accelerator module.

Figure 3.

Diagram of the DNN Configuration Selector hardware implementation.

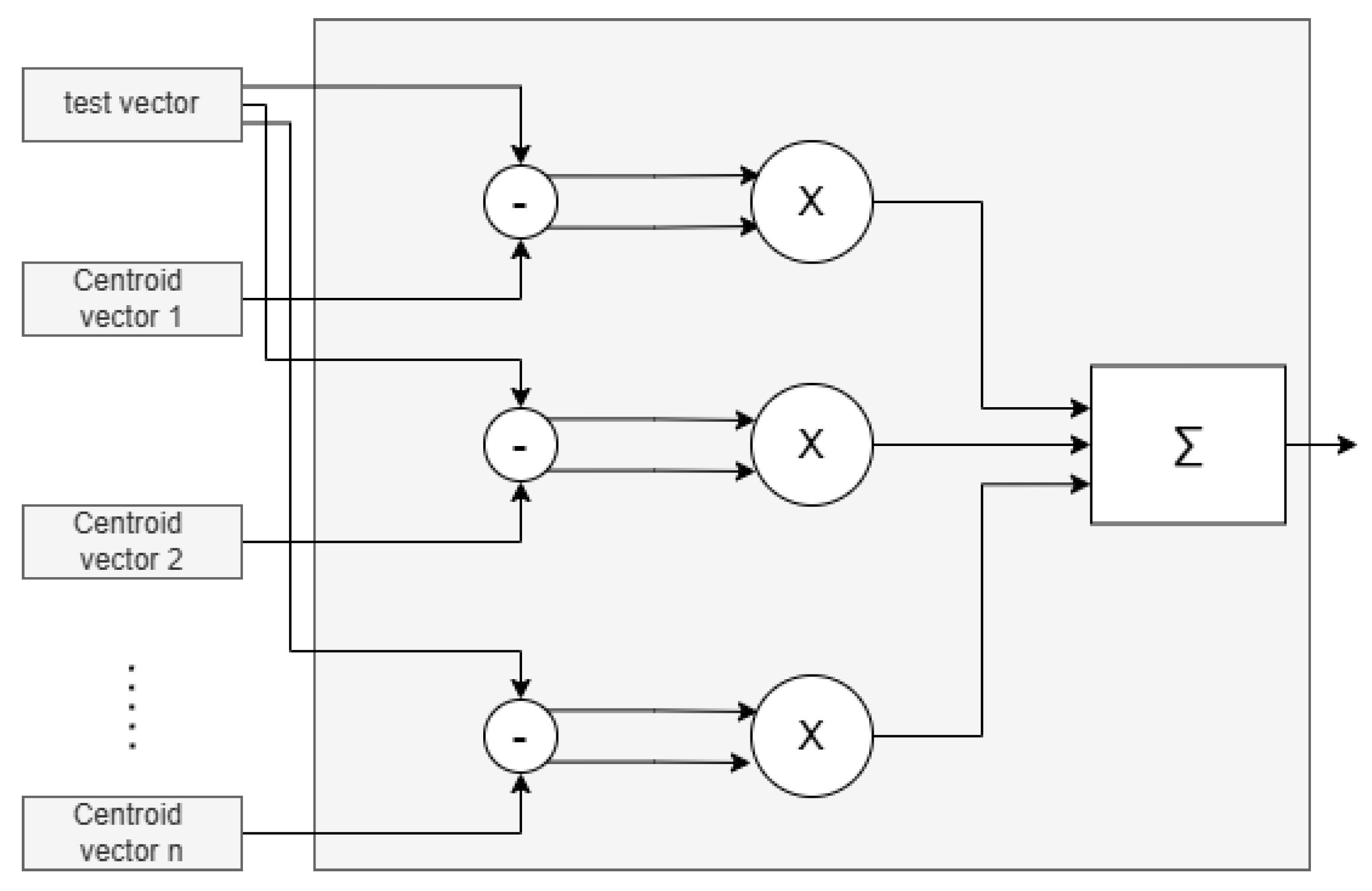

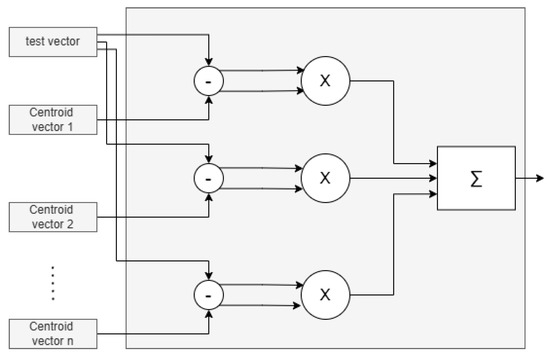

The DNN Configuration Selector module incorporates a Squared Euclidean Distance Unit that efficiently computes the distances between the input data vector and pre-stored centroids as shown in Figure 4. This computation is achieved through a pipeline of parallel subtractors, multipliers, and an accumulator.

Figure 4.

Diagram of the Squared Euclidean Distance Unit.

Initially, parallel subtractors calculate the differences between each feature of the input vector and the corresponding features of a centroid. These differences are then squared by the multipliers and the resulting squared values are aggregated by the accumulator to yield the squared Euclidean distance for the centroid. The computation adheres to the formula shown in Equation (1), enabling precise distance measurement while optimizing hardware performance.

where and are the individual features of the input vector and centroid.

After completing the centroid evaluations, the computed distances are temporarily stored in a buffer. A comparator examines these distances, identifies the smallest value, and retrieves its corresponding label to determine the most suitable neural network configuration. This selection process is facilitated by a lookup table, represented as the “configurations” block in Figure 3, which maps each closest centroid to its optimal neural network model configuration. This association ensures that each input data point is processed by the configuration best suited for accurate classification.

The Control Unit serves as a critical component, managing the data flow and overseeing all computational tasks within the system. It directs the neural network module to deploy the specific configuration identified by the DNN Configuration Selector, ensuring smooth operation and accurate classification.

In our FPGA architecture, each processing element mimics the function of a traditional neuron by carrying out Multiply-Accumulate operations followed by ReLU activation. Each processing element multiplies input vector elements by their corresponding weights W and adds a bias term b. This is mathematically represented as follows:

The implementation of the ReLU activation function is achieved using a comparator along with a 2:1 Multiplexer. This setup allows the activation function to be expressed mathematically as follows:

This implementation allows each processing element to efficiently handle all necessary calculations and activation steps, closely mimicking the behavior of neurons in traditional neural network models. The architecture accommodates variable neuron counts and supports multiple layers. In a static implementation, the design instantiates as many processing elements as the size of the largest hidden layer. For NeuroAdaptiveNet, we instantiate processing elements equal to the maximum hidden-layer size across all configurations in the ensemble. This arrangement ensures that all neurons within each layer execute in parallel, while layers are processed sequentially.

In the output stage, the commonly used softmax activation is replaced by the argmax function to better align with our focus on maximizing classification accuracy. The argmax function identifies the neuron with the highest output and converts this information into a one-hot encoded vector, circumventing the need for complete class probability distributions. This streamlined approach reduces computational overhead, simplifies hardware complexity, and accelerates inference.

4. Results

4.1. Dataset and Pre-Processing

We evaluate the NeuroAdaptiveNet system, implemented on an FPGA, using four distinct datasets from the UCI repository: Pima Indian Diabetes, Vehicle Silhouettes, Connect-4, and German Credit. These datasets vary in complexity and classification tasks, with Pima Indian Diabetes and German Credit tailored for binary classification and Vehicle Silhouettes and Connect-4 involving multiclass classification.

To maintain uniformity across these heterogeneous datasets, we adopt an 85–15 split for data partitioning. Specifically, 85% of each dataset is used both to train the models and to compute centroids. The remaining 15% of the data is held out for testing and performance evaluation, enabling a comprehensive assessment of the system’s accuracy and robustness.

The design is implemented on an Ultra96v2 board featuring the Zynq UltraScale+ MPSoC. Our FPGA implementations employ a 16-bit fixed-point format for all input vectors, weights, biases, and centroids.

We run scikit-learn’s KMeans multiple times to generate different centroid initializations, then select the initialization that performs best on a validation subset of the training data.

4.2. Configurations

We employ a small ensemble of compact neural networks that differ in both their training data and their architecture. To create this ensemble, we partition the full training set into two subsets and train half of our network configurations on the first subset and the other half on the second. Each configuration also varies the number of neurons per layer. Although this ensemble is not intended to represent the optimal combination of models, it demonstrates that selecting from a diverse collection of smaller networks for each individual input can achieve a more resource and energy-efficient adaptive implementation than relying on a single, statically configured network.

Table 1 lists the network configurations that make up the NeuroAdaptiveNet ensemble for each dataset. Each configuration is defined by its layer-wise neuron counts, ensuring a diverse set of model. At runtime, the DNN Configuration Selector chooses the configuration best suited to the current input and the accelerator dynamically loads its corresponding weights, biases, and neuron-count settings before performing inference.

Table 1.

Neural network configuration parameters.

Upon receiving an input sample, the selector identifies the optimal network configuration, which is defined by its layer-wise neuron counts, weight matrices, and bias vectors. The accelerator then loads these parameters and performs inference by processing exactly the specified neurons in each layer. We train each network configuration in Python 3.8 and export its weights and bias vectors into memory initialization files.

4.3. Accuracy Results

With the ensemble configurations defined, we now evaluate the classification accuracy of NeuroAdaptiveNet against static network designs.

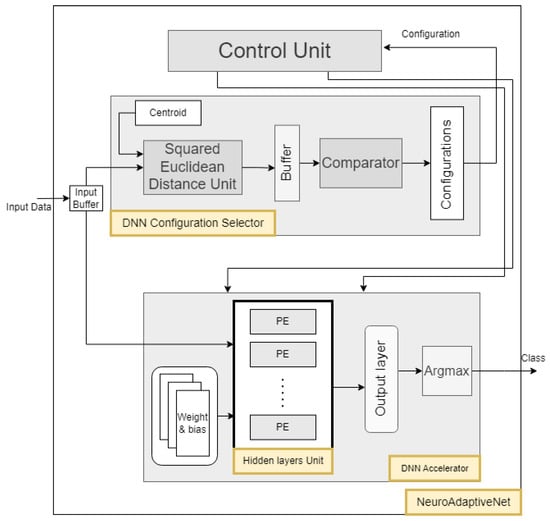

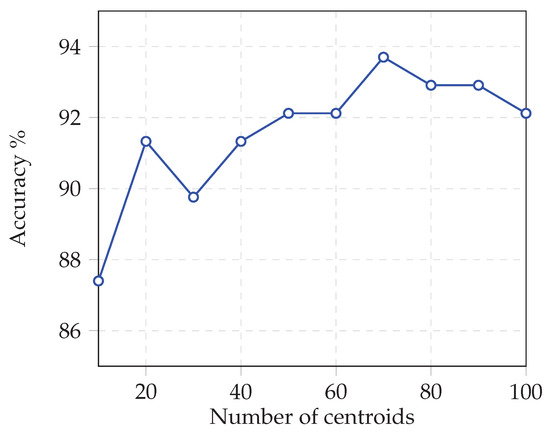

Determining the optimal number of centroids C is critical. This parameter has a critical impact on accuracy. To identify the best value, we ran a series of experiments varying the number of centroids from 10 to 100 for smaller datasets and from 10 to 200 for larger ones. Figure 5 shows how accuracy on the Vehicle dataset improves as the number of centroids increases.

Figure 5.

Effect of centroid count on classification accuracy for the Vehicle dataset.

Figure 5 clearly shows that increasing the number of centroids from 10 to 70 raises classification accuracy from 87.40% to 93.70%. This improvement occurs because each additional centroid refines the partitioning of the feature space, creating more regions in which a specialized network can operate.

Following comprehensive experiments to determine each dataset’s optimal centroid count, we evaluate NeuroAdaptiveNet performance against static neural network models with larger, denser architectures, as shown in Table 2.

Table 2.

Neural network model accuracy comparison.

The results indicate that the NeuroAdaptiveNet system outperforms the traditional models in all tested datasets, achieving up to 4.31% more accuracy. The NeuroAdaptiveNet showed higher accuracy compared to several larger networks employing the standard approach. This pattern of enhanced performance was consistent across all datasets, with the NeuroAdaptiveNet system demonstrating a clear advantage over the traditional setups.

For the Vehicle Silhouettes and German Credit datasets, the best configuration was achieved with 70 centroids. In contrast, the Diabetes dataset reached optimal performance with a different centroid count of 50, while the Connect-4 dataset required 180 centroids for the best results.

4.4. Resource Utilization and Power Analysis

Resource usage is a key indicator of FPGA designs efficiency. In this analysis, we compare how much hardware different neural network models use for all datasets. This helps us understand which designs are most efficient for specific applications.

Across all four benchmarks, as shown in Table 3, Table 4, Table 5 and Table 6, NeuroAdaptiveNet delivers consistent FPGA resource savings: LUT utilization decreases by roughly 4% to 15%, FF usage by approximately 19% to 51%, and DSP consumption by about 25% to 53%. These results demonstrate that NeuroAdaptiveNet effectively minimizes hardware utilization without sacrificing accuracy. These resource reductions result from NeuroAdaptiveNet’s dynamic use of compact networks, each of which requires fewer processing elements than a single, larger fixed design.

Table 3.

Resource utilization comparison for Vehicle dataset.

Table 4.

Resource utilization comparison for Connect-4 dataset.

Table 5.

Resource utilization comparison for Diabetes dataset.

Table 6.

Resource utilization comparison for German-Credit dataset.

We observed that NeuroAdaptiveNet uses more LUTRAM than a single static design. This increase results from storing multiple parameter sets, including each configuration’s weights and biases, as well as the centroid feature vectors required by the DNN Configuration Selector.

To assess the energy efficiency of our adaptive architecture, we performed post-implementation power estimation in Xilinx Vivado, targeting the programmable logic of an Ultra96-V2 board (Zynq UltraScale+ MPSoC). NeuroAdaptiveNet was configured with the centroid counts that maximize classification accuracy for each dataset, and its PL dynamic power consumption was compared against the highest-performing static Neural network implementation. The results are summarized in Table 7.

Table 7.

Dynamic PL power consumption and percentage decrease.

Table 7 presents the dynamic PL power consumption of NeuroAdaptiveNet when configured with the centroid counts (C) that yielded the highest classification accuracy on each dataset, compared against the corresponding neural networks (120, 120, 64) for Connect-4, (16, 16) for Diabetes, (60, 60, 30) for Vehicle, and (32, 32) for German-Credit, NeuroAdaptiveNet achieves power savings of 10.1%, 24.5%, 1.5%, and 18.2%, respectively. These findings confirm that NeuroAdaptiveNet consistently reduces FPGA power consumption compared to conventional fixed neural networks, achieving substantial energy savings without sacrificing accuracy.

4.5. Latency Analysis

Inference latency is a key metric for real-time neural network applications. Table 8 presents the measured maximum clock frequencies and inference latencies for NeuroAdaptiveNet.

Table 8.

Maximum frequency and inference latency.

The integration of the DNN Configuration Selector for centroid evaluation adds only a small latency overhead. Inference latency increases by 0.67 µs on Connect-4, 0.32 µs on Diabetes, 0.23 µs on Vehicle, and 0.40 µs on German-Credit.

5. Discussion

The NeuroAdaptiveNet framework, optimized for FPGA deployment, delivers remarkable hardware efficiency and classification accuracy. It relies on a k-nearest centroid mechanism, a distance-based approach akin to k-NN, making it susceptible to the curse of dimensionality [16]. As feature dimensionality increases, the number of subtractors, multipliers, and accumulators required to compute distances grows substantially, and the memory must store larger centroid vectors. The increased computational and storage requirements can offset the advantages of the method when applied to very high-dimensional data. To enhance its performance, dimensionality reduction techniques such as principal component analysis (PCA) or neural autoencoders can be employed to compress high-dimensional features into more compact, informative representations [17]. Additionally, designing adaptive distance metrics tailored for high-dimensional spaces can refine feature comparisons and reduce computational complexity. These additional improvements could potentially preserve the efficiency of NeuroAdaptiveNet while extending its applicability to real-time FPGA-based systems that manage complex, large-scale datasets.

6. Conclusions

The NeuroAdaptiveNet system represents a novel approach to FPGA-based neural networks, offering dynamic adaptability and high accuracy for real-time and edge computing scenarios. Experimental results across diverse datasets confirm its effectiveness in adjusting neural network configurations on a per-input basis, thus balancing hardware resource management and classification performance.

By capitalizing on an adaptive architecture that reconfigures its parameters in response to incoming data, NeuroAdaptiveNet showcases significant benefits over static neural network models, particularly in terms of efficiency and response time. This ability to select the most suitable neural configuration for each input greatly enhances its applicability in resource-limited environments where computational demands and power constraints are paramount.

Looking ahead, the integration of dimensionality reduction techniques and specialized distance metrics offers promising avenues to counteract the limitations posed by high-dimensional data. These enhancements have the potential to reinforce the adaptability of NeuroAdaptiveNet, further increasing its performance in a wide range of real-time and edge computing applications. Ultimately, the system’s flexibility and efficiency mark a meaningful step forward in developing next-generation, FPGA-optimized neural network solutions.

Author Contributions

Conceptualization, A.E.B.; methodology, A.E.B.; software, A.E.B.; formal analysis, A.E.B.; resources, A.E.B., A.H. and O.M.; writing—original draft preparation, A.E.B.; writing—review and editing, A.E.B., A.H. and O.M.; visualization, A.E.B.; supervision, A.H. and O.M.; project administration, A.H. and O.M.; funding acquisition, A.H. and O.M. All authors have read and agreed to the published version of the manuscript.

Funding

This research received no external funding.

Institutional Review Board Statement

Not applicable.

Informed Consent Statement

Not applicable.

Data Availability Statement

No new data were created or analyzed in this study. Data sharing is not applicable to this article.

Conflicts of Interest

The authors declare no conflicts of interest.

References

- Müller, B.; Reinhardt, J.; Strickland, M.T. Neural Networks: An Introduction; Springer Science & Business Media: Berlin/Heidelberg, Germany, 2012. [Google Scholar]

- Alpaydin, E. Introduction to Machine Learning; MIT Press: Cambridge, MA, USA, 2020. [Google Scholar]

- Chen, L.; Lin, S.; Lu, X.; Cao, D.; Wu, H.; Guo, C.; Liu, C.; Wang, F.Y. Deep neural network based vehicle and pedestrian detection for autonomous driving: A survey. IEEE Trans. Intell. Transp. Syst. 2021, 22, 3234–3246. [Google Scholar] [CrossRef]

- Ali, A.; Almaiah, M.A.; Hajjej, F.; Pasha, M.F.; Fang, O.H.; Khan, R.; Teo, J.; Zakarya, M. An industrial IoT-based blockchain-enabled secure searchable encryption approach for healthcare systems using neural network. Sensors 2022, 22, 572. [Google Scholar] [CrossRef] [PubMed]

- Beckerleg, M.; Matulich, J.; Wong, P. A comparison of three evolved controllers used for robotic navigation. AIMS Electron. Electr. Eng. 2020, 4, 259–286. [Google Scholar] [CrossRef]

- Gauni, S.; Chandhar, P. Modulation classification analysis of CNN model for wireless communication systems. AIMS Electron. Electr. Eng. 2023, 7, 337–353. [Google Scholar]

- Ma, Y.; Cao, Y.; Vrudhula, S.; Seo, J.S. Optimizing the convolution operation to accelerate deep neural networks on FPGA. IEEE Trans. Very Large Scale Integr. Syst. 2018, 26, 1354–1367. [Google Scholar] [CrossRef]

- Khalil, K.; Kumar, A.; Bayoumi, M. Reconfigurable hardware design approach for economic neural network. IEEE Trans. Circuits Syst. Express Briefs 2022, 69, 5094–5098. [Google Scholar] [CrossRef]

- Cho, J.; Jung, Y.; Lee, S.; Jung, Y. Reconfigurable binary neural network accelerator with adaptive parallelism scheme. Electronics 2021, 10, 230. [Google Scholar] [CrossRef]

- Oliveira, J.G.; Moreno, R.L.; de Oliveira Dutra, O.; Pimenta, T.C. Implementation of a reconfigurable neural network in FPGA. In Proceedings of the 2017 International Caribbean Conference on Devices, Circuits and Systems (ICCDCS), Cozumel, Mexico, 5–7 June 2017; IEEE: Piscataway, NJ, USA, 2017; pp. 41–44. [Google Scholar]

- Giacinto, G.; Roli, F. Dynamic classifier selection. In Proceedings of the International Workshop on Multiple Classifier Systems, Cagliari, Italy, 21–23 June 2000; Springer: Berlin/Heidelberg, Germany, 2000; pp. 177–189. [Google Scholar]

- Giacinto, G.; Roli, F. Methods for dynamic classifier selection. In Proceedings of the 10th International Conference on Image Analysis and Processing, Venice, Italy, 27–29 September 1999; IEEE: Piscatway, NJ, USA, 1999; pp. 659–664. [Google Scholar]

- Cruz, R.M.; Sabourin, R.; Cavalcanti, G.D. Dynamic classifier selection: Recent advances and perspectives. Inf. Fusion 2018, 41, 195–216. [Google Scholar] [CrossRef]

- El Bouazzaoui, A.; Hadjoudja, A.; Mouhib, O.; Cherkaoui, N. FPGA-based ML adaptive accelerator: A partial reconfiguration approach for optimized ML accelerator utilization. Array 2024, 21, 100337. [Google Scholar] [CrossRef]

- El Bouazzaoui, A.; Jariri, N.; Mouhib, O.; Hadjoudja, A. Adaptive K values and training subsets selection for optimal K-NN performance on FPGA. J. King Saud Univ. Comput. Inf. Sci. 2024, 36, 102081. [Google Scholar] [CrossRef]

- Indyk, P. Nearest neighbors in high-dimensional spaces. In Handbook of Discrete and Computational Geometry; Taylor & Francis: Boca Raton, FL, USA, 2004. [Google Scholar]

- Reddy, G.T.; Reddy, M.P.K.; Lakshmanna, K.; Kaluri, R.; Rajput, D.S.; Srivastava, G.; Baker, T. Analysis of dimensionality reduction techniques on big data. IEEE Access 2020, 8, 54776–54788. [Google Scholar] [CrossRef]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).