Topic Menu

► Topic MenuAdvances in Microelectronics and Semiconductor Engineering

Topic Information

Dear Colleagues,

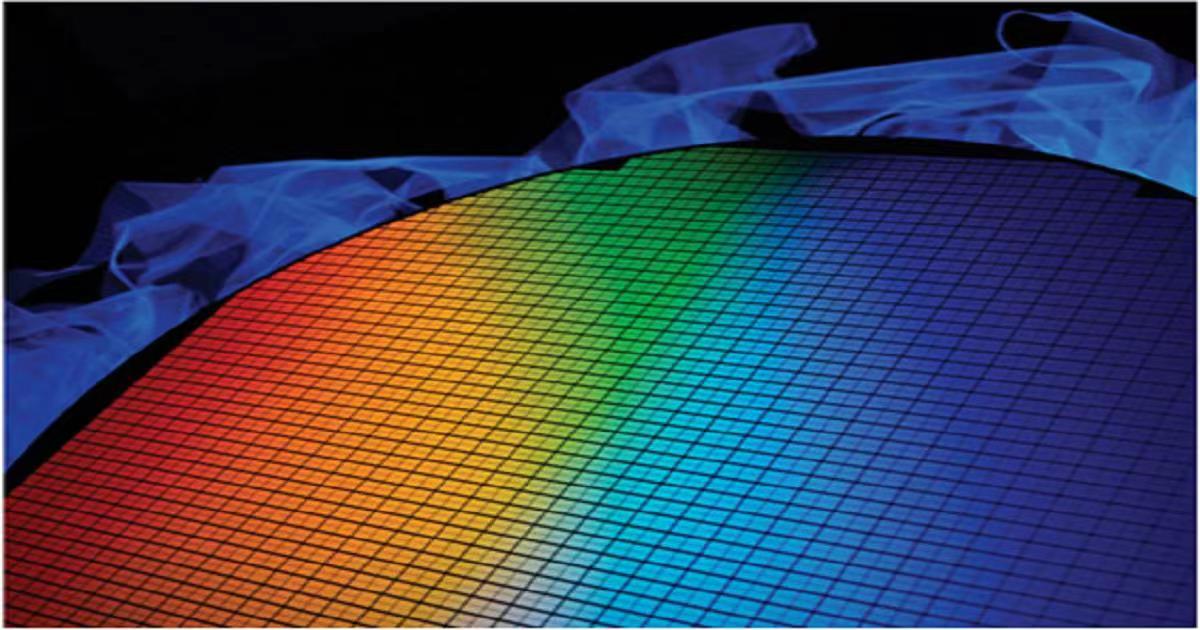

Silicon microelectronics is at the heart of modern electronics, finding applications in the computing, data processing, data storage, communications, and Internet of Things fields. Its development has been guided by Moore’s law since the 1970s and is now reaching its physical limits related to device dimension, integration density, and complexity both in CMOS and memory technologies. To overcome these limits, new challenges have been addressed regarding new material integration for FEOL and BEOL purposes, new processes for material growth, deposition, doping, etching and patterning, new device architectures for better scalability, improved physical characterization techniques for CD metrology, and advanced device and interconnect electrical characterization methodologies.

Dr. Gerard Ghibaudo

Dr. Francis Balestra

Topic Editors

Keywords

- new materials

- integration processes

- device architectures

- physical characterization and metrology

- electrical characterization and reliability

- CMOS

- memories

- cryogenic electronics

- beyond CMOS

- 3D integration

Participating Journals

| Journal Name | Impact Factor | CiteScore | Launched Year | First Decision (median) | APC |

|---|---|---|---|---|---|

Applied Sciences

|

2.5 | 5.5 | 2011 | 16 Days | CHF 2400 |

Electronics

|

2.6 | 6.1 | 2012 | 16.4 Days | CHF 2400 |

Materials

|

3.2 | 6.4 | 2008 | 15.5 Days | CHF 2600 |

Applied Nano

|

- | 4.6 | 2020 | 15.7 Days | CHF 1000 |

Technologies

|

3.6 | 8.5 | 2013 | 19.1 Days | CHF 1800 |

Inventions

|

1.9 | 4.9 | 2016 | 21.9 Days | CHF 1800 |

Chips

|

- | - | 2022 | 22.4 Days | CHF 1000 |

Preprints.org is a multidisciplinary platform offering a preprint service designed to facilitate the early sharing of your research. It supports and empowers your research journey from the very beginning.

MDPI Topics is collaborating with Preprints.org and has established a direct connection between MDPI journals and the platform. Authors are encouraged to take advantage of this opportunity by posting their preprints at Preprints.org prior to publication:

- Share your research immediately: disseminate your ideas prior to publication and establish priority for your work.

- Safeguard your intellectual contribution: Protect your ideas with a time-stamped preprint that serves as proof of your research timeline.

- Boost visibility and impact: Increase the reach and influence of your research by making it accessible to a global audience.

- Gain early feedback: Receive valuable input and insights from peers before submitting to a journal.

- Ensure broad indexing: Web of Science (Preprint Citation Index), Google Scholar, Crossref, SHARE, PrePubMed, Scilit and Europe PMC.