Journal Description

Chips

Chips

is an international, peer-reviewed, open access journal on all aspects of chips published quarterly online by MDPI.

- Open Access— free for readers, with article processing charges (APC) paid by authors or their institutions.

- High Visibility: indexed within Scopus and other databases.

- Rapid Publication: manuscripts are peer-reviewed and a first decision is provided to authors approximately 22.4 days after submission; acceptance to publication is undertaken in 5.7 days (median values for papers published in this journal in the second half of 2025).

- Recognition of Reviewers: APC discount vouchers, optional signed peer review and reviewer names are published annually in the journal.

- Companion journal: Sensors.

- Journal Cluster of Electronic Engineering and Hardware Systems: Chips, Electronics, Hardware, Journal of Low Power Electronics and Applications, Microelectronics and Microwave.

Latest Articles

Security Threats and AI-Based Detection Techniques in IoT Chips

Chips 2026, 5(1), 9; https://doi.org/10.3390/chips5010009 - 4 Mar 2026

Abstract

The rapid expansion of the Internet of Things (IoT) has opened resource-limited devices to novel physical threats, such as Side-Channel Attacks (SCAs) and Hardware Trojans (HTs). Traditional security mechanisms are often not capable of standing against such hardware-based attacks, specifically on low-power System-on-Chip

[...] Read more.

The rapid expansion of the Internet of Things (IoT) has opened resource-limited devices to novel physical threats, such as Side-Channel Attacks (SCAs) and Hardware Trojans (HTs). Traditional security mechanisms are often not capable of standing against such hardware-based attacks, specifically on low-power System-on-Chip (SoC) where static defenses can incur 2× to 3× overhead in silicon area and power. Herein, the gap between hardware security and embedded AI is compositionally formulated for discussion. We present a comprehensive survey of the current hardware threat landscape and analyze the emergence of “Secure-by-Design” paradigms, specifically focusing on the integration of Edge AI and TinyML as active, on-chip intrusion detection mechanisms. This review presents a critical analysis of trade-offs for running lightweight ML models on hardware by comparing state-of-the-art approaches. Our analysis highlights that optimized architectures, such as Mamba-Enhanced Convolutional Neural Networks (CNNs) and Gated Recurrent Unit (GRU), can achieve detection accuracies exceeding 99% against SCA and >92% against stealthy Hardware Trojans, while offering up to 75% lower power consumption compared to standard deep learning baselines. Finally, open challenges such as adversarial attacks on defense models are briefly discussed, and the focus is put on future directions toward constructing secure chips based on robust, AI-driven technology.

Full article

(This article belongs to the Special Issue Emerging Issues in Hardware and IC System Security)

►

Show Figures

Open AccessArticle

An LOFIC Image Sensor Readout Circuit with an On-Chip HDR Merger Achieving 36.5% Area and 14.9% Power Reduction

by

Nao Kitajima, Seina Hori, Ai Otani, Hiroaki Ogawa and Shunsuke Okura

Chips 2026, 5(1), 8; https://doi.org/10.3390/chips5010008 - 24 Feb 2026

Abstract

►▼

Show Figures

For sensing applications, a complementary metal oxide semiconductor (CMOS) image sensor (CIS) with a lateral overflow integration capacitor (LOFIC) is in high demand. The LOFIC CIS can achieve high-dynamic-range (HDR) imaging by combining a low-conversion-gain (LCG) signal for large maximum signal electrons and

[...] Read more.

For sensing applications, a complementary metal oxide semiconductor (CMOS) image sensor (CIS) with a lateral overflow integration capacitor (LOFIC) is in high demand. The LOFIC CIS can achieve high-dynamic-range (HDR) imaging by combining a low-conversion-gain (LCG) signal for large maximum signal electrons and a high-conversion-gain (HCG) signal for a low electron-referred noise floor. However, the LOFIC CIS faces challenges regarding the power consumption and circuit area when reading both HCG and LCG signals. To address these issues, this study proposes a readout circuit composed of area-efficient MOS capacitors using a folding DC operating point technique and an in-column signal selector for an on-chip HDR merger of HCG and LCG signals. A 10-bit test chip was fabricated with a

Figure 1

Open AccessArticle

Hardware Acceleration with LWECC Approach on Memory and Router Optimization in Communication Applications

by

Ramakrishna Goli, Aravindhan Alagarsamy and Gian Carlo Cardarilli

Chips 2026, 5(1), 7; https://doi.org/10.3390/chips5010007 - 23 Feb 2026

Abstract

The fast expansion of the Internet of Things (IoT) has increased the need for strong security measures to protect the enormous network of interconnected devices. This paper proposes a unique approach that combines optimization, intuitive design principles, and Least Weighted Elliptic Curve Cryptography

[...] Read more.

The fast expansion of the Internet of Things (IoT) has increased the need for strong security measures to protect the enormous network of interconnected devices. This paper proposes a unique approach that combines optimization, intuitive design principles, and Least Weighted Elliptic Curve Cryptography (LWECC) to improve IoT device security while reducing power consumption. The proposed optimization strategy focuses on lowering computational overhead, which is critical for IoT devices with limited energy and processing power. The proposed method significantly reduces the amount of energy required for cryptographic operations by carefully selecting appropriate elliptic curves and optimizing cryptographic algorithms, ensuring that IoT devices may continue to function without compromising security. Furthermore, by selecting elliptic curves with minimal attack vulnerability, the use of LWECC provides an additional layer of protection. This technique ensures that, even in the face of emerging threats, IoT devices remain highly resilient, reducing the chance of security breaches while preserving functionality without using excessive power. Experimental results show a power consumption of only 0.156 W and 0.25 W for memory and router topologies, respectively, with an error margin of 0.01. The stated error margin pertains to the simulation-based evaluation of transmission-level data handling within the LWECC-enabled memory/router pipeline, rather than the risk of physical memory-cell failure or fabrication yield. The value shows the maximum amount of packet/data-stream loss detected during encrypted data transfer, rather than hardware memory reliability.

Full article

(This article belongs to the Special Issue Emerging Issues in Hardware and IC System Security)

►▼

Show Figures

Figure 1

Open AccessArticle

A Novel Design of Industrial Reconfigurable CDC

by

Karim M. Abozeid, Hassan Mostafa, A. H. Khalil and Mohamed Refky

Chips 2026, 5(1), 6; https://doi.org/10.3390/chips5010006 - 5 Feb 2026

Abstract

This paper presents a novel design for a reconfigurable CDC as a multiplexed sensor fusion that converts three analog signals into digital output bits with different resolutions. The proposed reconfigurable CDC design uses the SAR technique that introduces a small chip area and

[...] Read more.

This paper presents a novel design for a reconfigurable CDC as a multiplexed sensor fusion that converts three analog signals into digital output bits with different resolutions. The proposed reconfigurable CDC design uses the SAR technique that introduces a small chip area and low power consumption. The proposed novel CDC introduces reconfigurability by using a switching capacitive DAC that solves the problem of converting more than one analog signal with a single converter to a different number of output bits, giving better performance than previous designs. In this paper, three analog signals are used (as a case study) in a weather station to be converted. These signals are temperature, pressure, and humidity that are sensed using the BME-280 Bosch sensor. All CDC specifications are measured for each reconfigured number of output bits. The used supply voltage is 1.0 V, and the sampling frequency is 100 kHz. The 12-bit resolution consumes 2.54 µW, ENOB is 11.47 bits, and SNR equals 73.4 dB. The 8-bit resolution consumes 1.7 µW, ENOB is 7.39 bits, and SNR equals 46.24 dB. The 4-bit resolution consumes 0.68 µW, ENOB is 3.58 bits, and SNR equals 23.45 dB. The total chip area is 0.18 mm2.

Full article

(This article belongs to the Special Issue Design and Implementation of Reconfigurable Optoelectronic Integrated Chips)

►▼

Show Figures

Figure 1

Open AccessArticle

Highly Parallel Sorting Network Verification Using FPGAs

by

Philippos Papaphilippou

Chips 2026, 5(1), 5; https://doi.org/10.3390/chips5010005 - 4 Feb 2026

Abstract

►▼

Show Figures

Sorting networks are of prime importance as circuits, with applications in sorting small data chunks, big data analytics, permuting packets, and system interconnects. Finding optimal sorting networks is a highly complex problem, and knowledge on optimal sorting networks is limited. When optimising the

[...] Read more.

Sorting networks are of prime importance as circuits, with applications in sorting small data chunks, big data analytics, permuting packets, and system interconnects. Finding optimal sorting networks is a highly complex problem, and knowledge on optimal sorting networks is limited. When optimising the network depth or the number of comparators, one of the most expensive tasks is considered to be verification, that is, to verify that the candidate compare-and-swap network actually sorts the data. This grows exponentially with the size of the sorting network. However, FPGAs allow vast amounts of internal parallelism, and our presented work exploits this flexibility using dataflow techniques to achieve unparalleled amounts of speedup for sorting network verification. This work can be used in a modular way to accelerate the search for optimal sorting networks with a high number of inputs, as well for similar verification problems.

Full article

Figure 1

Open AccessReview

A Review of Thermal Management Techniques Adopted for High-Power-Density GaN-Based Converters

by

Mohamed Belguith, Sonia Eloued, Moncef Kadi, Jaleleddine Ben Hadj Slama and Mahmoud Hamouda

Chips 2026, 5(1), 4; https://doi.org/10.3390/chips5010004 - 22 Jan 2026

Cited by 2

Abstract

►▼

Show Figures

Power converters based on gallium nitride (GaN) are progressing swiftly owing to their exceptional efficiency and tiny dimensions, boosted by high power density and fast switching capabilities. Nevertheless, these benefits are accompanied by considerable thermal management issues that impact reliability, performance, and operational

[...] Read more.

Power converters based on gallium nitride (GaN) are progressing swiftly owing to their exceptional efficiency and tiny dimensions, boosted by high power density and fast switching capabilities. Nevertheless, these benefits are accompanied by considerable thermal management issues that impact reliability, performance, and operational lifespan. This review examines advanced thermal management approaches for high-power-density GaN power converters, including active and passive cooling technologies, sophisticated packaging designs, and the use of novel materials like graphene and diamond to improve heat dissipation. The impacts of thermal boundary resistance, self-heating phenomena, and substrate selection on thermal performance are thoroughly analyzed. Strategies for enhancing printed circuit board (PCB) layouts, thermal vias, and the use of thermal interface materials (TIMs) are also emphasized. The study highlights co-design approaches that optimize thermal resistance and layout efficiency, supporting GaN operation under high-frequency conditions. This thorough investigation offers insights into addressing the thermal challenges linked to GaN technology, promoting its adoption in forthcoming power devices.

Full article

Figure 1

Open AccessReview

A New Era in Computing: A Review of Neuromorphic Computing Chip Architecture and Applications

by

Guang Chen, Meng Xu, Yuying Chen, Fuge Yuan, Lanqi Qin and Jian Ren

Chips 2026, 5(1), 3; https://doi.org/10.3390/chips5010003 - 22 Jan 2026

Abstract

Neuromorphic computing, an interdisciplinary field combining neuroscience and computer science, aims to create efficient, bio-inspired systems. Different from von Neumann architectures, neuromorphic systems integrate memory and processing units to enable parallel, event-driven computation. By simulating the behavior of biological neurons and networks, these

[...] Read more.

Neuromorphic computing, an interdisciplinary field combining neuroscience and computer science, aims to create efficient, bio-inspired systems. Different from von Neumann architectures, neuromorphic systems integrate memory and processing units to enable parallel, event-driven computation. By simulating the behavior of biological neurons and networks, these systems excel in tasks like pattern recognition, perception, and decision-making. Neuromorphic computing chips, which operate similarly to the human brain, offer significant potential for enhancing the performance and energy efficiency of bio-inspired algorithms. This review introduces a novel five-dimensional comparative framework—process technology, scale, power consumption, neuronal models, and architectural features—that systematically categorizes and contrasts neuromorphic implementations beyond existing surveys. We analyze notable neuromorphic chips, such as BrainScaleS, SpiNNaker, TrueNorth, and Loihi, comparing their scale, power consumption, and computational models. The paper also explores the applications of neuromorphic computing chips in artificial intelligence (AI), robotics, neuroscience, and adaptive control systems, while facing challenges related to hardware limitations, algorithms, and system scalability and integration.

Full article

(This article belongs to the Special Issue Neuromorphic Chips at the Intersection of Neuroscience, Electronics and AI)

►▼

Show Figures

Figure 1

Open AccessArticle

A Procedure for Fast Circuit Cross Section Estimation

by

Clayton R. Farias, Tiago R. Balen and Paulo F. Butzen

Chips 2026, 5(1), 2; https://doi.org/10.3390/chips5010002 - 13 Jan 2026

Abstract

Semiconductor technologies are susceptible to radiation effects. The particle incidence in susceptible areas of an integrated circuit (IC) can generate physical interactions capable of producing errors. This paper predicts the IC cross sections for Single Event Effects. The cross section is a metric

[...] Read more.

Semiconductor technologies are susceptible to radiation effects. The particle incidence in susceptible areas of an integrated circuit (IC) can generate physical interactions capable of producing errors. This paper predicts the IC cross sections for Single Event Effects. The cross section is a metric that provides an IC’s susceptibility to radiation. It deals with particle source interaction and physical design volumes. This work evaluates the IC cross section, exploring the physical design characteristics of susceptible regions in logic gates. It explores particles with low LET, identifying the charge collection areas. Also, the heavy ions are used to evaluate the critical cross section range. Distinct benchmark circuits were simulated to characterize sensitivity trends. The influence of circuit input conditions along with cells’ susceptibility reveals significant findings. The results indicate a difference up to ten times between low- and high-energy particles. Consequently, predicting the IC cross section at an early stage of the design flow is essential, especially for electronics devices used in radiation environments.

Full article

(This article belongs to the Special Issue New Research in Microelectronics and Electronics)

►▼

Show Figures

Figure 1

Open AccessArticle

Electro-Physical Model of Amorphous Silicon Junction Field-Effect Transistors for Energy-Efficient Sensor Interfaces in Lab-on-Chip Platforms

by

Nicola Lovecchio, Giulia Petrucci, Fabio Cappelli, Martina Baldini, Vincenzo Ferrara, Augusto Nascetti, Giampiero de Cesare and Domenico Caputo

Chips 2026, 5(1), 1; https://doi.org/10.3390/chips5010001 - 12 Jan 2026

Abstract

►▼

Show Figures

This work presents an advanced electro-physical model for hydrogenated amorphous silicon (a-Si:H) Junction Field Effect Transistors (JFETs) to enable the design of devices with energy-efficient analog interface building blocks for Lab-on-Chip (LoC) systems. The presence of this device can support monolithic integration with

[...] Read more.

This work presents an advanced electro-physical model for hydrogenated amorphous silicon (a-Si:H) Junction Field Effect Transistors (JFETs) to enable the design of devices with energy-efficient analog interface building blocks for Lab-on-Chip (LoC) systems. The presence of this device can support monolithic integration with thin-film sensors and circuit-level design through a validated compact formulation. The model accurately describes the behavior of a-Si:H JFETs addressing key physical phenomena, such as the channel thickness dependence on the gate-source voltage when the channel approaches full depletion. A comprehensive framework was developed, integrating experimental data and mathematical refinements to ensure robust predictions of JFET performance across operating regimes, including the transition toward full depletion and the associated current-limiting behavior. The model was validated through a broad set of fabricated devices, demonstrating excellent agreement with experimental data in both the linear and saturation regions. Specifically, the validation was carried out at 25 °C on 15 fabricated JFET configurations (12 nominally identical devices per configuration), using the mean characteristics of 9 devices with standard-deviation error bars. In the investigated bias range, the devices operate in a sub-µA regime (up to several hundred nA), which naturally supports µW-level dissipation for low-power interfaces. This work provides a compact, experimentally validated modeling basis for the design and optimization of a-Si:H JFET-based LoC front-end/readout circuits within technology-constrained and energy-efficient operating conditions.

Full article

Graphical abstract

Open AccessArticle

Efficient mmWave PA in 90 nm CMOS: Stacked-Inverter Topology, L/T Matching, and EM-Validated Results

by

Nusrat Jahan, Ramisha Anan and Jannatul Maua Nazia

Chips 2025, 4(4), 52; https://doi.org/10.3390/chips4040052 - 15 Dec 2025

Abstract

In this study, we present the design and analysis of a stacked inverter-based millimeter-wave (mmWave) power amplifier (PA) in 90 nm CMOS-targeting wideband Q-band operation. The PA employs two PMOS and two NMOS devices in a fully stacked inverter topology to distribute device

[...] Read more.

In this study, we present the design and analysis of a stacked inverter-based millimeter-wave (mmWave) power amplifier (PA) in 90 nm CMOS-targeting wideband Q-band operation. The PA employs two PMOS and two NMOS devices in a fully stacked inverter topology to distribute device stress, remove the need for an RF choke, and increase effective transconductance while preserving compact layout. A resistor ladder biases the stack near

(This article belongs to the Special Issue IC Design Techniques for Power/Energy-Constrained Applications)

►▼

Show Figures

Figure 1

Open AccessArticle

Optimizing Test Pattern Compaction with Boolean Satisfiability Attack

by

Yadi Zhong

Chips 2025, 4(4), 51; https://doi.org/10.3390/chips4040051 - 6 Dec 2025

Abstract

►▼

Show Figures

Test time per chip plays an essential role in manufacturing tests. Keeping a low number of test patterns becomes one of the prime objectives in concurrence with achieving the desired fault coverage. Unfortunately, finding an optimum set is an NP-hard problem. Today’s commercial

[...] Read more.

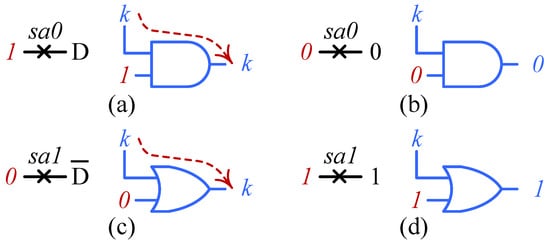

Test time per chip plays an essential role in manufacturing tests. Keeping a low number of test patterns becomes one of the prime objectives in concurrence with achieving the desired fault coverage. Unfortunately, finding an optimum set is an NP-hard problem. Today’s commercial ATPG tools have significantly reduced the number of test patterns to achieve a high fault coverage. However, there is still a huge gap for reducing the total pattern count, equivalent to minimizing test costs in the production phase. In this paper, we propose two novel methods to lower the test pattern count to detect all stuck-at faults in a circuit with the same or higher fault coverage as in the commercial ATPG tool, e.g., TetraMAX II. The first approach begins by applying a small set of random patterns to solve easy-to-detect faults. The remaining faults are detected by the SAT-based attack on logic locking with converting all the remaining faults into one locked circuit. Each stuck-at fault is modeled with its equivalent key gate. The second approach selects the first few patterns generated by the ATPG tool and applies the SAT attack of logic locking to determine the test patterns for detecting the undetected faults. By exploiting the overall linear iteration complexity and the exponential removal of incorrect key combinations per each SAT attack iteration, it is feasible to significantly reduce the total pattern count while maintaining the same or higher fault coverage as the ATPG counterpart. We demonstrate the effectiveness of both approaches and show that we are able to achieve a more compact test pattern set compared to a commercial ATPG tool.

Full article

Figure 1

Open AccessCommunication

The Design of a 140 GHz 28 nm CMOS Vector-Sum Phase Shifter Based on Gilbert Cell and Current-Steering Amplifiers

by

Junyung Cho, Jung-Hyun Lee and M. Kim

Chips 2025, 4(4), 50; https://doi.org/10.3390/chips4040050 - 13 Nov 2025

Abstract

This paper presents the design of a 140 GHz vector-sum phase shifter in a 28 nm CMOS process. Two variable-gain amplifiers—Gilbert cell and current-steering amplifiers—are investigated and compared. The Gilbert cell-based phase shifter controls the tail current source in a common-source amplifier. However,

[...] Read more.

This paper presents the design of a 140 GHz vector-sum phase shifter in a 28 nm CMOS process. Two variable-gain amplifiers—Gilbert cell and current-steering amplifiers—are investigated and compared. The Gilbert cell-based phase shifter controls the tail current source in a common-source amplifier. However, this configuration exhibits insufficient gain at D-band frequencies. To address this issue, we designed a current-steering variable-gain amplifier in cascode form to improve the gain performance. I/Q signals are generated by Marchand baluns and Lange couplers, and a 13-bit digital-to-analog converter enables fine bias control. Simulation results show that the current-steering phase shifter achieves up to a 4.4 dB higher gain than the Gilbert cell-based phase shifter, with an RMS gain error below 1.3 dB and an RMS phase error below 4.8° across 129–144 GHz.

Full article

(This article belongs to the Special Issue IC Design Techniques for Power/Energy-Constrained Applications)

►▼

Show Figures

Figure 1

Open AccessArticle

A Passage-Based Fault-Tolerant Routing Method for 3D Mesh NoCs Without Creating Faulty Regions

by

Yota Kurokawa and Masaru Fukushi

Chips 2025, 4(4), 49; https://doi.org/10.3390/chips4040049 - 11 Nov 2025

Abstract

►▼

Show Figures

This paper proposes a novel fault-tolerant routing method without creating faulty regions for 3D mesh Network-on-Chips (NoCs). Most conventional methods create faulty regions containing faulty nodes and route packets around them to reach the destinations. However, the creation of faulty regions results in

[...] Read more.

This paper proposes a novel fault-tolerant routing method without creating faulty regions for 3D mesh Network-on-Chips (NoCs). Most conventional methods create faulty regions containing faulty nodes and route packets around them to reach the destinations. However, the creation of faulty regions results in low communication performance and low node utilization. To overcome the two problems, the proposed method does not create faulty regions based on the idea of predefining paths in the absence of shortest paths while allowing the passage of faulty nodes. Simulation results show that, compared with conventional methods, the proposed method reduces average latency by about 44.5% and improves node utilization rate by about 41.2% for 3D mesh NoCs of

Figure 1

Open AccessArticle

Exploring Accelerated Aging Stress for Physical Unclonable Function Self-Corruption

by

Eric Hunt-Schroeder and Tian Xia

Chips 2025, 4(4), 48; https://doi.org/10.3390/chips4040048 - 11 Nov 2025

Abstract

Silicon-Based Physical Unclonable Functions (PUFs) exploit inherent manufacturing variations to produce a unique, random, and ideally unclonable secret key. As electronic devices are decommissioned and sent for End of Life (EOL) recycling, the encrypted critical program information remains within the device. However, conventional

[...] Read more.

Silicon-Based Physical Unclonable Functions (PUFs) exploit inherent manufacturing variations to produce a unique, random, and ideally unclonable secret key. As electronic devices are decommissioned and sent for End of Life (EOL) recycling, the encrypted critical program information remains within the device. However, conventional PUFs remain vulnerable to invasive attacks and reverse engineering that with sufficient time, resources, and effort can enable an adversary to bypass the security enclave of the system and extract this secret data. Recent research has started to explore techniques to respond to tamper attempts using electromigration (EM) and time-dependent dielectric breakdown (TDDB) to the PUF entropy source, preventing future authentication attempts with well-known semiconductor reliability failure mechanisms. This work presents a Pre-Amplifier Physical Unclonable Function (Pre-Amp PUF) with a self-corruption function designed and manufactured in a 3 nm FinFET technology. This PUF can perform a destructive read operation as an EOL anti-counterfeit measure against recycled and reused electronics. The destructive read utilizes an accelerated aging technique that exploits both Hot Carrier Injection (HCI) and Bias Temperature Instability (BTI) degradations directly at the PUF entropy source bitcell data. This work demonstrates a silicon proven ability to irreversibly corrupt the encryption key, invalidating the PUF key, and blocking future authentication attempts. By utilizing HCI and BTI aging effects rather than physical damage a PUF that can self-corrupt its own key without being detectable with imaging techniques is demonstrated for the first time. A feedback loop enables corruption of up to ~30% of the PUF entropy source, which is approximately 3× more data corruption than the prior state of the art self-corrupting PUF. Our technique reuses on-chip stable (repeatable) PUF bitcells identifying circuitry and thereby minimizes the area overhead to support this differentiated feature.

Full article

(This article belongs to the Special Issue Emerging Issues in Hardware and IC System Security)

►▼

Show Figures

Figure 1

Open AccessArticle

Triggered Hardware Trojan Detection in IP Cores for Ensuring Safety in Cyber Physical Systems

by

Mahfuzur Rahman Talukder, Md. Eftekhar Alam, Abu Monsur Mohammah Fahim and Fakir Sharif Hossain

Chips 2025, 4(4), 47; https://doi.org/10.3390/chips4040047 - 11 Nov 2025

Abstract

Cyber physical systems (CPSs) increasingly depend on complex hardware IP cores to perform critical functions. However, triggered hardware Trojans’ stealthy, malicious modifications activated under rare conditions pose significant threats to the safety and reliability of these systems. This research paper introduces a novel

[...] Read more.

Cyber physical systems (CPSs) increasingly depend on complex hardware IP cores to perform critical functions. However, triggered hardware Trojans’ stealthy, malicious modifications activated under rare conditions pose significant threats to the safety and reliability of these systems. This research paper introduces a novel detection framework that integrates multi-modal side-channel analysis with trigger-aware machine learning to identify Trojans embedded within IP cores. A lightweight runtime monitoring mechanism enables real-time Trojan detection while adhering to the stringent safety constraints of CPSs. To further strengthen resilience, cryptographic integrity verification and dynamic mitigation through partial reconfiguration are incorporated. Experimental validation on two representative IP cores, AES-128 and RS232, demonstrates the framework’s effectiveness by achieving high detection accuracy (over 96%) with minimal hardware overhead (<3% LUT utilization) and latency increase of 4.95%. It can also be seen that our trigger-aware methodology more than doubles the toggling probability of rare Trojan trigger nets compared to conventional approaches. Furthermore, results from FPGA prototypes and standard Trojan benchmarks confirm the effectiveness of the proposed framework, and the proposed approach achieves high detection accuracy with minimal resource and performance penalties. This work advances the state of the art in securing CPS hardware against Trojan-based attacks.

Full article

(This article belongs to the Special Issue Emerging Issues in Hardware and IC System Security)

►▼

Show Figures

Figure 1

Open AccessArticle

Wideband CMOS Variable Gain Low-Noise Amplifier with Integrated Attenuator for C-Band Wireless Body Area Networks

by

Nusrat Jahan, Nishat Anjumane Salsabila, Susmita Barua, Mohammad Mahmudul Hasan Tareq, Quazi Delwar Hossain, Ramisha Anan and Jannatul Maua Nazia

Chips 2025, 4(4), 46; https://doi.org/10.3390/chips4040046 - 3 Nov 2025

Cited by 1

Abstract

This work presents a wideband variable gain low-noise amplifier (VGA-LNA) specifically engineered for medical systems operating in the C frequency band, which require the substantial amplification of low-intensity signals. The proposed design integrates a low-noise attenuator with a low-noise amplifier (LNA), fabricated using

[...] Read more.

This work presents a wideband variable gain low-noise amplifier (VGA-LNA) specifically engineered for medical systems operating in the C frequency band, which require the substantial amplification of low-intensity signals. The proposed design integrates a low-noise attenuator with a low-noise amplifier (LNA), fabricated using 90 nm CMOS technology and leveraging a combined common-source and common-gate topology. The integrated LNA achieved a notable power gain of 29 dB across a broad bandwidth of 2 GHz (6.4–8.4 GHz), maintaining an average noise figure (NF) below 3.14 dB. The design ensures superior impedance matching, demonstrated by reflection coefficients of S11 < −18.14 dB and S22 < −20.23 dB. Additionally, the amplifier exhibits a third-order input intercept point (IIP3) of 21.15 dBm while consuming only 83 mW from a 1.2 V supply voltage. A low-noise attenuator was incorporated at the input side to enable effective gain control through a digitally controlled variable gain, with step sizes ranging from 0.4 to 3.3 dB. This configuration enables a dynamic range of the transmission coefficient (|S21|) from 16 dB to 23 dB, adjustable by 0.4 dB to 3.3 dB with a trade-off in an NF maintained at 6 dB. The VGA-LNA demonstrates exceptional potential for integration into wireless body area networks (WBANs), balancing flexible gain control with stringent performance metrics.

Full article

(This article belongs to the Special Issue New Research in Microelectronics and Electronics)

►▼

Show Figures

Figure 1

Open AccessArticle

Layout-Aware Analysis of Transistor Fingering Effects on Hysteresis and Reliability in CMOS Schmitt Triggers

by

Liron Cohen and Emmanuel Bender

Chips 2025, 4(4), 45; https://doi.org/10.3390/chips4040045 - 1 Nov 2025

Abstract

►▼

Show Figures

Schmitt Triggers are essential building blocks in noise-resilient systems and are useful in managing switching behavior in low-power designs. Yet, as CMOS technologies scale down, their designs become increasingly challenging. This paper presents a comprehensive investigation into the performance and reliability of multiple

[...] Read more.

Schmitt Triggers are essential building blocks in noise-resilient systems and are useful in managing switching behavior in low-power designs. Yet, as CMOS technologies scale down, their designs become increasingly challenging. This paper presents a comprehensive investigation into the performance and reliability of multiple Schmitt Trigger topologies across two CMOS technology nodes (180 nm and 45 nm), with a particular focus on transistor sizing and layout optimization through multi-finger transistor structures. A series of pre-layout and post-layout simulations reveal that fingered implementations significantly enhance hysteresis robustness, switching speed, and delay consistency in PVT variations. Notably, post-layout results in 45 nm technology demonstrate remarkable improvements in both speed and power efficiency. This highlights the inadequacy of schematic-level models to predict the true behavior of fingered transistor configurations. Additionally, we explored the implications of finger designs on reliability concerns including electromigration and IR drop to determine the tradeoff between interconnect reliability optimization and internal routing. The findings establish practical design guidelines for optimizing number of fingers based on device width and technology node, offering new insights into layout-aware Schmitt Trigger design for high-performance and area-constrained applications.

Full article

Figure 1

Open AccessReview

Comparative Review of Multicore Architectures: Intel, AMD, and ARM in the Modern Computing Era

by

Raghad H. AlShekh, Shefa A. Dawwd and Farah N. Qassabbashi

Chips 2025, 4(4), 44; https://doi.org/10.3390/chips4040044 - 27 Oct 2025

Cited by 2

Abstract

Every element of our contemporary lives has changed as a result of the widespread use of computing infrastructure and information technology in daily life. Less focus has been placed on the hardware components that underpin the computing revolution, despite the fact that its

[...] Read more.

Every element of our contemporary lives has changed as a result of the widespread use of computing infrastructure and information technology in daily life. Less focus has been placed on the hardware components that underpin the computing revolution, despite the fact that its effects on software applications have been the most obvious. The computer chip is the most basic component of computer hardware and powers all digital devices. Every gadget, including mainframes, laptops, cellphones, tablets, desktop PCs, and supercomputers, is powered by different computer chips. Although there are many different types of these chips, the biggest producers in this field are AMD (Advanced Micro Devices), Intel, and ARM (Advanced RISC Machines). These companies make processors for both consumer and business markets. Users have compared their products based on a number of factors, including pricing, cache and memory, approaches, etc. This paper provides a comprehensive comparative analysis of Intel, AMD, and ARM processors, focusing on their architectural characteristics and performance within the context of burgeoning artificial intelligence applications. The detailed architectural features, performance evaluation for AI workloads, a comparison of power efficiency and cost, and analysis for current market trends are presented. By thoroughly examining core architectural elements and key performance factors, this work provides valuable insights for users and developers to seek optimal processor choices to maximize AI tool utilization in the contemporary era.

Full article

(This article belongs to the Special Issue IC Design Techniques for Power/Energy-Constrained Applications)

►▼

Show Figures

Figure 1

Open AccessArticle

Hardware-Described Nanoscale Carry-Save Adder in Quantum-Dot Cellular Automata: An Optimised Design and Evaluation Framework

by

Mohammad Abdullah-Al-Shafi

Chips 2025, 4(4), 43; https://doi.org/10.3390/chips4040043 - 15 Oct 2025

Abstract

►▼

Show Figures

Quantum-dot Cellular Automata (QCA) technology has emerged as a promising approach for constructing nanoscale digital circuits, offering notable advantages such as minimal power consumption, rapid processing speeds, and highly compact layouts. Traditional CMOS technology faces significant challenges at the nanoscale, including reduced gate

[...] Read more.

Quantum-dot Cellular Automata (QCA) technology has emerged as a promising approach for constructing nanoscale digital circuits, offering notable advantages such as minimal power consumption, rapid processing speeds, and highly compact layouts. Traditional CMOS technology faces significant challenges at the nanoscale, including reduced gate control and increased current leakage. QCA, on the other hand, provides a robust platform for building next-generation digital systems. In this study, a unique single-layer QCA-based Full-Adder (QCAFA) and Carry-Save Adder (CSA) architecture is developed to enhance key performance factors such as delay, space, cost, and cell block count. The outlined designs demonstrate superior efficiency compared to state-of-the-art single-layer and multilayer QCA designs. Simulation results conducted with QCADesigner 2.0.3 and QCADesigner-E reveal that the proposed architecture achieves a substantial 34.29% diminution in total cells compared with the recent design, utilising only 46 QCA cells. Similarly, for the CSA, the proposed design attains an 18.62% reduction in cell count compared with its best counterpart, utilising only 424 QCA cell blocks. To enhance design credibility and hardware relevance, this research additionally models and validates the architecture using the Verilog hardware description language (HDL Version 12.0), thereby bridging the gap between nano-architecture and HDL-based prototyping. Simulation results obtained through QCADesigner confirm the correctness and stability of the QCA layout, while HDL simulation verifies functional equivalence at the behavioural and structural levels. The proposed designs not only enhance speed and reduce energy consumption but also offer better manufacturability. The findings of this study highlight the potential of QCA technology as a feasible substitute for CMOS for high-performance digital arithmetic circuits at the nanoscale.

Full article

Figure 1

Open AccessPerspective

A Perspective on Analog and Mixed-Signal IC Design Amid Semiconductor Paradigm Shifts

by

Gabriele Manganaro

Chips 2025, 4(4), 42; https://doi.org/10.3390/chips4040042 - 9 Oct 2025

Abstract

►▼

Show Figures

This position paper extends the author’s keynote address from the 2024 IEEE European Solid-State Electronics Research Conference, offering a perspective on effective strategies for the advancement of analog and mixed-signal (AMS) integrated circuit (IC) design. It is argued that traditional methodologies, characterized by

[...] Read more.

This position paper extends the author’s keynote address from the 2024 IEEE European Solid-State Electronics Research Conference, offering a perspective on effective strategies for the advancement of analog and mixed-signal (AMS) integrated circuit (IC) design. It is argued that traditional methodologies, characterized by their focus on transistor-level optimization within individual sub-blocks, are insufficient for satisfying the stringent performance and power consumption demands of contemporary information and communication technologies (ICT), especially in the context of expanding AI applications. Consequently, a paradigm shift is necessary, emphasizing “full-stack” solutions that prioritize comprehensive system-level analysis and aim to minimize physical resources and reduce complexity by innovating across the established boundaries of design abstraction levels. Building on prior work, this manuscript offers a more thorough justification for the proposed full-stack analog design methodology, supported by broader evidence and more comprehensive discussion. It also identifies key considerations regarding EDA and workforce development as topics for future work.

Full article

Figure 1

Highly Accessed Articles

Latest Books

E-Mail Alert

News

Topics

Topic in

Applied Sciences, Electronics, Energies, Sensors, Chips, JLPEA

VLSI-Based Sequential Devices in Cyber-Physical Systems

Topic Editors: Alexander Barkalov, Larysa Titarenko, Kazimierz KrzywickiDeadline: 30 April 2026

Topic in

Electronics, Sensors, Micromachines, JLPEA, Semiconductors and Heterogeneous Integration, Chips, Hardware, Encyclopedia

Edge AI: From Intelligent Sensing to AI-Dedicated Hardware

Topic Editors: Laura Falaschetti, Giorgio BiagettiDeadline: 31 December 2026

Topic in

Energies, Micromachines, Chips, Entropy, Processes

Advances in Liquid Cooling Technologies for High-Power Chips and Data Centers

Topic Editors: Mengjie Song, Tomasz MuszyńskiDeadline: 30 April 2027

Conferences

Special Issues

Special Issue in

Chips

Silicon Photonic Integrated Circuits: Advancements and Challenges

Guest Editors: Stanley Cheung, Yingtao HuDeadline: 30 June 2026

Special Issue in

Chips

IC Design Techniques for Power/Energy-Constrained Applications

Guest Editors: Andrea Ballo, Orazio AielloDeadline: 31 July 2026

Special Issue in

Chips

New Research in Microelectronics and Electronics

Guest Editors: Gianluca Giustolisi, Elisabetta MoiselloDeadline: 30 September 2026

Special Issue in

Chips

Magnetoresistive Random-Access Memory (MRAM): Present and Future

Guest Editor: Cheng WangDeadline: 31 October 2026