1. Introduction

Wireless communication systems have evolved rapidly and are now among the most important aspects of daily life. Various wireless standards, such as Bluetooth, Wi-Fi, GPS, and 2G/3G/4G/5G cellular systems, use different frequency bands that require a transceiver that can operate with robust performance over a wide range of frequencies, while maintaining low power consumption, low occupied volume, good noise performance, and low cost [

1].

Low-noise amplifier (LNA) as the first active block of the receiver system determines the receiver bandwidth and noise figure (NF) [

2]. Trade-offs between input matching, NF, gain, bandwidth, and linearity should be considered in the design process. Single-ended LNAs lack sufficient power supply rejection and have limited second-order distortion performance. Therefore, differential signaling is preferable because of its robustness against power supply, substrate noise, and second-order distortion [

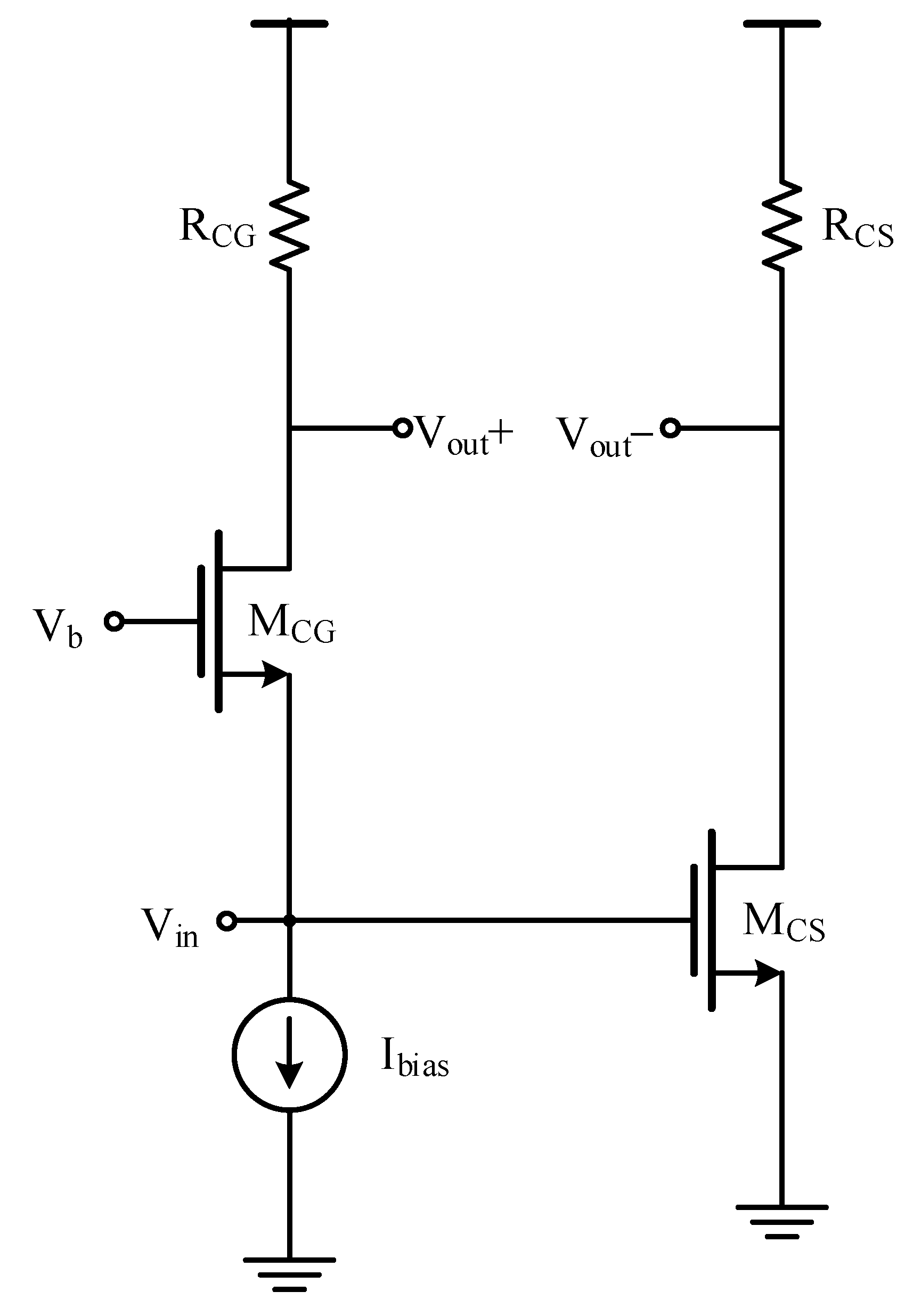

3]. Single-to-differential conversion (balun) is required to convert a single-ended RF signal into a differential signal. However, off-chip passive baluns are typically lossy and narrowband; thus, several baluns are needed to accommodate wideband operation, which increases the overall cost. A well-known topology for broadband applications employs a common-gate (CG) common-source (CS) pair as an active balun. This topology provides high power gain and the ability to cancel thermal noise and distortion over wideband frequency ranges [

3,

4].

Previous studies on CG-CS topology [

3,

4,

5,

6,

7,

8,

9,

10,

11,

12] show that a balanced condition between the CG and CS stages is essential for the noise canceling condition. Furthermore, scaling between the transconductance of the CS stage (

) and the transconductance of the CG stage (

) also affects the NF performance [

3]. To satisfy input matching,

must be 20

mS. Thus, the drawback of this topology is its large power consumption, because

needs to be significantly large to achieve better NF performance. Another critical issue is that the parasitic capacitances cause gain and phase imbalances due to the active circuit components. Previous work in [

4] utilizes negative feedback from the source node of the cascoded CS stage to the gate of the CG stage. The voltage gain of the cascode CS stage is utilized to boost the

. The work in [

5] improved the overall power consumption by employing negative feedback from the output of the CS stage to the gate of the CG stage, resulting in a higher effective

, reduced power consumption, and smaller size. Gain and phase imbalances can also be compensated using a passive capacitor between differential outputs. This technique is suitable for low-voltage applications, but its drawback is the headroom of the amplifier. Furthermore, the CS stage consumes a large amount of power because

needs to be high for better noise performance. Other critical works in [

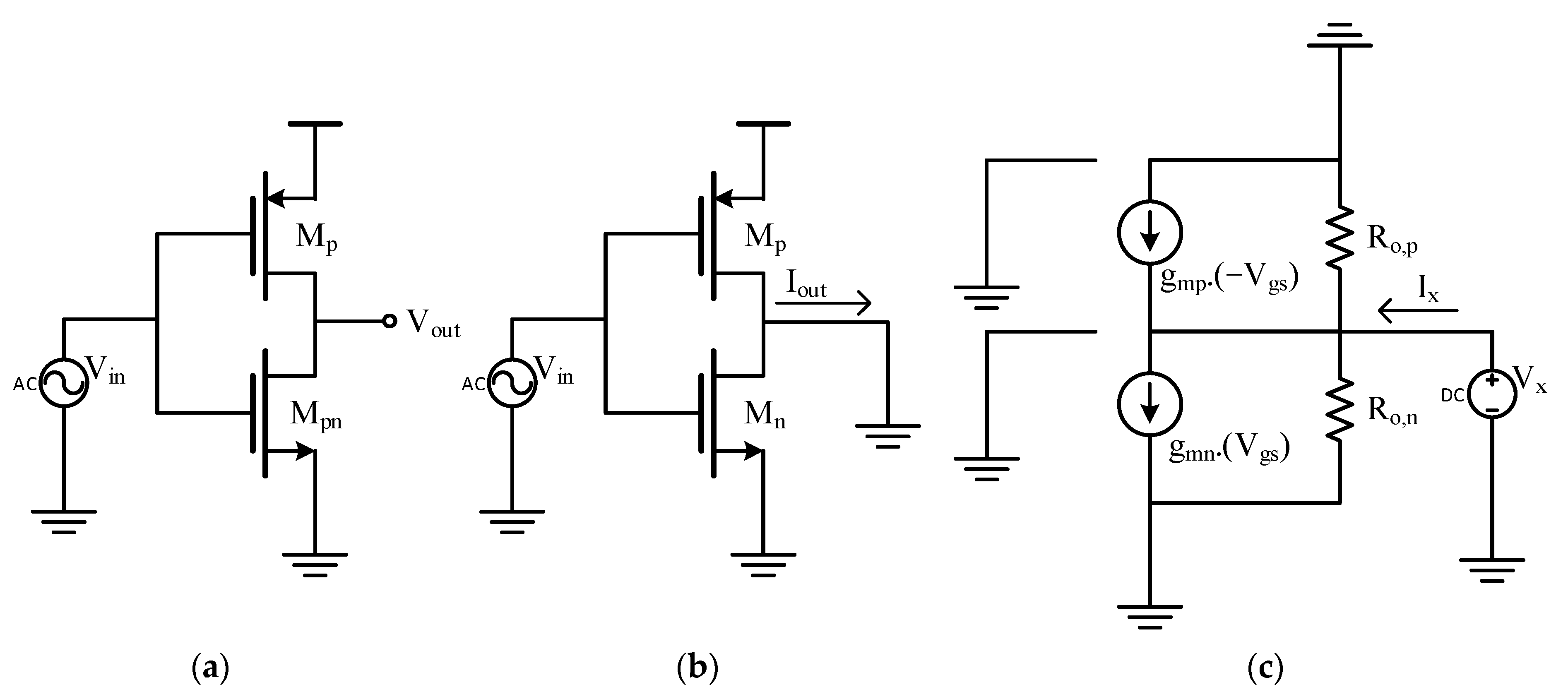

6] and [

8] proposed a balun CG-CS paired with the current reuse to further increase

efficiency but the trade-off between gain and bandwidth showed a marginal improvement factor. Authors in [

12] proposed a CG-CS pair with the current reuse to decrease the power consumption and to improve the noise contribution of the CS stage as well, however the proposed design is just for a single-ended LNA and is not suitable for single to differential conversion.

This paper proposes a balun-LNA with CG-CS topology employing negative feedback on the CG stage and current reuse for the CS stage. Negative feedback utilizes the gain of the CS stage to increase for better input matching and to satisfy wideband operation. Current reuse is applied to increase the overall by adding a complementary transistor within the CS stage, resulting in higher transconductance scaling for better NF performance. Both negative feedback and current reuse keep the power consumption for the overall stages of the CG-CS topology low.

The remainder of this paper is organized as follows.

Section 2 reviews the CG-CS active-balun topologies and their general properties. The analysis and properties of the current reuse technique are described in

Section 3. The proposed LNA is described in

Section 4, followed by a thorough analysis of its input matching, gain, and noise.

Section 5 presents the simulation results of the proposed LNA, and conclusions are presented in

Section 6.

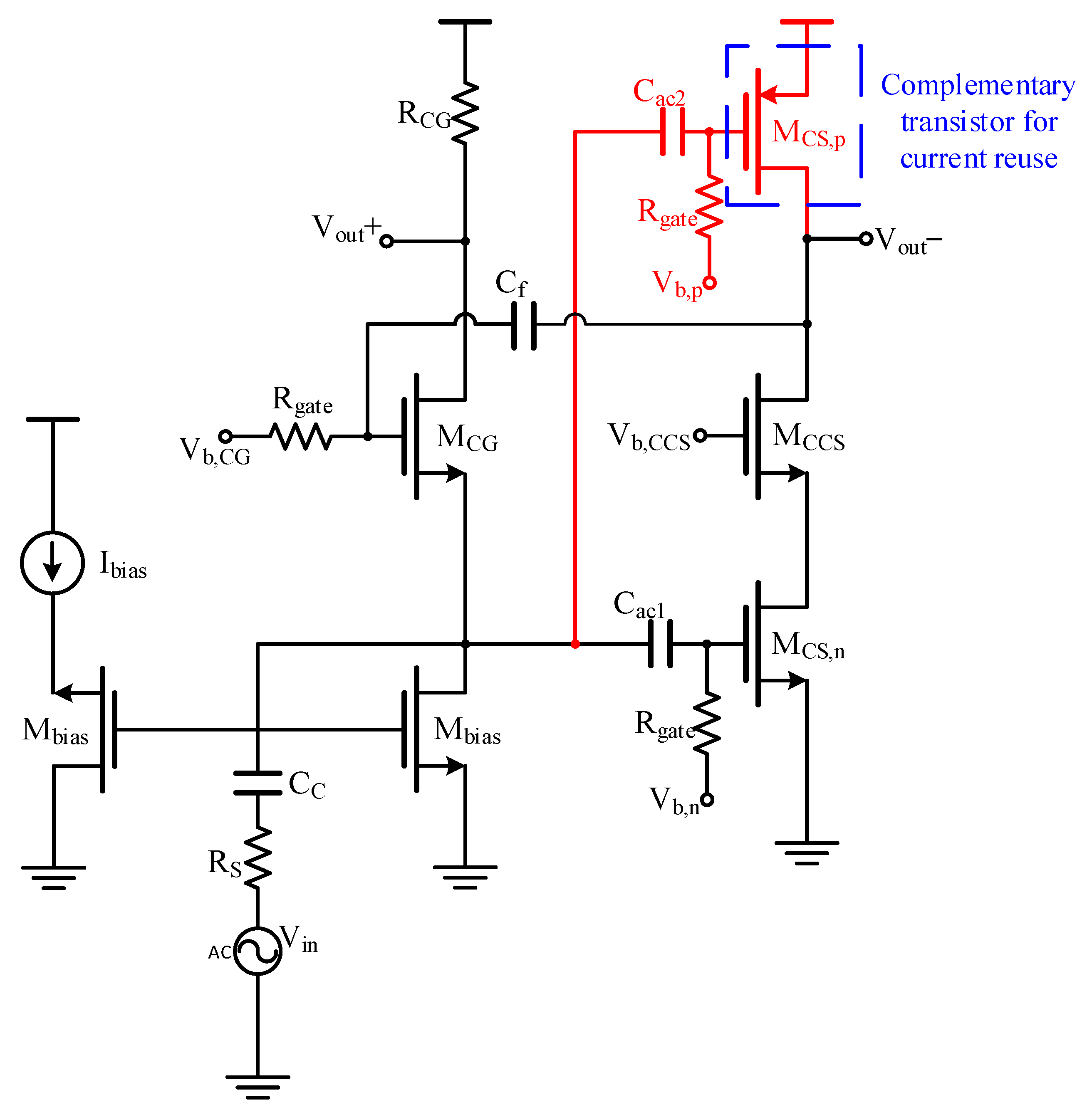

4. Wideband Balun-LNA with Feedback and Current Reuse Technique

Figure 3 shows the proposed wideband balun-LNA with the negative feedback for the CG stage and the current reuse technique for the CS stage. The CG stage provides input-matching and non-inverting signals at the CG output, whereas in the CS stage, the signal phase is inverted by

. The output of the CS stage is fed back to the gate of the CG stage to increase the effective

by the gain of the CS stage. Thus, the negative feedback connection relaxes the input matching condition without increasing the current of the CG stage or increasing the transistor size for a higher

. In contrast, the CS stage employs complementary CMOS transistors using current reuse. The gain of each stage is

where

and

are the gains of the CS and CG stages, respectively. Note that in (12), the CS stage output resistance

is determined by the transconductance of the cascoded NMOS transistor

and its output resistance

) in parallel with the output resistance of the PMOS transistor

.

can be approximated as

because the cascoded NMOS transistor produces a much larger resistance at the CS output stage. The PMOS and NMOS transistors share the same current; therefore, the overall

is effectively doubled.

4.1. Input Matching

Note that in (11), the CG stage transconductance is increased by a factor of

due to the negative feedback employed from the CS stage output to the CG stage gate. Therefore, the input impedance of the proposed LNA can be approximated as

It is clear from Equation (13) that the required for the matching condition is reduced significantly, allowing the CG stage to have lower current consumption and size. The parasitic capacitance , which is determined by the input pad, transistor size of the CG and CS stages, and bias transistors, is also reduced owing to the proposed scheme.

4.2. Noise Analysis

The important property of the CG-CS balun-LNA topology is that the thermal noise of the CG transistor is fully canceled when the gains of the CG and CS stages are balanced. The NF of the proposed LNA employing feedback and current reuse is

where

is the differential gain, which can be expressed as

The second term is the noise contribution owing to the CG stage, and its contribution is fully canceled when the balanced gain condition is met. The third term is the noise contribution due to the CS stage, and its noise is spread among the PMOS and NMOS transistors, whereas the last term is the noise due to the CG stage load resistance. Equation (14) does not consider the current mirror noise contributions, which can be significantly smaller with the feedback scheme [

4].

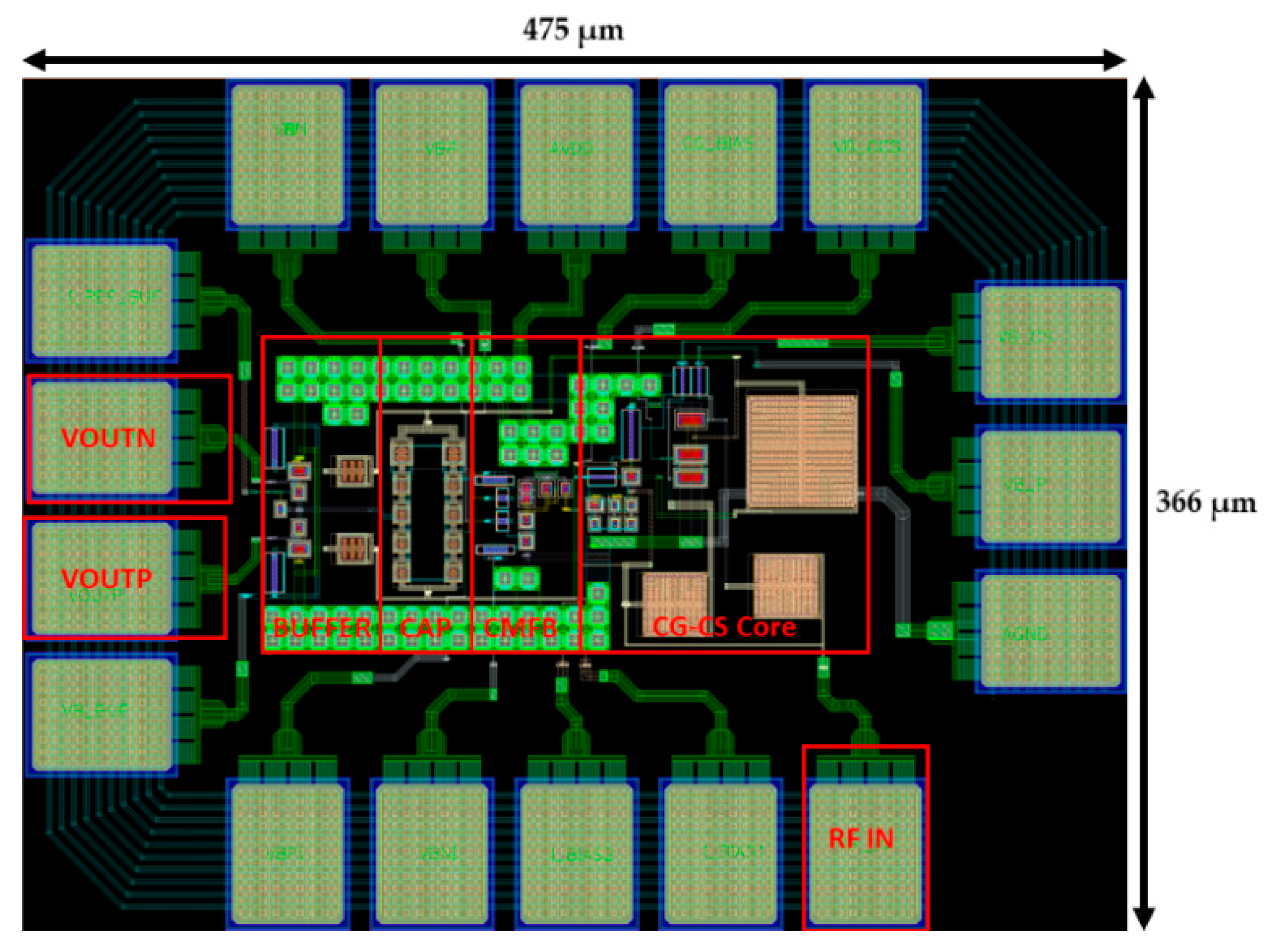

5. Simulation Results

The balun-LNA was designed using TSMC 65 nm technology. Its device dimensions and bias points are indicated in

Table 1. The balun-LNA layout is illustrated in

Figure 4. The total area of the chip is 475 × 366 μm, including the balun-LNA core, common-mode feedback for gain and phase imbalance compensation, buffer (source follower) to interface balun-LNA outputs to off-chip ports, and pads. The active area of the LNA core is only 150 × 150 μm. The PMOS and NMOS CS stages are designed to match each other such that the second-order distortion produced by the stage is eliminated. The CG stage is designed to match a 50 Ω input impedance (

. As shown in

Table 1, with a given transistor size, the CG stage only consumes 0.375 mA of current, in contrast with the conventional topology, which requires approximately 4 mA of current to obtain the same transconductance [

2]. CS stage consumes the largest current in the overall stage by 3.7 mA. With the given size and bias condition, the transconductance of the CS stage is 2.5 times larger than the CG stage. The current reuse technique improved the

efficiency of the CS stage. Both positive output and negative output are sensed by common-mode feedback to ensure the stable gain and phase imbalance for robustness operation across PVT variation.

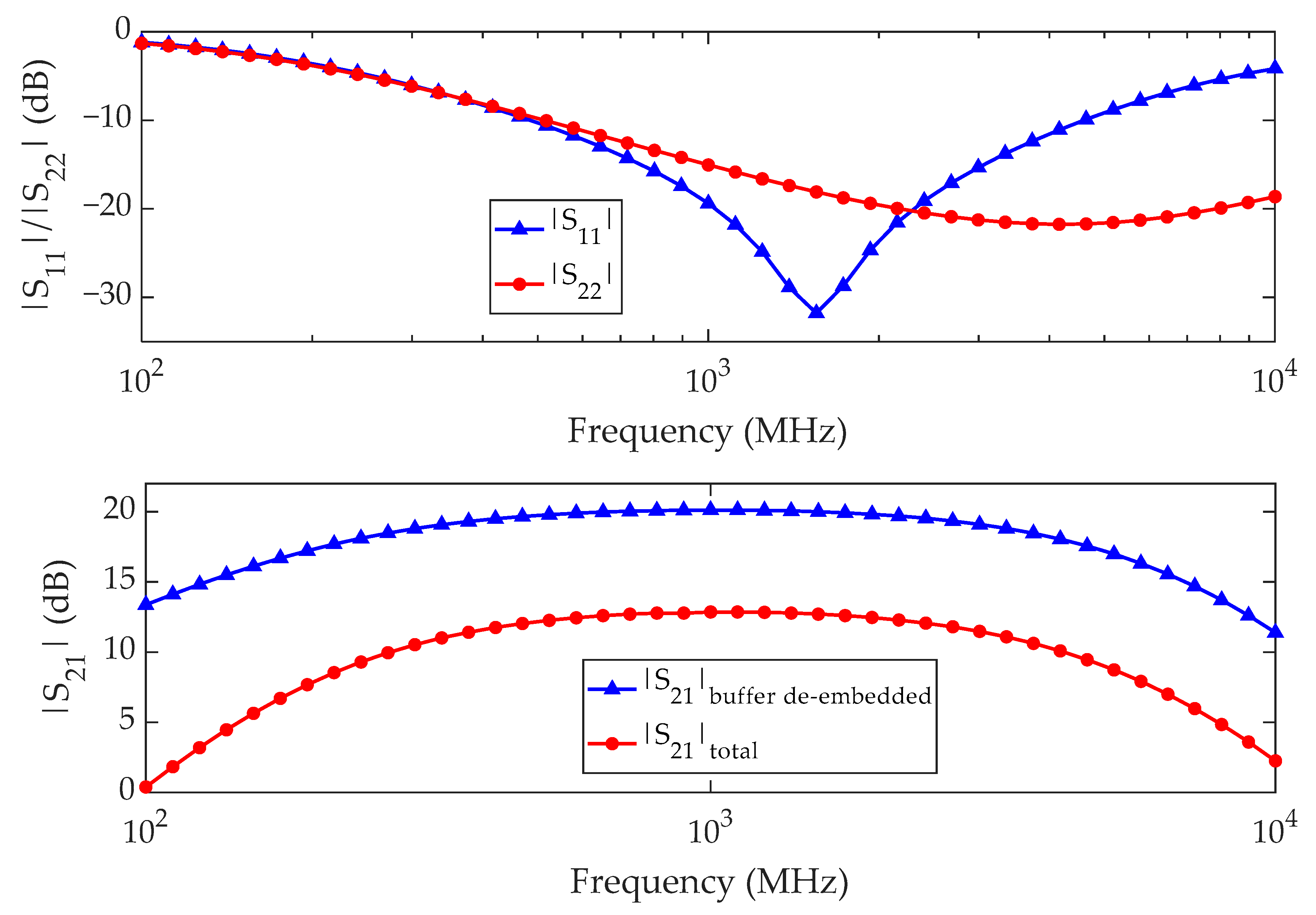

Figure 5 shows a post-layout simulation of the input/output impedance matching performance

) and power gain

) of the total circuit and core, where the effect of the buffer is de-embedded. The simulated

and

values are well below −10 dB over a frequency range of 0.5–5 GHz. The maximum power gain of the proposed Balun-LNA is 20 dB and the maximum power gain with the effect of the buffer is 13 dB, including the intrinsic 6 dB loss from the output matching. The buffer was designed with a source follower architecture and consumes 4 mA of current, which can be avoided in the receiver front end, where the LNA is driving the mixer on-chip [

1].

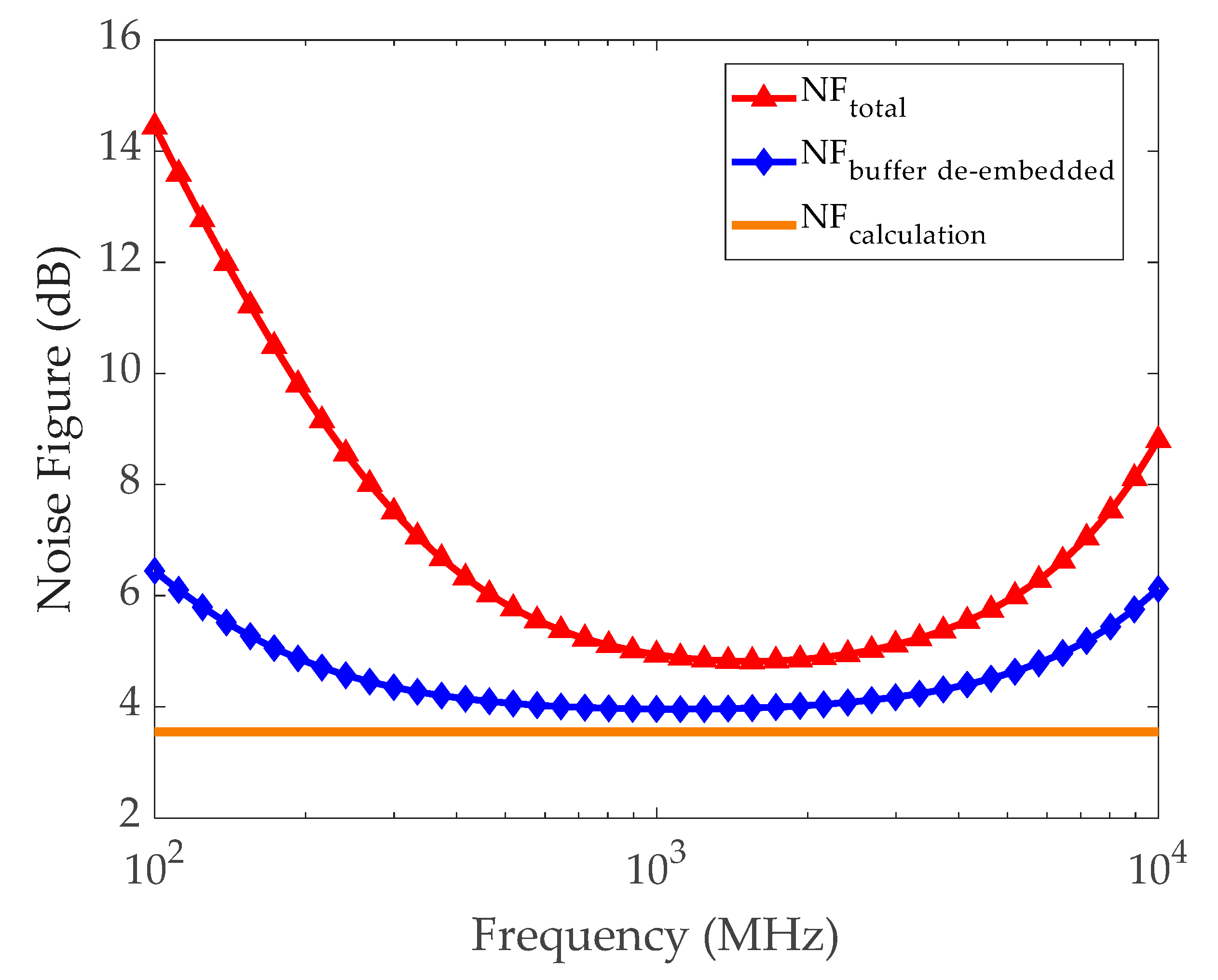

Figure 6 shows the NF of the entire circuit (LNA core and buffer) and LNA core while de-embedding the buffer contribution, and the NF calculated from Equation (14) and designed device parameters is also shown. The calculated NF is 3.55 dB, while the LNA core shows an NF of 4 dB across the range of 0.5–2 GHz. The NF is increased in the post-layout simulation owing to the contribution of parasitic resistance, bias (current mirror), and other passive devices, such as R

Gate, which are not included in Equation (14). The CS stage provides the highest noise contribution for the LNA core, which is spread among the PMOS and NMOS transistors. With the buffer effect, the overall NF is increased by 0.8 dB owing to the contribution of the source follower and passive RC connection for high pass response. Within the frequency of operation, the NF for both the LNA core and the whole circuit shows favorable and stable results.

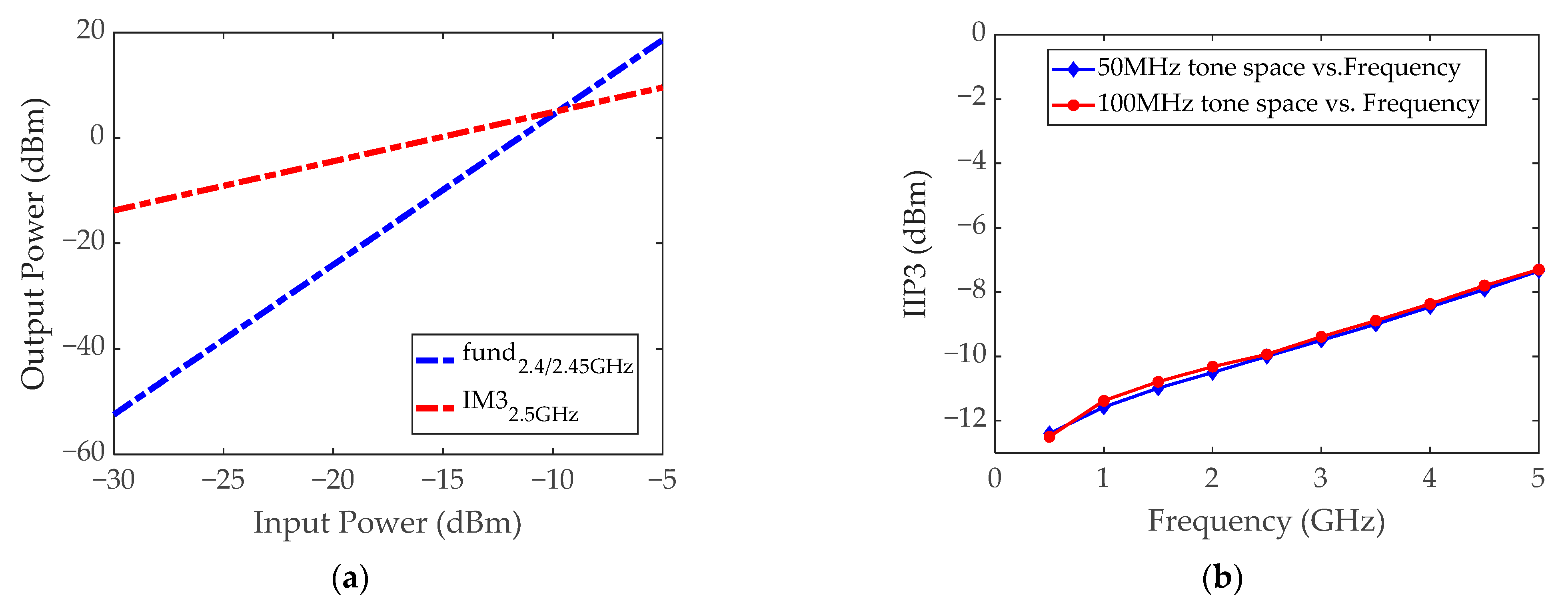

As mentioned in Equations (5)–(7), the current reuse technique affects third-order distortion performance. The distortion of the CG stage is also canceled along with the NF as long as both stages are in a balanced condition. IIP3 of the proposed LNA is mostly determined by the linearity of the CS stage itself. Linearity tests were performed using two different tones located at 2.4 GHz and 2.45 GHz (50 MHz spacing) (

Figure 7a) and sweeping the injection tones from 0.5 GHz to 5 GHz with 50 MHz and 100 MHz tone spacing (

Figure 7b). IIP3 of the LNA shows a minimum −12 dBm for both 50 MHz and 100 MHz tone spacing. Increased IIP3 across the frequency occurred due to lower gain at a higher frequency, which also reduces higher frequency harmonics.

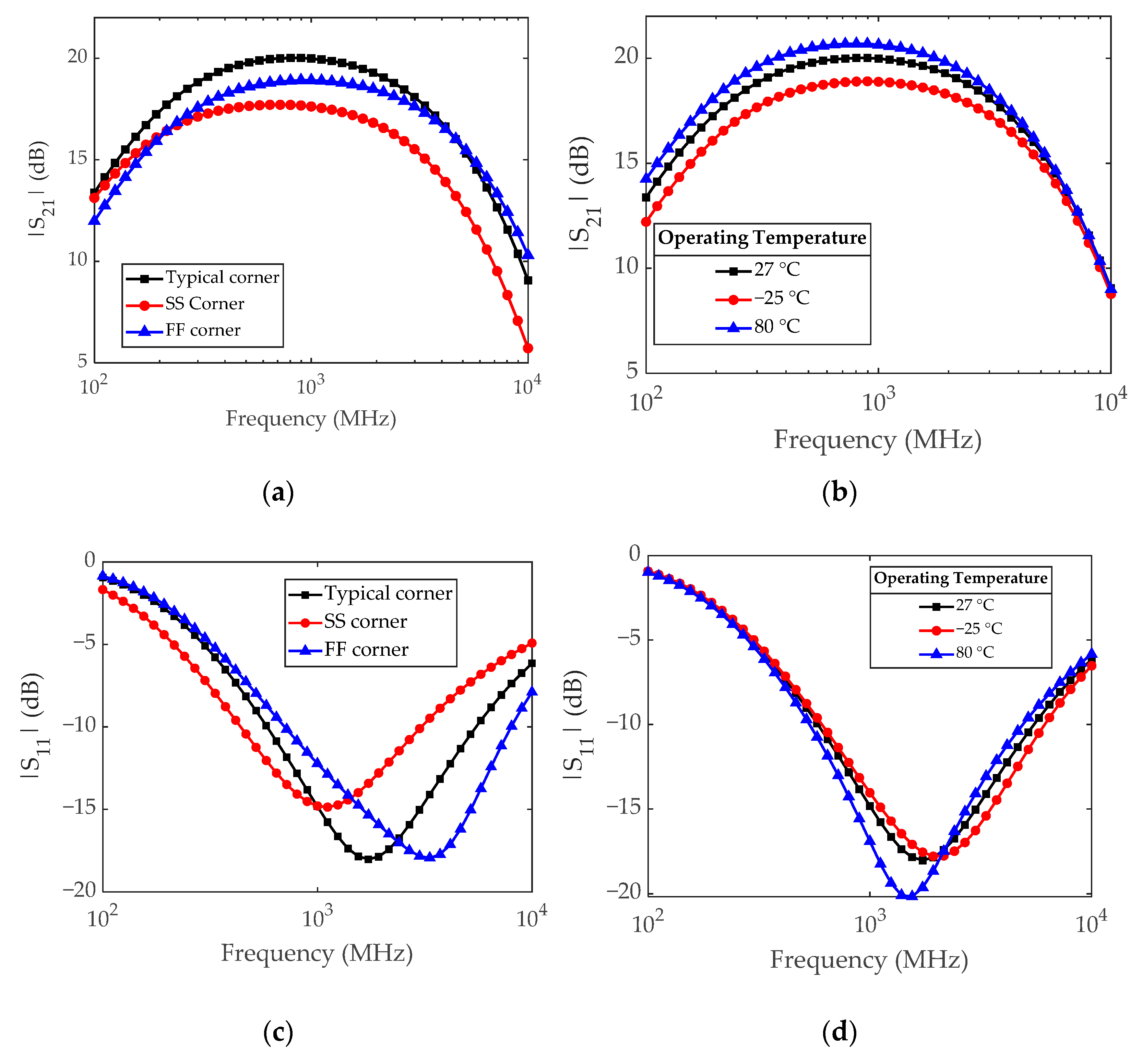

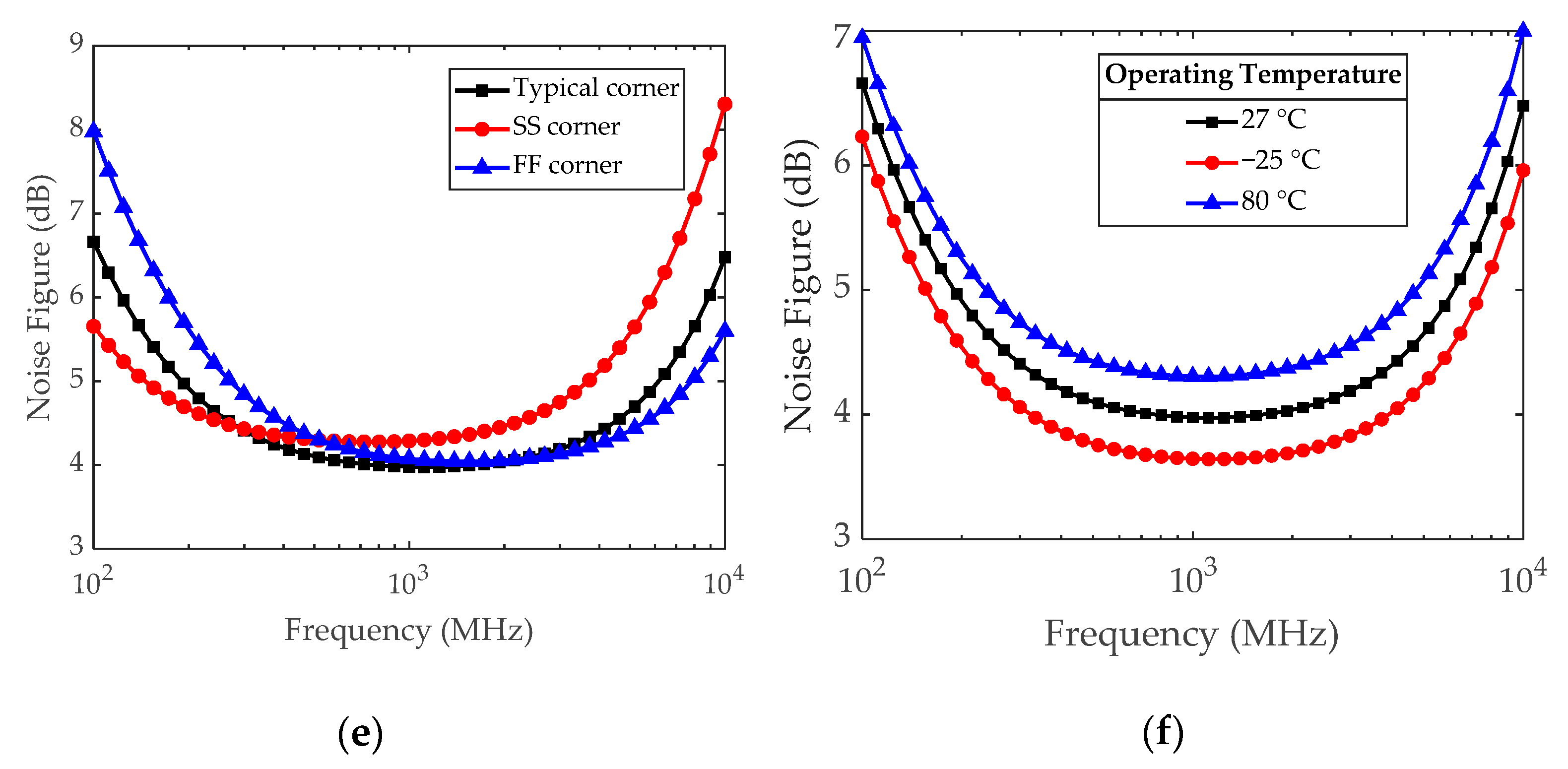

Wideband LNA with noise-canceling ability has to offer stable performance against process, voltage, and temperature (PVT) variations. To ensure the robustness of the circuit, the core LNA is simulated across typical, slow-slow (SS), and fast-fast (FF) process corners at room temperature (27°) as well as different temperatures at −25°, and 80° Celsius as depicted in

Figure 8. The power gain of the core LNA (

Figure 8a,b) shows a maximum of 19 dB, 20 dB, and 20.7 dB for −25°, 27°, and 80° Celsius, respectively. This result shows an insensitive response of the proposed LNA against temperature variations. SS corner gives a maximum power gain of 18 dB, while FF corner gives 18.9 dB. SS corner affected the power gain at a higher frequency by 2 dB, while FF corner affected the gain at a lower frequency. However, both SS and FF corners are still showing high gain performance of the proposed LNA.

Input matching (

Figure 8c,d) of the proposed LNA shows robustness against temperature variations. At −10 dB the point of low temperature shifted to 0.5–5.2 GHz, while high temperature shifted to 0.45–4.8 GHz. Furthermore, process corners are shifting the −10 dB point of the LNA by 0.4–3.3 and 0.65–8 GHz for SS, and FF corners, respectively. The noise figure of an amplifier is mainly determined by its white (thermal) noise performance. Therefore, the NF corner simulation (

Figure 8e,f) of the proposed shows temperature dependency. NF at −25°, 27°, and 80° are 3.65 dB, 4 dB, and 4.3 dB, respectively. Process variations at the SS and FF corners (

Figure 8e) increase the noise contribution in higher frequency and lower frequency, respectively. The minimum NF of the SS corner is 4.25 dB, while the FF corner is 4 dB. All of

,

, and NF corners simulation results show small variation which confirms that our design is robust against PVT variation.

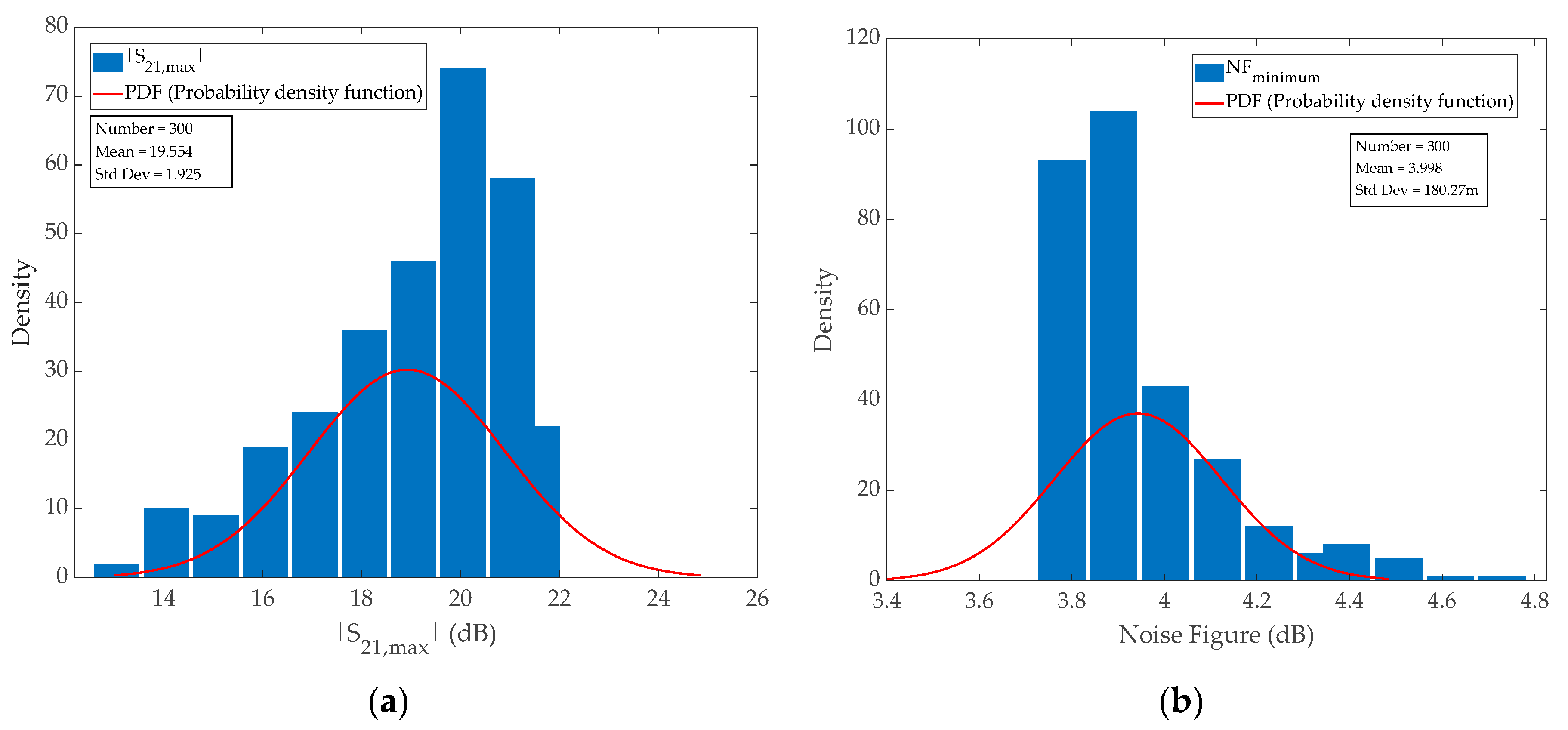

Furthermore, Monte Carlo (MC) simulations with 300 samples were run for

and NF to evaluate the stability (robustness) of gain and minimum noise figure against the statistical variations as shown in

Figure 9. Both simulations were carried out across 0.1–10 GHz frequency. Maximum

(

Figure 9a) gives a mean of 19.55 and a standard deviation of 1.925. Minimum NF (

Figure 9b) of the proposed LNA gives a mean of 3.998 dB and a standard deviation of 0.182 dB. NF that is lower than 4.2 dB is 93% of total samples. Both maximum

and minimum NF show stable results across the mismatch and process variability.

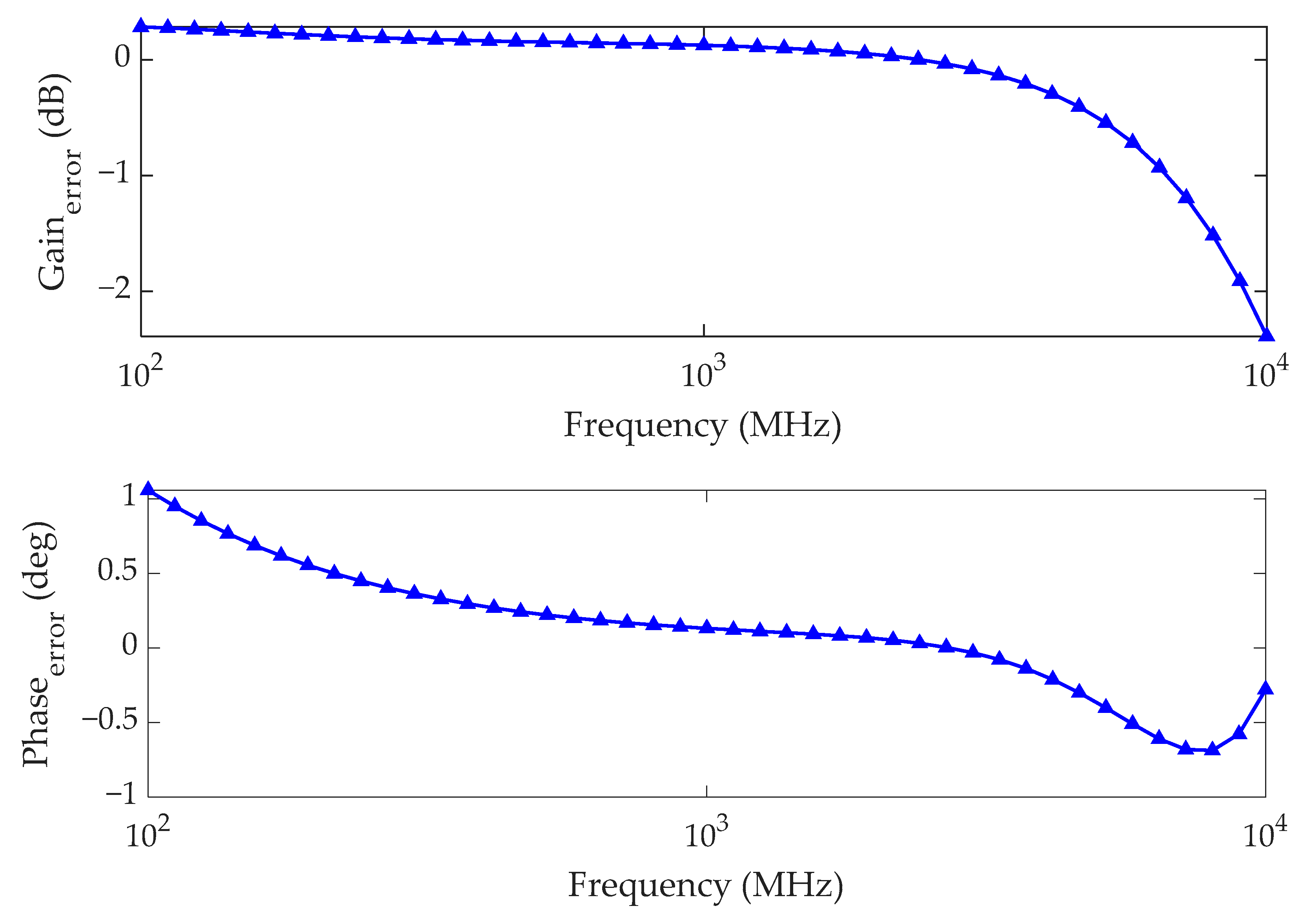

In [

13], the phase imbalance was required to be within ±5° to suppress local oscillator (LO) leakage by more than 25 dBc. The gain and phase imbalance between the positive and negative outputs for the total circuit is shown in

Figure 10. The parasitic from the devices and interconnect routings is compensated with the aid of common-mode feedback. The gain and phase imbalance of the LNA is only 0.15 to −0.54 dB and 0.2° to −0.3°, respectively, over the frequency of operation (0.5–5 GHz). Both results show effective and stable operation for the noise canceling condition as well.

The overall performance of the proposed LNA and previous works for balun-LNAs is compared in

Table 2. Conventional CG-CS balun LNA topology [

3] shows higher bandwidth and lower NF, but the power consumption is much higher than our design. Feedback CG-CS LNA without current reuse [

5] has slightly lower power consumption, gain, and noise figure but exhibits much lower bandwidth than our work, which shows better power efficiency due to the proposed current reuse technique. The design proposed by [

8] applied the same complementary NMOS/PMOS technique and has a high gain with low power consumption but gain and bandwidth are very limited due to the dependency of load resistance, compared to the bandwidth of our work which is significantly higher. LNA with active balun proposed by [

10] has the highest gain among other designs but at the cost of linearity degradation and increased power consumption. For performance comparison, the following figure of merit (FoM) [

14,

15] is used, which is typically used for LNA and low noise circuits.

where

,

BW,

,

are maximum gain, bandwidth, power consumption, and noise figure, respectively. Our LNA-balun shows the highest FOM among other works. Our proposed design further shows a fine performance for wideband operation, gain, and noise with minimum power consumption.