Abstract

The design of a wide-band voltage-controlled oscillator (VCO) modified as a VCO with programmable tail currents is introduced herein. The VCO is implemented by using CMOS current-mode logic stages, which are based on differential pairs that are connected in a ring topology. SPICE simulation results show that the VCO operates within the frequency ranges of 2.65–5.65 GHz, and when it is modified, the VCO with programmable tail currents operates between 1.38 GHz and 4.72 GHz. The design of the CMOS differential stage is detailed along with the symbolic approximation of its dominant pole, which is varied to increase the frequency response in order to achieve a higher oscillation frequency when implementing the ring oscillator structure. The layout of the VCO is described and pre- and post-layout simulations are provided, which are in good agreement using CMOS technology of 180 nm. Finally, process, voltage and temperature variations are performed to guarantee robustness of the designed CMOS ring oscillator.

1. Introduction

Originally, current mode logic (CML) was used as a mean to design VLSI logic gates to accomplish nanosecond delays. CML emerged with bipolar junction transistors (BJT) [1], and the aim was focused on eliminating the emitter-coupled logic (ECL) drawbacks at that time, such as large power consumption and excessive heat generation [2]. When CMOS technology was used to design CML stages, it was introduced with the adaptive pipeline technique to compensate for deviations in the MOS device’s parameters and in the operating environment, which in turn was used to compensate for clock skew and to decrease the power dissipation [3]. It was shown that CML has many advantages, including high speed symmetric operation, equal noise margins, equal rise and fall times, requirement of relatively few components and low power dissipation. The symmetric operation feature allows an operation with a lower logical swing, thus improving the operating speed even more. That way, several CML blocks have been used for the implementation of various topologies and logic gates, such as, buffers, latches, flip-flops, XOR gates, and push–pull topologies, among others. In this manner, this article introduces the design of a wide-band voltage-controlled oscillator (VCO) that is implemented using CML stages connected in a ring topology. It is worth mentioning that designing VCOs is a challenge [4,5,6]; besides, one can find guidelines to deal with modern design issues, such as ultra-low-power requirements [7]. Other important applications require robust VCOs, such as in designing analog-to-digital converters [8,9] or phase-locked loops [10]. Some VCOs are designed using complex devices such as negative differential resistances [11], and others such as the one introduced herein use blocks connected in a ring topology [12].

Designing a VCO with a ring structure and using differential CML stages has the advantage of great immunity to supply disturbances [13]. Other desired features in designing a VCO are associated to accomplish low-power consumption, minimum layout area, large output frequency range and wide tuning range. Those target specifications become difficult to achieve due to the continuous down scaling of silicon technology. On the one hand, VCOs can be implemented using LC-tank structures, which can tune transistors to operate at higher frequencies than ring oscillators, are relatively immune to power supply noise [14], and have outstanding phase noise and jitter performance [13]. On the other hand, designing VCOs in a ring topology is frequently a more attractive alternative because of its wider tuning range, small layout area, higher gain, low cost, robustness to variations, simplicity and scalability in deep nanoscale processes [15,16]. One challenge of VCOs based on ring topologies is reducing the deterministic jitter induced by power supply noise [14]. That way, some authors explore the use of compensation techniques to reduce the sensitivity to supply noise and also the current consumption at high switching frequencies.

The oscillation frequency of a VCO can be evaluated using Equation (1), and, to vary such a frequency, a CMOS CML stage with active load is usually employed, as shown herein. In this manner, the CMOS CML stage has a P-type MOS transistor as load, which operates in the triode region and its associated resistance is controlled by a voltage source . The associated resistance of the active load is connected with a load capacitor in which both give rise to a time constant , so that varying makes varying the oscillation frequency [16], and depending on the number of CML stages N, one can use Equation (1). Extending the oscillation frequency in a wider range that can be controlled by varying , requires a good design methodology. For instance, one must consider the number of stages that must be connected in a ring topology, as well as the delay of each CMOS CML stage. At first sight, one can think on reducing the number of stages and their associated delay to increase the oscillation frequency. However, the main effects are that decreasing N yields a reduction in gain, which may result in the oscillation eventually stopping. In this manner, this article shows that deriving the symbolic approximation of the dominant pole of the CMOS CML stage, through the use of the high-frequency small-signal equivalent model of the MOS transistor [17], can help to enhance the oscillation frequency.

The rest of this article is organized as follows: Section 2 describes the considerations taken for the design of both the CMOS CML stage and the VCO, and the analyses carried out to measure its performance characteristics. The design of a VCO using CMOS differential stages with programable tail currents is detailed in Section 3. Section 4 describes the layout design of the CMOS differential stages and the VCO. Finally, Section 5 summarizes the conclusions.

2. VCO-Based on CMOS Differential Stages

2.1. CMOS Differential Stage with Passive Load

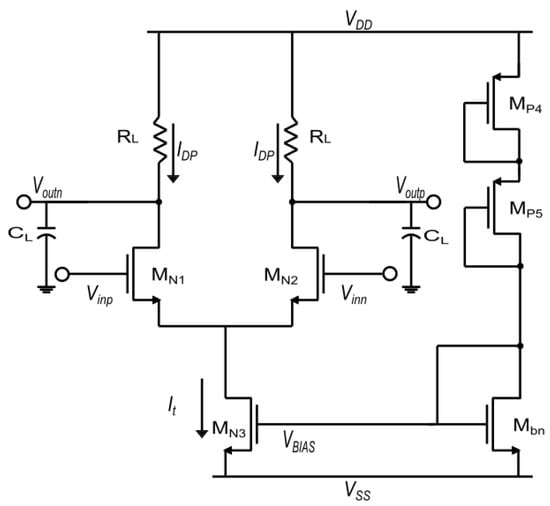

The main objective in designing a CMOS differential stage that is used for the implementation of a VCO, is oriented to achieve the highest oscillation frequency. In this manner, the first task is identifying the design issues to increase the frequency response of the CML block, which is shown in Figure 1. Its sizing considers that, according to Equation (1), the oscillation frequency is inversely proportional to both the number of CML stages N and the propagation delay . Therefore, to achieve a high oscillation frequency, the delay must be reduced [16,18]. It can be approximated by Equation (2), so that, varying the transistors dimensions [15,18,19], the delay can be reduced by augmenting and reducing the equivalent capacitance, where could be the dominant one. On the one hand, augmenting the MOS transistors dimensions leads to larger parasitic capacitance values. Therefore, the sizing is focused on reducing the dimensions of the differential-pair transistors. On the other hand, the load resistance affects the delay and it also modifies the value of the dominant pole [20], described as . In integrated circuit design, is directly proportional to the gain-bandwidth-product (), and considering the trade-off between and the open-loop gain , the most important issue is enhancing [21,22].

Figure 1.

CMOS current-mode logic stage with passive load.

To find the appropriate load resistor value one can use . If the MOS transistors should be in saturation, one must accomplish and . For instance, setting , , and , then . The overdrive voltages take into account that small size dimensions are desirable, and the ratios are calculated by Equation (3) that is obtained from the quadratic model equation. In this manner, using CMOS technology of 180 nm from UMC, the sizes are set to m, m, m, and m.

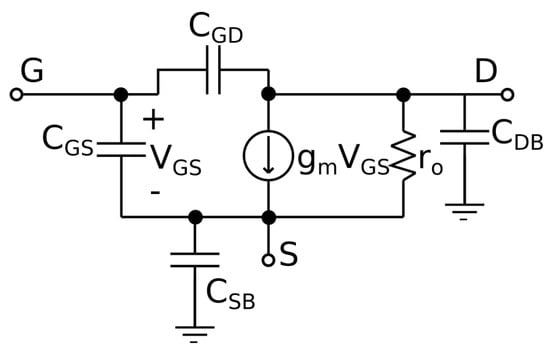

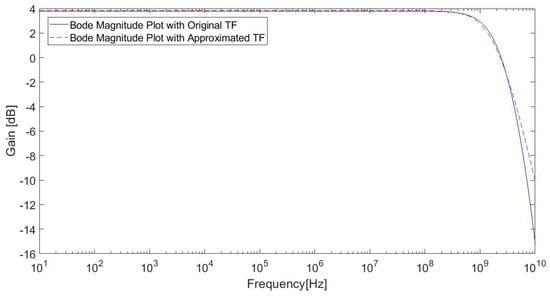

Since the VCO is desired to operate at high frequencies, the MOS high-frequency model shown in Figure 2 [22] is used. An input voltage is connected to the node labeled , and node is associated to the sources of the differential pair, so that performing nodal analysis results in the matrix formulation given in Equation (4), where: , , , , , , , , , , , , , . Applying the work in [23,24], the compact and second-order symbolic expression that approaches the dominant pole can be expressed by , where: and . It is notorious that the dominant pole value heavily depends on both and , the values of which are proportional to the transistor’s sizes [20]. That way, the reduction of transistor’s sizes leads to an increase of . To verify the symbolic approximation, the Bode magnitude given in Figure 3 compares the complete or original transfer function (TF) with the approximated TF.

Figure 2.

High-frequency MOSFET model [22].

Figure 3.

Bode magnitude of the current-mode logic stage shown in Figure 1, simulated using CMOS technology of 180 nm, and comparing the original TF versus the symbolic approximation.

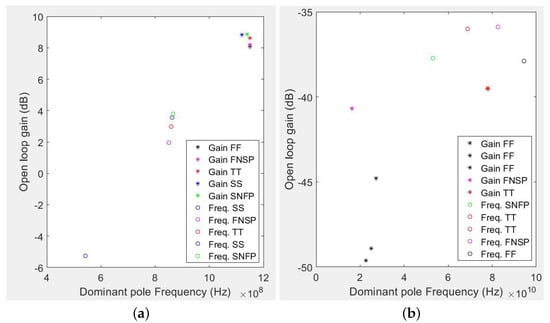

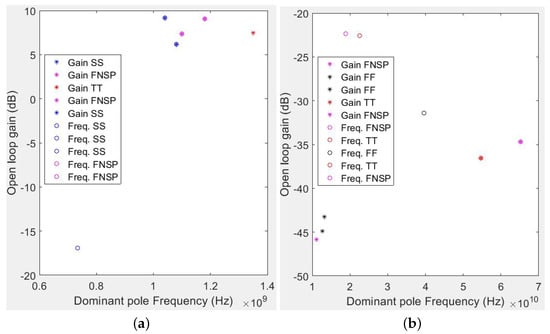

The CMOS CML stage can be characterized measuring the open-loop gain and the dominant pole . The gain-bandwidth product is the frequency at which becomes 0 dB [25]. The load capacitor is selected under the supposition that a CML stage must be capable of driving three stages, therefore we assume , where is obtained from the .lis file generated from the SPICE circuit simulation. The design is tested under process, voltage and temperature (PVT) variations. A robust design must have a low PVT sensitivity, and it is performed considering five process corners: TT (typical–typical), SS (slow–slow), SNFP (slow–fast), FNSP (fast–slow) and FF (fast–fast). The test considers three voltage variations of of , and three temperature variations from C, C and C [26]. Figure 4 summarizes the higher and lower values resulting from the PVT variations for . The dependence of the gain and dominant pole values under PVT variations depicted in this figure show that there is a wide variation in both parameters, where the high gain cases occur mostly for lower dominant pole frequencies and viceversa. Table 1 summarizes the measured and values, for each PVT variation. Due to the huge variations, this design is unsuitable for designing a VCO. Therefore, a CMOS CML stage with active load is detailed in the next subsection.

Figure 4.

(a) Higher and (b) lower gains and dominant pole frequencies with .

Table 1.

Open-loop gain and dominant pole values over PVT variations with .

2.2. CMOS Differential Stage with Active Load

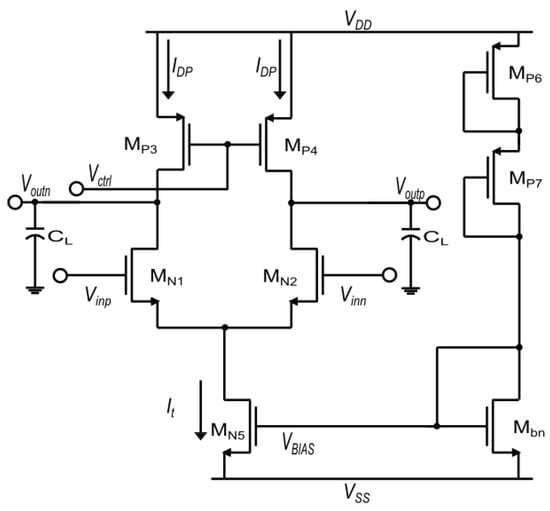

Figure 5 shows the CMOS differential stage with active loads implemented by P-type MOS transistors ( and ) that must operate in the triode region. The value of the equivalent resistance is controlled by varying the voltage at the gates of the PMOS transistors, which is called control voltage [16,27]. The output conductance of the PMOS transistor can be approached as . The sizing of - must accomplish and Equation (5) [28]. To achieve a wide range of control-voltage, the sizes are: m, m, m, m, and m, in all cases m.

Figure 5.

CMOS differential stage with active load and voltage control.

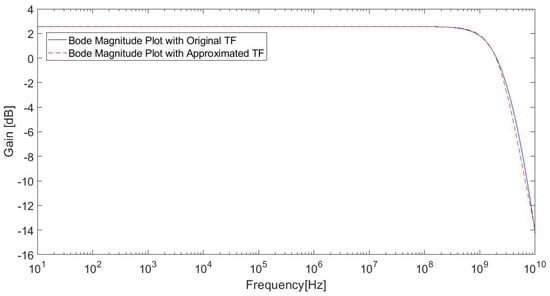

The approximation of the dominant pole is performed in the same way as done for the CML stage with passive load, and it can be approached by Equation (6). The comparison of the Bode magnitude of both the original and the approximated transfer functions (TF) is shown in Figure 6. Again, it can be appreciated that the dominant pole depends on both , of the differential pair, and of the active load [24], so that the reduction of the transistor’s sizes leads to an increase of .

Figure 6.

Bode magnitude of the CMOS differential stage shown in Figure 5, simulated using CMOS technology of 180 nm, and comparing the original TF versus the symbolic approximation.

The characterization of the CMOS differential stage with active load provides the results given in Section 4, where one can see the comparison between the performances with and without post-layout simulations. The PVT variations are simulated setting , considering five process corners (TT, SS, SNFP, FNSP and FF), three voltage variations ( of ), and three temperature variations ( C, C and C) [26]. The higher and lower gain and frequency values are shown in Figure 7. One can see that the higher dominant pole frequencies are achieved in the FNSP and TT process corners; however, the FNSP corner also presents some of the lowest dominant pole values along with the SS corner. Table 2 summarizes the PVT simulation results.

Figure 7.

(a) Higher and (b) lower gains and dominant pole frequencies, for the CMOS differential stage with active load and V.

Table 2.

Open-loop gain and dominant pole frequency over PVT variations with V.

2.3. Voltage Controlled Oscillator Based on CMOS Differential Stages

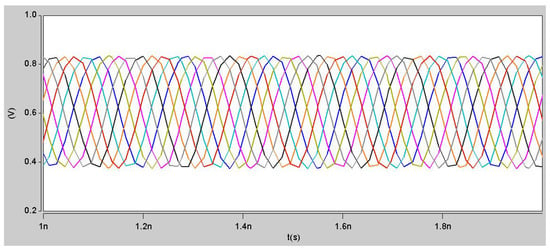

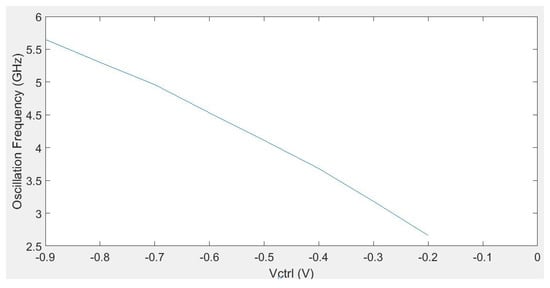

The CMOS differential stage with active load is used herein to design a four-differential stages VCO, as shown in Figure 8. In this case, the sizes of the MOS transistors are varied to reach the highest oscillation frequency, so that they were established as m, m, with , thus resulting in oscillations between the frequencies 2.65 GHz and 5.65 GHz, which require control voltages in the range between V and V. The oscillating frequency of 5.65 GHz with a control voltage of V is shown in Figure 9, for which the average power consumption was 39 mW. The control voltage range can be appreciated in Figure 10.

Figure 8.

Voltage controlled ring oscillator consisting of four-differential stages with active loads.

Figure 9.

VCO response when V and = 5.65 GHz.

Figure 10.

Oscillation frequency vs. control voltage variation.

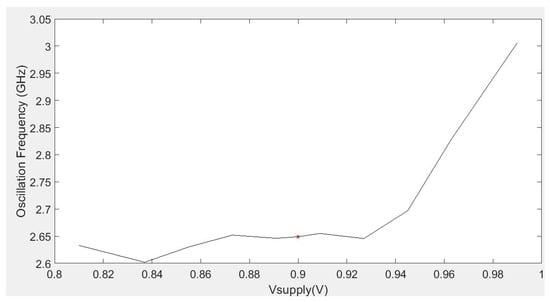

The static supply sensitivity of the VCO is very important, and it is measured observing the change in the oscillation frequency due to a supply voltage variation [29]. Figure 11 shows the frequency variations produced by the changes in the supply voltage. The results show a static supply sensitivity of . Table 3 shows a comparison between the proposed VCO and other CML-based VCOs already published in the literature. As one can see, the three VCOs are designed using CMOS technology of 180 nm and voltage supplies of 1.8 V. Other VCOs implemented in CML-based ring structure have been designed and applied in analog-to-digital converter [30] and pseudo-random bit sequence generator [31]. However, they are not listed in Table 3 due to lack of information such as number of stages, supply voltage, tail current, load capacitance, and power dissipation. Besides, the VCO in [30] was implemented using CMOS technology of 90 nm and the one in [31] using 180 nm. These VCOs provide frequency tuning ranges of 1–7.2 and 2.7–3.3 GHz and voltage tuning ranges of 0.32–0.62 and 0–1.1 V, respectively. On the other hand, the proposed VCO uses four stages and a higher load capacitance compared to the one in [15,32], and it provides the higher frequency tuning range while maintaining an acceptable control-voltage range, power dissipation and supply sensitivity.

Figure 11.

VCO’s oscillation frequency vs. supply voltage.

Table 3.

Comparison among the proposed VCO and related designs.

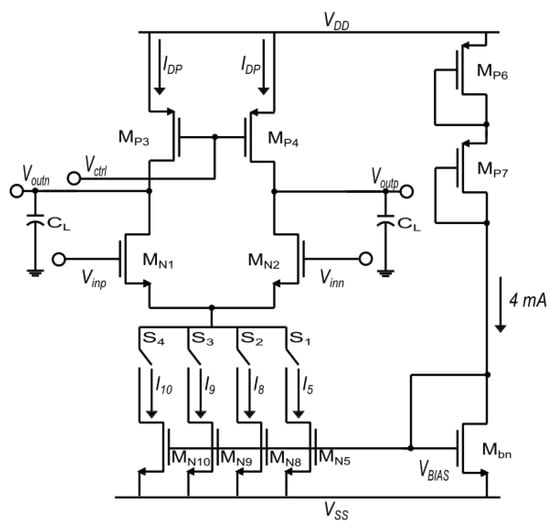

3. VCO with Programmable Tail Currents

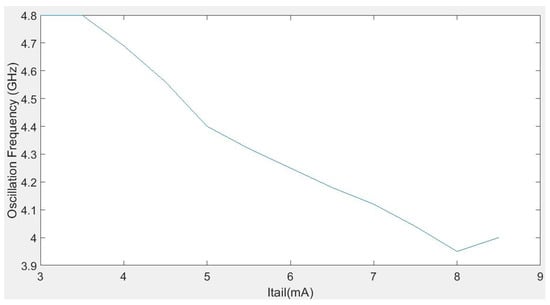

Based on the VCO design shown in Figure 8, this section shows its programmable version by designing a logic that controls the flow of the tail current. The programmability of the tail current can be performed using different number of switches; in this section, four switches are used, as shown in Figure 12. Basically, the sizes of the MOS transistors are calculated to control the current flow, which can also be replaced by a variable current source when setting the to a constant value. In this case, the control-voltage is fixed to the value that allows the widest current variation to achieve a wide programmable current range, while keeping the transistors working in the desired operation region. It resulted in V to have the oscillation frequency shown in Figure 13, which is associated to a current variation between 3 and 8 mA, approximately.

Figure 12.

Programmable tail currents in the CMOS differential stage using four switches.

Figure 13.

Oscillation frequency vs. tail current @ V.

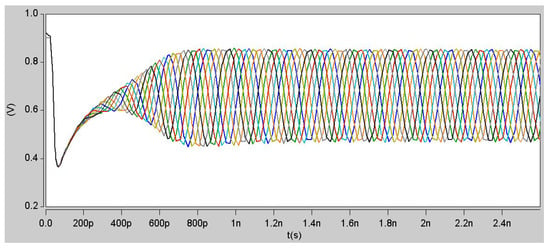

The four switches shown in Figure 12 allow a discrete variation of the current that can be programmed using four bits. Each MOS transistor is sized differently to provide a fraction of the current that will flow in the tail of the differential pair. That way, the programmable current ranges can be established to be between 3 mA and mA, and the current flowing through the bias transistors is defined to be 4 mA. Therefore, to be able to program the tail current with discrete values, the MOS transistors and are sized to drive a current of 4 mA, 2 mA, 1 mA and mA, respectively. The sizes of those MOS transistors are the following: m, m, m and m. In this case, the logic states of the switches are programmed as shown in Table 4, which summarizes the logical values needed to produce each tail current, where a logical 1 is produced with a pulse of 0.9 V and a logical 0 with a pulse of 0 V, the pulses are mean that the corresponding switch must be closed and open, respectively. It is worth mentioning that the design of the switches must be done carefully to mitigate the on parasitic resistance and capacitances of the MOS transistors. Figure 14 shows the programmable tail currents in the VCO’s output waveforms generating an oscillation frequency for a 3 mA tail current. The tendency of the oscillation frequency to decrease with an increasing tail current coincides with the programmable VCO’s results shown in Figure 13.

Table 4.

Programmable switches to provide bias currents in the range from 3 to 7.5 mA, in steps of 0.5 mA.

Figure 14.

VCO’s output waveforms for a programmed current of 3 mA.

4. Layout Design of the VCO Based on CMOS Differential Stages with Active Load

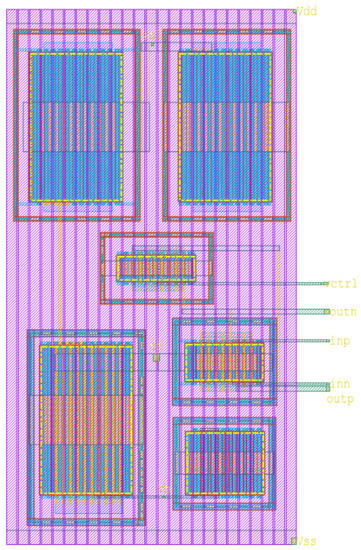

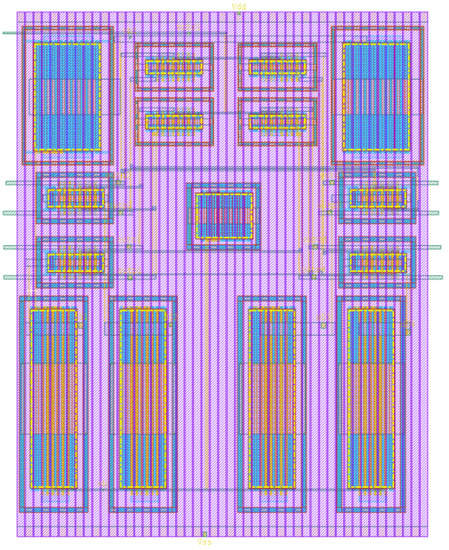

The minimum width and length sizes of the MOS transistors for a 180 nm UMC technology are m and m, for the NMOS and PMOS transistors, respectively. The minimum diffusion area is 0.1936 m, the minimum poly to diffusion spacing is m, and the minimum implant overhang of diffusion equals m. The sizes for the SPICE simulations are slightly modified to achieve a highly symmetrical layout in order to reduce mismatches [25]. The MOS transistors are placed with the same orientation and maintaining the NMOS and PMOS accommodated in different areas of the chip, but trying to use minimum silicon area. The placement of each transistor is the first task to get a symmetrical layout; after this, electromigration rules are taken into account to determine the minimum amount of fingers, which are necessary for the desired current to flow through each metal without damaging the integrated circuit. In this manner, the efficient placement is to maintain NMOS transistors at the bottom block and the PMOS transistors at the top block, to achieve a good matching between the differential pair transistors, which are placed in an interdigitated structure and over . The layout of one CMOS differential stage with active load is shown in Figure 15, which occupies an area of 6377 m, including the power grid.

Figure 15.

Layout of a CMOS differential stage implemented in Tanner from Mentor graphics using UMC 180 nm technology.

The sizes of the CMOS differential stages consider dimensions with multiplicities to ensure that the post-layout simulations provide the same or a best range of control-voltage and oscillation frequency. Table 5 summarizes the comparison of the simulation results of the CMOS differential stage performing post-layout characterization, which has a power consumption of 32 mW. This table shows that there are very minor changes in the characterizations of the CMOS differential stage in the post-layout simulation.

Table 5.

Pre- and post-layout characterization of the CMOS differential stage.

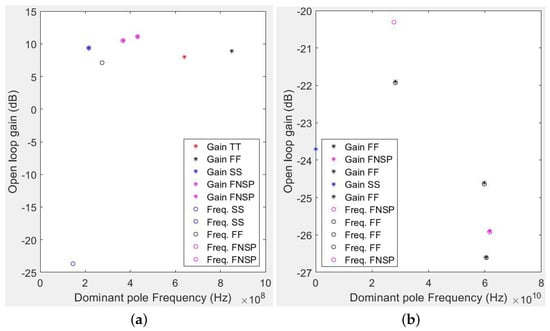

PVT variations are simulated for five corners and setting V, so that the higher and lower gain and frequency values for the post-layout VCO are shown in Figure 16. The higher dominant pole frequencies are achieved in the FNSP and the FF process corners, however, the FNSP corner also presents some of the lowest dominant pole frequency values along with the SS corner. Table 6 summarizes the measured and values for each PVT variation.

Figure 16.

(a) Higher and (b) lower gains and dominant pole frequencies of the CMOS differential stage with active load under PVT variations and setting V.

Table 6.

Post-layout open-loop gain and dominant pole frequency values under PVT variations and setting V.

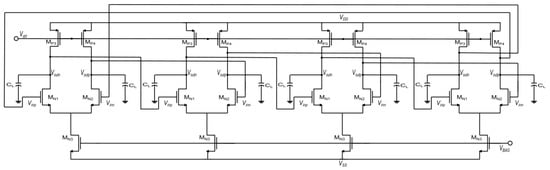

The complete layout of the four-stage VCO based on CMOS differential stages is shown in Figure 17. It reuses the layout of the CMOS stage shown in Figure 15, and the complete layout is also designed with the goal of obtaining a highly symmetrical layout. The silicon area of the complete VCO including the power grid is 17,019 m.

Figure 17.

Complete layout of the VCO based on four CMOS differential stages, implemented in Tanner from Mentor graphics using UMC technology of 180 nm.

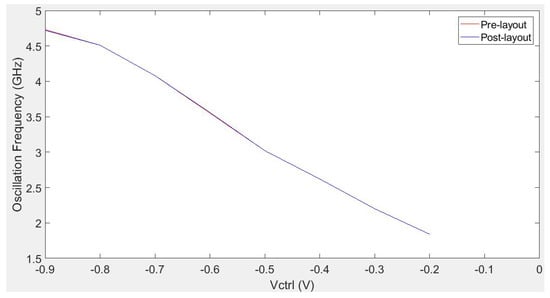

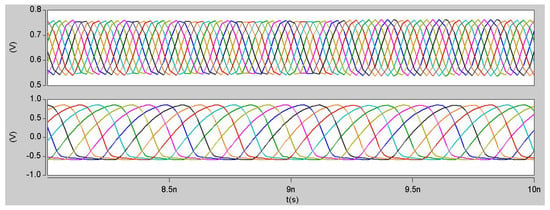

The post-layout oscillation frequencies are between GHz and GHz, for control voltages between V and V. Figure 18 shows the comparison between the pre- and post-layouts of the VCO based on four CMOS differential stages. An amplified view of the post-layout output signals for control voltages of V and V is shown in Figure 19. The average power consumptions of both cases is 42 mW.

Figure 18.

Comparison of the oscillation frequency vs. control voltage for the pre- and post-layout simulations of the VCO.

Figure 19.

Post-layout output waveforms of the VCO for V (top) and V (bottom).

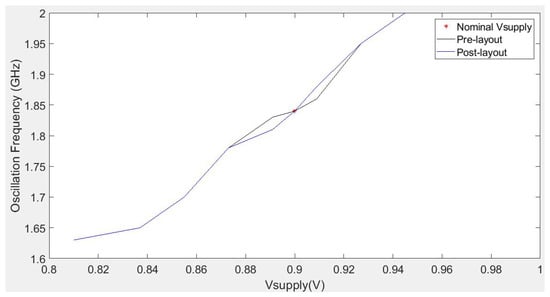

To measure the static supply sensitivity of the VCO, the change in the oscillation frequency due to a supply voltage variation is measured [29], and the results are shown in Figure 20 for both the pre- and post-layout VCOs. The results show a static supply sensitivity of and for the VCO and the post-layout VCO, respectively.

Figure 20.

Frequency variations produced by the changes in the supply voltage of the VCO.

5. Conclusions

The design of a VCO based on four CMOS differential stages connected in a ring topology is presented. Analytical expressions were derived applying symbolic analysis to identify the requirements to extend the frequency of oscillation. As a result, the theoretical simulations provided a range of control-voltage between −0.2 V and −0.9 V, which corresponds to an oscillation frequency in the range between 2.65 GHz and 5.65 GHz. This range is wider compared to similar topologies reported in the literature. In addition, the post-layout simulation results verified that the design of the proposed VCO was successful. The VCO was modified to program the tails currents using four switches for a current range between 3 mA and 7.5 mA, which provided an oscillation frequency within the range from 1.38 GHz to 4.72 GHz. This range is very close to the one measured before layout, thus showing the suitability of the CMOS differential stage to be used in the design of a VCO.

Finally, as stated by Equation (1), the oscillation frequency is inversely proportional to the number of stages, so that a reduction of stages leads to a reduction in the gain, and augmenting the stages leads to a reduction in the frequency range. For instance, performing simulations using six CMOS differential stages instead of four, the frequency range of the VCO is reduced from 2.65–5.65 GHz to 1.81–3.7 GHz. That way, using four stages is a good number to increase the range of frequency and voltage-control.

Author Contributions

Investigation, E.T.-C., P.R.C.-A., R.T.-G. and V.H.C.-G.; and Writing—review and editing, E.T.-C., P.R.C.-A., R.T.-G.

Funding

This work was not funding.

Conflicts of Interest

The authors declare no conflict of interest. The founding sponsors had no role in the design of the study; in the collection, analyses, or interpretation of data; in the writing of the manuscript, or in the decision to publish the results.

References

- Tanaka, M.; Ozawa, S.; Mori, S. Rewritable programmable logic array of current mode logic. IEEE Trans. Comput. 1981, 30, 229–234. [Google Scholar] [CrossRef]

- Einspruch, N. The VLSI Handbook; CRC Press: Boca Raton, FL, USA, 2012. [Google Scholar]

- Mizuno, M.; Yamashina, M.; Furuta, K.; Igura, H.; Abiko, H.; Okabe, K.; Ono, A.; Yamada, H. A GHz MOS adaptive pipeline technique using MOS current-mode logic. IEEE J. Solid-State Circuits 1996, 31, 784–791. [Google Scholar] [CrossRef]

- Hsieh, J.Y.; Lin, K.Y. A 0.7-mW LC Voltage-Controlled Oscillator Leveraging Switched Biasing Technique for Low Phase Noise. IEEE Trans. Circuits Syst. II Express Briefs 2019, 66, 1307–1310. [Google Scholar] [CrossRef]

- Basaligheh, A.; Saffari, P.; Winkler, W.; Moez, K. A Wide Tuning Range, Low Phase Noise, and Area Efficient Dual-Band Millimeter-Wave CMOS VCO Based on Switching Cores. IEEE Trans. Circuits Syst. I Regul. Pap. 2019, 66, 2888–2897. [Google Scholar] [CrossRef]

- Poor, M.A.; Esmaeeli, O.; Sheikhaei, S. A low phase noise quadrature VCO using superharmonic injection, current reuse, and negative resistance techniques in CMOS technology. Analog Integr. Circuits Signal Process. 2019, 99, 633–644. [Google Scholar] [CrossRef]

- Ghorbel, I.; Haddad, F.; Rahajandraibe, W.; Loulou, M. Design Methodology of Ultra-Low-Power LC-VCOs for IoT Applications. J. Circuits Syst. Comput. 2019, 28. [Google Scholar] [CrossRef]

- Al-Tamimi, K.M.; El-Sankary, K.; Fouzar, Y. VCO-Based ADC With Built-In Supply Noise Immunity Using Injection-Locked Ring Oscillators. IEEE Transa. Circuits Syst. II Express Briefs 2019, 66, 1089–1093. [Google Scholar] [CrossRef]

- Ding, Z.; Zhou, X.; Li, Q. A 0.5-1.1-V Adaptive Bypassing SAR ADC Utilizing the Oscillation-Cycle Information of a VCO-Based Comparator. IEEE J. Solid-State Circuits 2019, 54, 968–977. [Google Scholar] [CrossRef]

- Sharma, J.; Krishnaswamy, H. A 2.4- GHz Reference-Sampling Phase-Locked Loop That Simultaneously Achieves Low-Noise and Low-Spur Performance. IEEE J. Solid-State Circuits 2019, 54, 1407–1424. [Google Scholar] [CrossRef]

- Ulansky, V.; Raza, A.; Oun, H. Electronic Circuit with Controllable Negative Differential Resistance and its Applications. Electronics 2019, 8, 409. [Google Scholar] [CrossRef]

- Sun, I.F.; Yin, J.; Mak, P.I.; Martins, R.P. A Comparative Study of 8-Phase Feedforward-Coupling Ring VCOs. IEEE Trans. Circuits Syst. II Express Briefs 2019, 66, 527–531. [Google Scholar] [CrossRef]

- Abidi, A.A. Phase noise and jitter in CMOS ring oscillators. IEEE J. Solid-State Circuits 2006, 41, 1803–1816. [Google Scholar] [CrossRef]

- Wang, Z.; Bai, X.; Diao, S.; Lin, F. An open loop compensation technique for reducing supply sensitivity of CML ring oscillator. Analog Integr. Circuits Signal Process. 2017, 93, 277–285. [Google Scholar] [CrossRef]

- Gui, X.; Green, M.M. Design of CML ring oscillators with low supply sensitivity. IEEE Trans. Circuits Syst. I Regul. Pap. 2013, 60, 1753–1763. [Google Scholar] [CrossRef]

- Zhang, Z.; Chen, L.; Djahanshahi, H. A SEE Insensitive CML Voltage Controlled Oscillator in 65nm CMOS. In Proceedings of the 2018 IEEE Canadian Conference on Electrical & Computer Engineering (CCECE), Quebec City, QC, Canada, 13–16 May 2018; pp. 1–4. [Google Scholar]

- Kishine, K.; Inaba, H.; Ohtomo, Y.; Nakamura, M.; Koizumi, H.; Nakamura, M. Analysis and design based on small-signal equivalent circuit for a lO- GHz ring VCO with 65-nm CMOS. In Proceedings of the 2013 IEEE 56th International Midwest Symposium on Circuits and Systems (MWSCAS), Columbus, OH, USA, 4–7 August 2013; pp. 904–907. [Google Scholar]

- Heydari, P.; Mohanavelu, R. Design of ultrahigh-speed low-voltage CMOS CML buffers and latches. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2004, 12, 1081–1093. [Google Scholar] [CrossRef]

- Kumar, M. Design of Linear Low-Power Voltage-Controlled Oscillator with I-MOS Varactor and Back-Gate Tuning. Circuits Syst. Signal Process. 2018, 37, 3685–3701. [Google Scholar] [CrossRef]

- Razavi, B. Design of Analog CMOS Integrated Circuits; McGraw-Hill: New York, NY, USA, 2002. [Google Scholar]

- Meyer, R.G. Noise, Gain and Bandwidth in Analog Design. In Trade-Offs in Analog Circuit Design; Toumazou, C., Moschytz, G., Eds.; Springer: Boston, MA, USA, 2002; pp. 227–256. [Google Scholar]

- Razavi, B. Fundamentals of Microelectronics; Wiley: Hoboken, NJ, USA, 2008. [Google Scholar]

- Duarte-Villaseñor, M.A.; Tlelo-Cuautle, E.; de la Fraga, L.G.; Sánchez-López, C. Symbolic Analysis and Synthesis of Analog Circuits Using Nullors and Pathological Mirror Elements. In Pathological Elements in Analog Circuit Design; Springer: Manhattan, NY, USA, 2018; pp. 3–30. [Google Scholar]

- Palumbo, G.; Pennisi, S. Feedback Amplifiers: Theory and Design; Springer Science & Business Media: Berlin, Germany, 2002. [Google Scholar]

- Maloberti, F. Analog design for CMOS VLSI Systems; Springer Science & Business Media: Berlin, Germany, 2006; Volume 646. [Google Scholar]

- Chen, P.; Cheng, H.C.; Widodo, A.; Tsai, W.X. A PVT insensitive field programmable gate array time-to-digital converter. In Proceedings of the 2013 IEEE Nordic-Mediterranean Workshop on Time-to-Digital Converters (NoMe TDC), Perugia, Italy, 3 October 2013; pp. 1–4. [Google Scholar]

- Jyotsna, K.; Kumar, P.S.; Madhavi, B. Implementation of 8 Bit Microprocessor Using Current Mode Logic (CML) Approach. In Proceedings of the 2018 3rd International Conference for Convergence in Technology (I2CT), Pune, India, 6–8 April 2018; pp. 1–6. [Google Scholar]

- Sedra, A.S.; Smith, K.C. Microelectronic Circuits; Holt, Rinehart and Oxford University Press: Oxford, UK, 1982. [Google Scholar]

- Mansuri, M.; Yang, C.K. A low-power adaptive bandwidth PLL and clock buffer with supply-noise compensation. IEEE J. Solid-State Circuits 2003, 38, 1804–1812. [Google Scholar] [CrossRef]

- Aryasomayajula, L.J.; Khatua, P.; Mal, A.K. Analog-to-digital converter using CML based Ring oscillator with tuning range 1–7.2 GHz in 90 nm CMOS. In Proceedings of the IEEE International Conference on Computer Communication and Systems ICCCS14, Chennai, India, 20–21 February 2014; pp. 130–135. [Google Scholar]

- Chen, H.J.; Jou, J.J.; Shih, T.T. Design of pseudo-random bit sequence generator with adjustable sinusoidal jitter. In Proceedings of the 2016 International SoC Design Conference (ISOCC), Jeju, South Korea, 23–26 October 2016; pp. 263–264. [Google Scholar]

- Mondal, A.J.; Majudmer, A.; Bhattacharyya, B.K. A Design Methodology for MOS Current Mode Logic VCO. In Proceedings of the 2017 IEEE International Symposium on Nanoelectronic and Information Systems (iNIS), Bhopal, India, 18–20 December 2017; pp. 206–209. [Google Scholar]

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).