A Class-AB Reference Voltage Buffer for SC Circuits in Pipelined ADCs

Abstract

1. Introduction

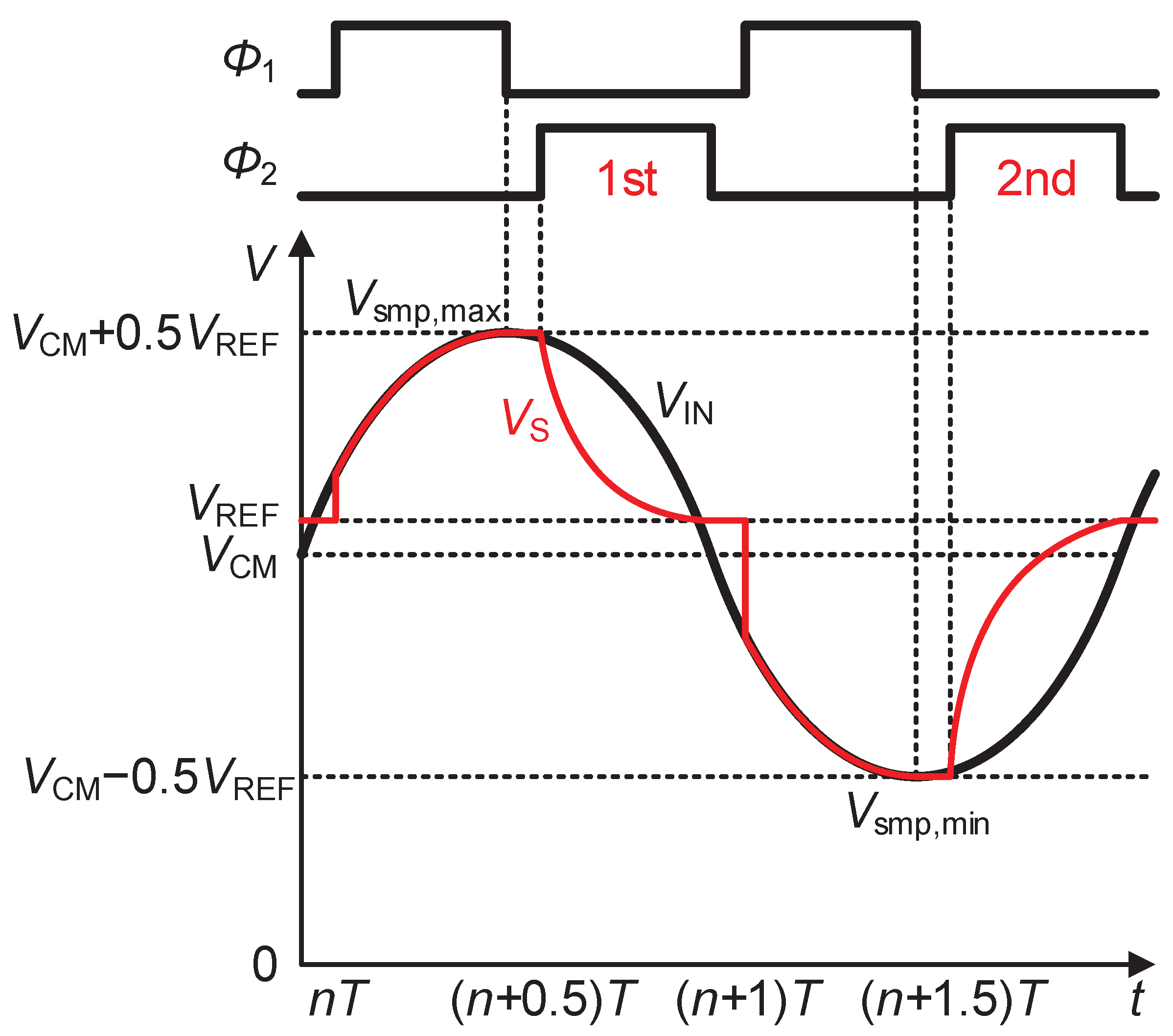

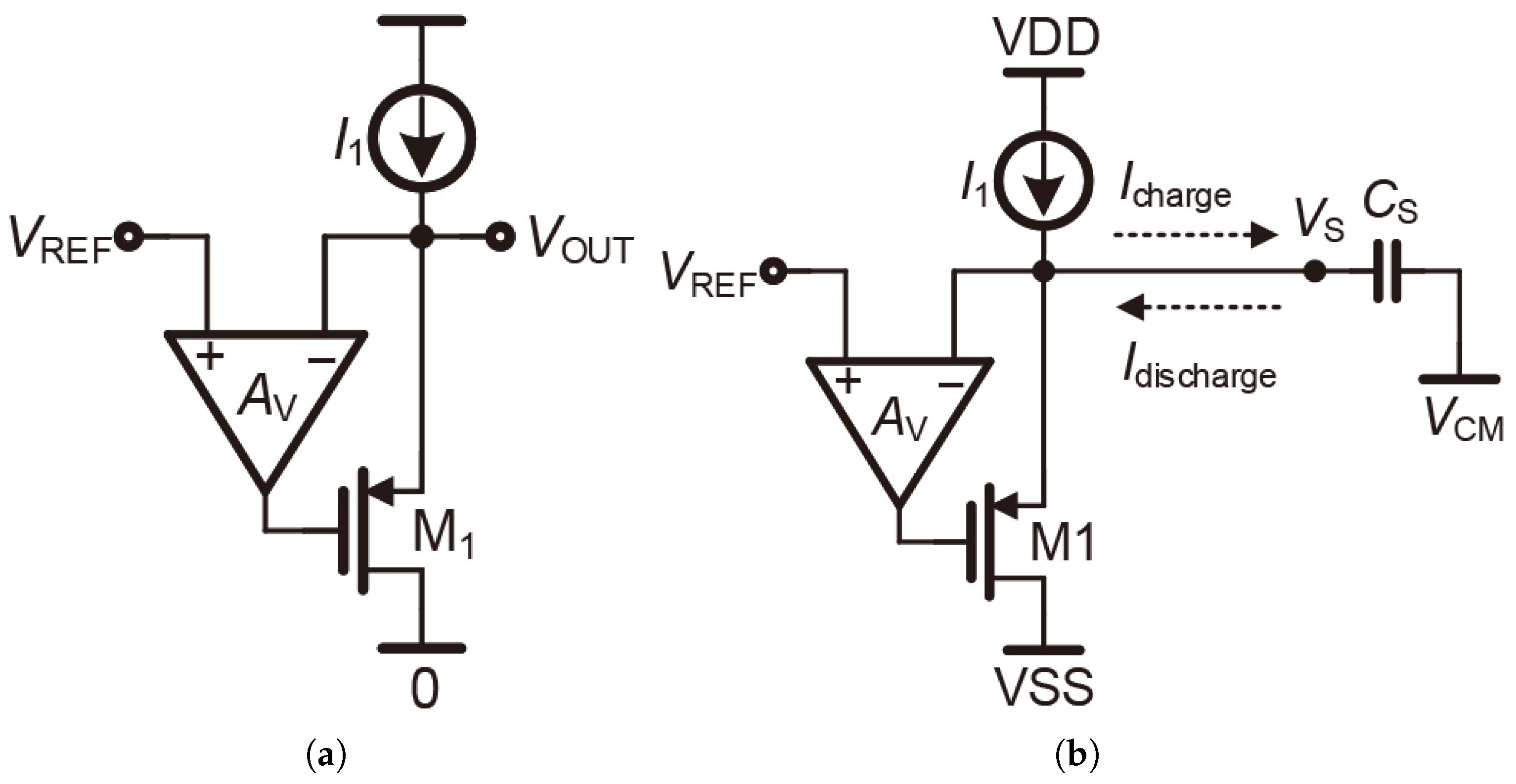

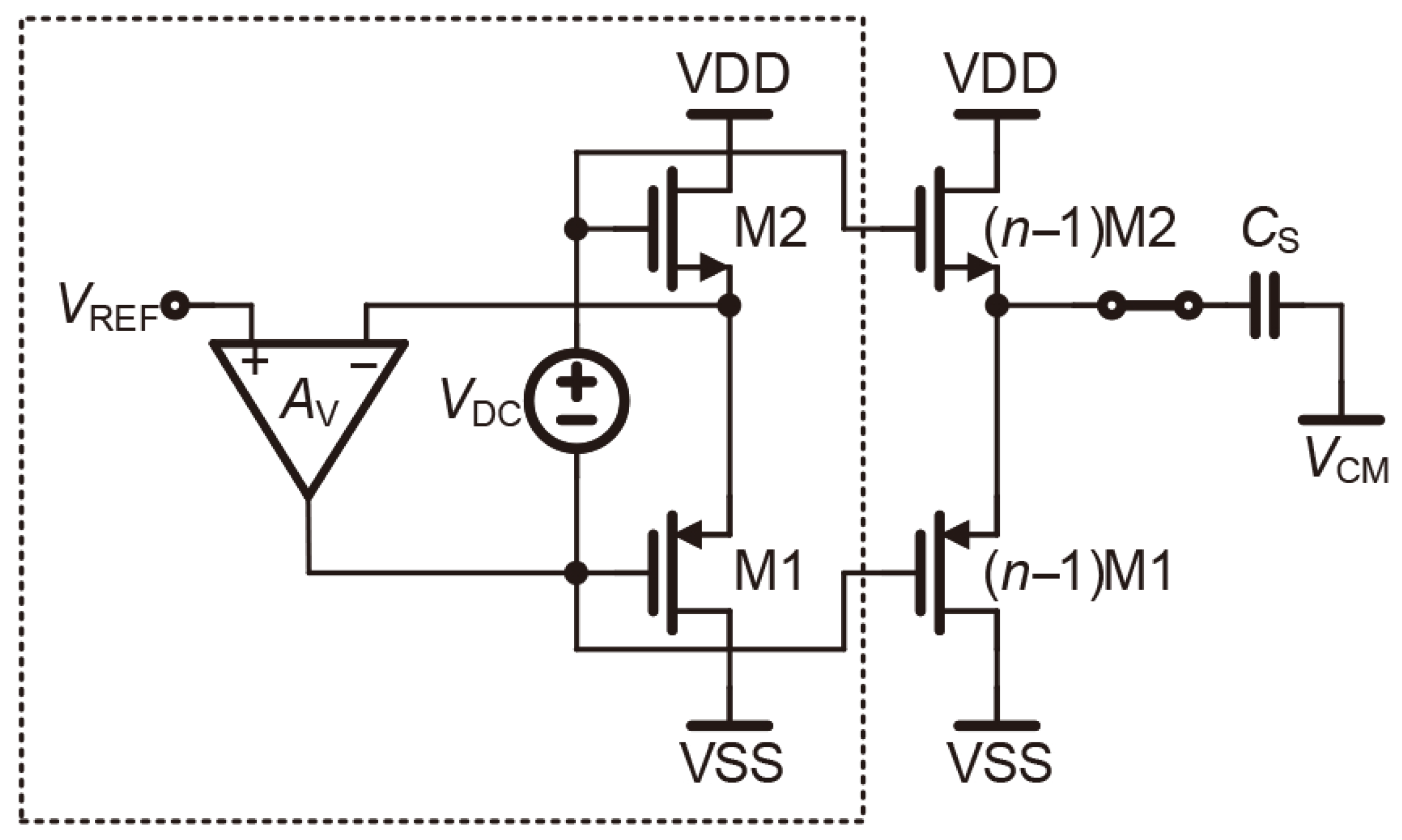

2. The Process of VREF Settling

3. The Proposed RVB

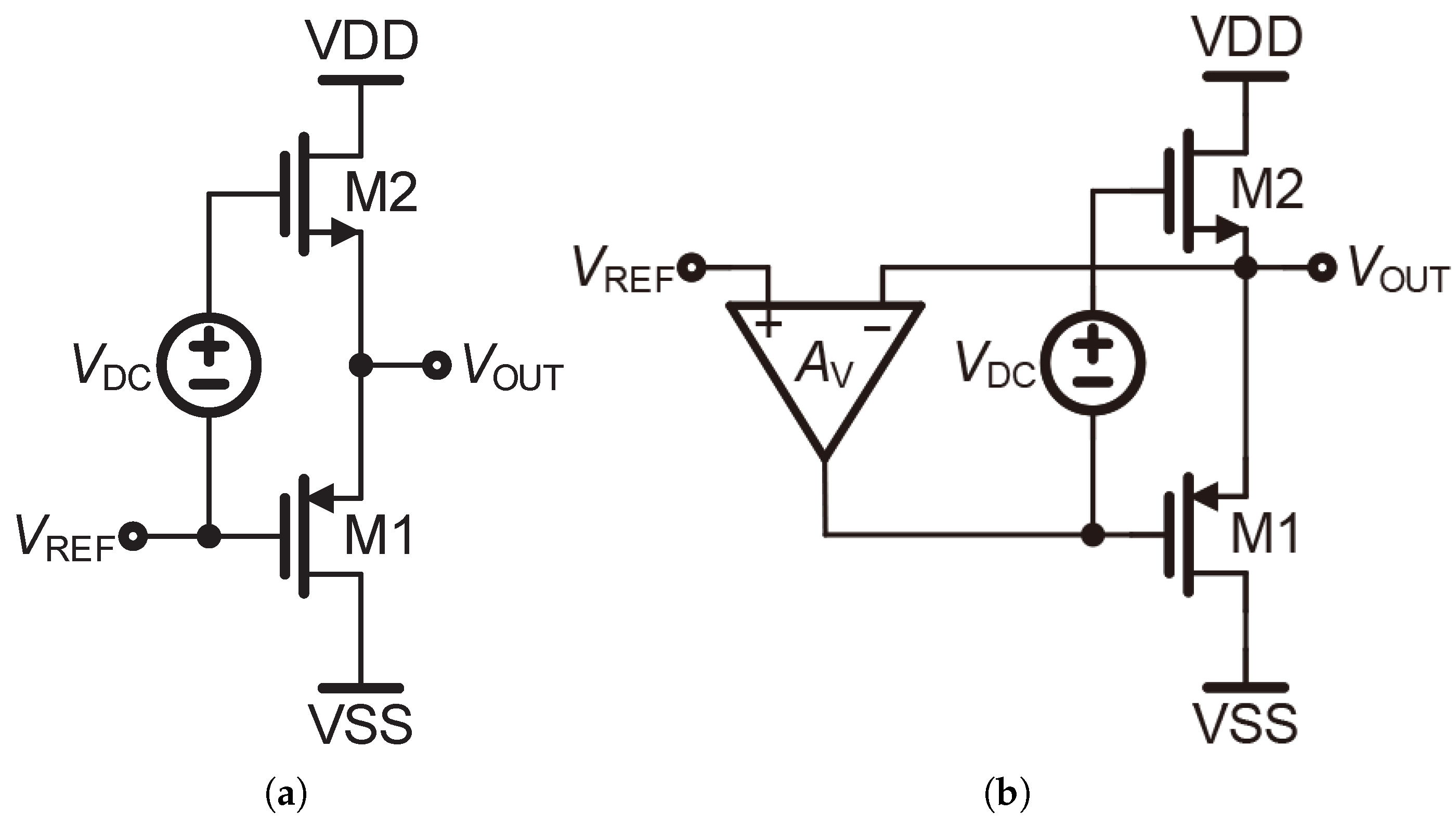

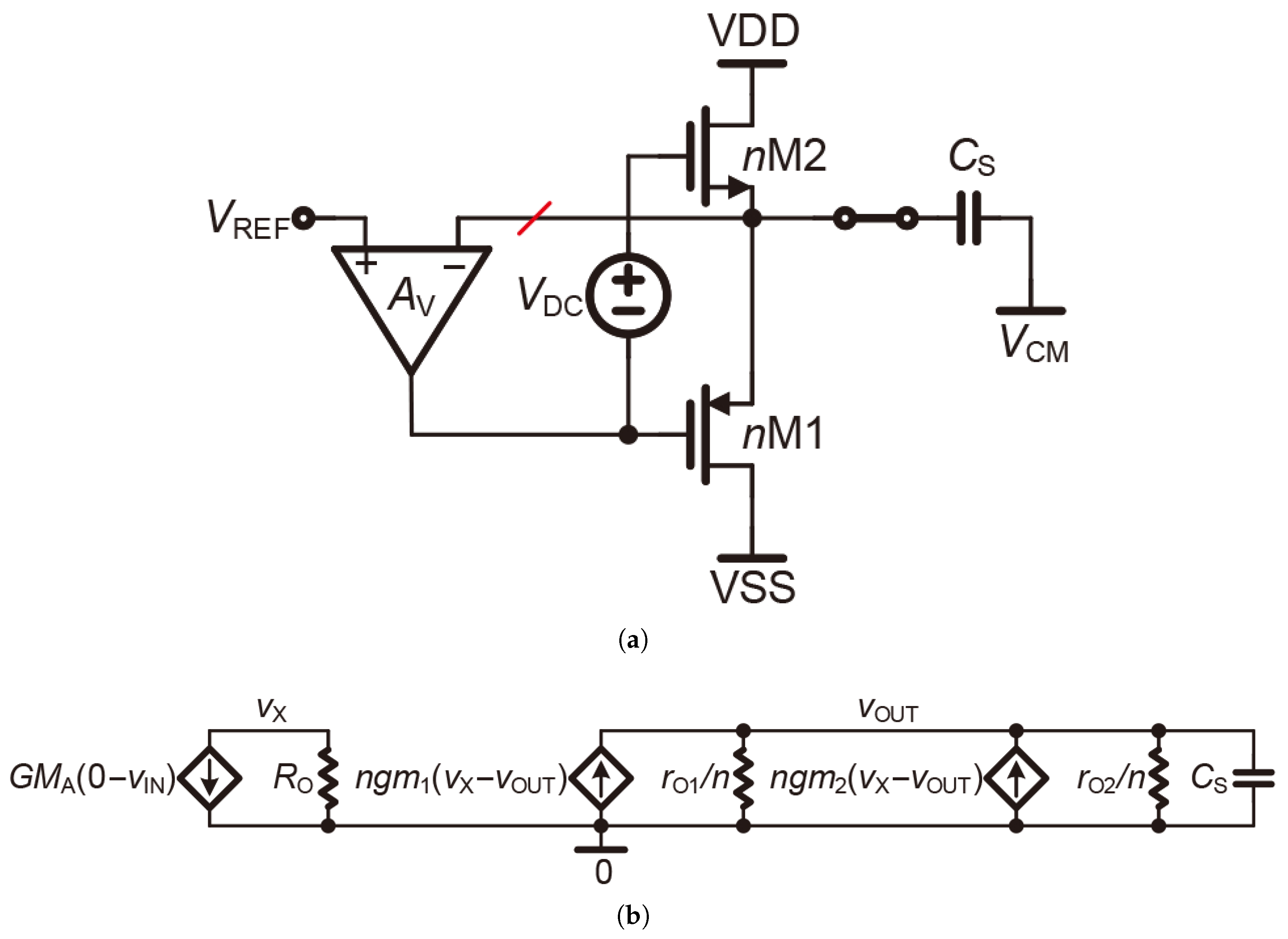

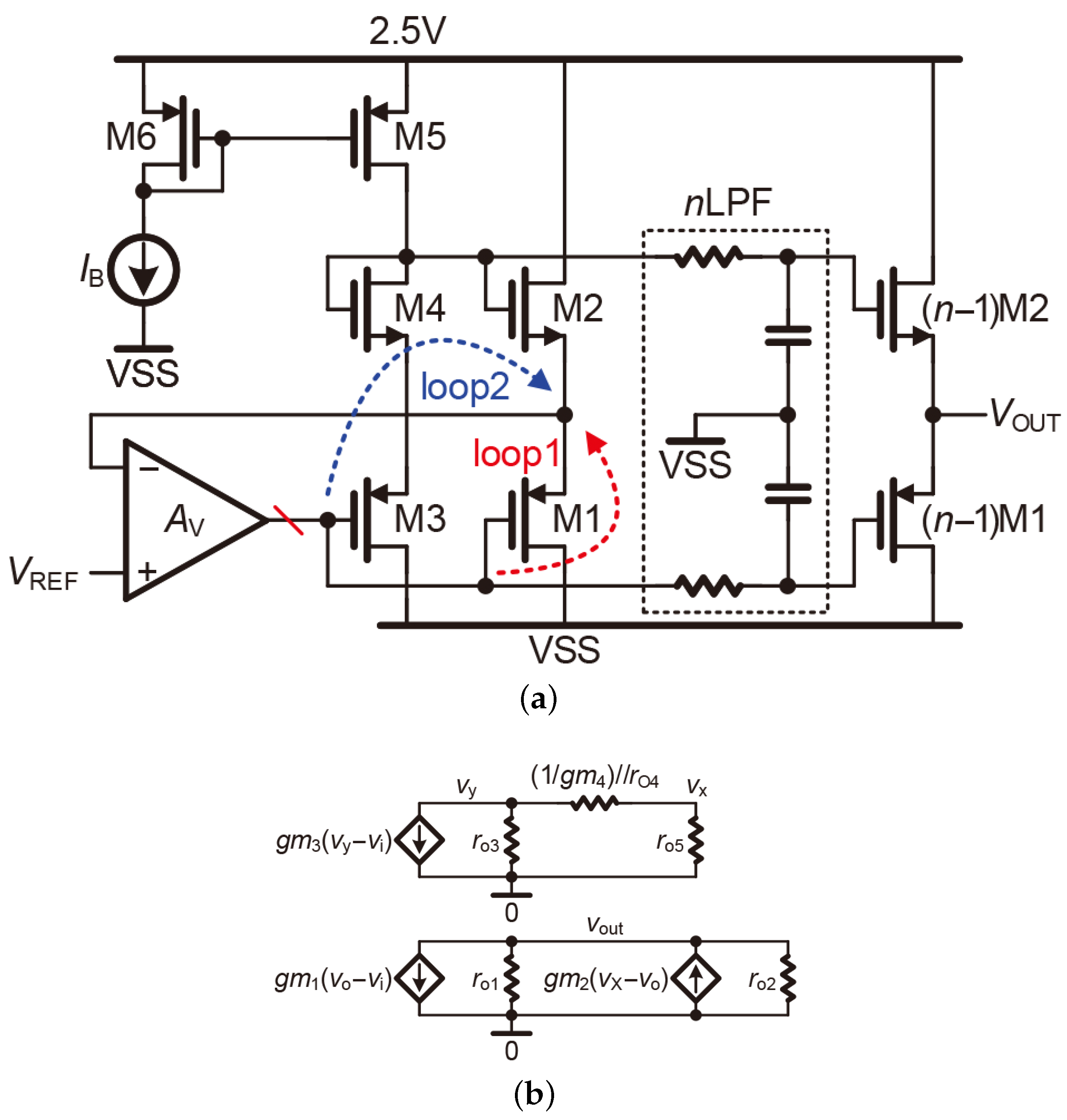

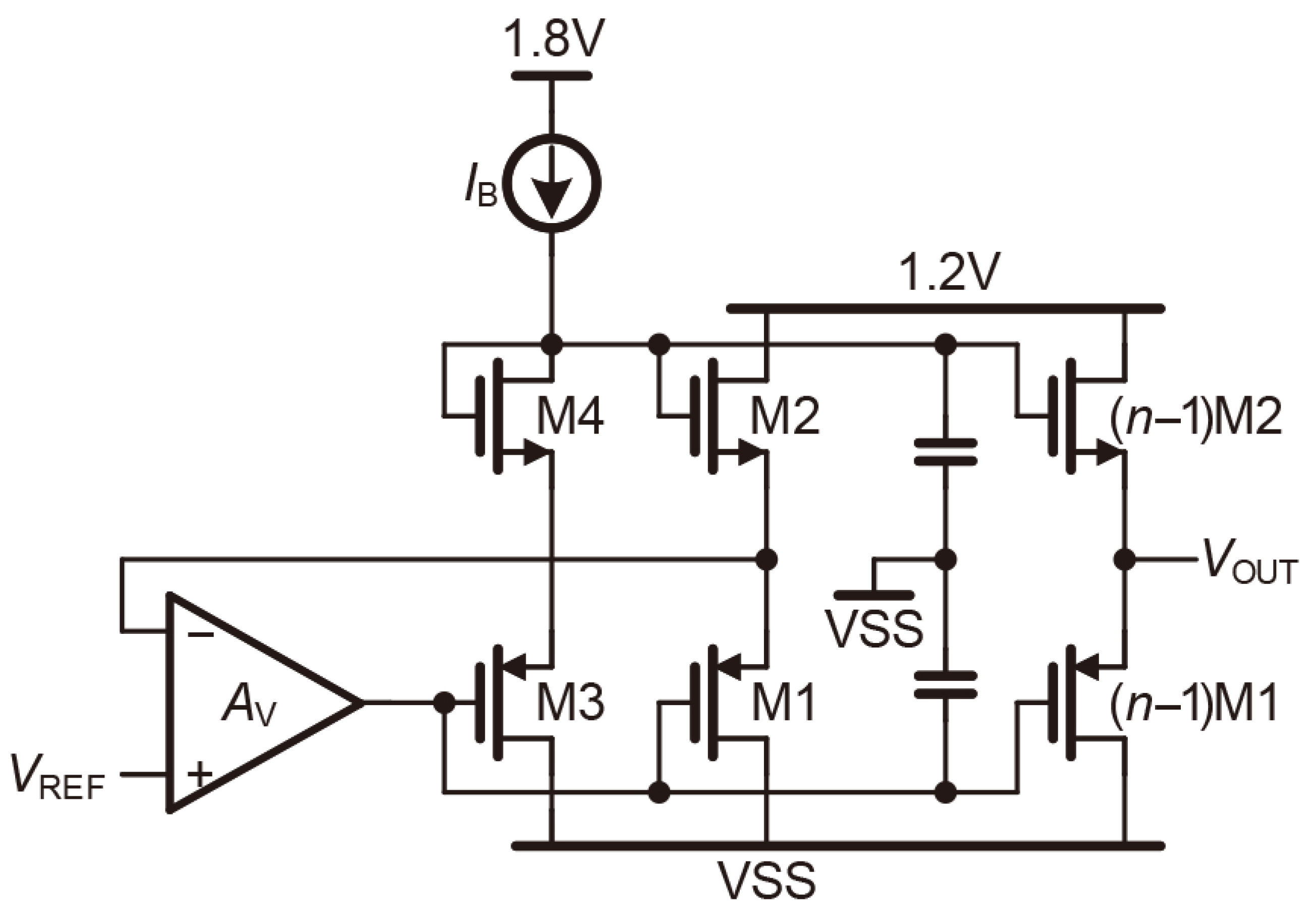

3.1. Circuit Architecture

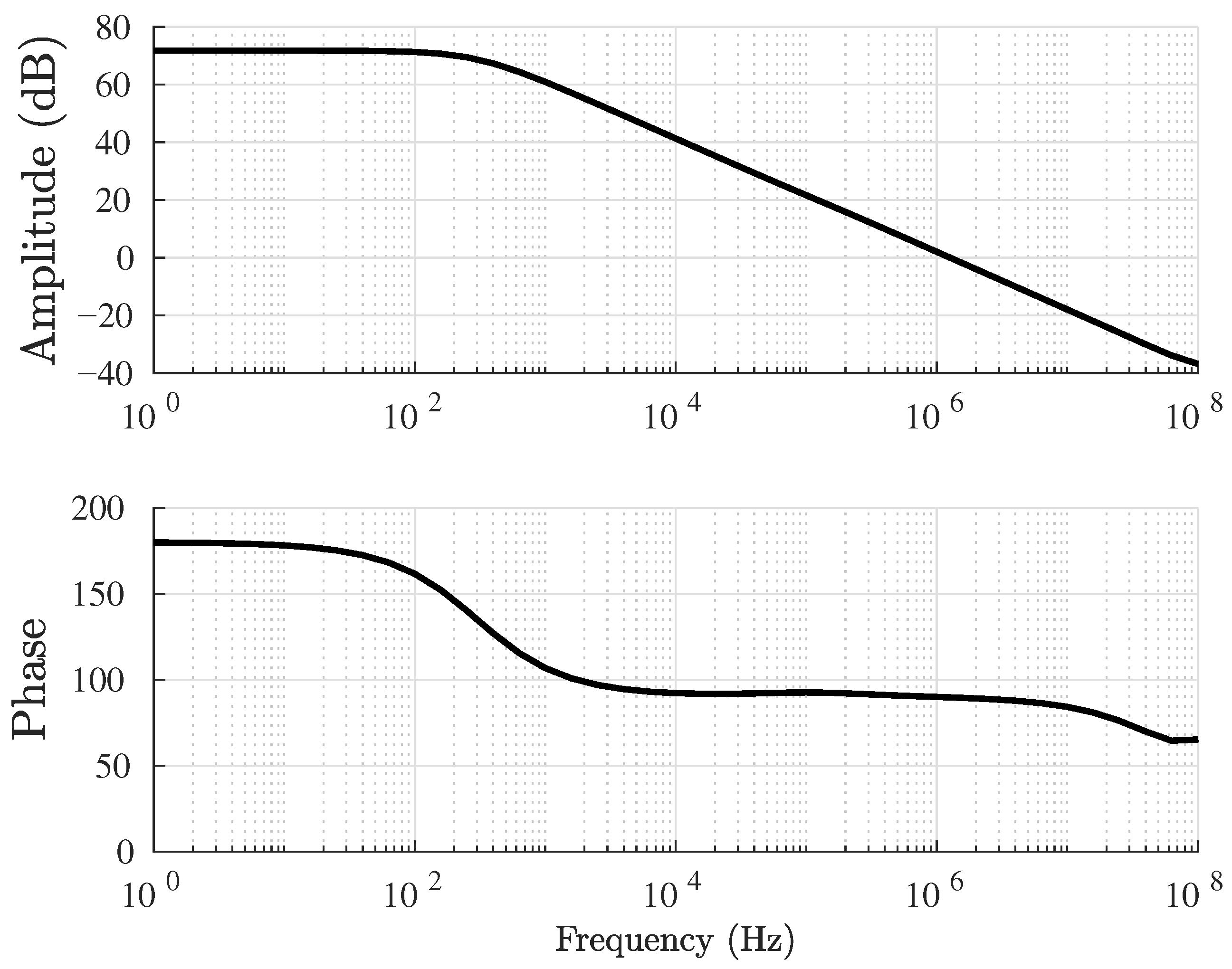

3.2. Loop Stability

4. Simulation Results

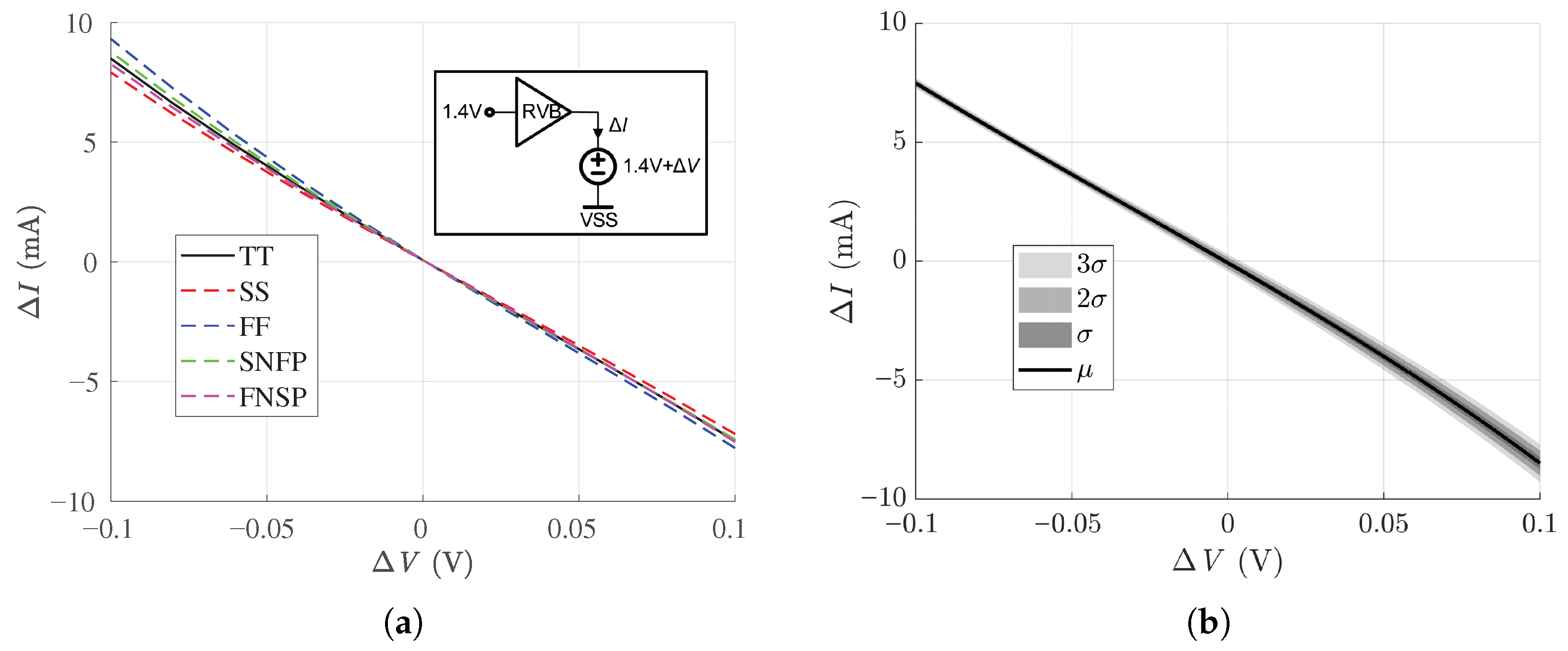

4.1. Driving Capability

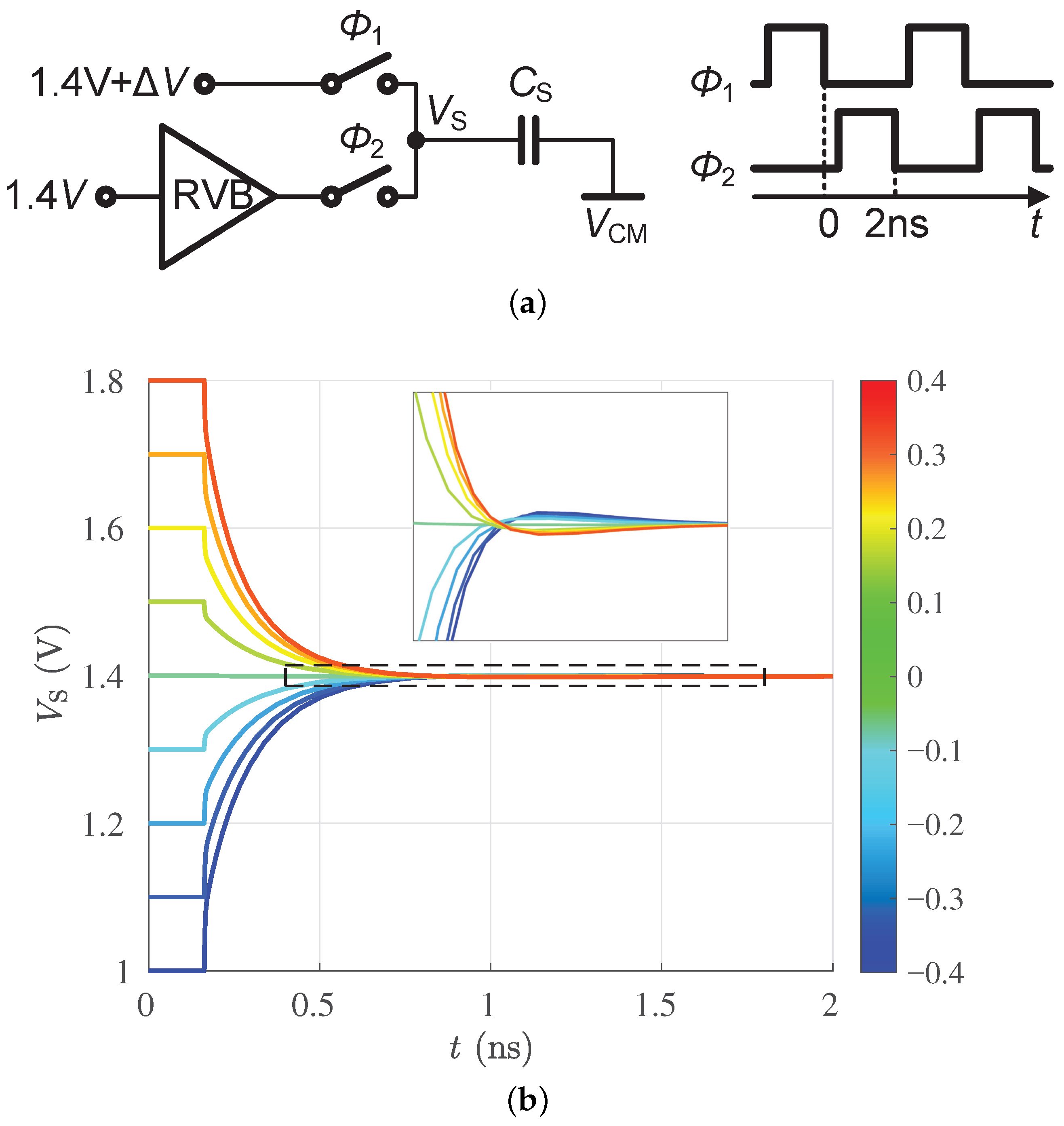

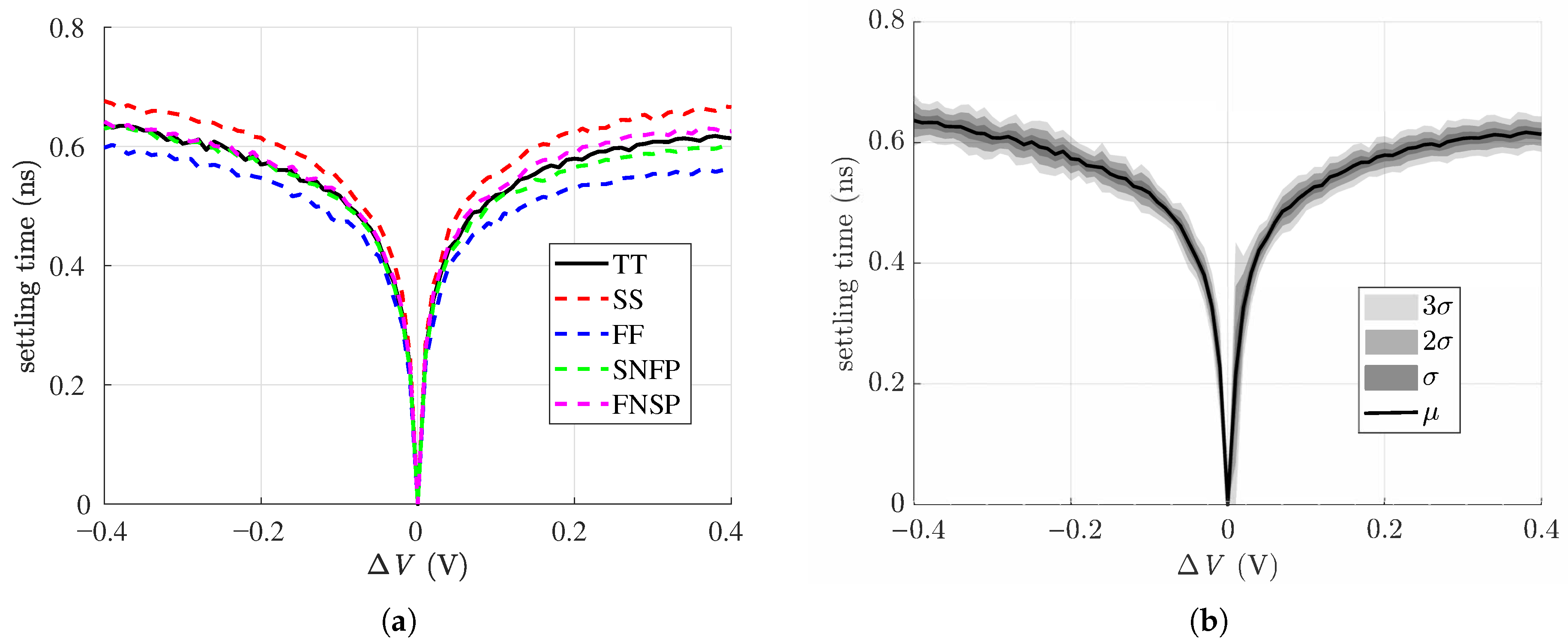

4.2. Transient Response

4.3. Power Supply and Temperature Sensitivities

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Kurose, D.; Ito, T.; Ueno, T.; Yamaji, T.; Itakura, T. 55-mW 200-MSPS 10-bit pipeline ADCs for wireless receivers. IEEE J. Solid-State Circuits 2006, 41, 1589–1595. [Google Scholar] [CrossRef]

- Shibata, H. Continuous-Time Pipelined ADC: A Breed of Continuous-Time ADCs for Wideband Data Conversion. IEEE Open J. Solid-State Circuits Soc. 2023, 3, 162–173. [Google Scholar] [CrossRef]

- Dhiman, S.; Shrimali, H. An MDAC-Less Pipelined ADC for AI-Powered Medical Imaging Applications. IEEE Sens. J. 2024, 24, 39182–39194. [Google Scholar] [CrossRef]

- He, J.; Hu, J.; Liu, S.; Feng, S.; Wang, D. A 12-bit 100-MS/s Pipeline SAR ADC for Professional Medical Field. In Proceedings of the 6th International Conference on Electrical, Electronic Information and Communication Engineering (EEICE), Shenzhen, China, 18–20 April 2025; pp. 487–491. [Google Scholar]

- Kim, K.; Yu, W.; Cho, S. A 9 bit, 1.12 ps Resolution 2.5 b/Stage Pipelined Time-to-Digital Converter in 65 nm CMOS Using Time-Register. IEEE J. Solid-State Circuits 2014, 49, 1007–1016. [Google Scholar] [CrossRef]

- Maatta, K.; Kostamovaara, J. A high-precision time-to-digital converter for pulsed time-of-flight laser radar applications. IEEE Trans. Instrum. Meas. 1998, 47, 521–536. [Google Scholar] [CrossRef]

- Verbruggen, B.; Craninckx, J.; Kuijk, M.; Wambacq, P.; Van der Plas, G. A 2.6 mW 6 bit 2.2 GS/s Fully Dynamic Pipeline ADC in 40 nm Digital CMOS. IEEE J. Solid-State Circuits 2010, 45, 2080–2090. [Google Scholar] [CrossRef]

- Zhu, Y.; Liu, T.; Kaile, S.K.; Kiran, S.; Yi, I.-M.; Liu, R.; Diaz, J.C.G.; Hoyos, S.; Palermo, S. A 38-GS/s 7-bit Pipelined-SAR ADC with Speed-Enhanced Bootstrapped Switch and Output Level Shifting Technique in 22-nm FinFET. IEEE J. Solid-State Circuits 2023, 58, 2300–2313. [Google Scholar] [CrossRef]

- Liu, J.; Hassanpourghadi, M.; Chen, M.S.-W. A 10-GS/s 8-bit 2850-μm2 Two-Step Time-Domain ADC with Speed and Efficiency Enhanced by the Delay-Tracking Pipelined-SAR TDC. IEEE J. Solid-State Circuits 2022, 57, 3757–3767. [Google Scholar] [CrossRef]

- Yu, L.; Miyahara, M.; Matsuzawa, A. A 9-bit 1.8 GS/s 44 mW Pipelined ADC Using Linearized Open-Loop Amplifiers. IEEE J. Solid-State Circuits 2016, 51, 2210–2221. [Google Scholar] [CrossRef]

- Hao, J.; Zhang, M.; Liu, Z.; Zhang, Y.; Liu, S.; Zhu, Z.; Zhu, Y.; Martins, R.P.; Chan, C.-H. An Intrinsically PVT Robust 10-bit 2.6-GS/s Dynamic Pipelined ADC with Dual-Path Time-Assisted Residue Generation Schem. IEEE J. Solid-State Circuits 2025, 60, 2545–2557. [Google Scholar] [CrossRef]

- Zhang, Z.; Hu, Y.; Lang, L.; Dong, Y. A 16 Bit 125 MS/s Pipelined Analog-to-Digital Converter with a Digital Foreground Calibration Based on Capacitor Reuse. Electronics 2024, 13, 1474. [Google Scholar] [CrossRef]

- Wu, J.; Xu, H.; Cao, X.; Liu, T. A 16-Bit 120 MS/s Pipelined ADC Using a Multi-Level Dither Technique. Electronics 2022, 11, 3979. [Google Scholar] [CrossRef]

- Wu, Y.; Ye, F.; Ren, J. A Calibration-Free, 16-Channel, 50-MS/s, 14-Bit, Pipelined-SAR ADC with Reference/Op-Amp Sharing and Optimized Stage Resolution Distribution. Electronics 2022, 11, 749. [Google Scholar] [CrossRef]

- Zhou, X.; He, W.; Su, C.; Liu, T.; Fu, D.; Li, Q. A Low Power 16-bit 125MS/s Pipeline ADC with 100dB SFDR. In Proceedings of the IEEE International Symposium on Circuits and Systems (ISCAS), Singapore, 19–22 May 2024; pp. 1–5. [Google Scholar]

- Cao, H.; Yu, Z.; Deng, H.; Li, P. A reference voltage source and its output buffer for pipeline ADC. In Proceedings of the International Conference on Anti-Counterfeiting, Security and Identification (ASID), Macao, China, 1–3 December 2014; pp. 1–5. [Google Scholar]

- Harikumar, P.; Angelov, P.; Hägglund, R. Design of a reference voltage buffer for a 10-bit 1-MS/s SAR ADC. In Proceedings of the 21st International Conference Mixed Design of Integrated Circuits and Systems (MIXDES), Lublin, Poland, 19–21 June 2014; pp. 185–188. [Google Scholar]

- Carvajal, R.; Ramirez-Angulo, J.; Lopez-Martin, A.; Torralba, A.; Galan, J.; Carlosena, A. The flipped voltage follower: A useful cell for low-voltage low-power circuit design. IEEE Trans. Circuits Syst. I Regul. Pap. 2005, 52, 1276–1291. [Google Scholar] [CrossRef]

- Gagliardi, F.; Catania, A.; Piotto, M.; Bruschi, P.; Dei, M. Parallel Slew-Rate Enhancer with Current-Recycling Core for Switched-Capacitors Circuits. IEEE Trans. Circuits Syst. II Express Briefs 2024, 71, 4814–4818. [Google Scholar] [CrossRef]

- Kapusta, R.; Shinozaki, H.; Ibaragi, E.; Ni, K.; Wang, R.; Sayuk, M.; Singer, L.; Nakamura, K. A 4-channel 20-to300 Mpixel/s analog front-end with sampled thermal noise below kT/C for digital SLR cameras. In Proceedings of the IEEE International Solid-State Circuits Conference—Digest of Technical Papers, San Francisco, CA, USA, 8–12 February 2009; pp. 42–43. [Google Scholar]

- Zhou, Y.; Xu, B.; Chiu, Y. A 12-b 1-GS/s 31.5-mW Time-Interleaved SAR ADC with Analog HPF-Assisted Skew Calibration and Randomly Sampling Reference ADC. IEEE J. Solid-State Circuits 2019, 54, 2207–2218. [Google Scholar] [CrossRef]

- Zhan, M.; Jie, L.; Zhong, Y.; Sun, N. A 10-mW 10-ENoB 1-GS/s Ring-Amp-Based Pipelined TI-SAR ADC with Split MDAC and Switched Reference Decoupling Capacitor. IEEE J. Solid-State Circuits 2023, 58, 3576–3585. [Google Scholar] [CrossRef]

- Kim, I.; Qin, Y. A Fully Integrated FVF Based Low-Noise Voltage Buffer for ADC Reference. In Proceedings of the IEEE 17th International Conference on Solid-State Integrated Circuit Technology (ICSICT), Zhuhai, China, 22–25 October 2024; pp. 1–3. [Google Scholar]

- Park, S.; Son, S.; Chung, W. A rail-to-rail unity gain buffer amplifier for low-cost high resolution TFT LCD panels. IEEE Trans. Consum. Electron. 2009, 55, 2190–2194. [Google Scholar] [CrossRef]

- Yu, Z.; Zhou, J. A 12-bit 1 MS/s SAR ADC with Buffers. In Proceedings of the IEEE 17th International Conference on Anti-counterfeiting, Security, and Identification (ASID), Xiamen, China, 1–3 December 2023; pp. 131–134. [Google Scholar]

- He, W.; Ye, F.; Ren, J. A Fast Response Reference Voltage Buffer for 12b 200 MS/s SAR ADC. In Proceedings of the IEEE 63rd International Midwest Symposium on Circuits and Systems (MWSCAS), Virtual, 9–12 August 2020; pp. 1–4. [Google Scholar]

- Yin, Q.; Bai, C. A CMOS Reference Voltage Buffer Designed for Near-rail Voltage. In Proceedings of the IEEE 5th International Conference on Integrated Circuits and Microsystems (ICICM), Nanjing, China, 23–25 October 2020; pp. 173–176. [Google Scholar]

- Seo, M.; Jin, D.; Kim, Y.; Kim, J.; Ryu, S. A Single-Supply CDAC-Based Buffer-Embedding SAR ADC with Skip-Reset Scheme Having Inherent Chopping Capability. IEEE J. Solid-State Circuits 2020, 55, 2660–2669. [Google Scholar] [CrossRef]

- Liang, Y.; Ding, R.; Zhu, Z. A 9.1ENOB 200 MS/s Asynchronous SAR ADC with Hybrid Single-Ended/Differential DAC in 55-nm CMOS for Image Sensing Signals. IEEE Sens. J. 2018, 18, 7130–7140. [Google Scholar] [CrossRef]

- He, W.; Li, Z.; Ye, F.; Ren, J. A Low Power Reference Voltage Buffer and High Density Unit capacitor in a 12b 200 MS/s SAR ADC. In Proceedings of the IEEE Asia Pacific Conference on Circuits and Systems (APCCAS), Ha Long, Vietnam, 8–10 December 2020; pp. 82–85. [Google Scholar]

- Li, W.; Li, F.; Yang, C.; Li, M.; Wang, Z. A power-efficient reference buffer with wide swing for switched-capacitor ADC. Microelectron. J. 2015, 46, 410–414. [Google Scholar] [CrossRef]

- Lee, C.-K.; Kim, W.; Kang, H.; Ryu, S.-T. A Replica-Driving Technique for High Performance SC Circuits and Pipelined ADC Design. IEEE Trans. Circuits Syst. II Express Briefs 2013, 60, 557–561. [Google Scholar] [CrossRef]

| TT | SS | FF | SNFP | FNSP | 1000-Run MC () | 1000-Run MC () | |

|---|---|---|---|---|---|---|---|

| PSRR@1 Hz (dB) | 128.9 | 128.86 | 128.26 | 129.47 | 128.37 | 123.3 | 5.13 |

| PSRR@1 kHz (dB) | 107.25 | 107.46 | 108.59 | 108.06 | 106.45 | 99.57 | 2.61 |

| PSRR@1 MHz (dB) | 59.6 | 60.01 | 59.19 | 60.2 | 59.05 | 59.69 | 0.23 |

| This Work | ASID 2014 [16] | MIXDES 2014 [17] | TCAS-II 2013 [32] | JSSC 2023 [22] | JSSC 2019 [21] | ICSICT 2024 [23] | APCCAS 2020 [30] | |

|---|---|---|---|---|---|---|---|---|

| Techn. (nm) | 180 | 180 | 180 | 65 | 28 | 65 | 180 | 28 |

| (V) | 1.8 | 1.8 | 1.8 | 1.2 | 1.2 | 2.5 | 5 | 1 |

| (V) | 1.4 | 0.5 | 0.5 | N/A | 1 | 1.2 | 2.5 | 0.75 |

| RVB power (mW) | 4.5 | N/A | 0.12 | 16.8 | 3.7 | N/A | 0.056 | 2.4 |

| Settling time (ns) | 0.68 | 1.549 | 19.3 | N/A | 0.05 | N/A | 1810 | 0.115 |

| Load Cap. (pF) | 9 | N/A | 3.7 | 4 | 1 | 2 | 0–20 | 2 |

| PSRR (dB) | 128.9 (1 Hz) | 107.3 (1 Hz) | 72 | N/A | ∼43 (3 GHz) | N/A | N/A | N/A |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2026 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license.

Share and Cite

Zeng, L.; Wang, M.; Yin, R.; Gu, Y.; Zhang, Y.; Tang, Z. A Class-AB Reference Voltage Buffer for SC Circuits in Pipelined ADCs. Electronics 2026, 15, 547. https://doi.org/10.3390/electronics15030547

Zeng L, Wang M, Yin R, Gu Y, Zhang Y, Tang Z. A Class-AB Reference Voltage Buffer for SC Circuits in Pipelined ADCs. Electronics. 2026; 15(3):547. https://doi.org/10.3390/electronics15030547

Chicago/Turabian StyleZeng, Li, Ming Wang, Rui Yin, Yanhan Gu, Yuxing Zhang, and Zhangwen Tang. 2026. "A Class-AB Reference Voltage Buffer for SC Circuits in Pipelined ADCs" Electronics 15, no. 3: 547. https://doi.org/10.3390/electronics15030547

APA StyleZeng, L., Wang, M., Yin, R., Gu, Y., Zhang, Y., & Tang, Z. (2026). A Class-AB Reference Voltage Buffer for SC Circuits in Pipelined ADCs. Electronics, 15(3), 547. https://doi.org/10.3390/electronics15030547