Abstract

Ultralow-voltage (ULV) CMOS will be a core building block of highly energy efficient electronics. Although the operation at the minimum energy point (MEP) is effective for ULP CMOS circuits, its slow operation speed often means that it is not used in many applications. The silicon-on-thin-buried-oxide (SOTB) CMOS is a strong candidate for the ultralow-power (ULP) electronics because of its small variability and back-bias control. Proper power and performance optimization with adaptive Vth control taking advantage of SOTB’s features can achieve the ULP operation with acceptably high speed and low leakage. This paper describes our results on the ULV operation of logic circuits (CPU, SRAM, ring oscillator and other logic circuits) and shows that the operation speed is now sufficiently high for many ULP applications. The “Perpetuum-Mobile” micro-controllers operating down to 0.4 V or lower are expected to be implemented in a huge number of electronic devices in the internet-of-things (IoT) era.

1. Introduction: Issues for ULV Operation Possibly Staying on MEP Point

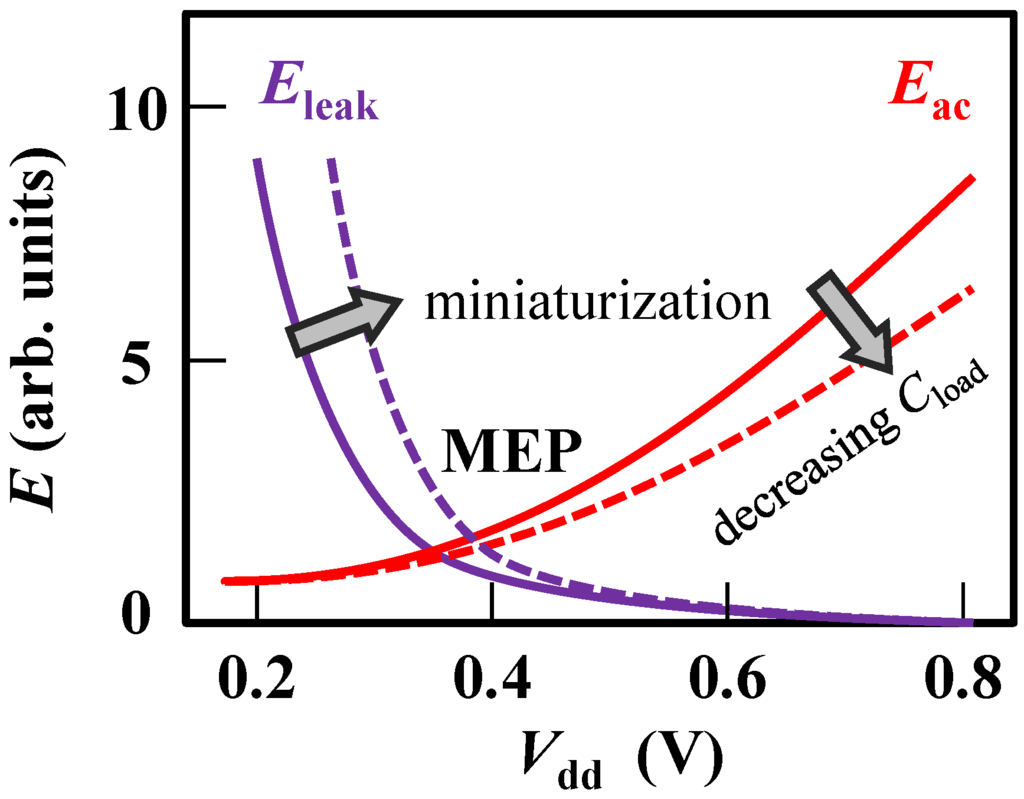

A huge number of small electronic devices composing big data are expected to be used across the globe as the “internet of things” (IoT). The CMOS integrated circuit is a core part of these devices. The energy efficiency of the CMOS circuits should therefore be greatly improved. It is well known that the operating voltage (Vdd) is a primarily important parameter for reducing the energy per operation cycle in the CMOS circuits. As shown in Figure 1, the energy is a sum of active (Eac) and leakage (Eleak) energy as shown in Equation (1) in the simplified form.

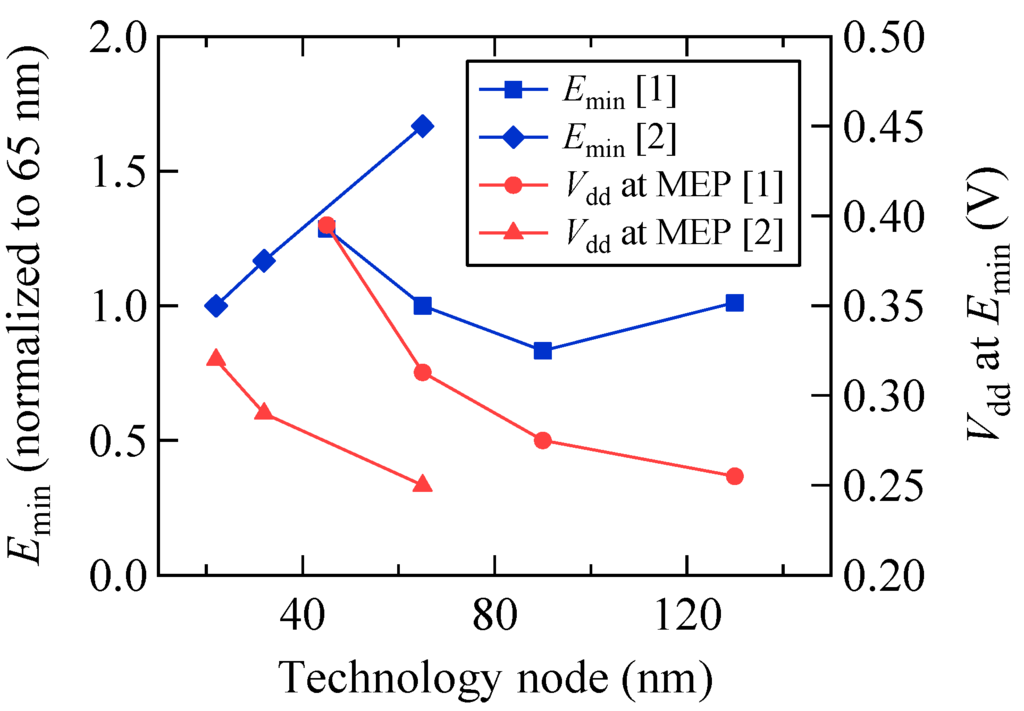

where Cload, Ileak, a, and f denote load capacitance, leakage current, activity, and frequency, respectively. With decreasing Vdd, Eac decreases since it is proportional to CloadVdd2. However, Eleak relatively increases as f decreases with decreasing Vdd. These two terms determine the minimum energy point (MEP). The energy efficiency of CMOS circuits has been greatly improved by the miniaturization of CMOS transistors. This improvement is mainly accomplished by Eac reduction due to Cload reduction with the transistor scaling. However, most of the circuits do not operate at MEP and the improvement in terms of the efficiency has not been perfect so far. In recent generations, the scaling has increased the Vdd at MEP, as shown in Figure 2 [1,2]. This is because Eleak tends to increase with the miniaturization that has been seen in recent generations, especially for the performance-oriented applications. In the energy-efficiency conscious design like [1], the Emin has already an increasing trend (minimum point of Emin at 90-nm node), as shown in Figure 2.

E = Eac + Eleak = CloadVdd 2 + IleakVdd / af

The near- or sub-Vth operation is attractive to improve the energy efficiency. The operating speed of these circuits, however, is not high. The maximum frequency rapidly drops with decreasing Vdd in the conventional CMOS [3]. In the device design for ULP circuits, it is important to optimize both Vdd and Vth. With decreasing Vdd, Vth should increase to minimize the energy [4]. This drastically decreases the frequency and in many cases the MEP operation is a sub-Vth operation and its frequency is less than MHz. The variable Vth approach with adaptive back-bias control can mitigate the situation: optimizing frequency and decreasing energy as low as possible down to the MEP value. Both Vdd and Vth are controlled to minimize the energy, while satisfying the required workload: required frequency. In the dynamic voltage and frequency scaling (DVFS), only Vdd is controlled. In order to achieve higher energy efficiency, the control of Vth should be accompanied.

Figure 1.

Schematic relationship between energy per operation E versus operating voltage Vdd.

Figure 2.

Minimum energy Emin and Vdd at MEP as a function of technology node number after [1,2].

It is well known that the characteristic variability of transistors is recognized as a major obstacle for the performance/power tradeoff, especially at low Vdd. The increasing variability also increases Vdd at MEP [5] simply because of the increase in leakage current in a circuit that is a sum of transistor leakages [6]. Moreover, increasing the transistor variation causes delay variation, especially at low Vdd and causes a significant performance drop [7]. Design to cope with the increasing variability at low Vdd becomes more complex. The variability tolerant design prefers to increase the transistor width W; however, this directly increases the power [8,9]. Another variability tolerant logic design prefers a smaller number of pipeline stages and longer logic depth. However, these design strategies decrease the frequency [10,11] and increase Emin.

We hypothesize the main issues for the highly energy efficient CMOS circuits are adaptive Vth control and small variability, as described in this section. In order to solve these issues, we are developing the silicon on thin buried oxide (SOTB) [12,13,14,15,16]. In this article, we show SOTB’s low voltage capability, including small variability and back-bias control through device and circuit results.

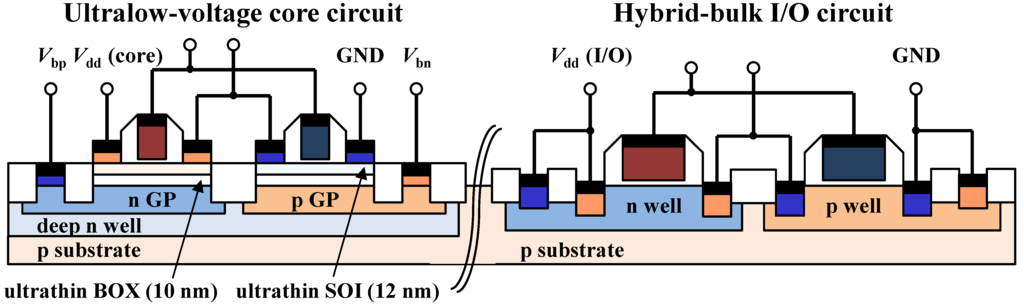

2. SOTB Device Technology

Schematic cross section of the SOTB is shown in Figure 3. There are four major factors: (i) small local variability due to low-impurity fully depleted SOI channel; (ii) high back-bias coefficient due to thin BOX layer and doped ground plane (n GP and p GP) just below the BOX layer; (iii) flexible Vth tuning by impurity density control of the ground plane and (iv) high design compatibility with the conventional CMOS due to mostly identical planar layout to the bulk and a hybrid bulk integration for I/O. Details of the SOTB fabrication process are reported elsewhere [15,16].

Figure 3.

Schematic cross section of silicon on thin buried oxide (SOTB) and hybrid bulk transistors. Vbp and Vbn denote back-bias terminal for p- and n-type SOTB, respectively.

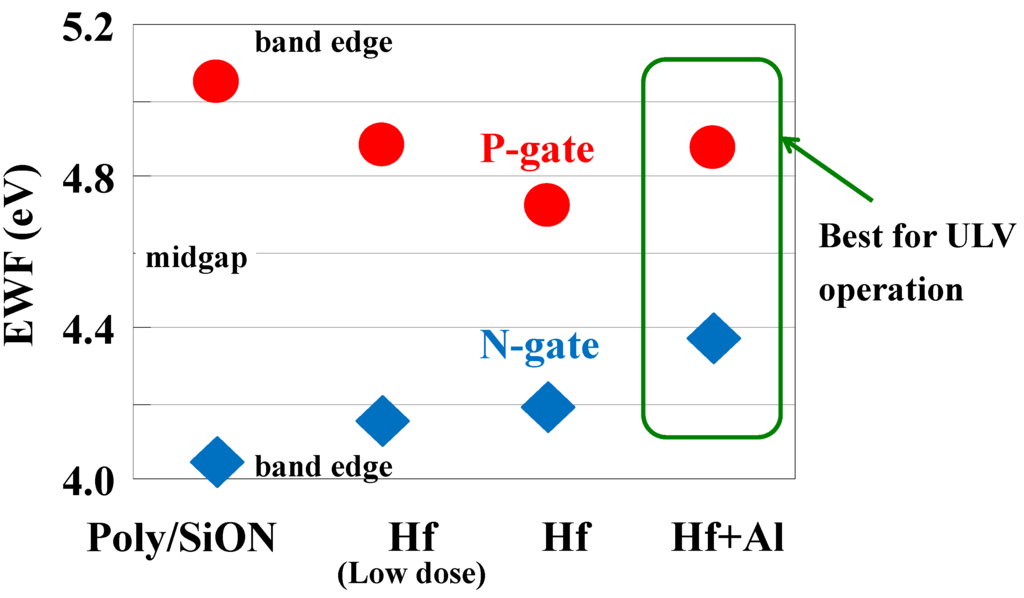

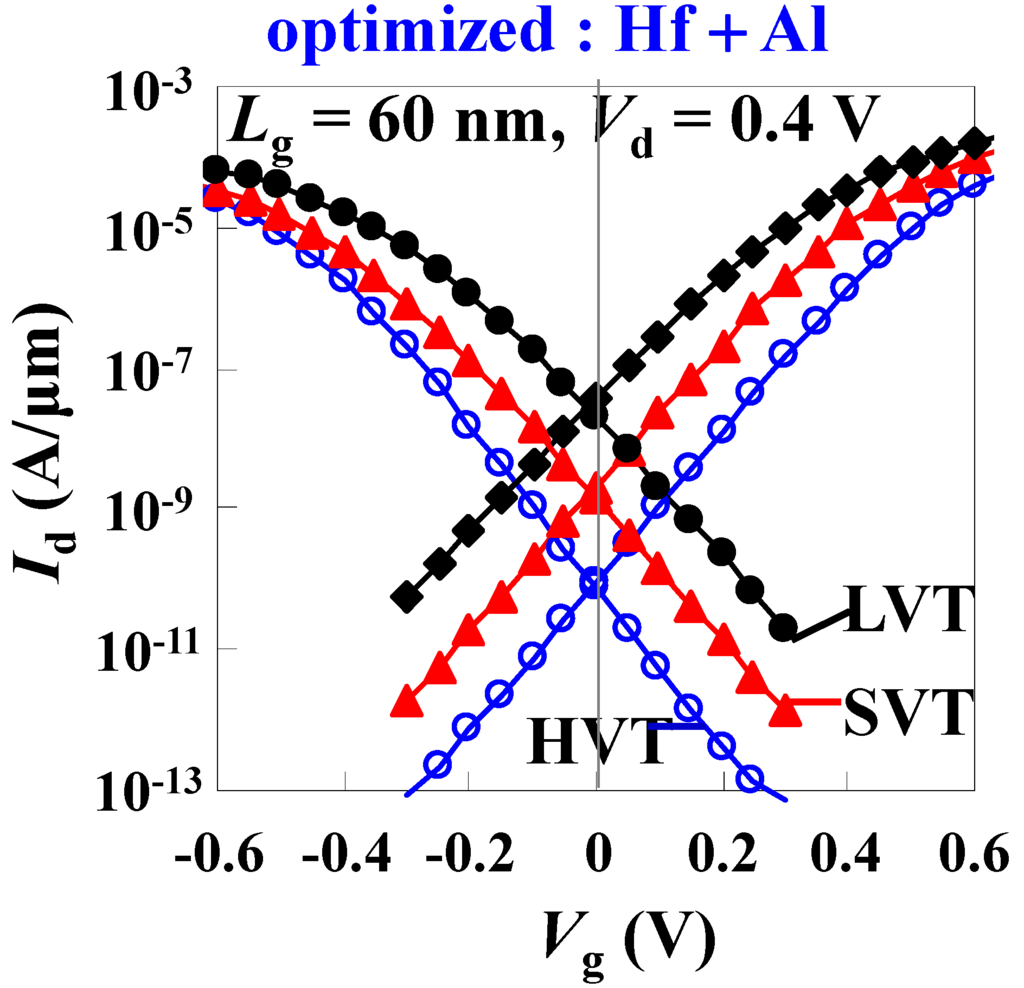

Vth control optimized for the ULV operation has been an important process issue. In this optimization, we controlled the Vth values at around 0.2 V, which is by about 0.2 V lower than that for the low-standby-power (LSTP) application, with the multiple Vth option utilizing a poly-silicon and high-k gate-stack technology and a proper doping profile control of the ground plane [15]. As shown in Figure 4, we utilize a small amount of high-k (Hf and Al) oxide mixed with the conventional SiON gate dielectric and control proper effective work function (EWF) both for NMOS and PMOS. Typical Id-Vg characteristics of triple Vth option are shown in Figure 5. LVT, SVT, and HVT denote low, standard, and high Vth option, respectively. Two-orders-of-magnitude off-leakage-current variation can be done only by changing the doping density below the BOX layer with the same gate stack.

Figure 4.

Effective work function (EWF) control with high-k/SiON gate stack [15]. Circles and diamonds represent EMF of P-type and N-type gate stacks for PMOS and NMOS, respectively.

Figure 5.

Id-Vg characteristics of triple Vth option controlled by ground plane doping [15].

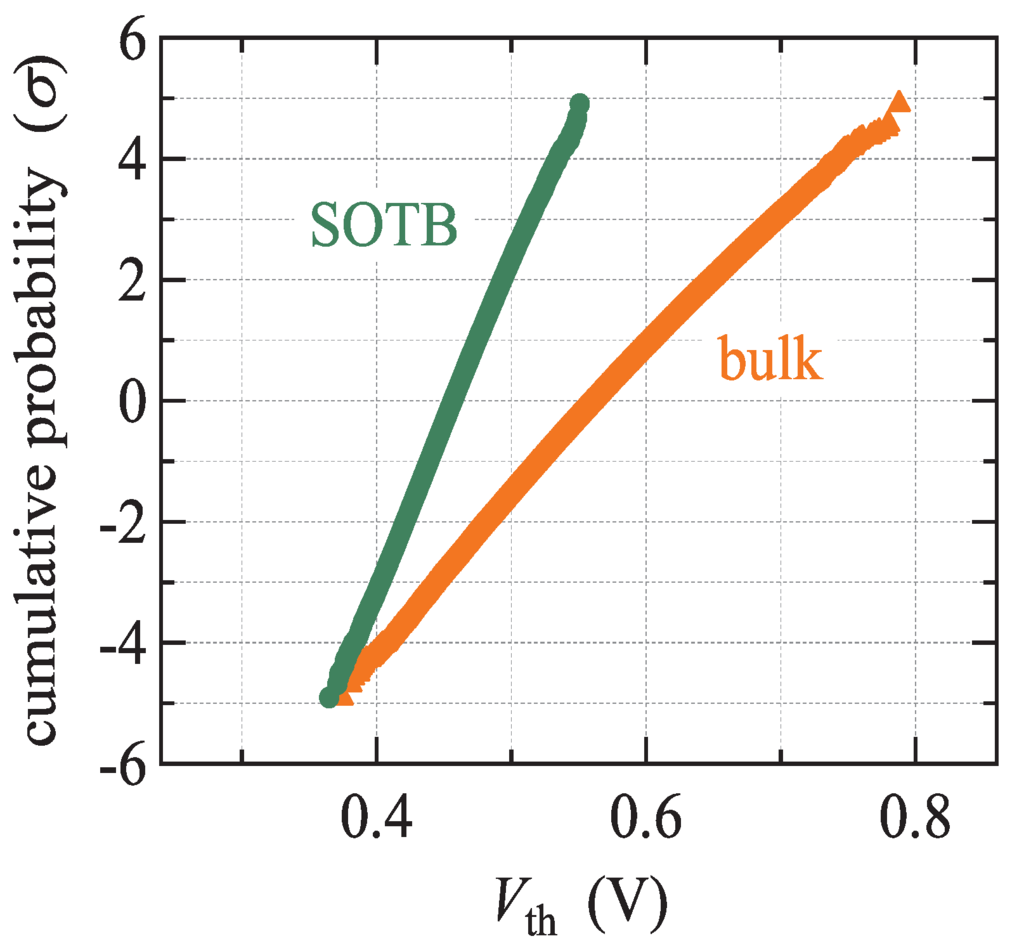

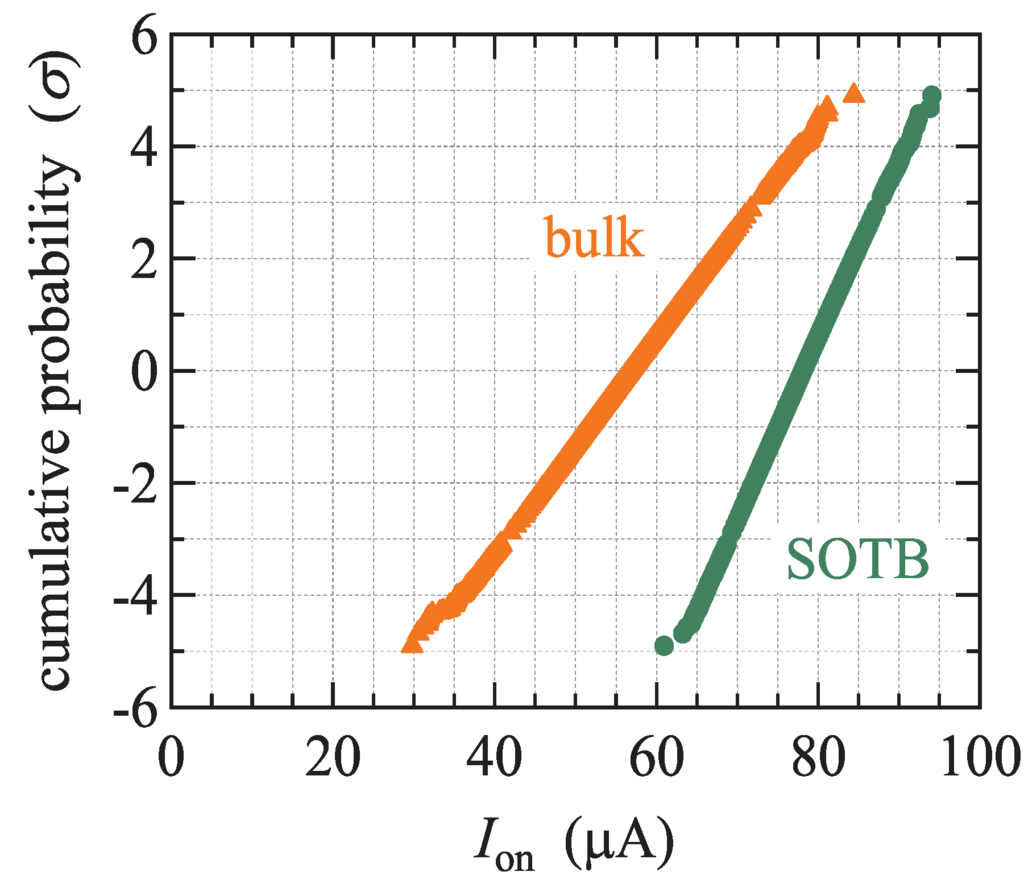

We have demonstrated significant reduction of the Vth variability. The Pelgrom coefficient (AVT) of the SOTB was about 1.2–1.3 mVμm [16], which is less than half of the bulk. Moreover, we measured the Vth variation of one-million transistors (gate length and width: 0.06 and 0.14 μm, respectively) [16] as shown in Figure 6 and confirmed regular distribution without dropout transistors. Variation of on-state current Ion is important and must be decreased since this directly affects the delay variation of circuits. The Ion variation was demonstrated to be less than half of bulk [17] and we confirmed a significant reduction of the Ion variability for one-million transistors as shown in Figure 7 [16]. The lowest Vth values of SOTB and bulk are the same as shown in Figure 6. This means the highest leakage current among one-million transistors is the same. Besides, the highest Vth transistor determines the delay. As shown in Figure 7, the smallest Ion value for SOTB is about twice as high as the bulk’s worst value. This is a strong advantage of SOTB’s small variability in terms of the circuit performance.

Figure 6.

Vth distribution of 1 M transistors. [16] Vertical-axis value shows deviation from Vth median value. Positive or negative σvalues indicate that the corresponding Vth value is upper or below median, respectively.

Figure 7.

Ion distribution of 1 M transistors [16].

3. ULV Operation of SOTB Circuits

3.1. Vmin Reduction of 6T-SRAM and Leakage Control by Back-Bias

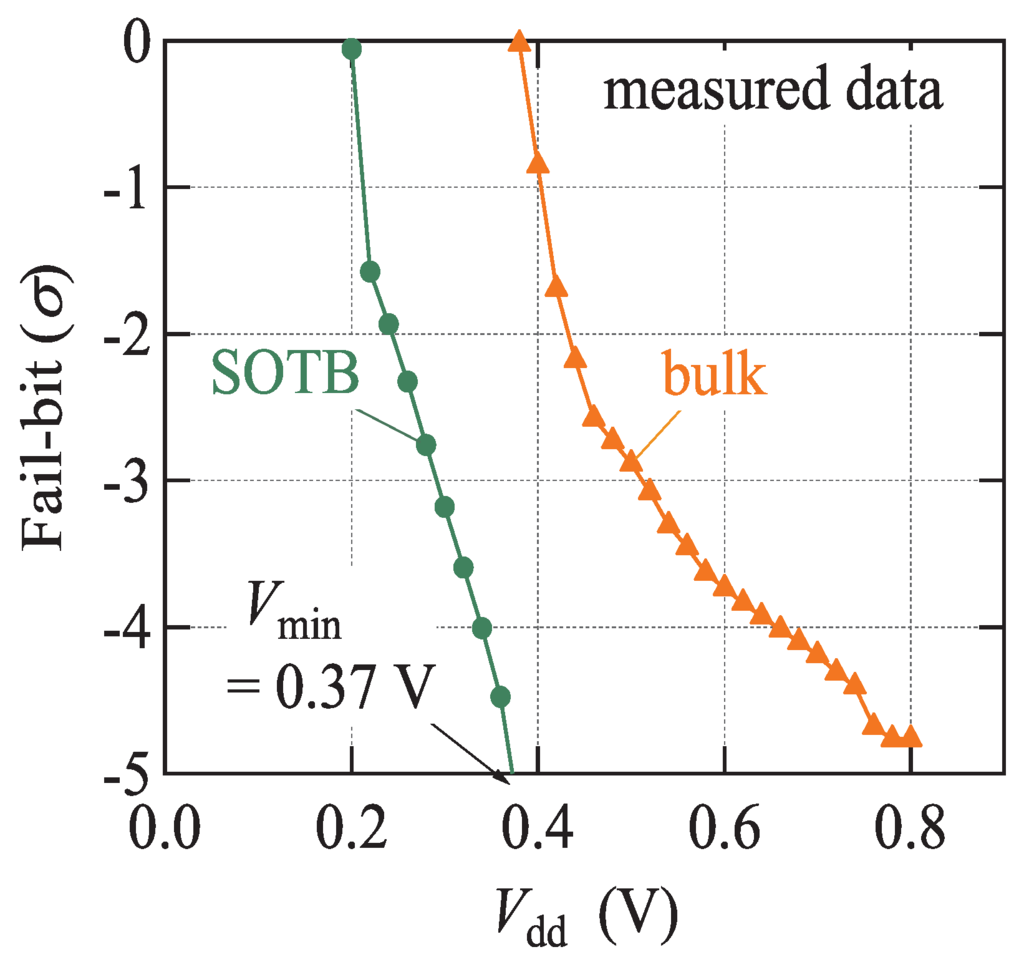

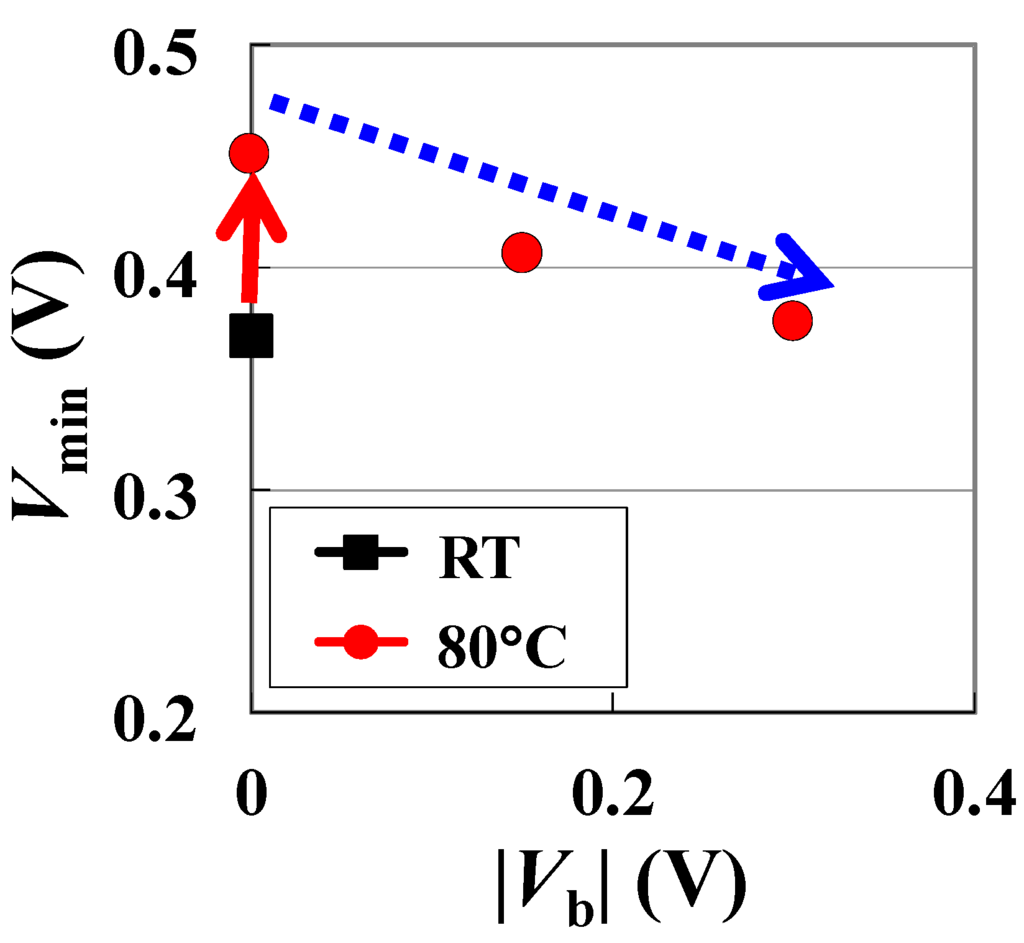

Thanks to the significant reduction of the variability, as shown in Figure 6 and Figure 7, we successfully demonstrated 2-Mbit SRAM operation at Vmin = 0.37 V [16] of the standard six-transistor (6T) layout and without assist circuits as shown in Figure 8. Due to the Vth optimization mentioned in the previous section, very small access time (5.5 ps at Vdd = 0.4 V) was demonstrated. This enables a circuit operation with SRAM at several tens of MHz. The standby leakage decreased more than two orders of magnitude by a reverse back biasing and achieved 1.2 pA/cell without destroying the data. Moreover, the above Vmin value can be kept at lower at elevated temperatures with a proper back-bias control. In Figure 9, the Vmin value at room temperature was the same as the value shown in Figure 8. At 80 °C, the Vmin value increased to 0.46 V. This is because the Vth values of NMOS and PMOS transistors differently shifted from the room-temperature values. Although these Vth values were smaller than the room-temperature values (this increased the leakage current about two orders of magnitude higher than that at room temperature), balance of Vths (current drivabilities) between the NMOS and PMOS transistors untuned. This deteriorated the SRAM cell stability and increased the Vmin. By applying proper back-bias voltages for both transistors, the Vmin value again reduced to less than 0.4 V as shown in Figure 9. Leakage current also can be minimized by the back-bias control regardless of temperature, which is roughly the same as the room-temperature value.

3.2. Ring Oscillator Circuit Results

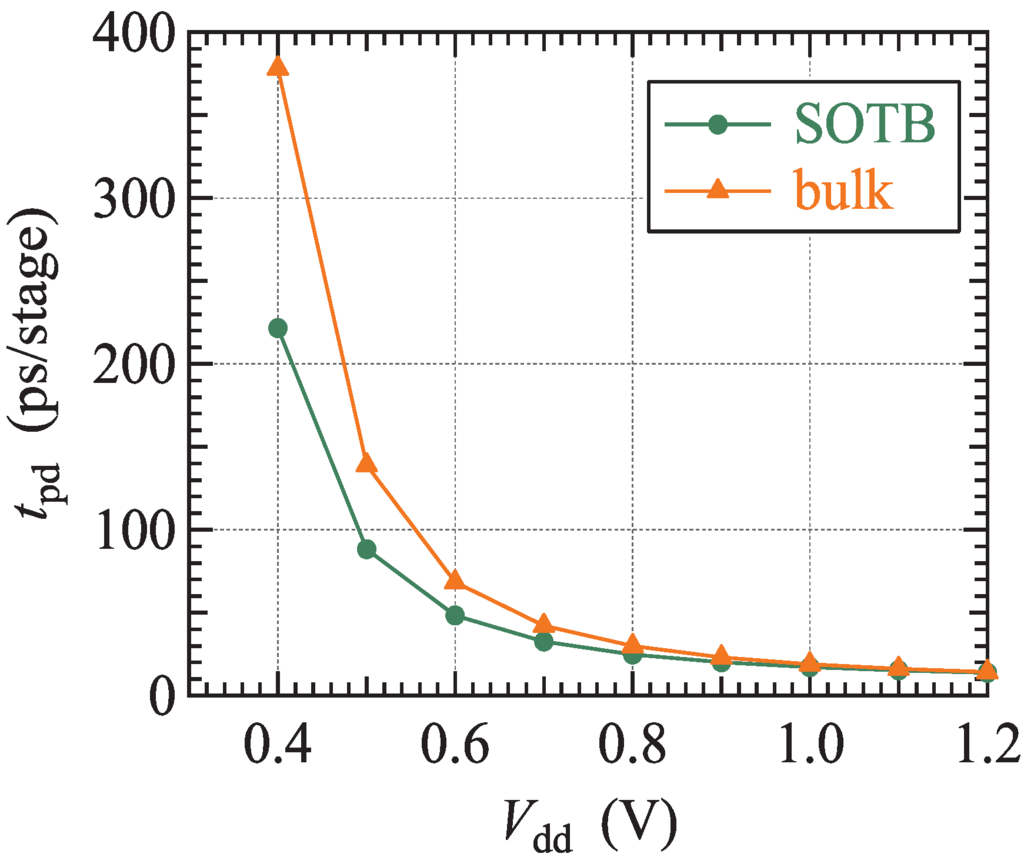

We have developed a standard logic cell library of the SOTB technology with a hybrid bulk I/O library. The delay characteristics of the cells were evaluated through the RO measurements [18]. Figure 10 shows propagation delay tpd of a 101-stage inverter RO for SOTB and bulk. The delay of SOTB was by 42% smaller than bulk at Vdd = 0.4 V. Note that Vths of SOTB and bulk were the same at Vdd = 0.4 V. The speed gain of SOTB was higher at lower Vdd because of better Ieff/Ioff and smaller DIBL. The delay variability was then investigated. The standard deviation of tpd for SOTB exhibited a very weak  dependence. The result means that the local delay variability of SOTB is very small. We also succeeded in the significant reduction of die-to-die delay variability by a proper back-biasing [19]. The logic circuits contain various types of logic cells such as inverter, NAND, NOR, etc. We found that back-biasing considering a drivability balance of NMOS and PMOS transistors is essential for an effective suppression of die-to-die delay variability for various types of the cells.

dependence. The result means that the local delay variability of SOTB is very small. We also succeeded in the significant reduction of die-to-die delay variability by a proper back-biasing [19]. The logic circuits contain various types of logic cells such as inverter, NAND, NOR, etc. We found that back-biasing considering a drivability balance of NMOS and PMOS transistors is essential for an effective suppression of die-to-die delay variability for various types of the cells.

dependence. The result means that the local delay variability of SOTB is very small. We also succeeded in the significant reduction of die-to-die delay variability by a proper back-biasing [19]. The logic circuits contain various types of logic cells such as inverter, NAND, NOR, etc. We found that back-biasing considering a drivability balance of NMOS and PMOS transistors is essential for an effective suppression of die-to-die delay variability for various types of the cells.

dependence. The result means that the local delay variability of SOTB is very small. We also succeeded in the significant reduction of die-to-die delay variability by a proper back-biasing [19]. The logic circuits contain various types of logic cells such as inverter, NAND, NOR, etc. We found that back-biasing considering a drivability balance of NMOS and PMOS transistors is essential for an effective suppression of die-to-die delay variability for various types of the cells.

Figure 8.

Fail-bit count of 2-M bit SRAM array as a function of Vdd [16].

Figure 9.

Vmin of 2-M bit SRAM array as a function of back-bias voltage |Vb|: absolute values of back-bias voltage for NMOS and PMOS, |Vb| = |Vbn| = |Vbp|.

The minimum energy consumption of SOTB logic circuits of 50 kgates was estimated based on the RO results by optimizing the back-bias voltage [20]. At the same energy per operation, SOTB operates about ×10 higher than bulk. The power consumption of 44 μW at 10 MHz (4.4 pJ/cycle) is expected at Vdd = 0.33 V whereas bulk operates at 1 MHz with the same energy per cycle as SOTB.

Figure 10.

Inverter delay tpd as a function of Vdd [18].

3.3. Demonstration of ULV and ULP Operation of Logic Circuits

The design flow for the SOTB integrated circuits is basically the same as the conventional one. Using our newly developed design flow with the SOTB/bulk hybrid library, several ULV circuits were designed. Significant power reduction was demonstrated by the post-layout timing and power analysis. The reconfigurable accelerator named cool mega array (CMA) was designed and silicon results were obtained [21]. The bulk CMA operates at 0.8–1.2 V (with dynamic voltage scaling) and 210 MHz, and the SOTB version operates at 0.4 V (with back-biasing) and 65 MHz. The energy efficiency executing the Alpha blender test program was 38 and 65 MOPS/mW for bulk and SOTB, respectively.

The back-bias control offers a strong advantage for the FPGA circuits. The flex-power FPGA of the SOTB version was firstly implemented and silicon results were obtained [22]. After the FPGA configuration, the back-bias control enables that the only critical-path logic elements are set to low Vth. This significantly reduces the leakage power with no operation speed penalty.

High-efficiency generator of back-bias voltage is important for the SOTB technology since standby leakage current is kept low by applying reverse back-bias voltage. A superior point of the SOTB technology is that current load of the back-bias generator is very small because back-gate region of the SOTB transistor is electrically isolated by the BOX layer. This leads to a significant reduction of current consumption of the back-bias generator itself. We designed the generator circuit using the standard Dickson’s charge pump for the SOTB and bulk hybrid platform and silicon results were obtained [23]. The generator operates at Vdd = 0.1 V and higher, and generates sufficient back-bias voltages for NMOS and PMOS of 0.85 and −1.5 V, respectively, at Vdd = 0.4 V with a current consumption of only 13 μA. By applying these back-bias voltages, leakage current of a 500 kgate logic circuit reduced to 2 μA corresponding to 4 pA/gate. There are still several points of the optimization and the generator current consumption is still higher than our target specification. The optimization is now under way.

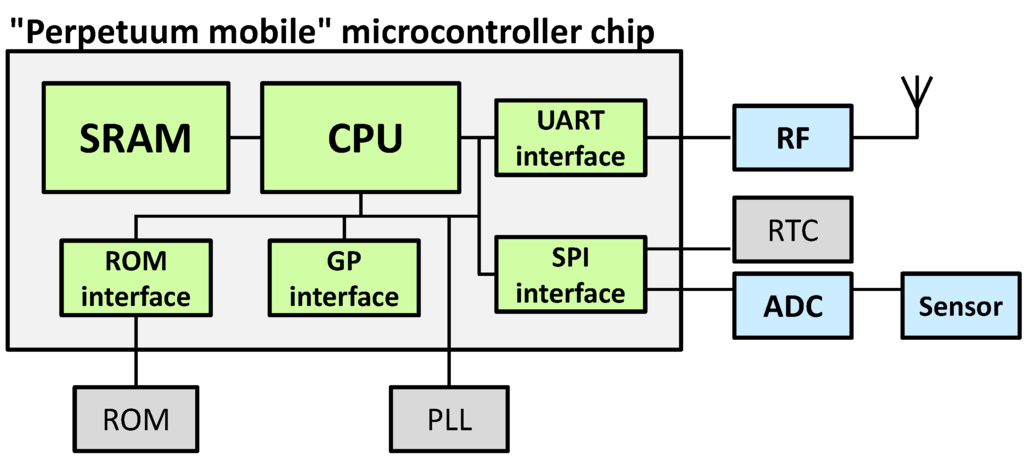

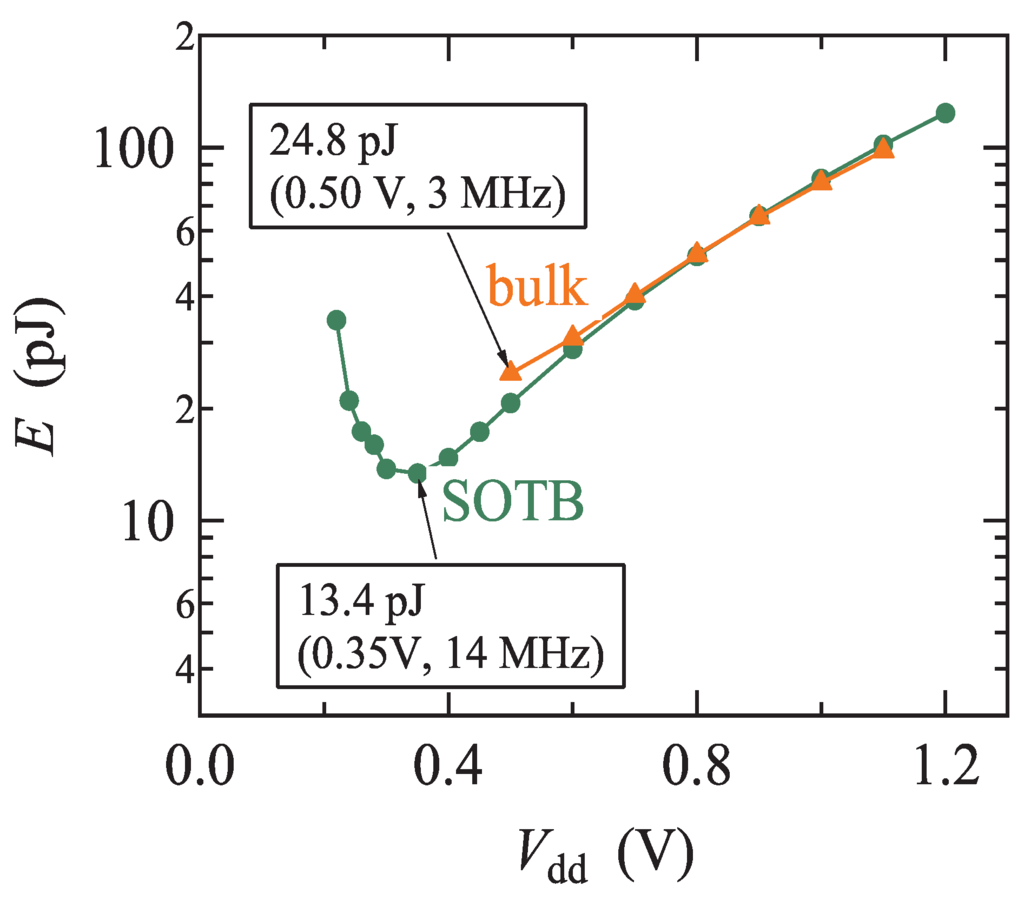

We have confirmed a successful operation [24] of the proto-type ULV micro-controller chip as shown in Figure 11. This chip is composed of 32-bit RISC CPU with five-stage pipeline, 144 kByte SRAM, and interfaces (ROM, UART, SPI, and GP) and can be connected with sensors and rf modules for the sensor-network node. The micro-controller chip operates at Vdd = 0.35 V and consumes only E = 13.4 pJ (f = 14 MHz) as shown in Figure 12. Note that the E values for SOTB and bulk at Vdd ≥ 0.8 V are identical because it is determined by Eac (same Cload of the same 65-nm technology) in this region. Sleep current is only 0.14 μA. By taking advantage of the ULP capability of our SOTB micro-controller chip, named “Perpetuum-Mobile”, the sensor node is expected to operate with a sufficient frequency (>10 MHz) for a long period with a single battery or further longer operation with an energy harvester.

Figure 11.

Block diagram of “Perpetuum-Mobile” micro-controller chip for a sensor-node application. (PLL: phase locked loop; ADC: analog to digital converter; SPI: serial peripheral interface; UART: universal asynchronous receiver transmitter; GP: general purpose).

Figure 12.

Energy per cycle E as a function of operating voltage Vdd for the “Perpetuum-Mobile” micro-controller chip [24].

4. Conclusions

Silicon on thin buried oxide (SOTB) is suitable for the ULV operation thanks to its small variability and back-gate bias controllability. We have demonstrated significant variability reduction, 0.4-V operation of SRAM, and reducing power consumption of logic circuits including a micro-controller chip with a significant speed gain even at ULV. Many ULP applications are expected with SOTB chips. The “Perpetuum-Mobile” micro-controller chips will work as a core electronics parts in various types of electronic apparatuses of the “internet of things”.

Acknowledgments

This work was performed as “Ultra-Low Voltage Device Project” funded and supported by the Ministry of Economy, Trade and Industry (METI) and the New Energy and Industrial Technology Development Organization (NEDO). The authors thank the staff of Renesas Electronics Corporation for the SOTB process integration.

Author Contributions

Nobuyuki Sugii coordinated and discussed the overall research and prepared the manuscript. Yoshiki Yamamoto and Hideki Makiyama designed the wafer fabrication process, prepared the device wafer, and measured their electrical characteristics. Tomohiro Yamashita, Hidekazu Oda, and Yasuo Yamaguchi designed the fabrication process and discussed the electrical characteristics. Shiro Kamohara and Koichiro Ishibashi designed and characterized the test chips. Tomoko Mizutani and Toshiro Hiramoto measured the electrical characteristics of the device wafers and discussed the results.

Conflicts of Interest

The authors declare no conflict of interest.

References

- Bol, D.; Kamel, D.; Flandre, D.; Legat, J.-D. Nanometer MOSFET Effects on the Minimum-Energy Point of 45nm Subthreshold Logic. In Proceedings of the 14th IEEE/ACM International Symposium on Low-Power Electronics and Design, San Franciscon, CA, USA, 19–21 August 2009; pp. 3–8.

- Chandrakasan, A.P.; Daly, D.C.; Finchelstein, D.C.; Kwong, J.; Ramadass, Y.K.; Sinangil, M.E.; Sze, V.; Vermaet, N. Technologies for ultradynamic voltage scaling. Proc. IEEE 2010, 98, 191–214. [Google Scholar] [CrossRef]

- Zhai, B.; Nazhandali, L.; Olson, J.; Reeves, A.; Minuth, M.; Helfand, R.; Pant, S.; Blaauw, D.; Austin, T. A 2.60 pJ/Inst Subthreshold Sensor Processor for Optimal Energy Efficiency. In Proceedings of the 2006 Symposium on VLSI CircuitsDigest of Technical Papers, Honolulu, HI, USA, 15–17 June 2006; pp. 154–155.

- Wang, A.; Chandrakasan, A. A 180-mV subthreshold FFT processor using a minimum energy design methodology. IEEE J. Solid-State Circuits 2005, 40, 310–319. [Google Scholar] [CrossRef]

- Slimani, M.; Silveira, F.; Matherat, P. Variability-Speed-Consumption Trade-off in Near Threshold Operation. In Proceedings of the 21st The International Workshop on Power and Timing Modeling, Optimization and Simulation (PATMOS), Madrid, Spain, 26–29 September 2011; pp. 308–316. [CrossRef]

- Sugii, N.; Tsuchiya, R.; Ishigaki, T.; Morita, Y.; Yoshimoto, H.; Iwamatsu, T.; Oda, H.; Inoue, Y.; Hiramoto, T.; Kimura, S. Evaluation of threshold-voltage variation in silicon on thin buried oxide complementary metal–oxide–semiconductor and its impact on decreasing standby leakage current. Jpn. J. Appl. Phys. 2009, 48, 04C043. [Google Scholar]

- Seo, S.; Dreslinski, R.G.; Woh, M.; Park, J.; Charkrabari, C.; Mahlke, S.; Blaauw, D.; Mudge, T. Process Variation in Near-Threshold Wide SIMD Architectures. In Proceedings of the 49th ACM/EDAC/IEEE Design Automation Conference (DAC), San Francisco, CA, USA, 3–7 June 2012; pp. 980–987.

- Kwong, J.; Chandrakasan, A.P. Variation-Driven Device Sizing for Minimum Energy Sub-Threshold Circuits. In Proceedings of the 2006 International Symposium on Low Power Electronics and Design (ISLPED’06), Tegernsee, Germany, 4–6 October 2006; pp. 8–13.

- Blaauw, D.; Zhai, B. Energy Efficient Design for Subthreshold Supply Voltage Operation. In Proceedings of the 2006 IEEE International Symposium on Circuits and Systems (ISCAS) 2006, Island of Kos, Greece, 21–24 May 2006; p. 32.

- Bowman, K.A.; Duvall, S.G.; Meindl, J.D. Impact of Die-to-Die and within-Die Parameter Fluctuations on the Maximum Clock Frequency Distribution. In Proceedings of the 2001 IEEE International Solid-State Circuits Conference (ISSCC), Digest of Technical Papers 2001, San Francisco, CA, USA, 7 February 2001; pp. 278–279.

- Datta, A.; Bhunia, S.; Mukhopadhyay, S.; Roy, K. Delay modeling and statistical design of pipelined circuit under process variation. IEEE Trans. Comput. Aided Des. Integr. Circuits Syst. 2006, 25, 2427–2436. [Google Scholar] [CrossRef]

- Tsuchiya, R.; Horiuchi, M.; Kimura, S.; Yamaoka, M.; Kawahara, T.; Maegawa, S.; Ipposhi, T.; Ohji, Y.; Matsuoka, H. Silicon on Thin BOX: A New Paradigm of the CMOSFET for Low-Power High-Performance Application Featuring Wide-Range Back-Bias Control. In Proceedings of the IEEE International Electron Devices Meeting, IEDM Technical Digest, San Francisco, CA, USA, 13–15 December 2004; pp. 631–634.

- Morita, Y.; Tsuchiya, R.; Ishigaki, T.; Sugii, N.; Iwamatsu, T.; Ipposhi, T.; Oda, H.; Inoue, Y.; Torii, K.; Kimura, S. Smallest Vth Variability Achieved by Intrinsic Silicon on Thin BOX (SOTB) CMOS with Single Metal Gate. In Proceedings of the 2008 Symposium on VLSI Technology, Honolulu, HI, USA, 17–19 June 2008; pp. 166–167.

- Sugii, N.; Tsuchiya, R.; Ishigaki, T.; Morita, Y.; Yoshimoto, H.; Kimura, S. Local Vth variability and scalability in Silicon-on-Thin-BOX (SOTB) CMOS with small random-dopant fluctuation. IEEE Trans. Electron Devices 2010, 57, 835–845. [Google Scholar] [CrossRef]

- Yamamoto, Y.; Makiyama, H.; Tsunomura, T.; Iwamatsu, T.; Oda, H.; Sugii, N.; Yamaguchi, Y.; Mizutani, T.; Hiramoto, T. Poly/high-k/SiON Gate Stack and Novel Profile Engineering Dedicated for Ultralow-Voltage Silicon-on-Thin-BOX (SOTB) CMOS Operation. In Proceedings of the 2012 Symposium on VLSI Technology, Honolulu, HI, USA, 12–14 June 2012; pp. 109–110.

- Yamamoto, Y.; Makiyama, H.; Shinohara, H.; Iwamatsu, T.; Oda, H.; Kamohara, S.; Sugii, N.; Yamaguchi, Y.; Mizutani, T.; Hiramoto, T. Ultralow-Voltage Operation of Silicon-on-Thin-BOX (SOTB) 2 Mbit SRAM Down to 0.37 V Utilizing Adaptive Back Bias. In Proceedings of the 2013 Symposium on VLSI Technology, Kyoto, Japan, 11–13 June 2013; pp. T212–T213.

- Mizutani, T.; Yamamoto, Y.; Makiyama, H.; Tsunomura, T.; Iwamatsu, T.; Oda, H.; Sugii, N.; Hiramoto, T. Reduced Drain Current Variability in Fully Depleted Silicon-on-Thin-BOX (SOTB) MOSFETs. In Proceedings of the 2012 IEEE Silicon Nanoelectronics Workshop (SNW), Honolulu, HI, USA, 10–11 June 2012; pp. 1–2.

- Makiyama, H.; Yamamoto, Y.; Shinohara, H.; Iwamatsu, T.; Oda, H.; Sugii, N.; Ishibashi, K.; Yamaguchi, Y. Speed enhancement at Vdd = 0.4 V and random τpd variability reduction and analyisis of τpd variability of silicon on thin buried oxide circuits. Jpn. J. Appl. Phys. 2014, 53. [Google Scholar] [CrossRef]

- Makiyama, H.; Yamamoto, Y.; Shinohara, H.; Iwamatsu, T.; Oda, H.; Sugii, N.; Ishibashi, K.; Mizutani, T.; Hiramoto, T.; Yamaguchi, Y. Suppression of Die-to-Die Delay Variability of Silicon on Thin Buried Oxide (SOTB) CMOS Circuits by Balanced P/N Drivability Control with Back-Bias for Ultralow-Voltage (0.4 V) Operation. In Proceedings of the 2013 IEEE International Electron Devices Meeting (IEDM), Washington, DC, USA, 9–11 December 2013; pp. 822–825.

- Morohashi, S.; Sugii, N.; Iwamatsu, T.; Kamohara, S.; Kato, Y.; Pham, C.-K.; Ishibashi, K. A 44 μW/10 MHz Minimum Power Operation of 50 K Logic Gate Using 65 nm SOTB Devices with Back Gate Control. In Proceedings of the 2013 IEEE SOI-3D-Subthreshold Microelectronics Technology Unified Conference (S3S), Monterey, CA, USA, 7–10 October 2013; pp. 165–166.

- Su, H.; Amano, H. Real Chip Evaluation of a Low Power Reconfigurable Accelerator with SOTB Technology; Technical Report of The Institute of Electronics, Information and Communication Engineers (IEICE), RECONF2013-52; IEICE: Tokyo, Japan, 2013; Volume 113, pp. 71–76. (In Japanese) [Google Scholar]

- Hioki, M.; Ma, C.; Kawanami, T.; Ogasahara, Y.; Nakagawa, T.; Sekigawa, T.; Tsutsumi, T.; Koike, H. The First SOTB Implementation of Flex Power FPGA. J. Low Power Electron. Appl. Submitted.

- Nagatomi, H.; Le, D.-H.; Pham, C.-K.; Sugii, N.; Kamohara, S.; Iwamatsu, T.; Ishibashi, K. A 4 pA/Gate Sleep Current 65 nm SOTB Logic Gates Using On-chip VBB Generator for Energy Harvesting Sensor Network Systems. In Proceedings of the 2013 International Conference on Integrated Circuits, Design, and Verification (ICDV 2013), Ho Chi Minh City, Vietnam, 15–16 November 2013.

- Ishibashi, K.; Sugii, N.; Usami, K.; Amano, H.; Kobayashi, K.; Pham, C.-K.; Makiyama, H.; Yamamoto, Y.; Shinohara, H.; Iwamatsu, T.; et al. A Perpetuum Mobile 32 bit CPU with 13.4 pJ/cycle, 0.14 µA Sleep Current using Reverse Body Bias Assisted 65 nm SOTB CMOS Technology. In Proceedings of the COOL Chips XVII, Yokohama, Kanagawa, Japan, 14–16 April 2014.

© 2014 by the authors; licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution license (http://creativecommons.org/licenses/by/3.0/).