Three-Dimensional Wafer Stacking Using Cu TSV Integrated with 45 nm High Performance SOI-CMOS Embedded DRAM Technology †

Abstract

:1. Introduction

2. Previous Work

2.1. Metal-Metal Bonding

2.2. Hybrid Bonding

2.3. SiO2 Bonding

3. Wafer Level 3D Integration Process

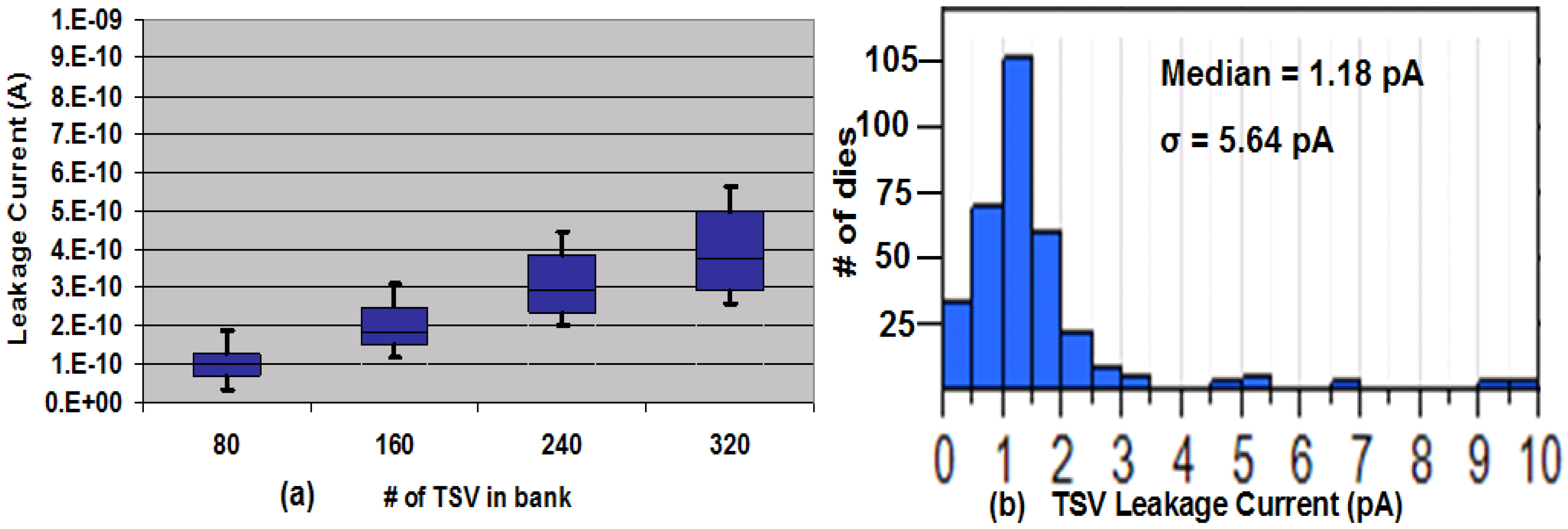

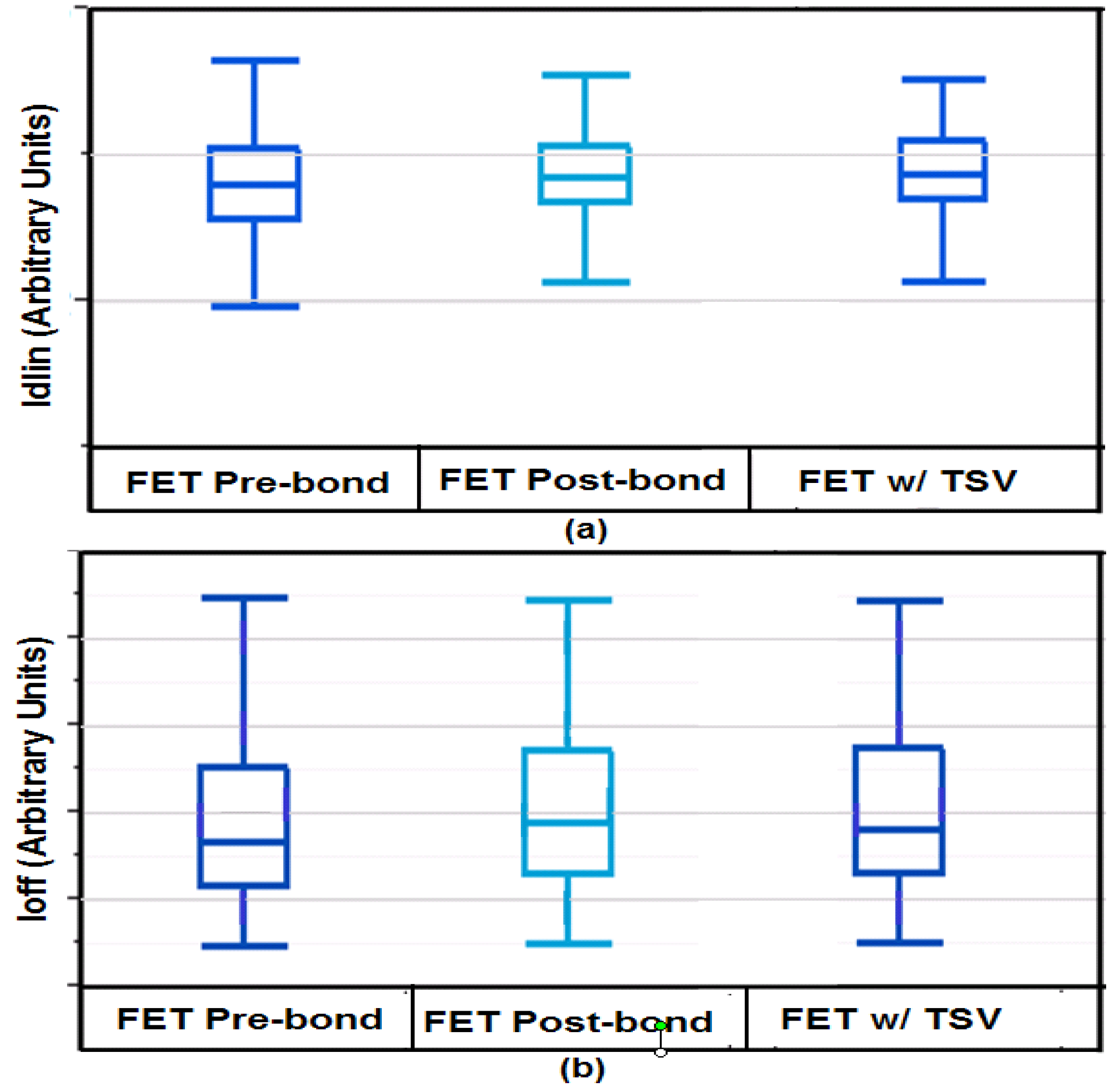

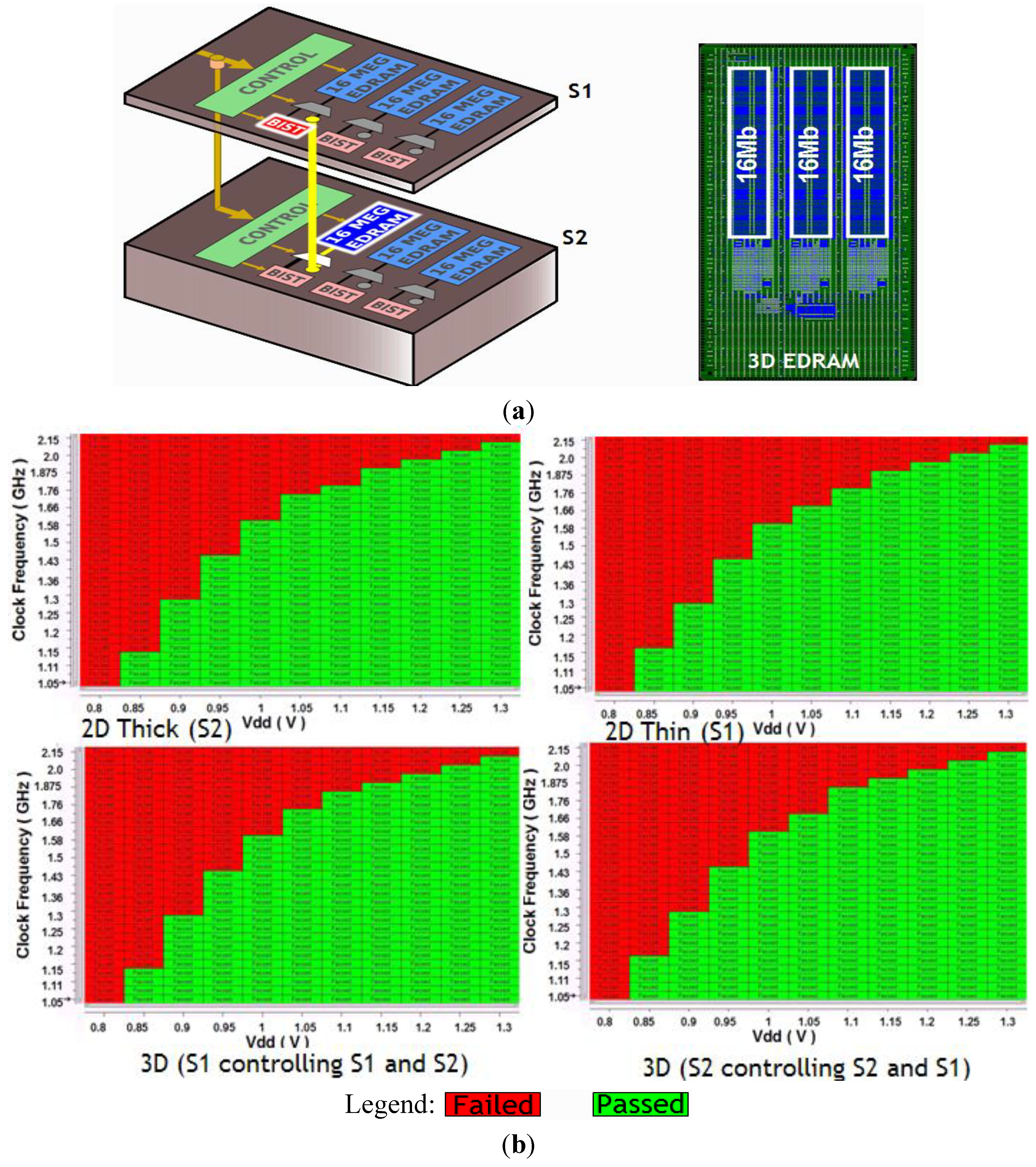

4. Hardware Results

- (a)

- 2D thick wafer mode where the memory on the thick S1 wafer was activated;

- (b)

- 2D thin wafer mode where the memory on thin wafer S1 was activated and the test patterns were loaded using the TSVs;

- (c)

- 3D mode where the BIST on S1 controls the memory on S1 as well as S2;

- (d)

- 3D mode where the BIST on S2 controls the memory on S2 as well as S1.

5. Conclusions

Acknowledgments

Conflicts of Interest

References

- Iyer, S.S.; Kirihata, T.; Wordeman, M.R.; Barth, J.; Hannon, R.H.; Malik, R. Process-Design Considerations for Three Dimensional Memory Integration. In Proceedings of the Symposium on VLSI Technology, Honolulu, HI, USA, 16–18 June 2009; pp. 60–63.

- Farooq, M.G.; Graves-Abe, T.L.; Landers, W.F.; Kothandaraman, C.; Himmel, B.A.; Andry, P.S.; Tsang, C.K.; Sprogis, E.; Volant, R.P.; Petrarca, K.S.; et al. 3D Copper TSV Integration, Testing and Reliability. In Proceedings of the IEEE International Electron Devices Meeting (IEDM), Washington, DC, USA, 5–7 December 2011.

- Wafer Level 3-D ICs Process Technology; Tan, C.S.; Gutmann, R.J.; Reif, R. (Eds.) Springer US: New York, NY, USA, 2008; p. 286.

- Barth, J.; Reohr, W.R.; Parries, P.; Fredeman, G.; Golz, J.; Schuster, S.E.; Matick, Richard E.; Hunter, H.; Tanner, C.C.; Harig, J.; et al. A 500 MHz random cycle, 1.5 ns latency, SOI embedded DRAM macro featuring a three-transistor micro sense amplifier. IEEE J. Solid-State Circuits 2008, 43, 86–95. [Google Scholar] [CrossRef]

- Totta, P.A.; Khadpe, S.; Koopman, N.G.; Sheaffer, M.J. Chip-to-Package Interconnections. In Microelectronics Packaging Handbook, Part II, 2nd ed.; Tummala, R.R., Rymaszewski, E.J., Klopfenstein, A.G., Eds.; Springer: New York, NY, USA, 1997; pp. 129–283. [Google Scholar]

- Oppermann, H.; Hutter, M. Au/Sn Solder. In Handbook of Wafer Bonding; Ramm, P., Lu, J.J.-Q., Taklo, M.M.V., Eds.; Wiley-VCH Verlag GmbH & Co.: Weinheim, Germany, 2012; p. 119. [Google Scholar]

- Hoivik, N.; Aasmundtveit, K. Wafer Level Solid-Liquid Interdiffusion Bonding. In Handbook of Wafer Bonding; Wiley-VCH Verlag & Co.: Weinheim, Germany, 2012; p. 181. [Google Scholar]

- Chen, K.N.; Tan, C.S. Thermocompression Cu-Cu Bonding of Blanket and Patterned Wafers. In Handbook of Wafer Bonding; Wiley-VCH Verlag & Co.: Weinheim, Germany, 2012; p. 161. [Google Scholar]

- Di Cioccio, L. Cu/SiO2 Hybrid Bonding. In Handbook of Wafer Bonding; Wiley-VCH Verlag & Co.: Weinheim, Germany, 2011; p. 237. [Google Scholar]

- Ko, C.-T.; Hsiao, Z.-C.; Fu, H.-C.; Chen, K.-N.; Lo, W.-C.; Chen, Y.-H. Wafer-to-Wafer Hybrid Bonding Technology for 3D IC. In Proceedings of the Electronic System-Integration Technology Conference, Berlin, Germany, 13–16 September 2010; pp. 1–5.

- Ko, C.-T.; Chen, K.-N.; Lo, W.-C.; Cheng, C.-A.; Huang, W.-C.; Hsiao, Z.-C.; Fu, H.-C.; Chen, Y.-H. Wafer-Level 3D Integration Using Hybrid Bonding. In Proceedings of the IEEE International 3D Systems Integration Conference, Munich, Germany, 16–18 November 2010; pp. 1–4.

- Skordas, S.; Tulipe, D.C.L.; Winstel, K.; Vo, T.A.; Priyadarshini, D.; Upham, A.; Song, D.; Hubbard, A.; Johnson, R.; Cauffman, K.; et al. Wafer-Scale Oxide Fusion Bonding and Wafer Thinning Development for 3D Systems Integration. In Proceedings of the 3rd IEEE International Workshop on Low Temperature Bonding for 3D integration (LTB-3D), Tokyo, Japan, 22–23 May 2012; pp. 203–208.

- Wordeman, M.; Silberman, J.; Maier, G.; Scheuermann, M. A 3D System Prototype of an EDRAM Cache Stacked Over Processor-Like Logic Using Through-Silicon Vias. In Proceedings of the IEEE International Solid State Circuits Conference (ISSCC), San Francisco, CA, USA, 19–23 February 2012; pp. 186–187.

- Golz, J.; Safran, J.; He, B.; Leu, D.; Yin, M.; Weaver, T.; Vehabovic, A.; Sun, Y.; Cestero, A.; Himmel, B.; et al. 3D stackable 32 nm High-K/Metal Gate SOI embedded DRAM prototype. In Proceedings of the Symposium on VLSI Circuits, Honolulu, HI, USA, 15–17 June 2011; pp. 228–229.

- Ohba, T. Bumpless WOW Stacking for Large-Scale 3D Integration. In Proceedings of the 10th IEEE International Conference on Solid-State and Integration Circuit Technology (ICSICT), Shanghai, China, 1–4 November 2010; pp. 70–73.

- Sarvari, R.; Naeemi, A.; Zarkesh-Ha, P.; Meindl, J.D. Design and Optimization for Nanoscale Power Distribution Networks in Gigascale Systems. In Proceedings of the IEEE International Interconnect Technology Conference, Burlingame, CA, USA, 4–6 June 2007; pp. 190–192.

- Mercha, A.; Van der Plas, G.; Moroz, V.; de Wolf, I.; Asimakopoulos, P.; Minas, N.; Domae, S.; Perry, D.; Choi, M.; Redolfi, A.; et al. Comprehensive Analysis of the Impact of Single and Arrays of Through Silicon Vias Induced Stress on High-K/Metal Gate CMOS Performance. In Proceedings of the IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 6–8 December 2010; pp. 2.2.1–2.2.4.

- Yu, L.; Chang, W.-Y.; Zuo, K.; Wang, J.; Yu, D.; Boning, D. Methodology for Analysis of TSV Stress Induced Transistor Variation and Circuit Performance. In Proceedings of the 13th International Symposium on Quality Electronic Design (ISQED), Santa Clara, CA, USA, 19–21 March 2012; pp. 216–222.

© 2014 by the authors; licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution license (http://creativecommons.org/licenses/by/3.0/).

Share and Cite

Batra, P.; Skordas, S.; LaTulipe, D.; Winstel, K.; Kothandaraman, C.; Himmel, B.; Maier, G.; He, B.; Gamage, D.W.; Golz, J.; et al. Three-Dimensional Wafer Stacking Using Cu TSV Integrated with 45 nm High Performance SOI-CMOS Embedded DRAM Technology. J. Low Power Electron. Appl. 2014, 4, 77-89. https://doi.org/10.3390/jlpea4020077

Batra P, Skordas S, LaTulipe D, Winstel K, Kothandaraman C, Himmel B, Maier G, He B, Gamage DW, Golz J, et al. Three-Dimensional Wafer Stacking Using Cu TSV Integrated with 45 nm High Performance SOI-CMOS Embedded DRAM Technology. Journal of Low Power Electronics and Applications. 2014; 4(2):77-89. https://doi.org/10.3390/jlpea4020077

Chicago/Turabian StyleBatra, Pooja, Spyridon Skordas, Douglas LaTulipe, Kevin Winstel, Chandrasekharan Kothandaraman, Ben Himmel, Gary Maier, Bishan He, Deepal Wehella Gamage, John Golz, and et al. 2014. "Three-Dimensional Wafer Stacking Using Cu TSV Integrated with 45 nm High Performance SOI-CMOS Embedded DRAM Technology" Journal of Low Power Electronics and Applications 4, no. 2: 77-89. https://doi.org/10.3390/jlpea4020077

APA StyleBatra, P., Skordas, S., LaTulipe, D., Winstel, K., Kothandaraman, C., Himmel, B., Maier, G., He, B., Gamage, D. W., Golz, J., Lin, W., Vo, T., Priyadarshini, D., Hubbard, A., Cauffman, K., Peethala, B., Barth, J., Kirihata, T., Graves-Abe, T., ... Iyer, S. (2014). Three-Dimensional Wafer Stacking Using Cu TSV Integrated with 45 nm High Performance SOI-CMOS Embedded DRAM Technology. Journal of Low Power Electronics and Applications, 4(2), 77-89. https://doi.org/10.3390/jlpea4020077