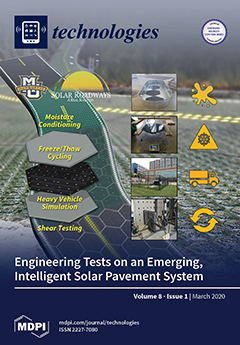

Concrete and asphalt are the primary materials used to construct roadways for motor vehicles, paths for pedestrians and bicyclists, and runways for aircraft. Solar Roadways

®, Inc. (SR) proposed a novel solar pavement technology (i.e., solar road panels (SRP)) as an alternative

[...] Read more.

Concrete and asphalt are the primary materials used to construct roadways for motor vehicles, paths for pedestrians and bicyclists, and runways for aircraft. Solar Roadways

®, Inc. (SR) proposed a novel solar pavement technology (i.e., solar road panels (SRP)) as an alternative material and energy source. SR performed load, traction, and impact testing to use SRPs in non-critical applications like parking lots. To use SRP in public roads, engineering tests including freeze/thaw, moisture absorption, heavy vehicle, and shear testing were accomplished on “SR3” prototypes. Testing was performed at Marquette University in the Engineering Materials and Structural Testing Laboratory and the SR Pilot Project area. Moisture absorption and freeze/thaw tests showed “SR3” resistant to extreme weather and moisture environments. Heavy vehicle testing revealed no physical damage to the “SR3” after approximately 989,457 equivalent single axle loads were continuously rolled over a prototype pavement. Shear testing was conducted to investigate “SR3” laminate structure properties. In all cases, electrical failure was defined when “SR3” photovoltaic voltage dropped to zero volts. The maximum shear stress and applied torque for “SR3”’ (S/N’s Paver 1, 002B, 007C, and 004B) were 1756 kPa, 1835 kPa, 1643 kPa, 2023 kPa; and 121.2 kN·m, 131.3 kN·m, 117.6 kN·m, 144.8 kN·m, respectively. In addition, the “SR3” “heartbeat” light emitting diode (LED) remained operational (i.e., indicates computer bus traffic) in all phases of shear testing. Overall, the results show “SR3” prototypes to be robust, resilient, and functional when subjected to “real-world” test conditions.

Full article