An 8–15 GHz Doherty Power Amplifier with a Compact Quadrature-Hybrid-Based Output Combiner in 22 nm FD-SOI

Abstract

1. Introduction

- Main contributions:

- A compact quadrature-hybrid-based Doherty topology that replaces lossy on-chip inverters while preserving the Doherty load-line trajectory.

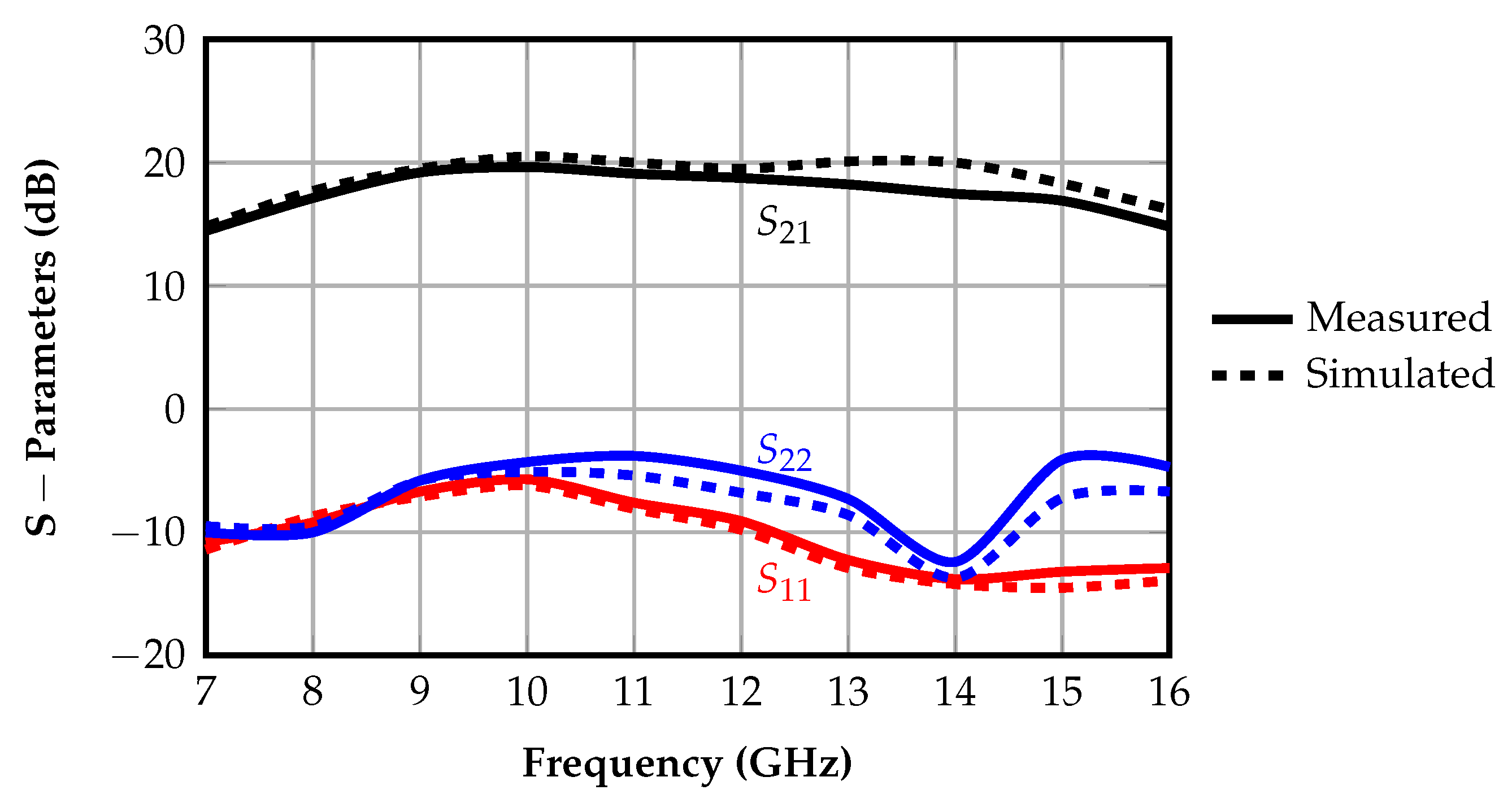

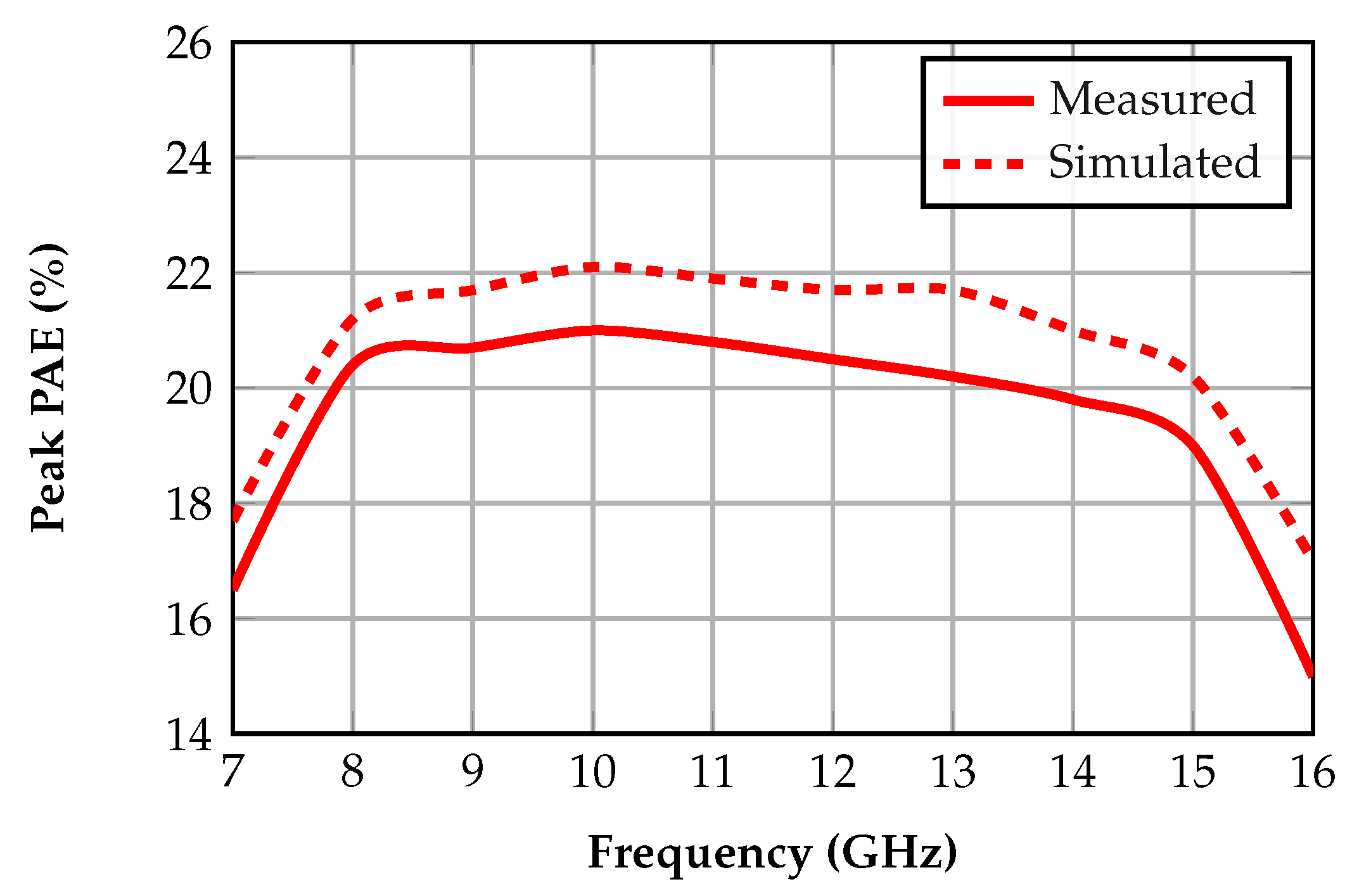

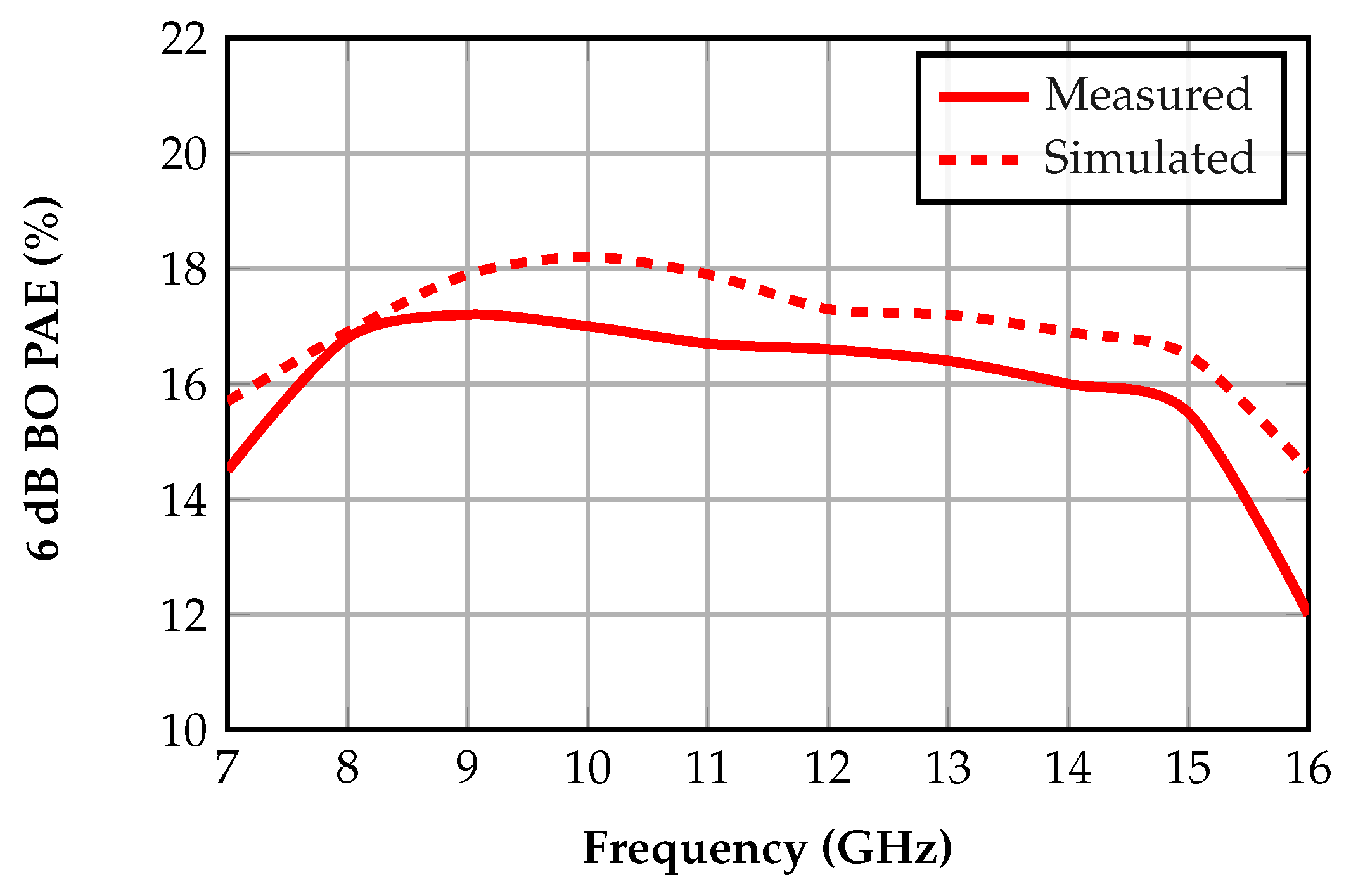

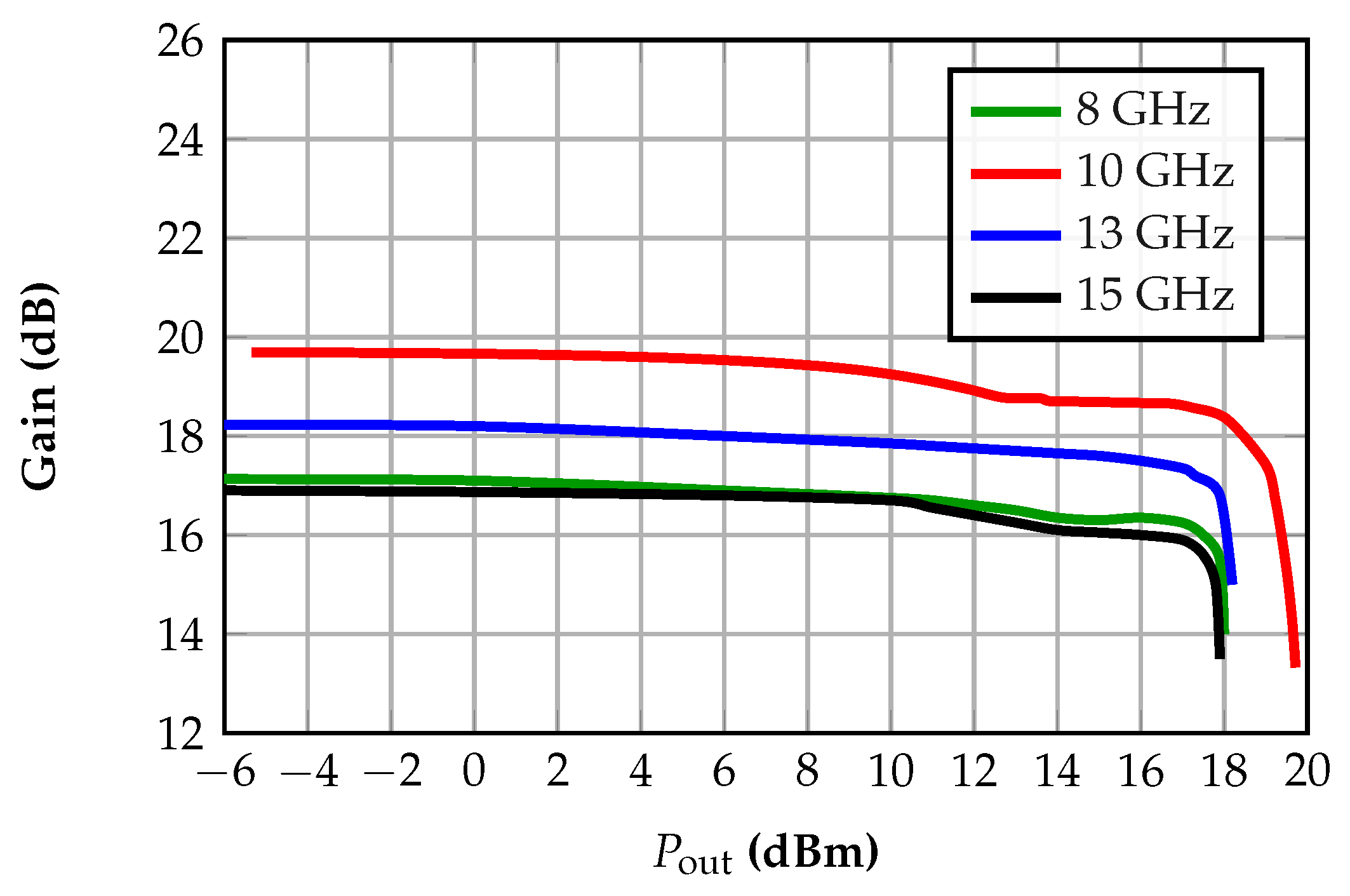

- Wideband 8–15 GHz-measured operation in 22 nm FD-SOI with maintained competitiveness with state-of-the-art CMOS DPAs.

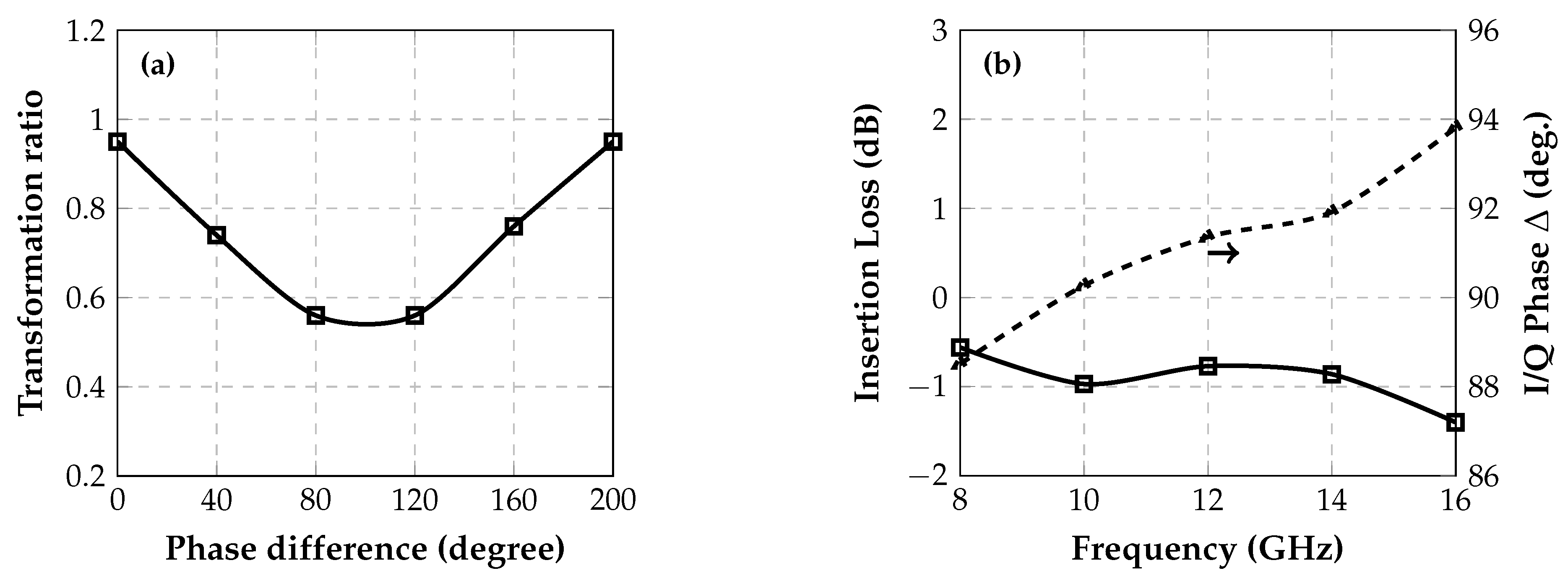

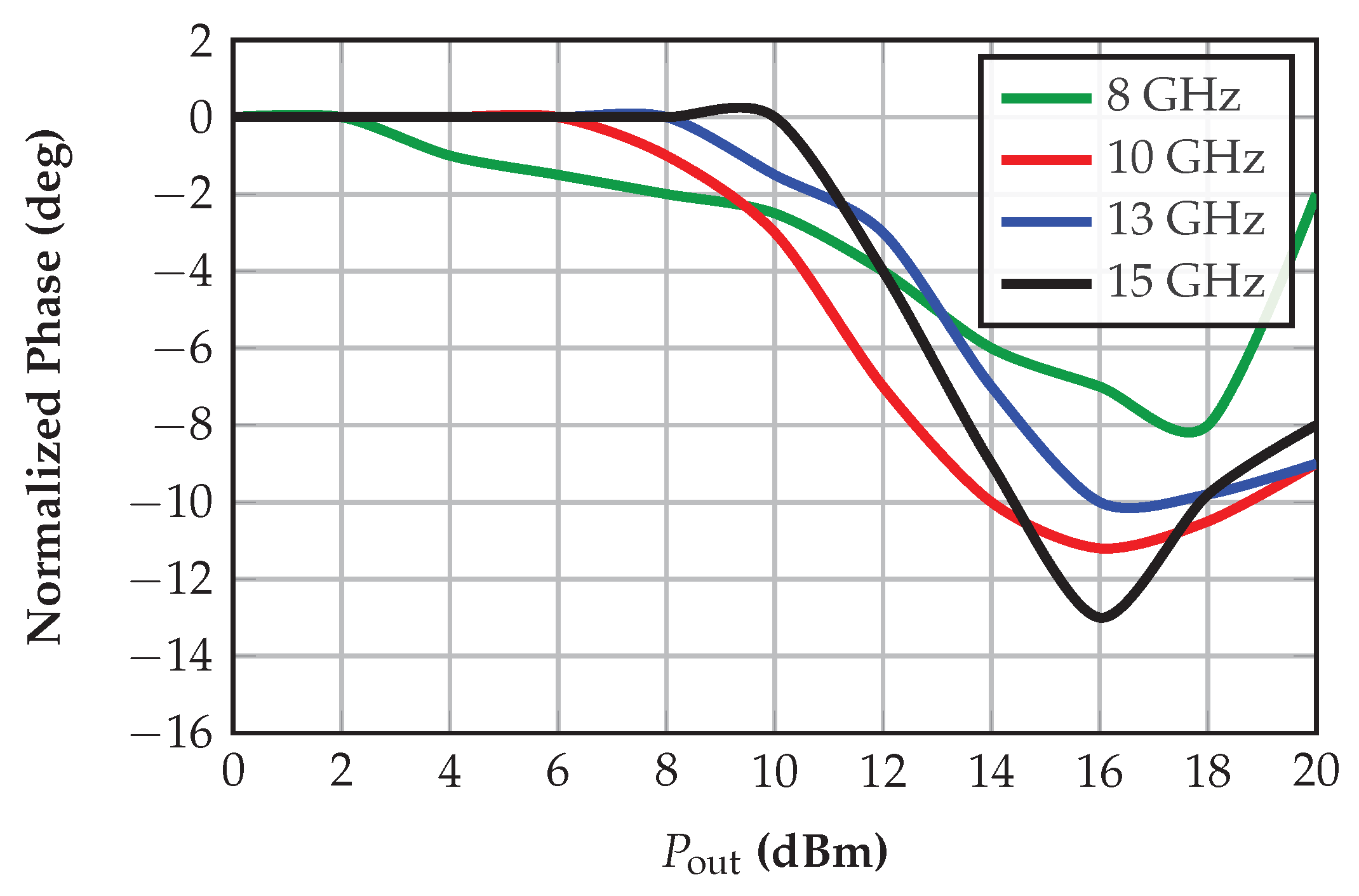

- A passive co-design methodology that accounts for on-chip attenuation and phase dispersion to sustain hybrid balance and DPA linearity over a large fractional bandwidth.

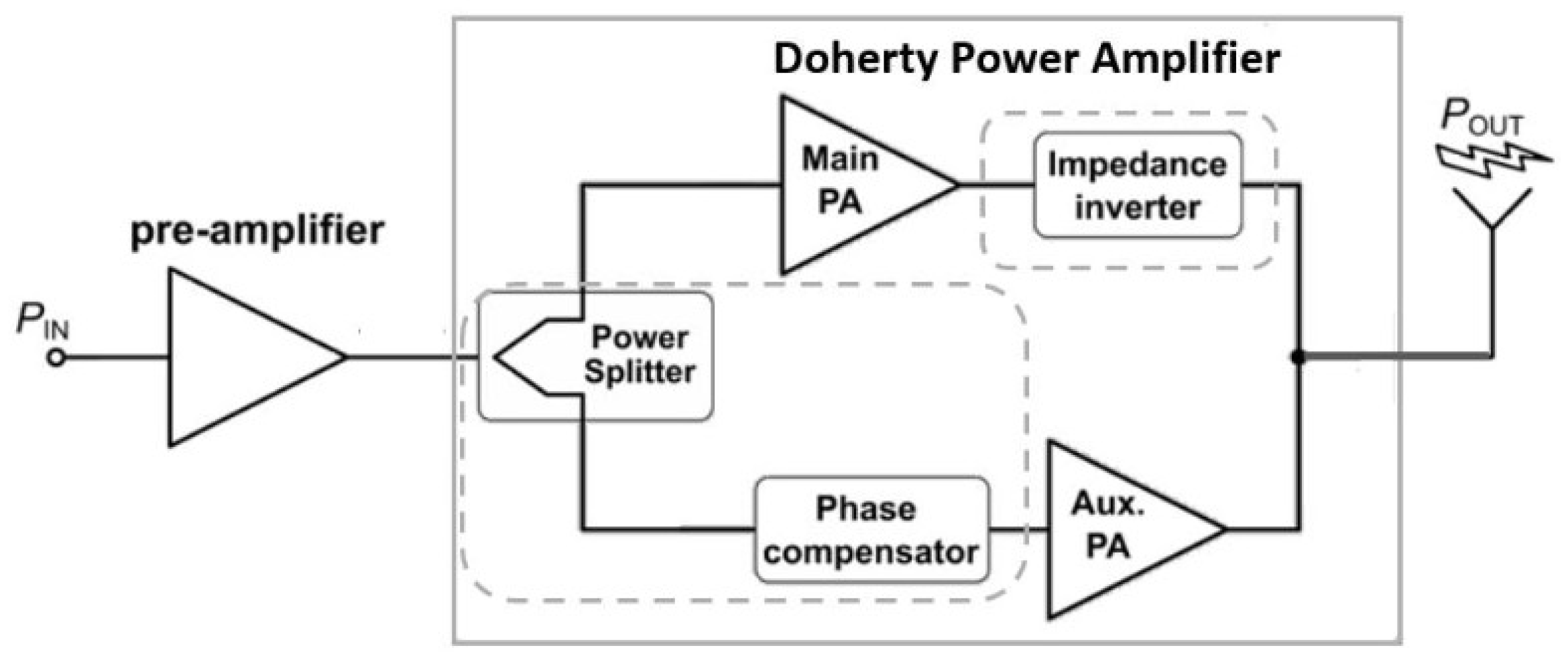

2. Quadrature Hybrids as Impedance Inverters: Robust DPA Operation Alongside Broader Bandwidth

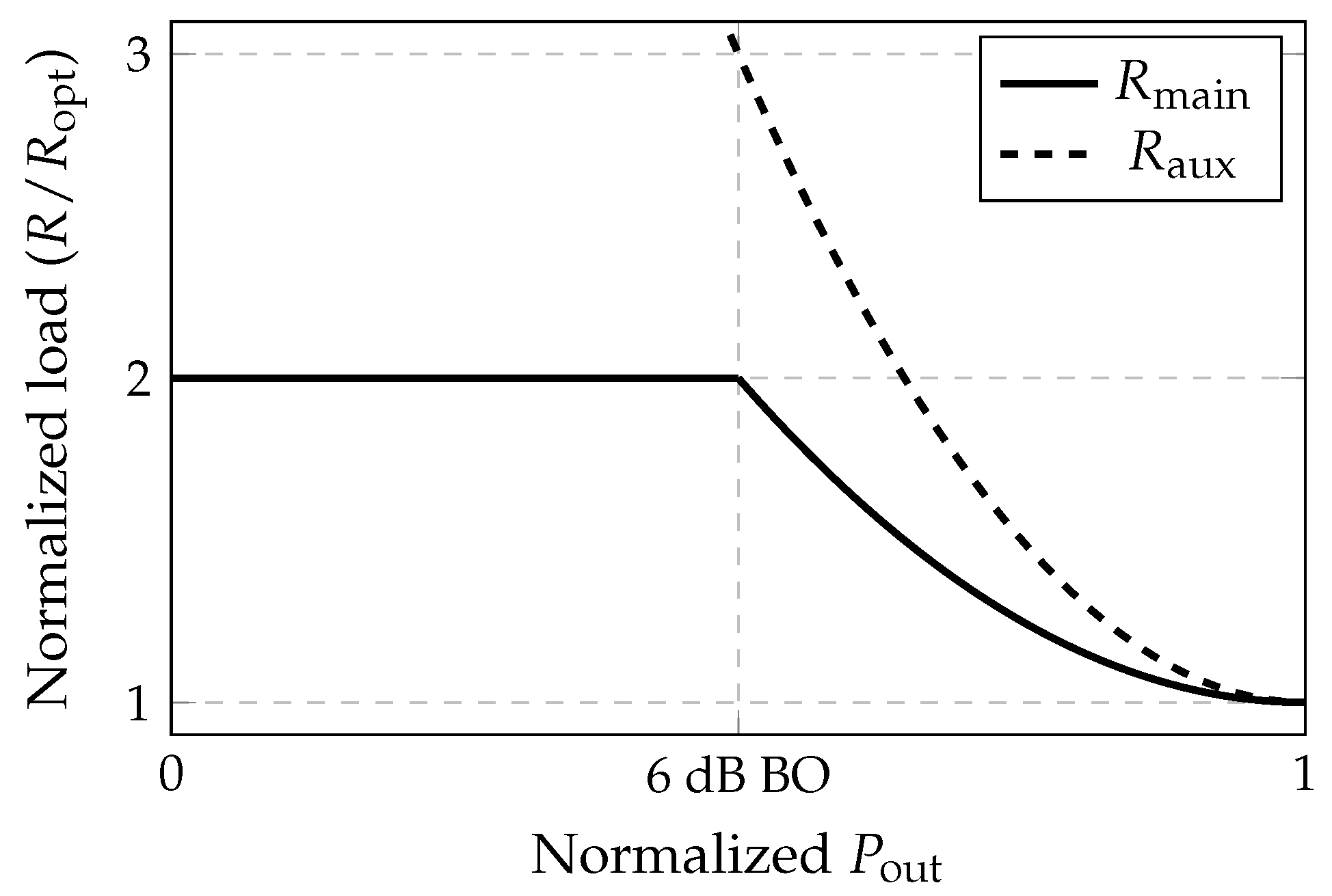

2.1. Validation of DPA Load Modulation Using a Quadrature-Hybrid Combiner

2.2. Why a Quadrature Hybrid Yields Wider Doherty Bandwidth than a Inverter

- (1)

- transmission line (characteristic impedance , terminated in a real ) [12]

- (2)

- Quadrature hybrid (3 dB, 90°) across frequency

- (3)

- Quantitative comparison at 8–15 GHz

- (4)

- Takeaways for Doherty bandwidth

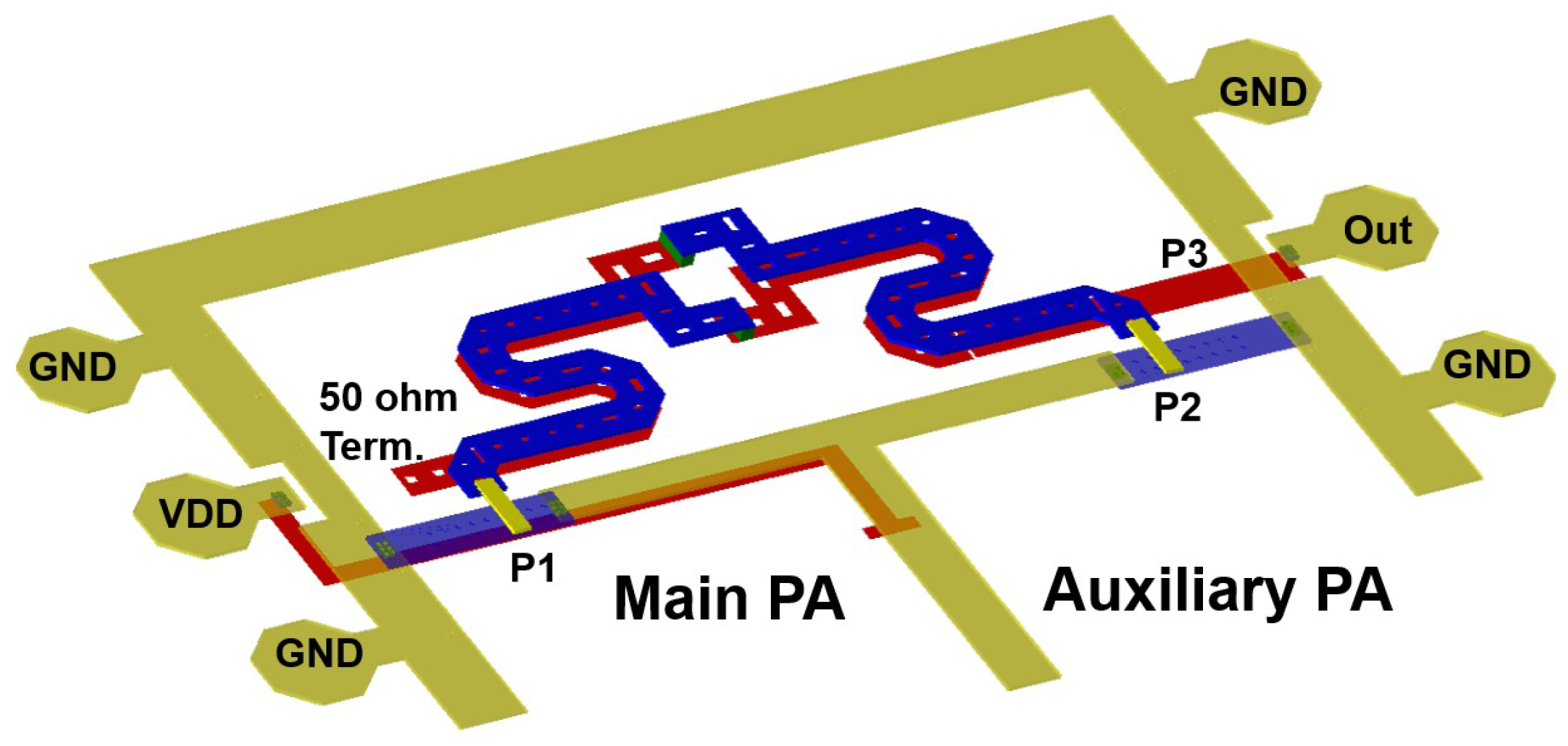

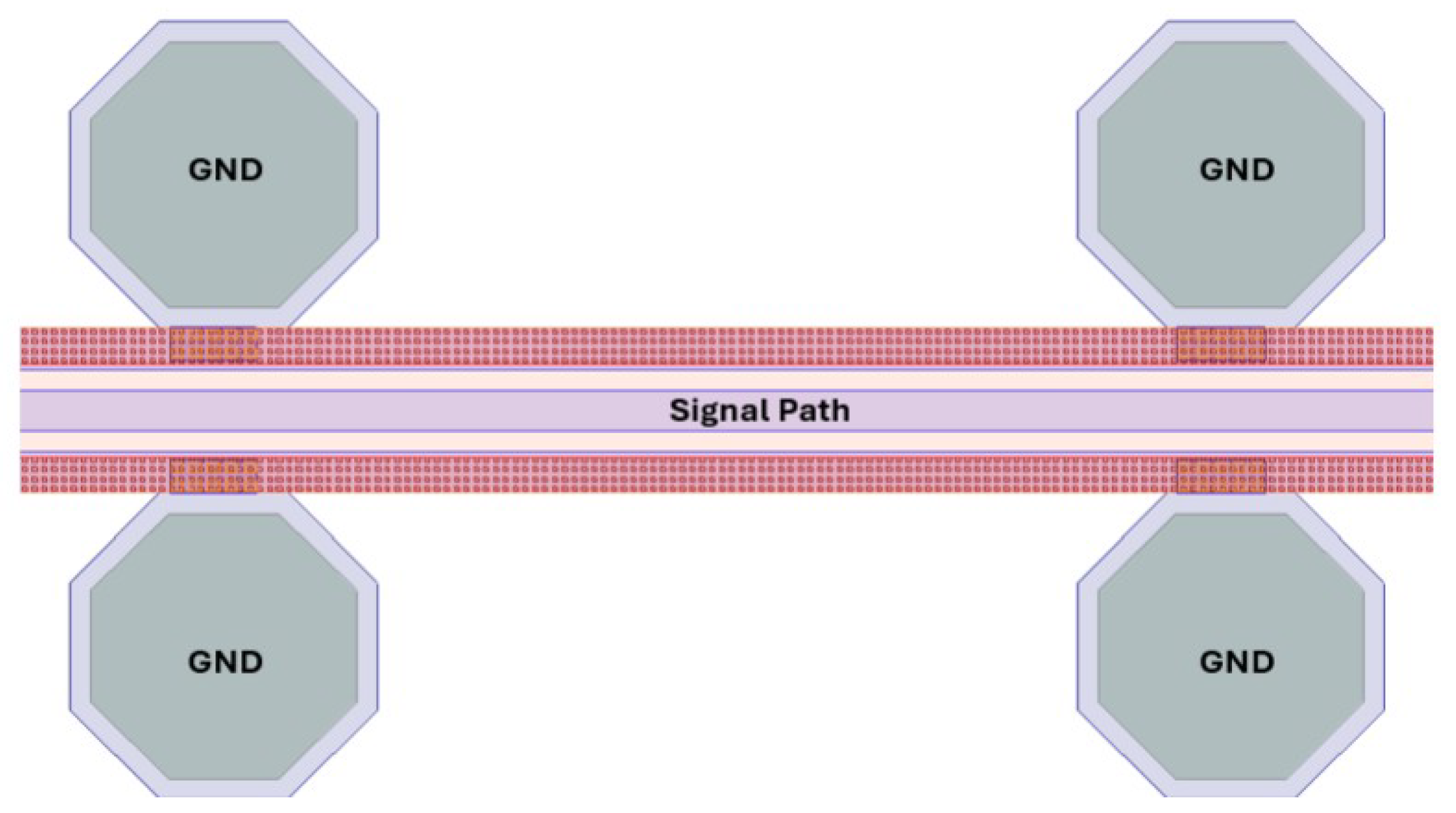

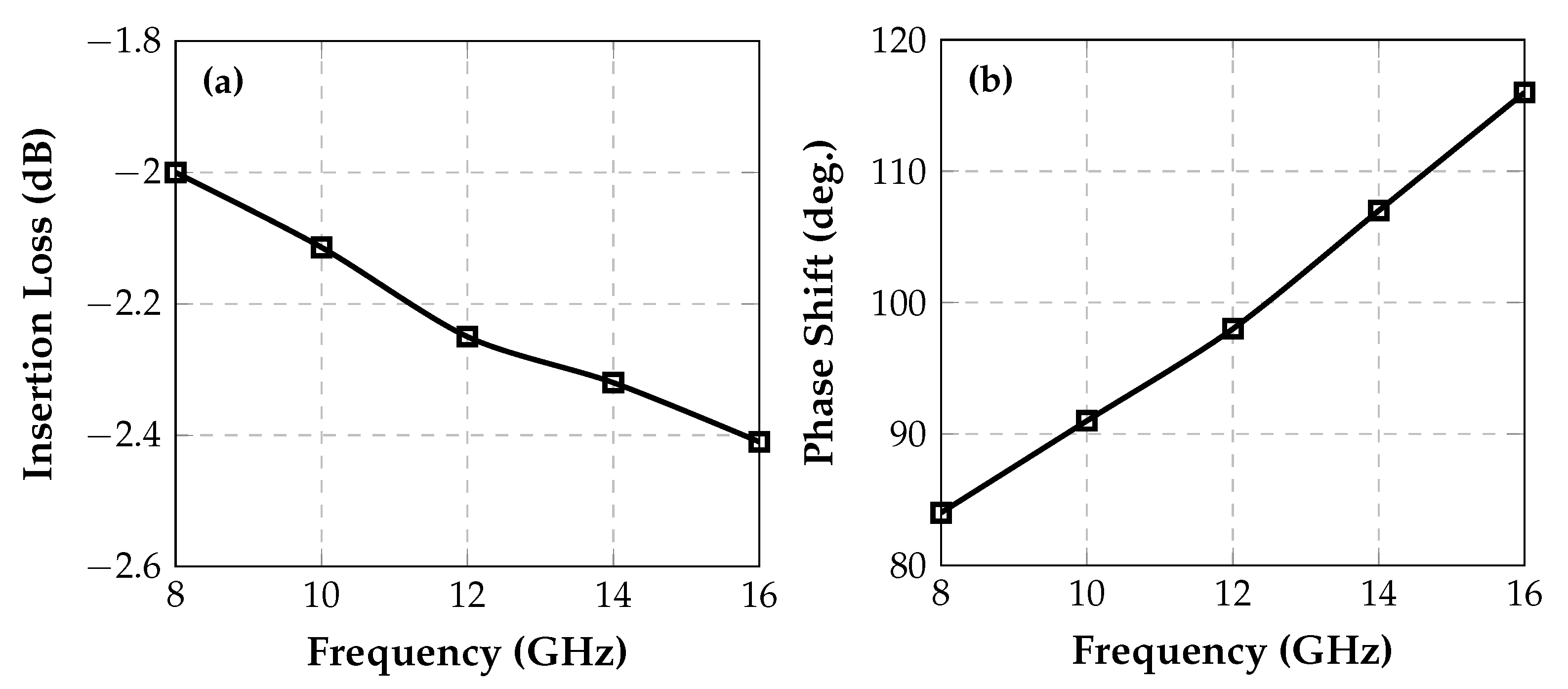

2.3. The Proposed Quadrature-Hybrid Combiner: Layout and Characterization

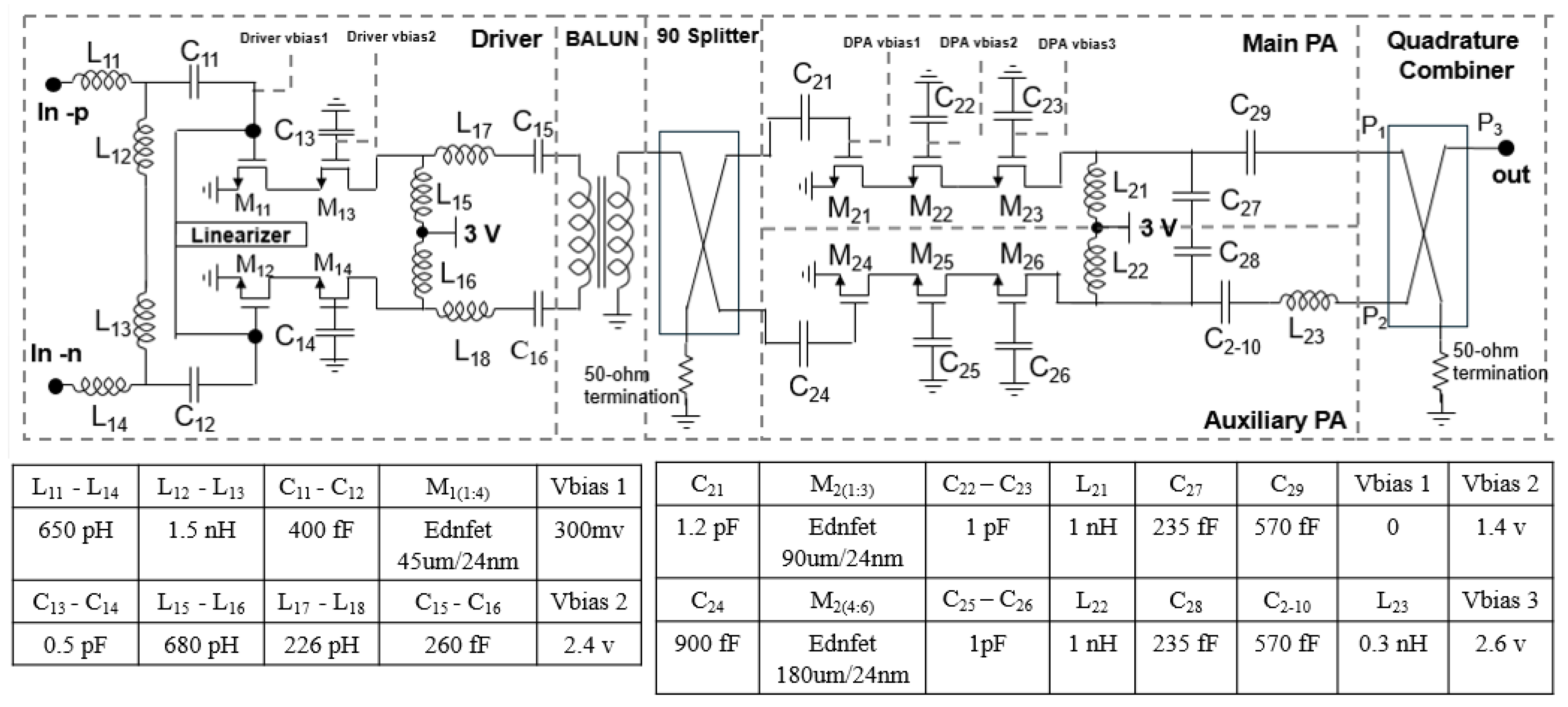

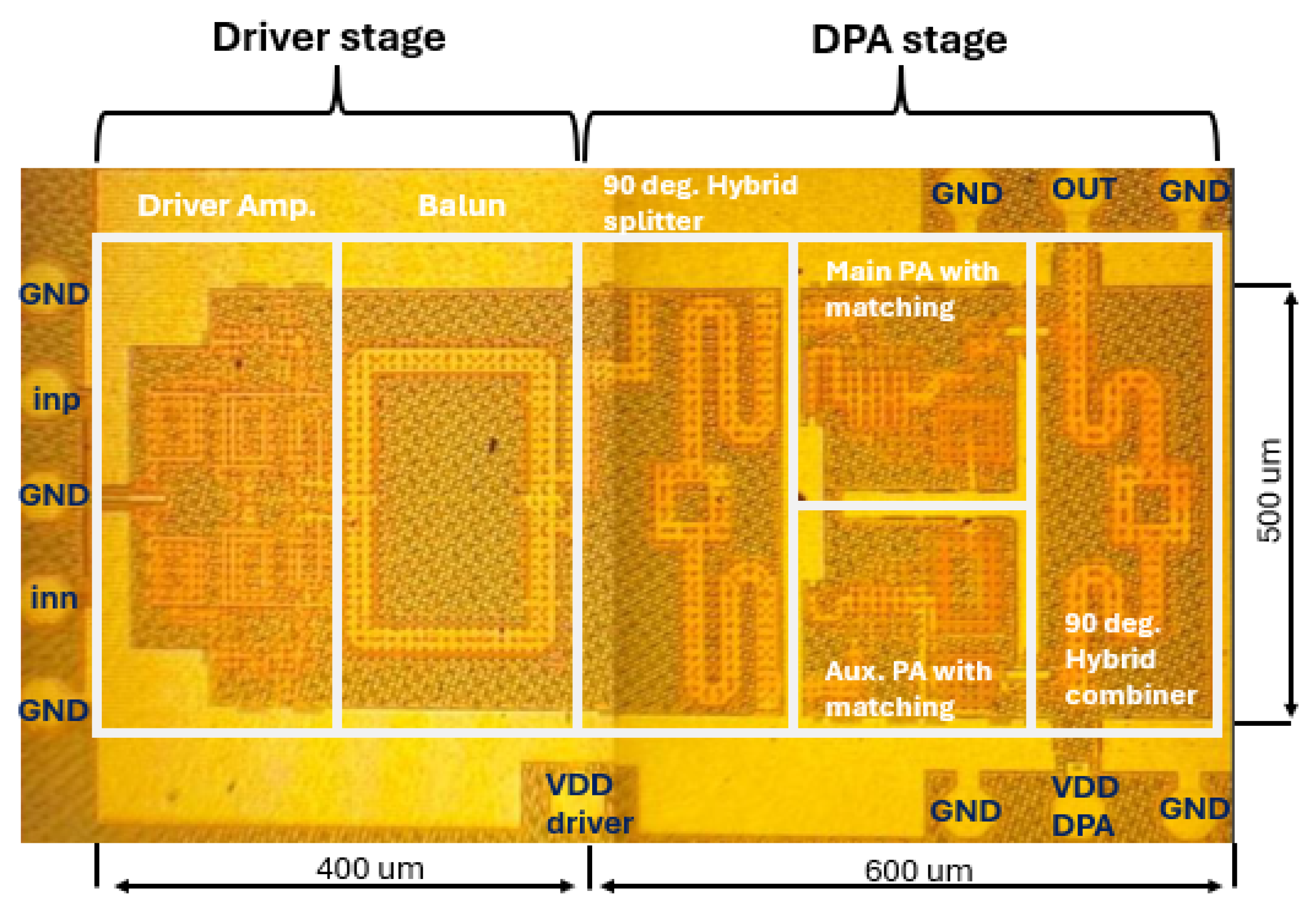

3. The Proposed DPA: Design Details

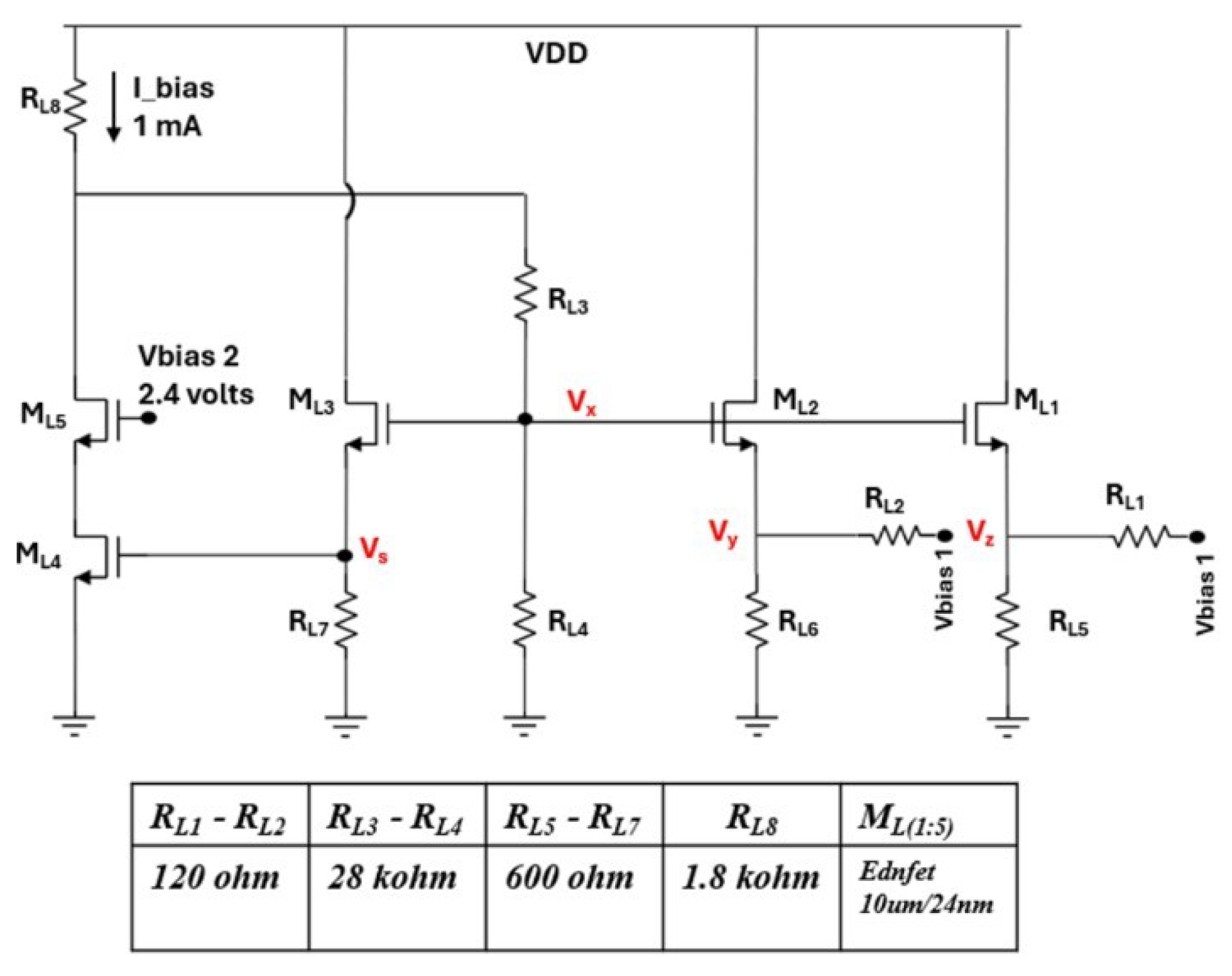

3.1. The Driver Stage

3.2. The DPA Stage

3.2.1. Target Power and Architecture

3.2.2. Stacking and Reliability

3.2.3. Bias Classes

3.2.4. Device Sizing and Current Density

3.2.5. Auxiliary Amplifier Sizing

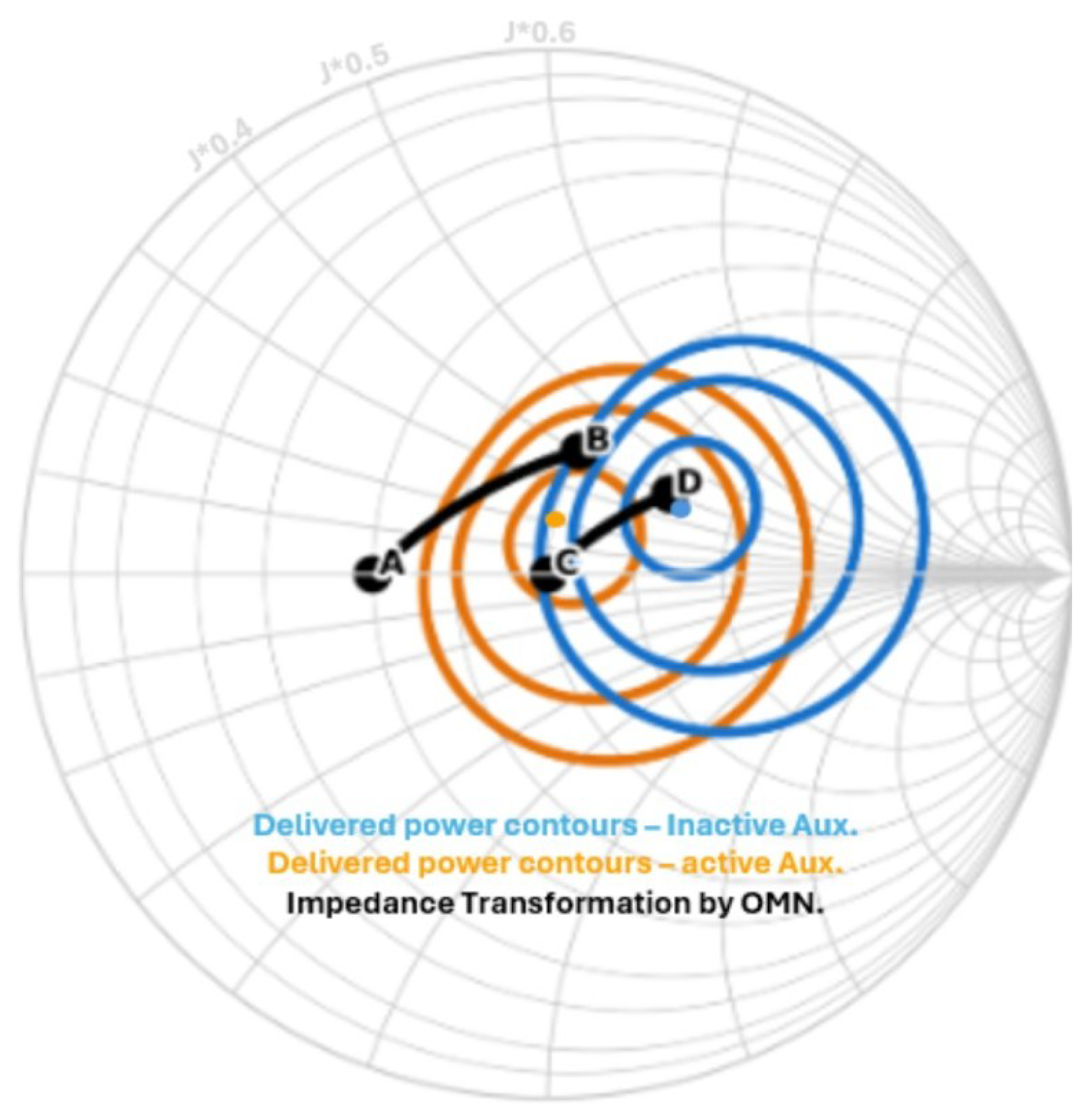

3.2.6. Load–Pull and Impedance Transformation

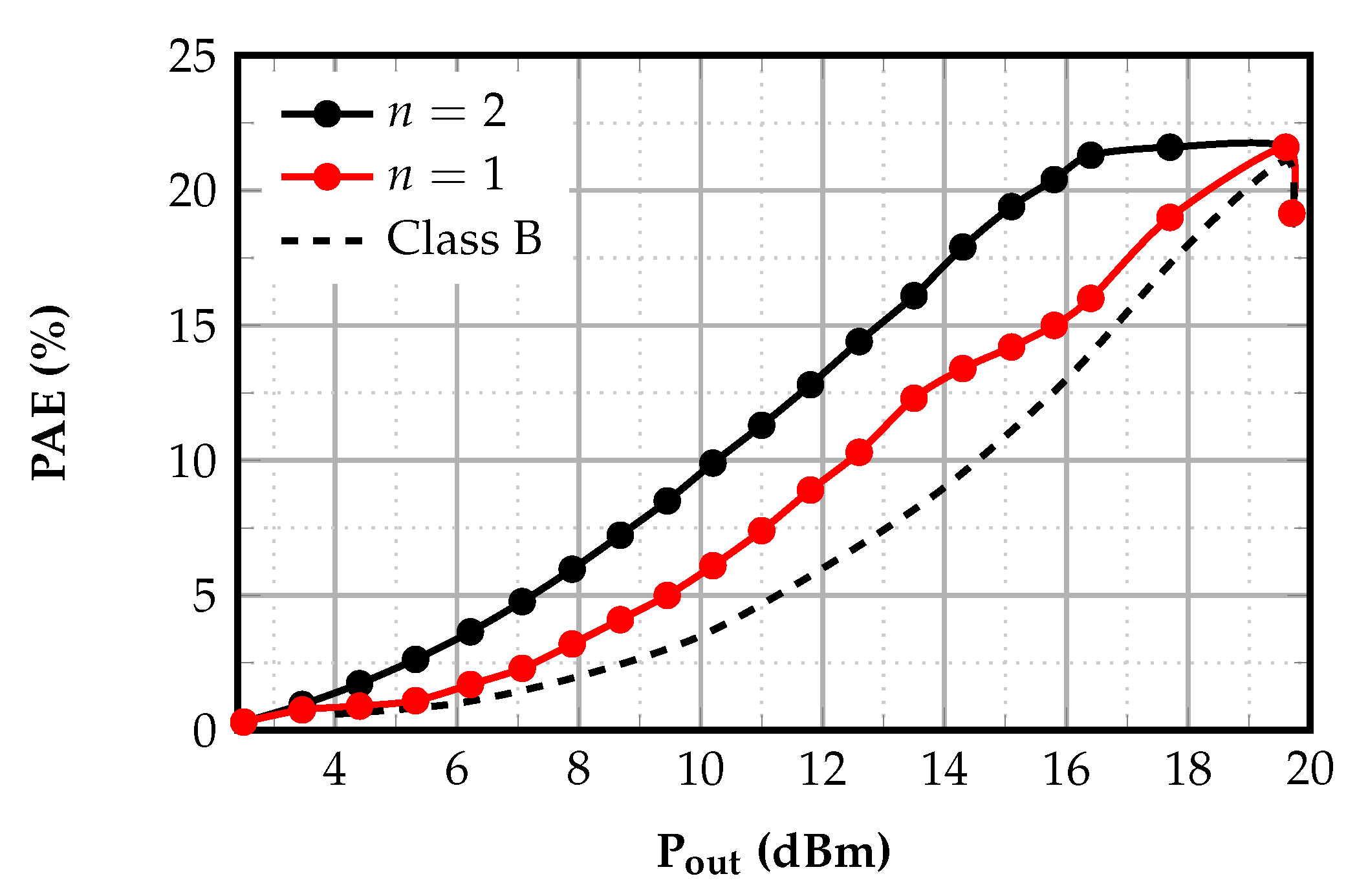

3.2.7. Efficiency Estimation

- Assumptions and sizing: The main PA is biased in Class AB with an assumed peak drain efficiency of . Its target is (), implying a DC draw of . At this corresponds to . The auxiliary device is sized for twice the main current at peak power, and the driver is budgeted at half the main current; hence,

- Predicted peak efficiency: The combined two-path target is (), giving an idealized peak drain efficiency of

- Realistic expectation: Accounting for the measured loss of the output match and quadrature combiner (hybrid) leads to a practical peak efficiency around ∼. This figure is intentionally conservative and will track upward with incremental loss reduction in the passive network and minor bias/drive tuning.

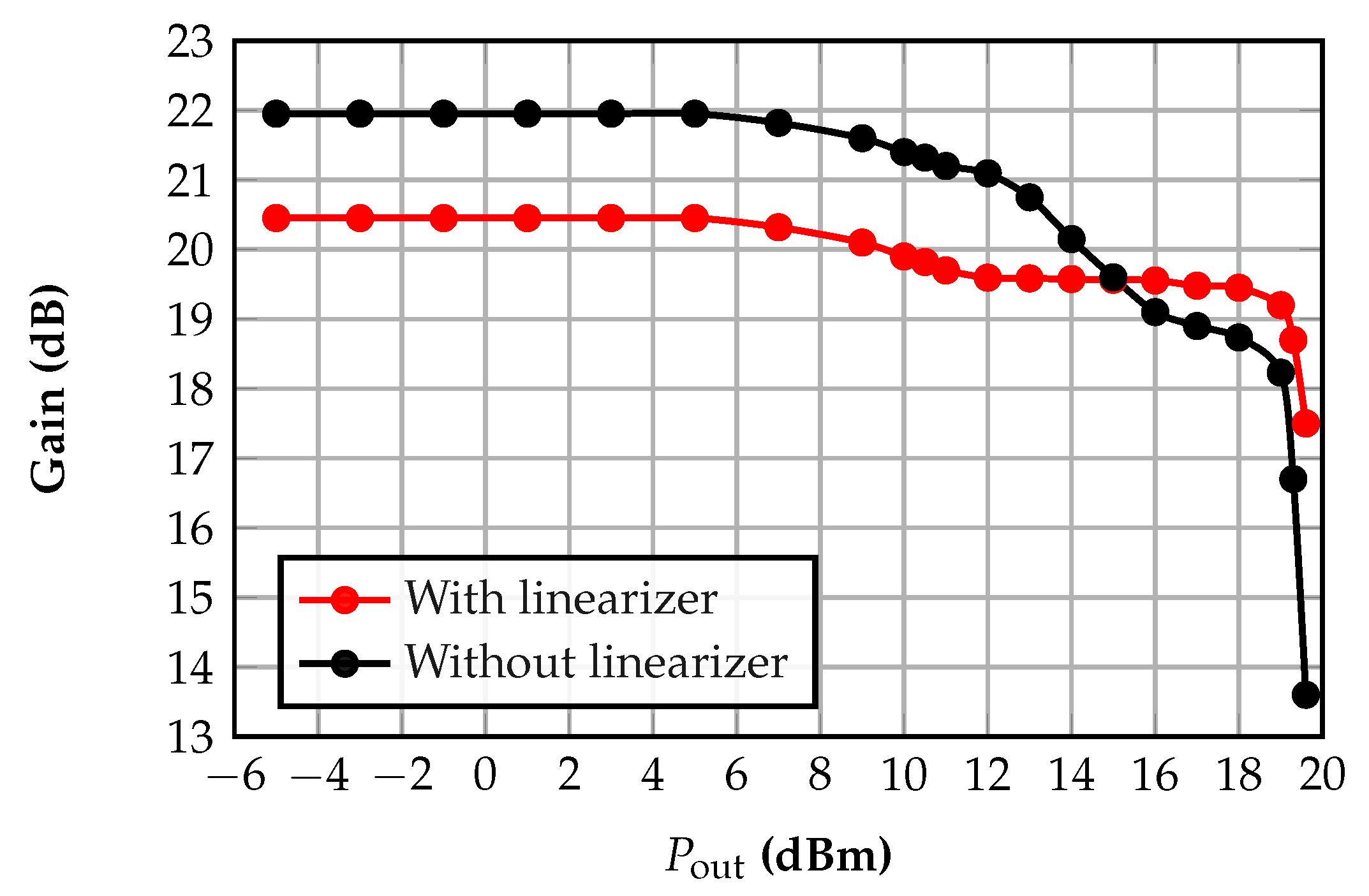

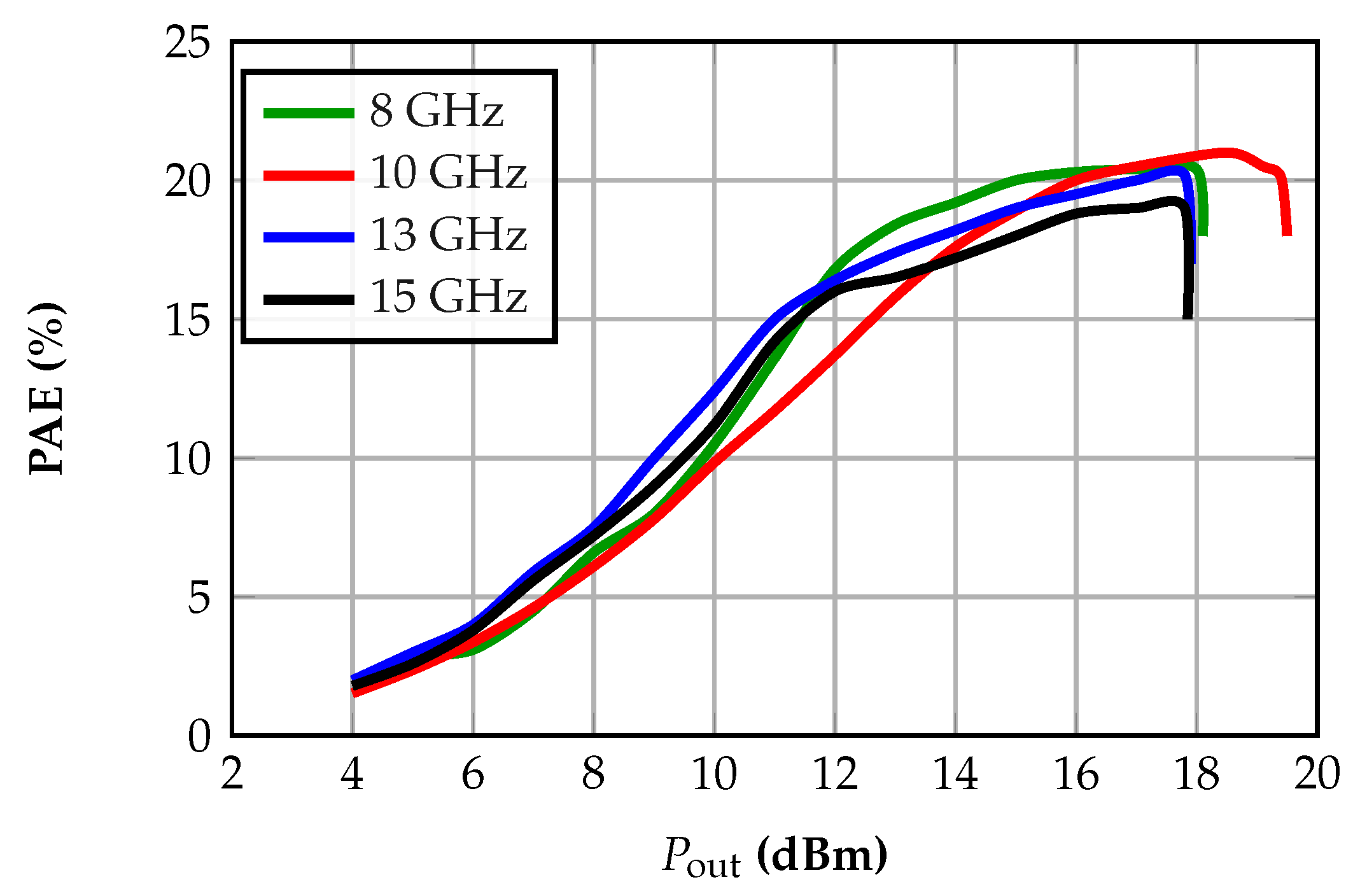

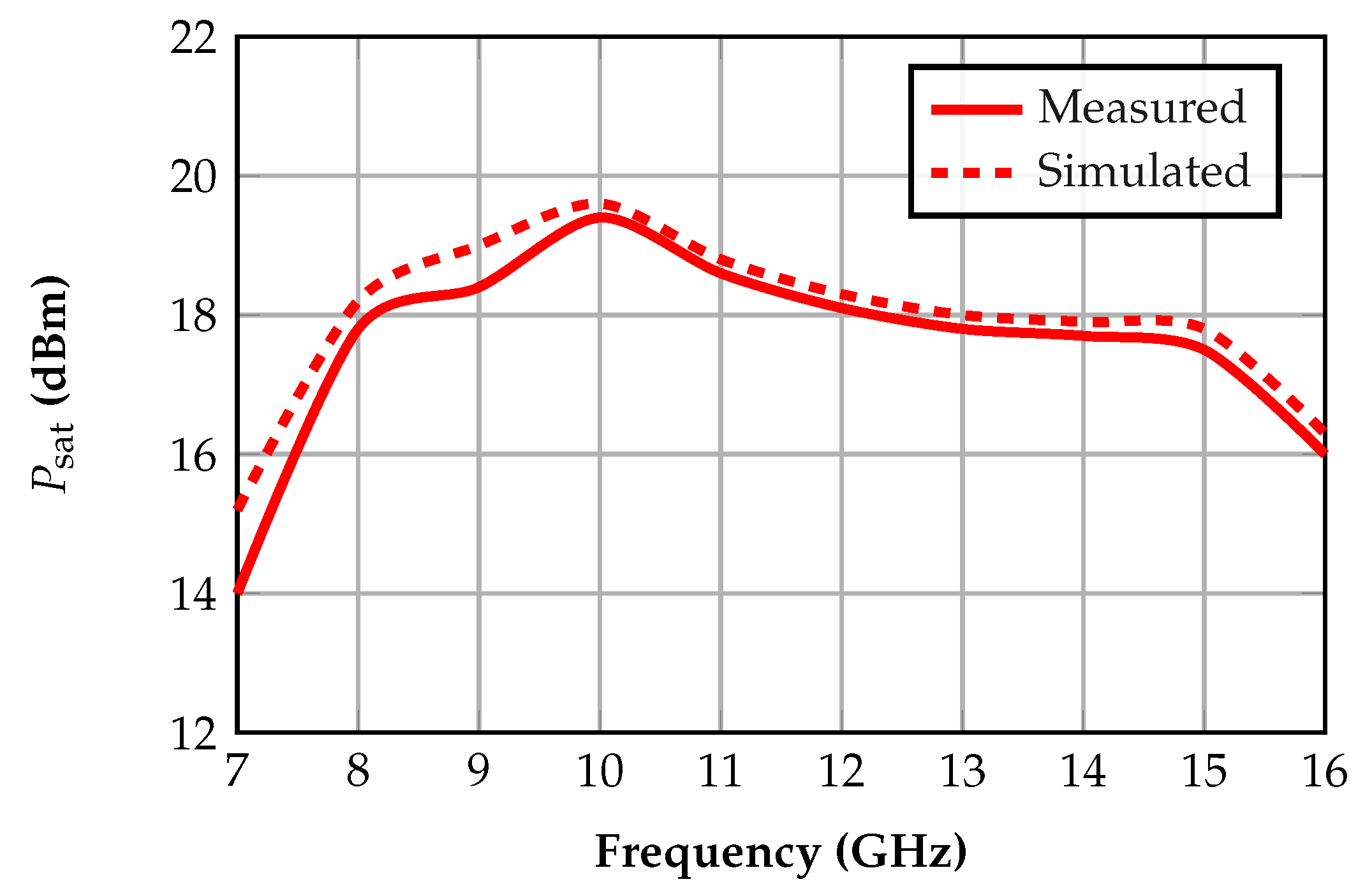

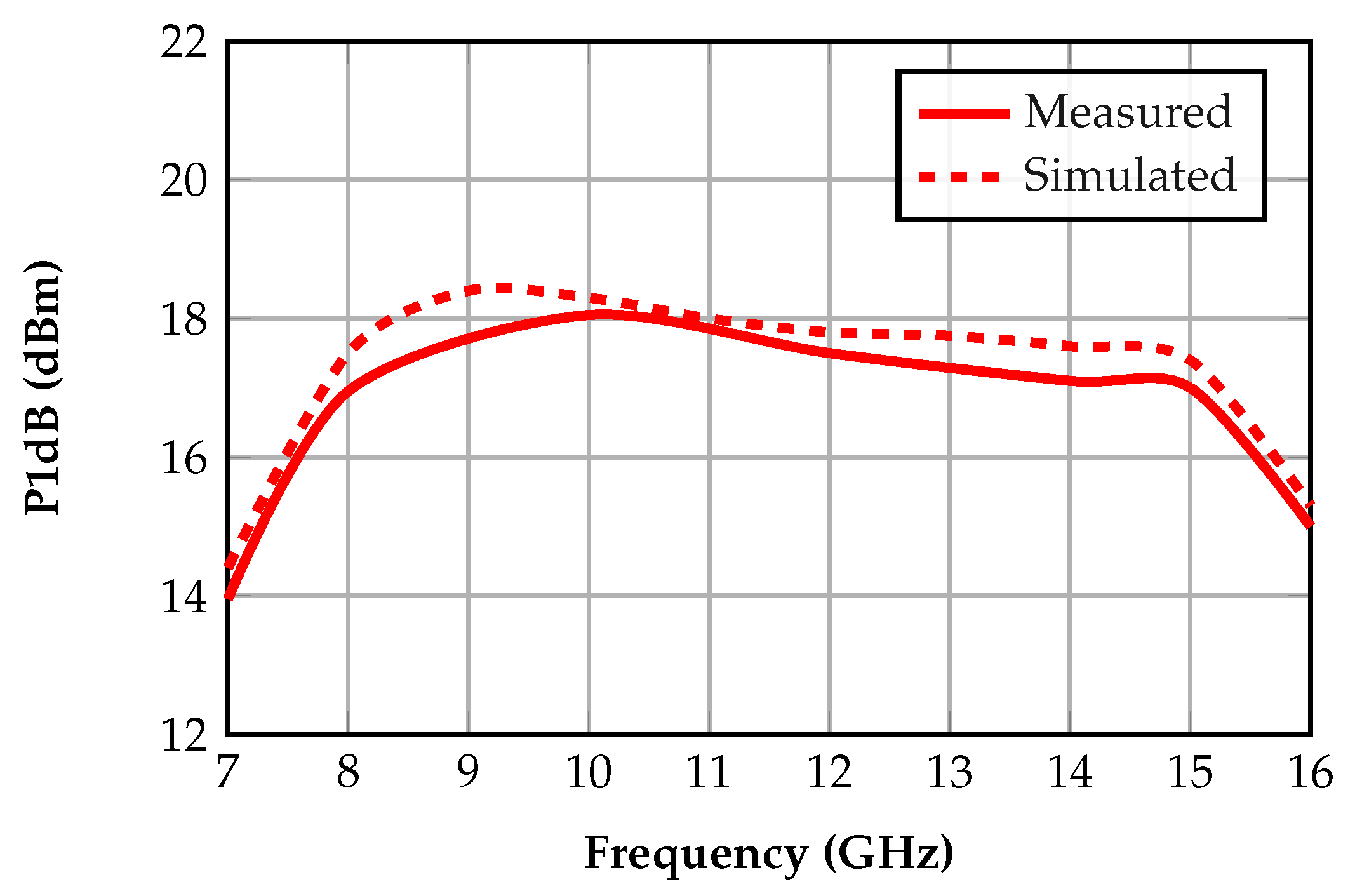

4. Measurements

Discussion and Synthesis

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Hedayati, M.K.; Abdipour, A.; Sarraf Shirazi, R.; Ammann, M.J.; John, M.; Cetintepe, C.; Staszewski, R.B. Challenges in On-Chip Antenna Design and Integration With RF Receiver Front-End Circuitry in Nanoscale CMOS for 5G Communication Systems. IEEE Access 2019, 7, 43190–43204. [Google Scholar] [CrossRef]

- Piacibello, A.; Figueiredo, R.; Quaglia, R.; Giofrè, R.; Colantonio, P.; Borges Carvalho, N.; Camarchia, V. Design and Extensive NPR Characterization of a Highly Linear SatCom GaN MMIC Doherty PA. IEEE Trans. Microw. Theory Tech. 2025, 73, 156–166. [Google Scholar] [CrossRef]

- Nyssens, L.; Rack, M.; Nabet, M.; Schwan, C.; Zhao, Z.; Lehmann, S.; Herrmann, T.; Henke, D.; Kondrat, A.; Soonekindt, C.; et al. High-resistivity with PN interface passivation in 22-nm FD-SOI technology for low-loss passives at RF and 387 millimeter-wave frequencies. Solid-State Electron. 2023, 205, 108656. [Google Scholar] [CrossRef]

- Camarchia, V.; Pirola, M.; Quaglia, R.; Jee, S.; Cho, Y.; Kim, B. The Doherty power amplifier: Review of recent solutions and trends. IEEE Trans. Microw. Theory Tech. 2015, 63, 559–571. [Google Scholar] [CrossRef]

- Grebennikov, A.; Bulja, S. Doherty Power Amplifiers: A Tutorial. IEEE Microw. Mag. 2012, 13, 100–114. [Google Scholar]

- Nikandish, G.; Staszewski, R.B.; Zhu, A. Breaking the bandwidth limit: A review of broadband Doherty power amplifier design for 5G. IEEE Microw. Mag. 2020, 21, 57–75. [Google Scholar] [CrossRef]

- Ku, B.-H.; Baek, S.-H.; Hong, S. A wideband transformer-coupled CMOS power amplifier for X-band multifunction chips. IEEE Trans. Microw. Theory Tech. 2011, 59, 1599–1609. [Google Scholar] [CrossRef]

- Mengozzi, M.; Maria Angelotti, A.; Gibiino, G.P.; Schulze, C.; Florian, C.; Colantonio, P.; Bengtsson, O.; Santarelli, A. Enhancing K-Band Dual-Input Doherty PA Performance by Bayesian Optimization. IEEE Trans. Microw. Theory Tech. 2025, 73, 3491–3502. [Google Scholar] [CrossRef]

- Yu, C.; Feng, J.; Zhao, D. A 28-GHz Doherty power amplifier with a compact transformer-based quadrature hybrid in 65-nm CMOS. IEEE Trans. Circuits Syst. II Express Briefs 2021, 68, 2790–2794. [Google Scholar] [CrossRef]

- Pozar, D.M. Microwave Engineering, 4th ed.; Wiley: Hoboken, NJ, USA, 2012. [Google Scholar]

- Cripps, S.C. RF Power Amplifiers for Wireless Communications, 3rd ed.; Artech House: Norwood, MA, USA, 2015. [Google Scholar]

- Bathich, K.; Hammi, O.; Ghannouchi, F.M. Frequency-Dependent Behavior of Doherty Power Amplifiers: Analysis and Design Considerations. IEEE Trans. Microw. Theory Techn. 2012, 60, 1390–1403. [Google Scholar]

- Chen, Y.-J.E.; Liu, C.-Y.; Luo, T.-N.; Heo, D. A High-Efficient CMOS RF Power Amplifier with Automatic Adaptive Bias Control. IEEE Microw. Wirel. Compon. Lett. 2006, 16, 615–617. [Google Scholar] [CrossRef]

- GlobalFoundries. Integrated 5G mmWave Infrastructure and SATCOM FEMs Using 22FDX® RF and 22FDX RF+; White Paper. 2021. Available online: https://gf.com/resource/integrated-5g-mmwave-infra-structure-and-satcom-fems-using-22fdx-rf-and-22fdx-rf/ (accessed on 19 October 2025).

- Rostomyan, N.; Jayamon, J.A.; Asbeck, P.M. 15 GHz Doherty Power Amplifier with RF Predistortion Linearizer in CMOS SOI. IEEE Trans. Microw. Theory Techn. 2018, 66, 1339–1348. [Google Scholar] [CrossRef]

- Kim, M.-G.; Kim, T.-H.; Lee, M.-K.; Park, J.-D. An X-Band Hybrid Three-Stack Power Amplifier with High Reliability in 65-nm Bulk CMOS. IEEE Microw. Wirel. Technol. Lett. 2025, 35, 1412–1415. [Google Scholar] [CrossRef]

- Trinh, V.-S.; Nam, H.; Park, J.-D. A 20.5-dBm X-Band Power Amplifier with a 1.2-V Supply in 65-nm CMOS Technology. IEEE Microw. Wirel. Compon. Lett. 2019, 29, 234–236. [Google Scholar] [CrossRef]

- Zong, Z.; Tang, X.; Khalaf, K.; Yan, D.; Mangraviti, G.; Nguyen, J.; Liu, Y.; Wambacq, P. A 28 GHz Voltage-Combined Doherty Power Amplifier with a Compact Transformer-Based Output Combiner in 22 nm FD-SOI. In Proceedings of the IEEE Radio Frequency Integrated Circuits Symposium (RFIC), Los Angeles, CA, USA, 4–6 August 2020; pp. 299–302. [Google Scholar] [CrossRef]

- Kim, S.; Park, H.-C.; Kang, D.; Minn, D.; Yang, S.-G. A 24.5–29.5 GHz Broadband Parallel-to-Series Combined Compact Doherty Power Amplifier in 28-nm Bulk CMOS for 5G Applications. In Proceedings of the IEEE Radio Frequency Integrated Circuits Symposium (RFIC), Atlanta, GA, USA, 7–9 June 2021; pp. 171–174. [Google Scholar] [CrossRef]

| Spec/Ref. | This Work | [15] † | [16] | [17] | [18] † | [19] † |

|---|---|---|---|---|---|---|

| Technology | 22 nm FD-SOI | 45 nm CMOS SOI | 65 nm Bulk CMOS | 65 nm Bulk CMOS | 22 nm FD-SOI | 28 nm Bulk CMOS |

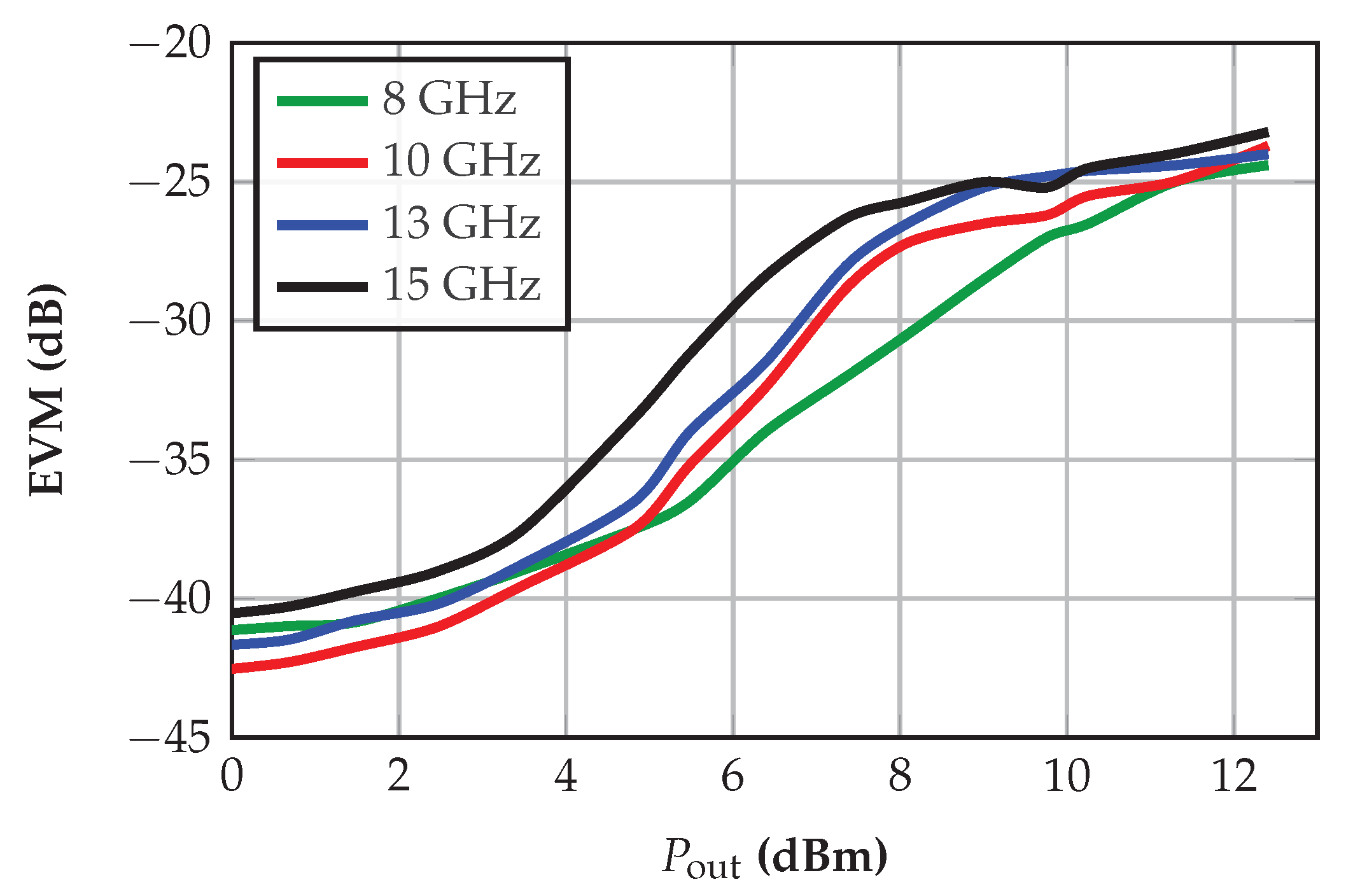

| Frequency (GHz) | 8–15 | 12–18 | 8.5–9.5 | 8–11.4 | 27–29 | 24.5–29.5 |

| FBW (%) | 61 | 40 | 11.1 | 35 | 7.1 | 18.5 |

| Gain (dB) | 19.6:17 | 16 | 23.2 | 24.4 | 26.1 | 16.5 |

| (dBm) | 19.5:18 | 25.5 | 20.9 | 20.5 | 22.5 | 18.8 |

| P1dB (dBm) | 18:17 | 25 | 16.5 | 15.2 | 21.1 | 17.5 |

| Peak PAE (%) | 21:19 | 31.9 | 24 | 24.5 | 28.5 | 30 |

| BO PAE (%) | 17:15 | 23 | N/A | 9 | 22.1 | 20 |

| Supply (V) | 3 | 2/4.8 | 3.3 | 1.2 | 2.4 | 1.8 |

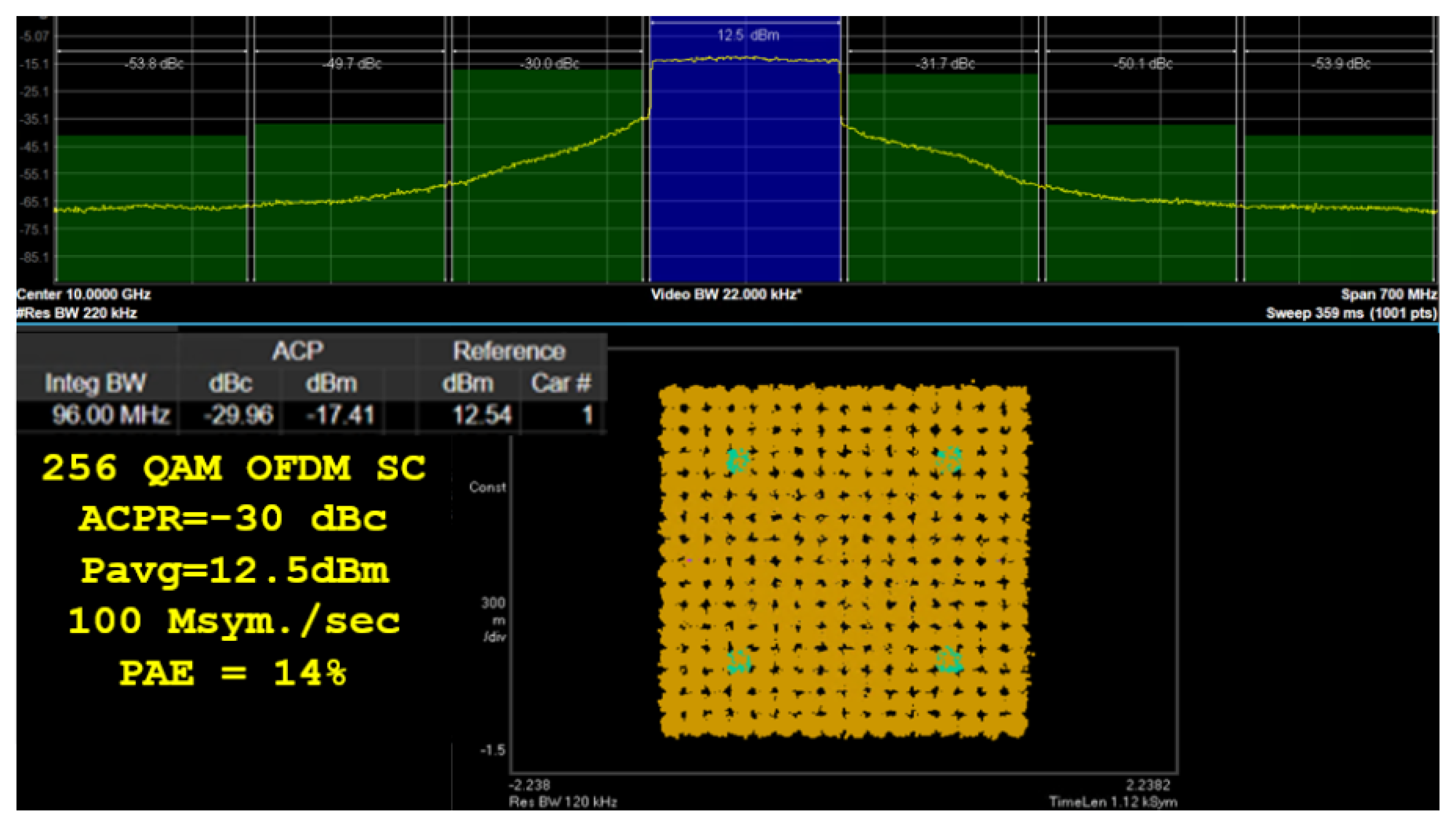

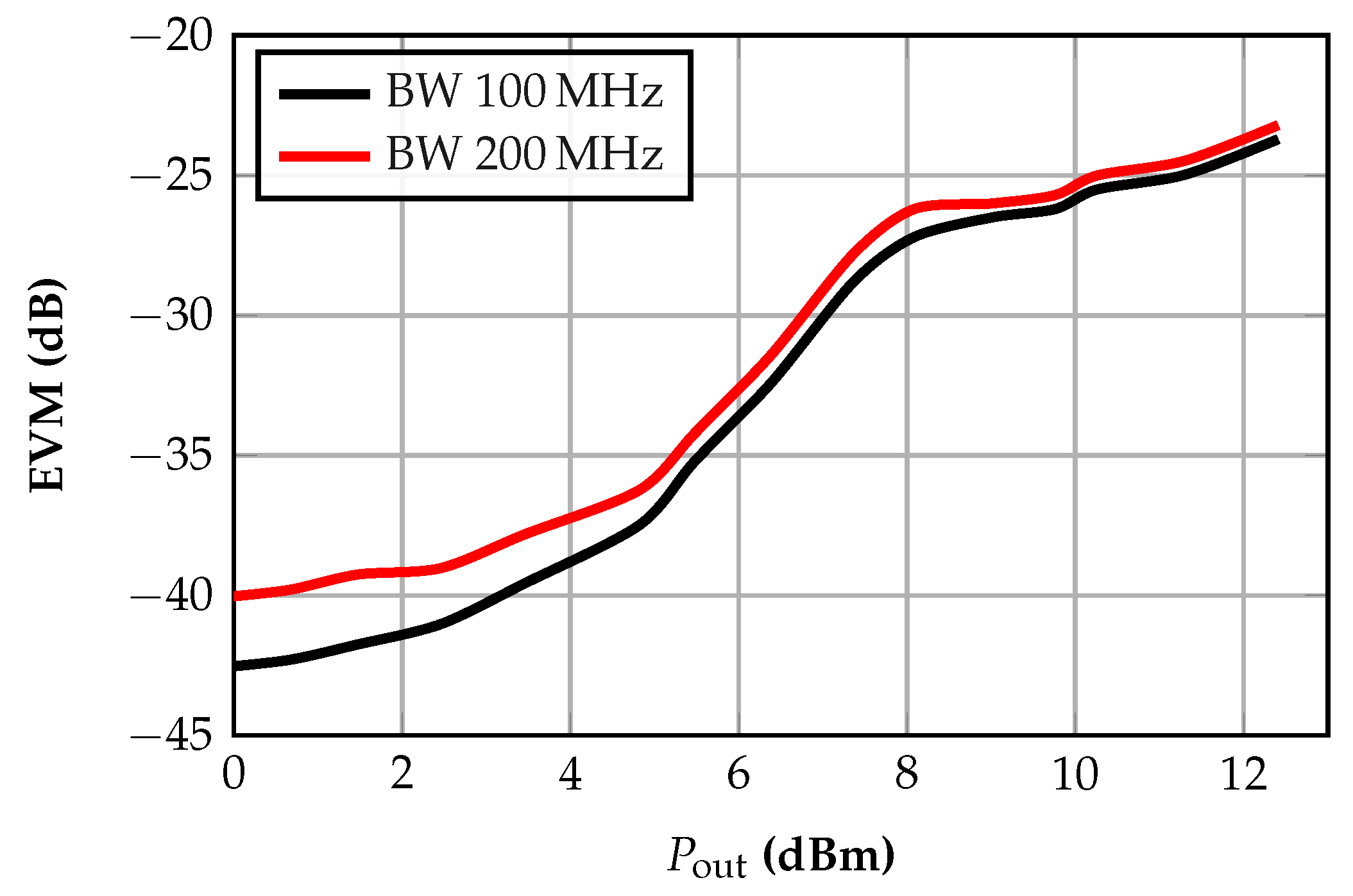

| Modulation | 256 QAM SC | 64 QAM SC | 256 QAM SC | N/A | 256 QAM SC | 64 QAM SC |

| Data rate (MSym/s) | 100 | 200 | 600 | N/A | 800 | 100 |

| EVM (dB) | −24.3 | −25 | −35.9 | N/A | −30 | −25 |

| Pavg (dBm) | 12.5 | 16.4 | 12.7 | N/A | 10.2 | 12.4 |

| BO level at Pavg (dB) | 7 | 9.1 | 8.2 | N/A | 12.3 | 6.4 |

| PAE% at Pavg | 15 | 15 | 4.58 | N/A | 9 | 20 |

| Die size (mm2) | 0.5 | 1 | 0.22 | 0.48 | 0.2 | 0.16 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Hussein, M.K.; Nafee, A.; Ahmed, M.G.; Ragaai, H.F.; El-Nozahi, M. An 8–15 GHz Doherty Power Amplifier with a Compact Quadrature-Hybrid-Based Output Combiner in 22 nm FD-SOI. Electronics 2025, 14, 4603. https://doi.org/10.3390/electronics14234603

Hussein MK, Nafee A, Ahmed MG, Ragaai HF, El-Nozahi M. An 8–15 GHz Doherty Power Amplifier with a Compact Quadrature-Hybrid-Based Output Combiner in 22 nm FD-SOI. Electronics. 2025; 14(23):4603. https://doi.org/10.3390/electronics14234603

Chicago/Turabian StyleHussein, Mohamed K., Adham Nafee, Mostafa G. Ahmed, Hani Fikri Ragaai, and Mohamed El-Nozahi. 2025. "An 8–15 GHz Doherty Power Amplifier with a Compact Quadrature-Hybrid-Based Output Combiner in 22 nm FD-SOI" Electronics 14, no. 23: 4603. https://doi.org/10.3390/electronics14234603

APA StyleHussein, M. K., Nafee, A., Ahmed, M. G., Ragaai, H. F., & El-Nozahi, M. (2025). An 8–15 GHz Doherty Power Amplifier with a Compact Quadrature-Hybrid-Based Output Combiner in 22 nm FD-SOI. Electronics, 14(23), 4603. https://doi.org/10.3390/electronics14234603