Design of a Bandgap Reference with a High PSRR and Strong Load-Driving Capability

Abstract

1. Introduction

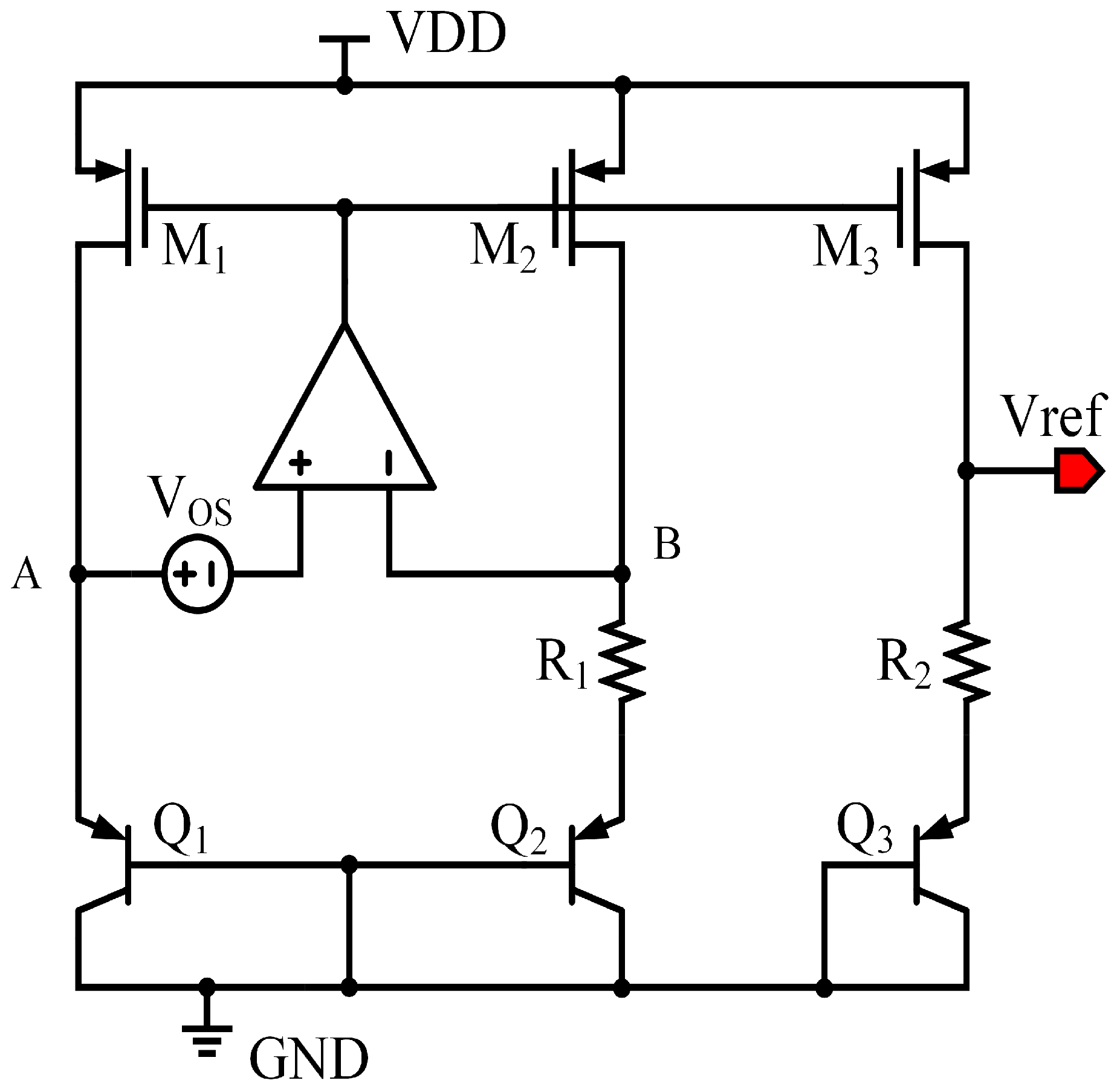

2. Conventional BGR and Comparison with the Proposed Method

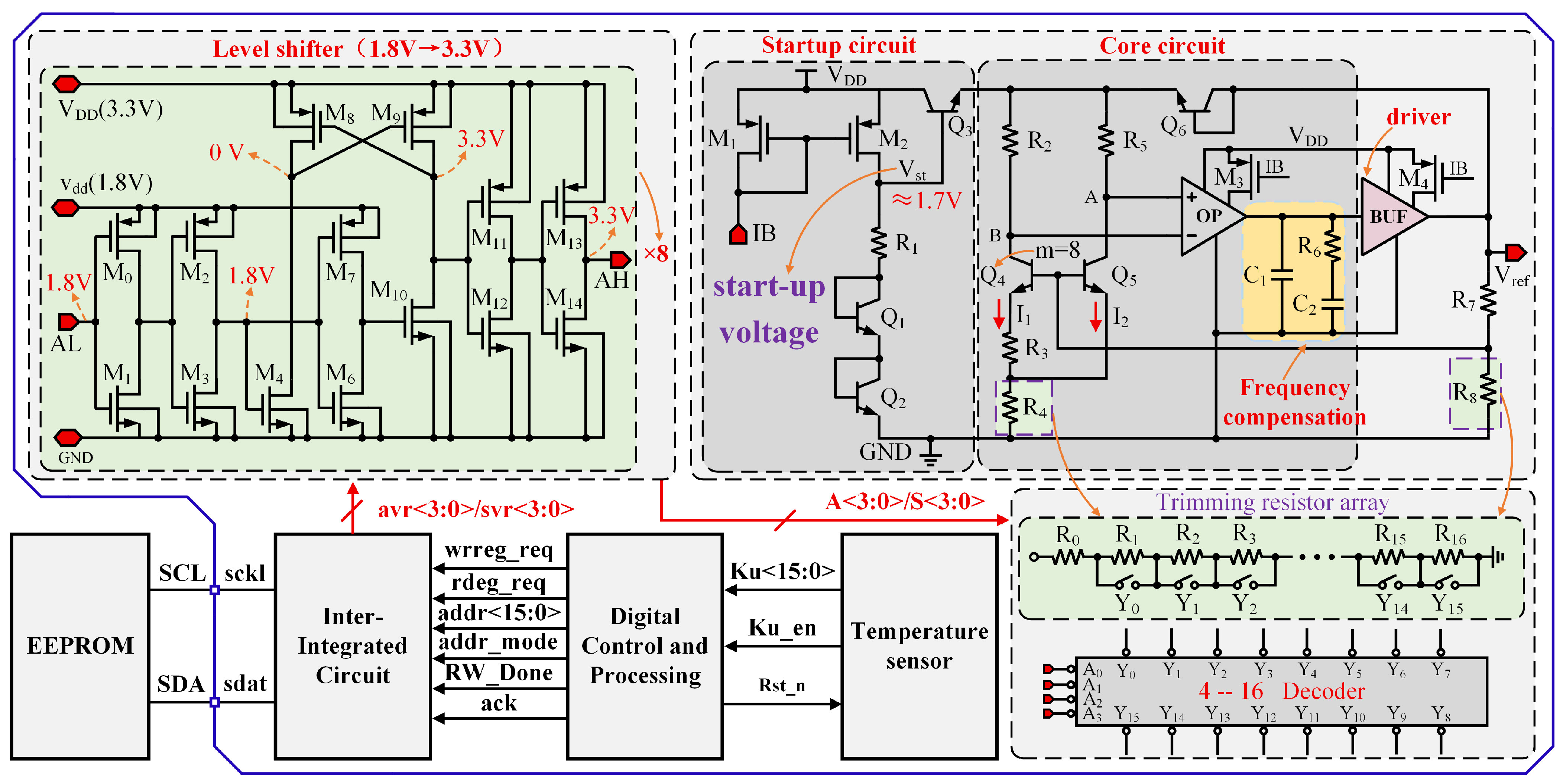

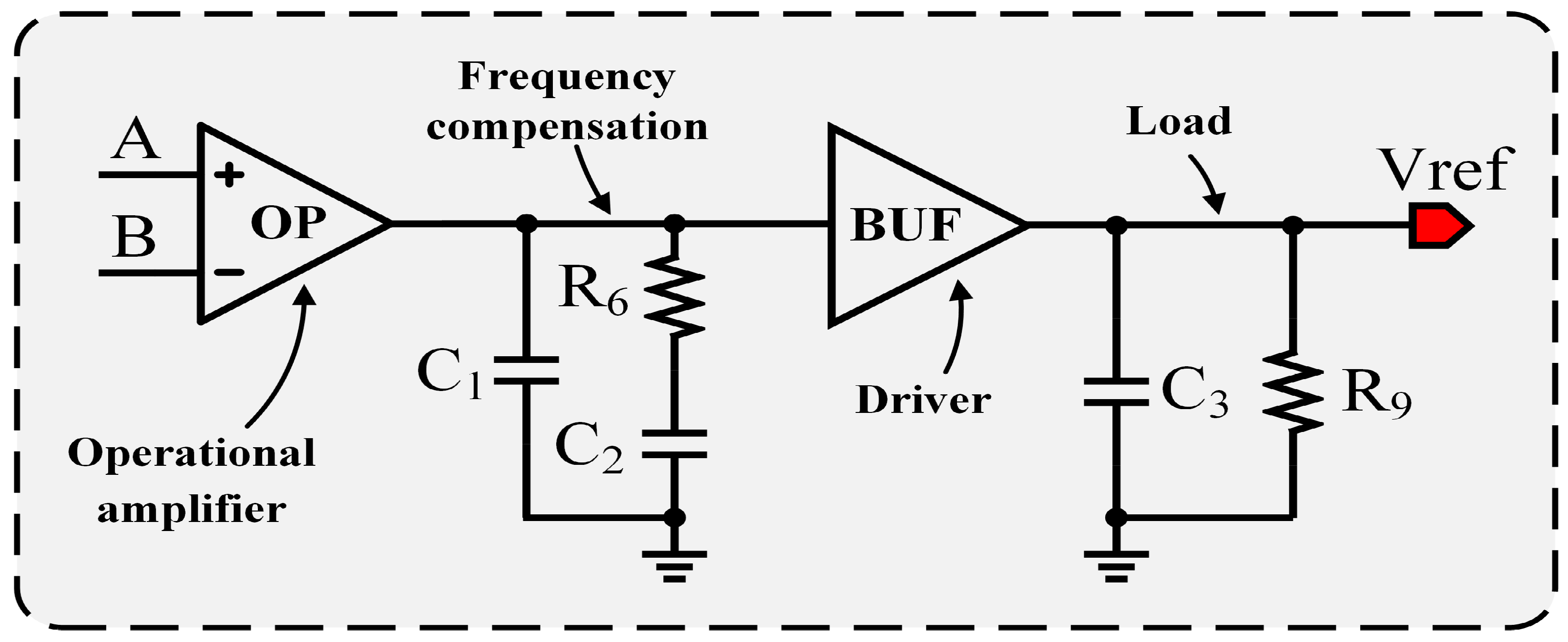

3. BGR Circuit Structure

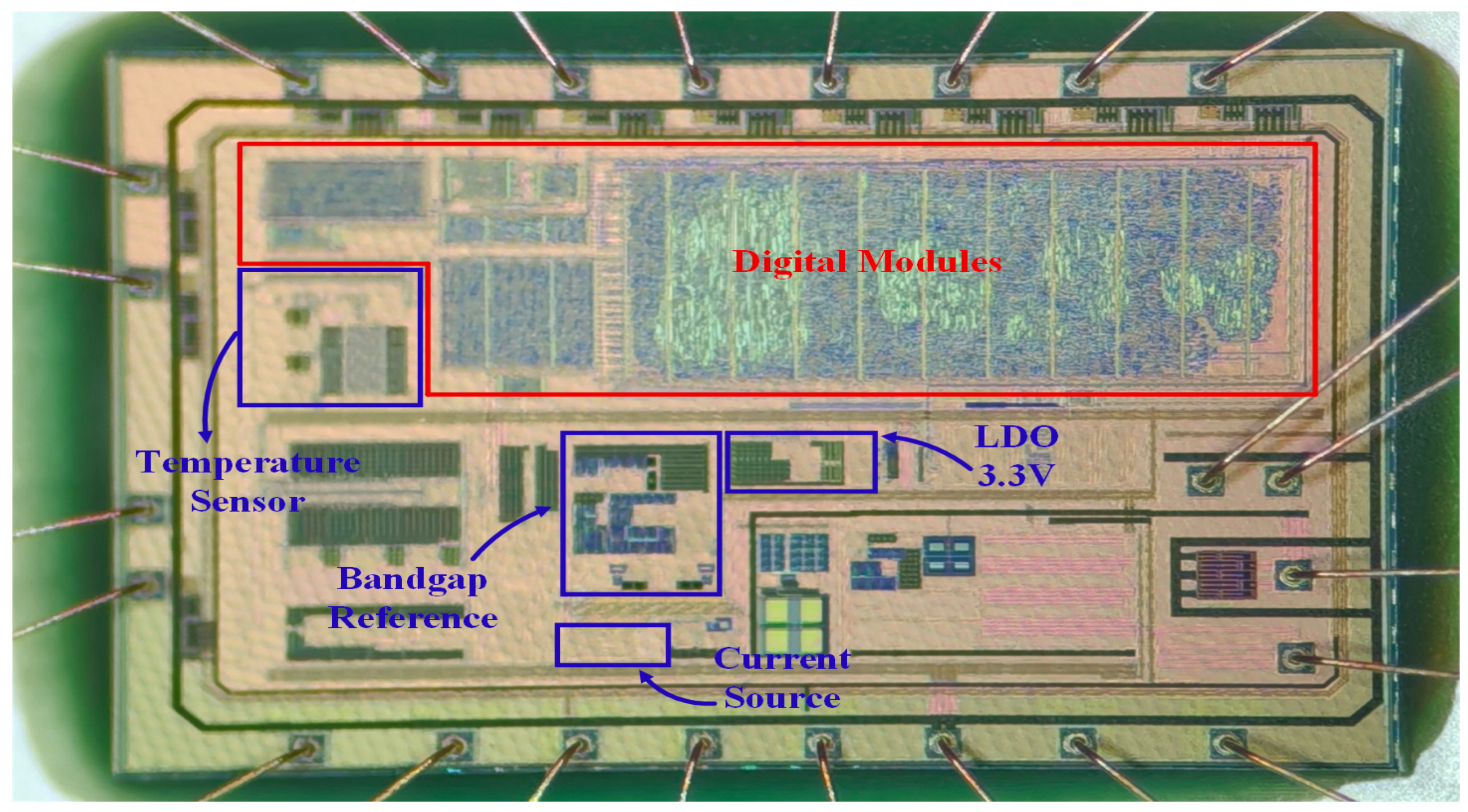

4. Circuit Architecture and Implementation

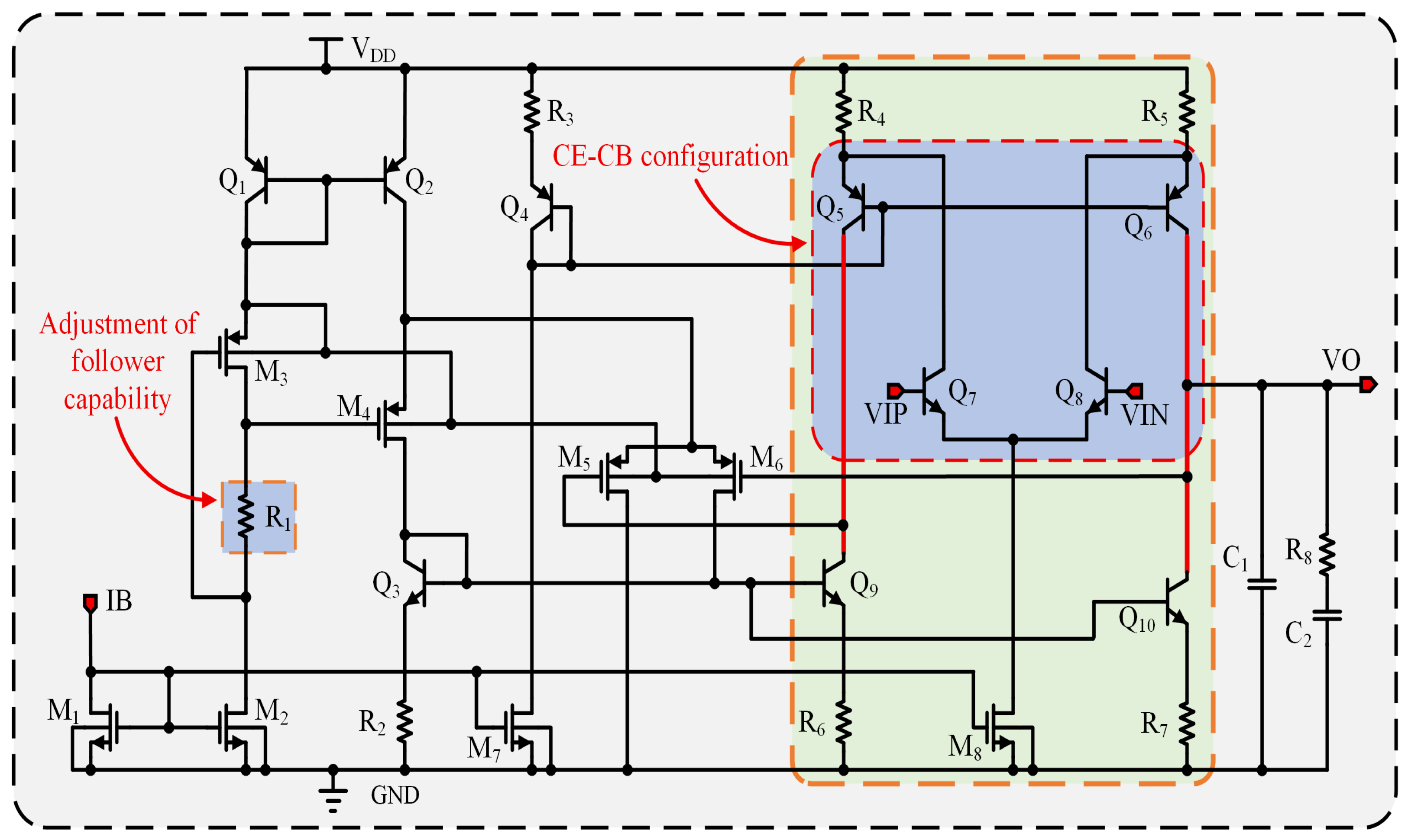

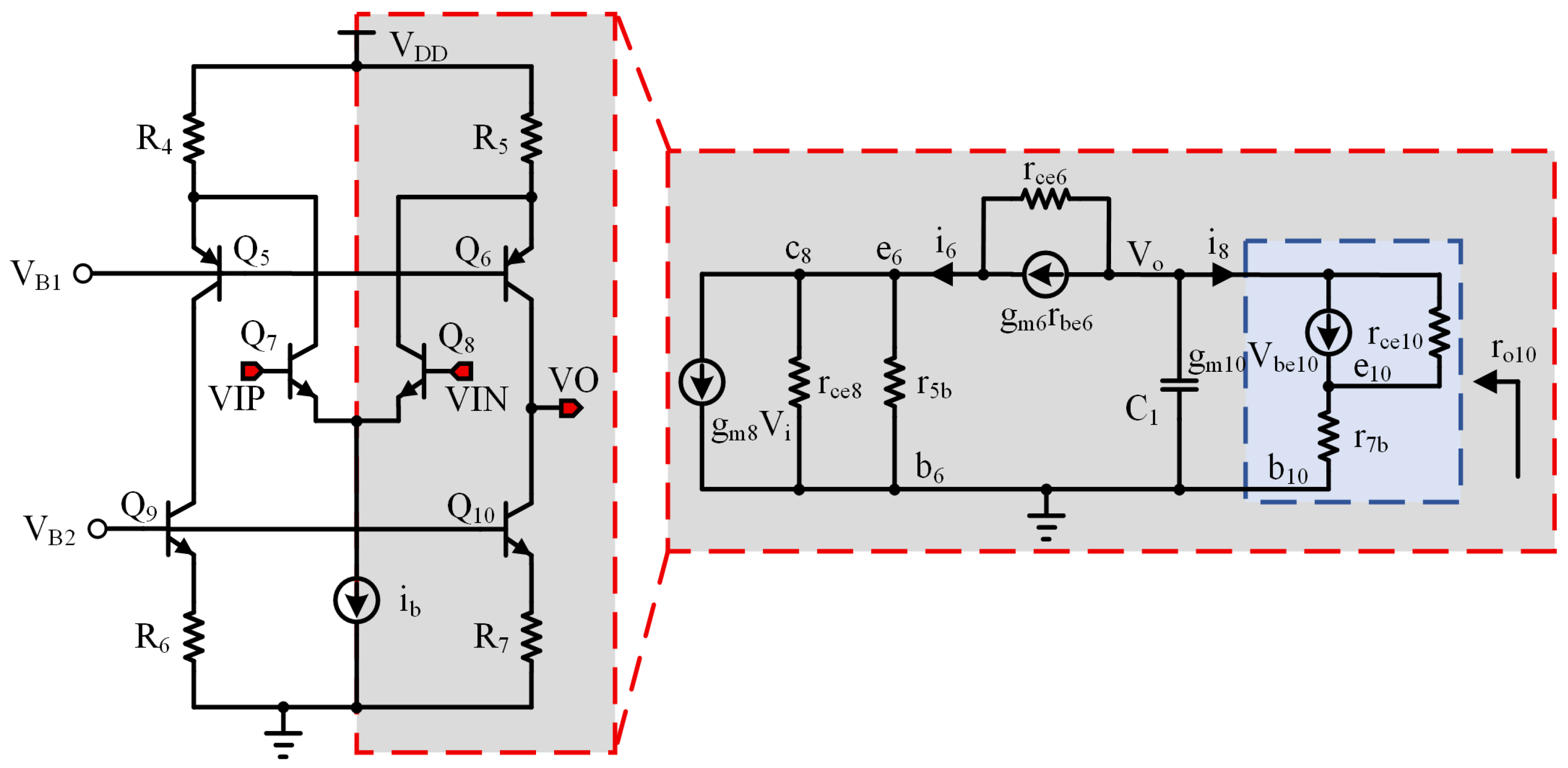

4.1. Amplifier Circuit Design

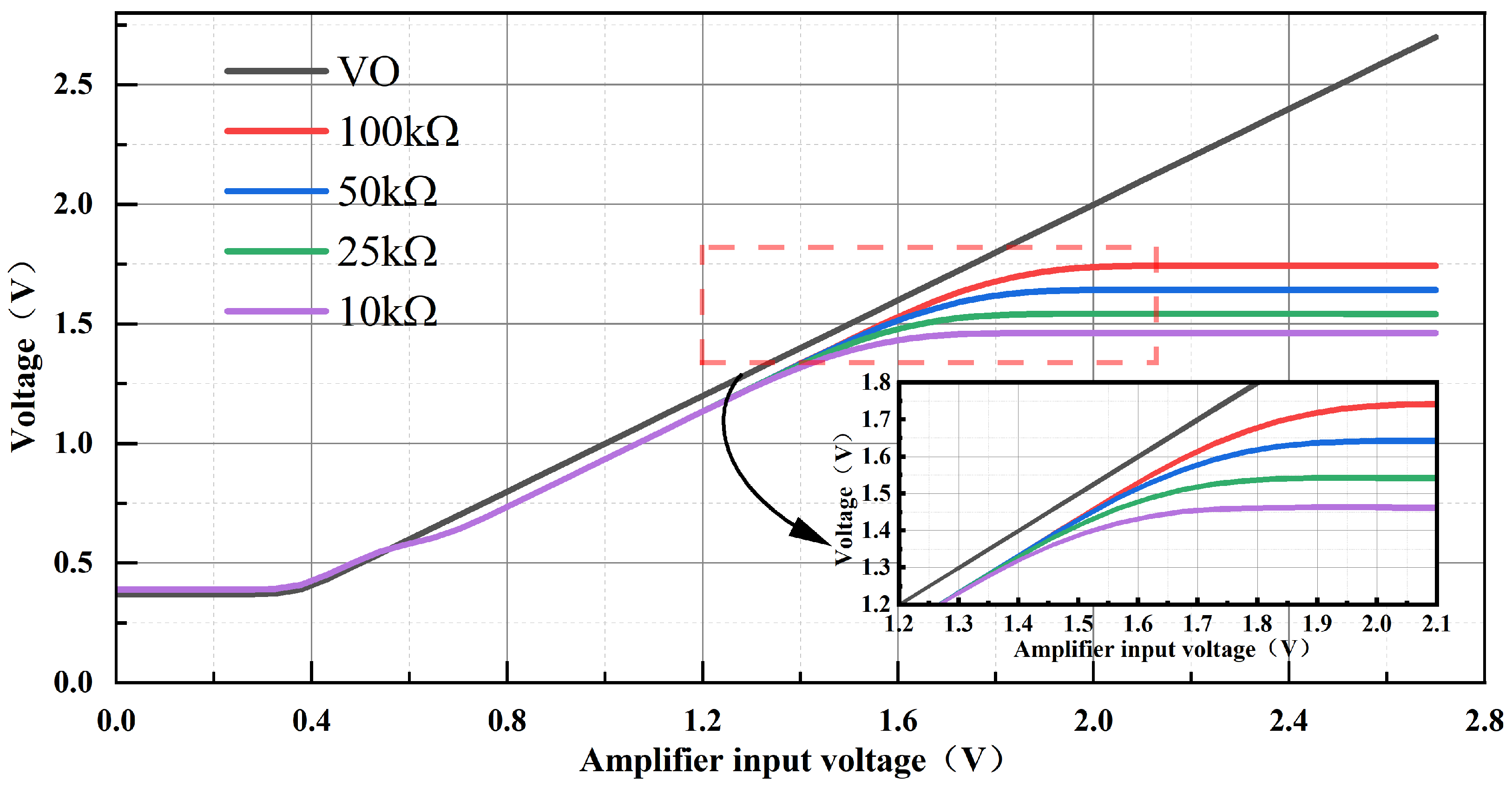

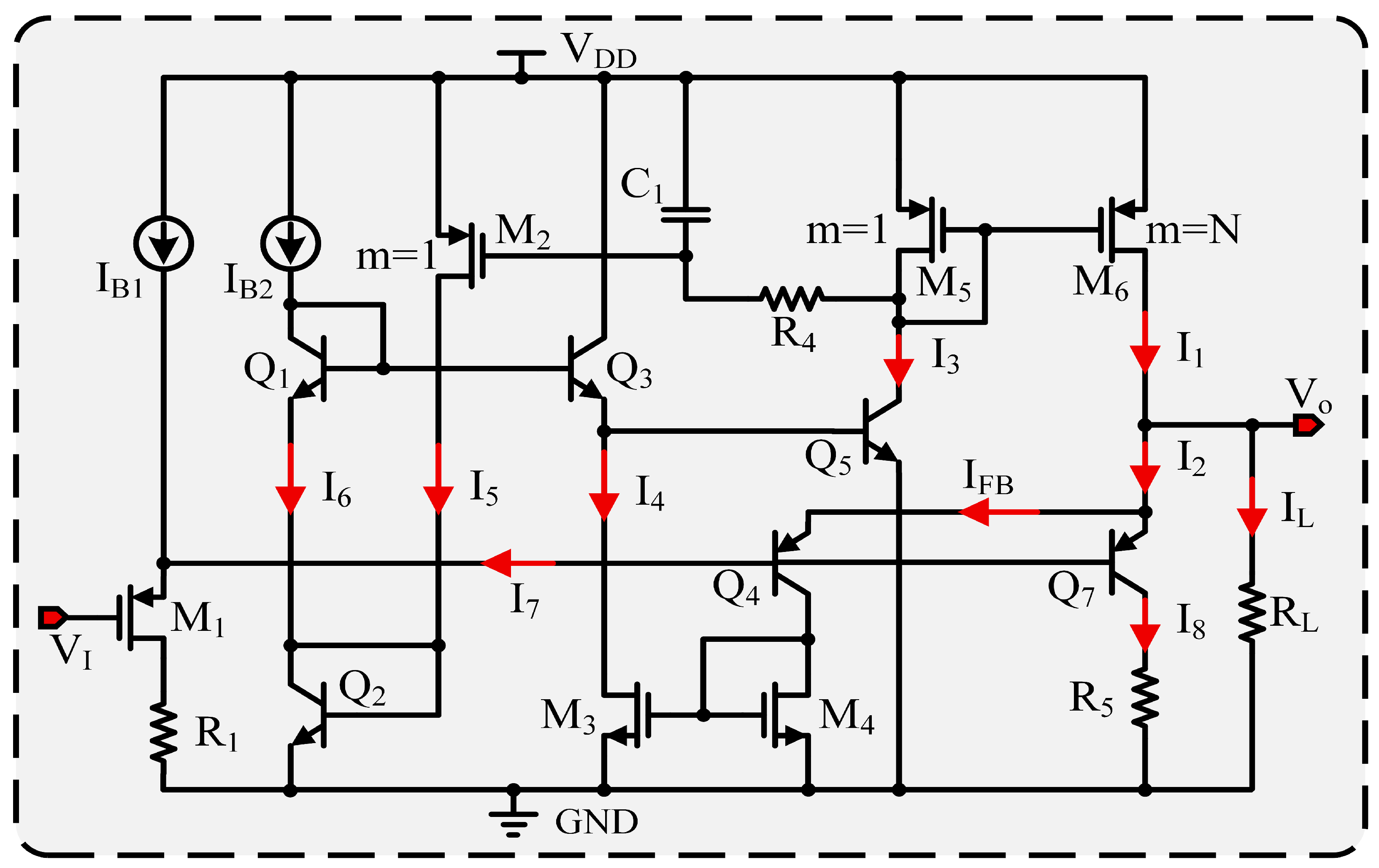

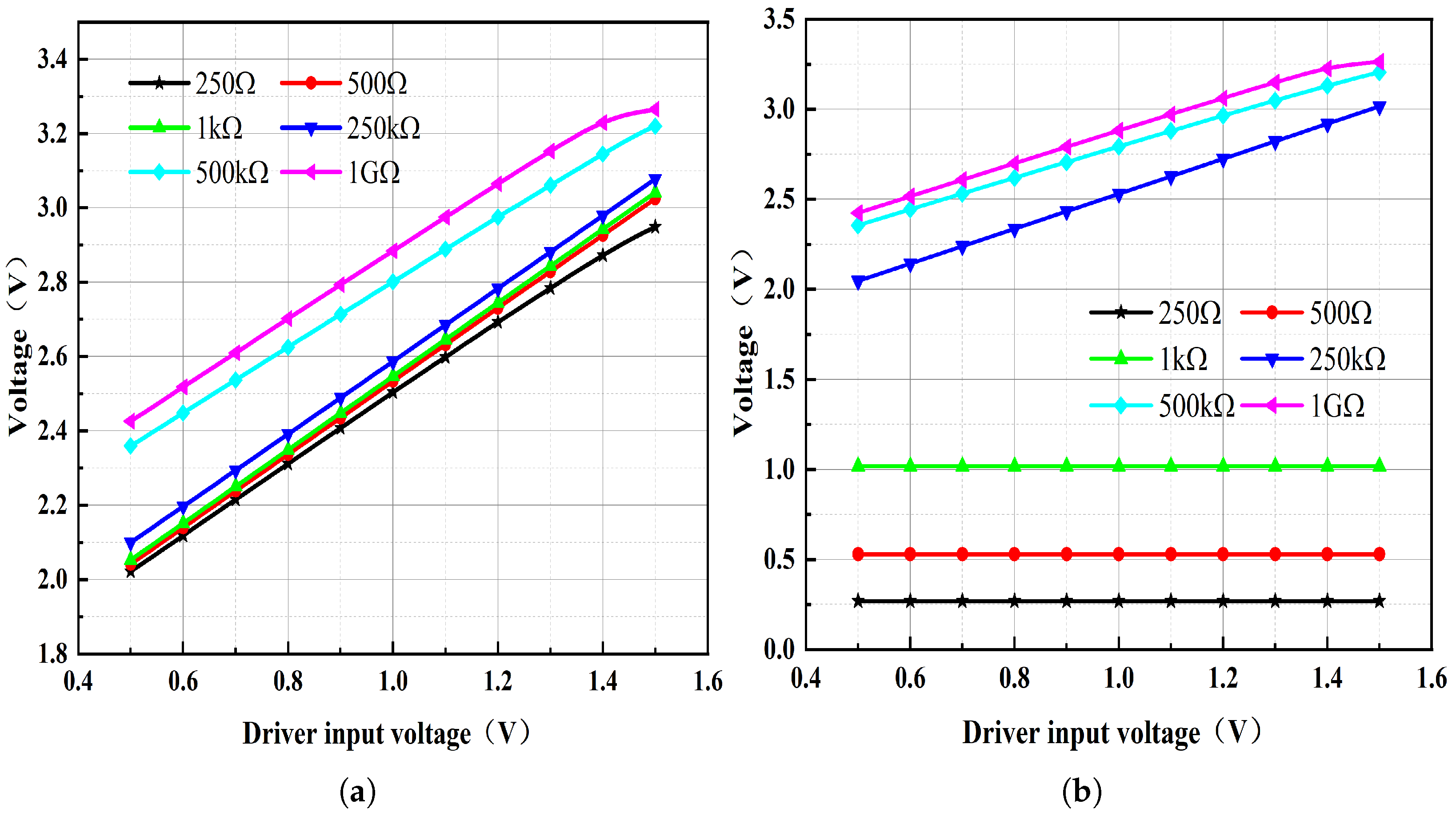

4.2. Driver Circuit Design

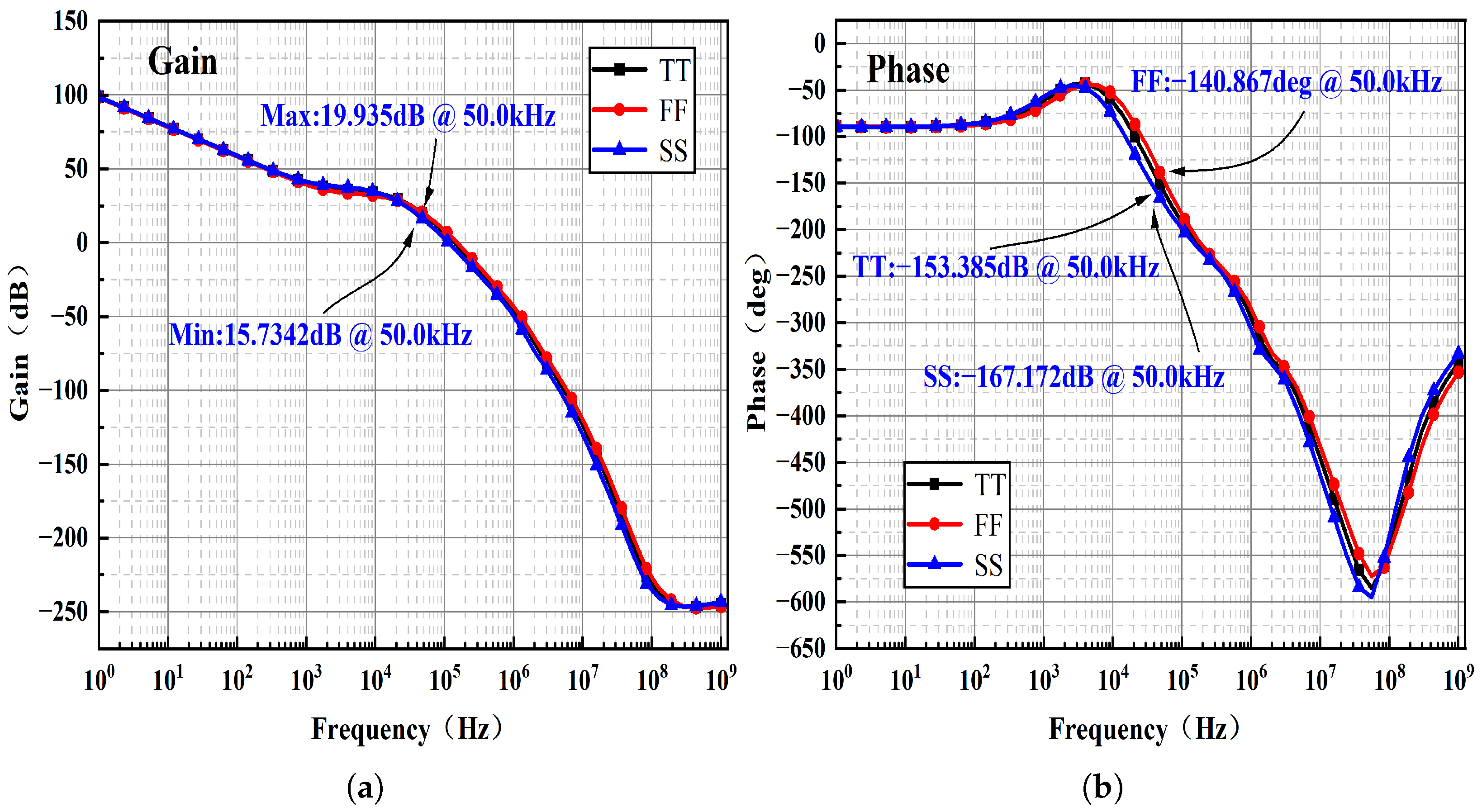

4.3. Frequency Compensation

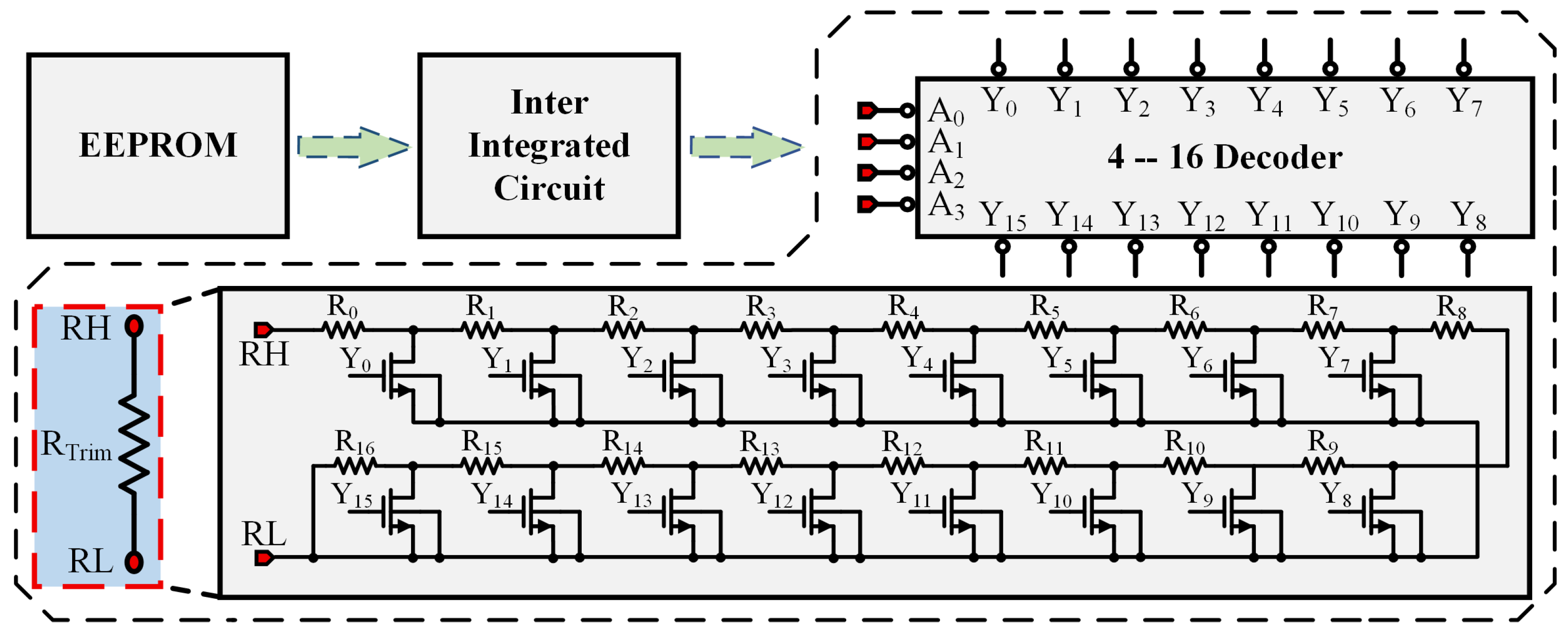

4.4. Switched Resistor Array Design

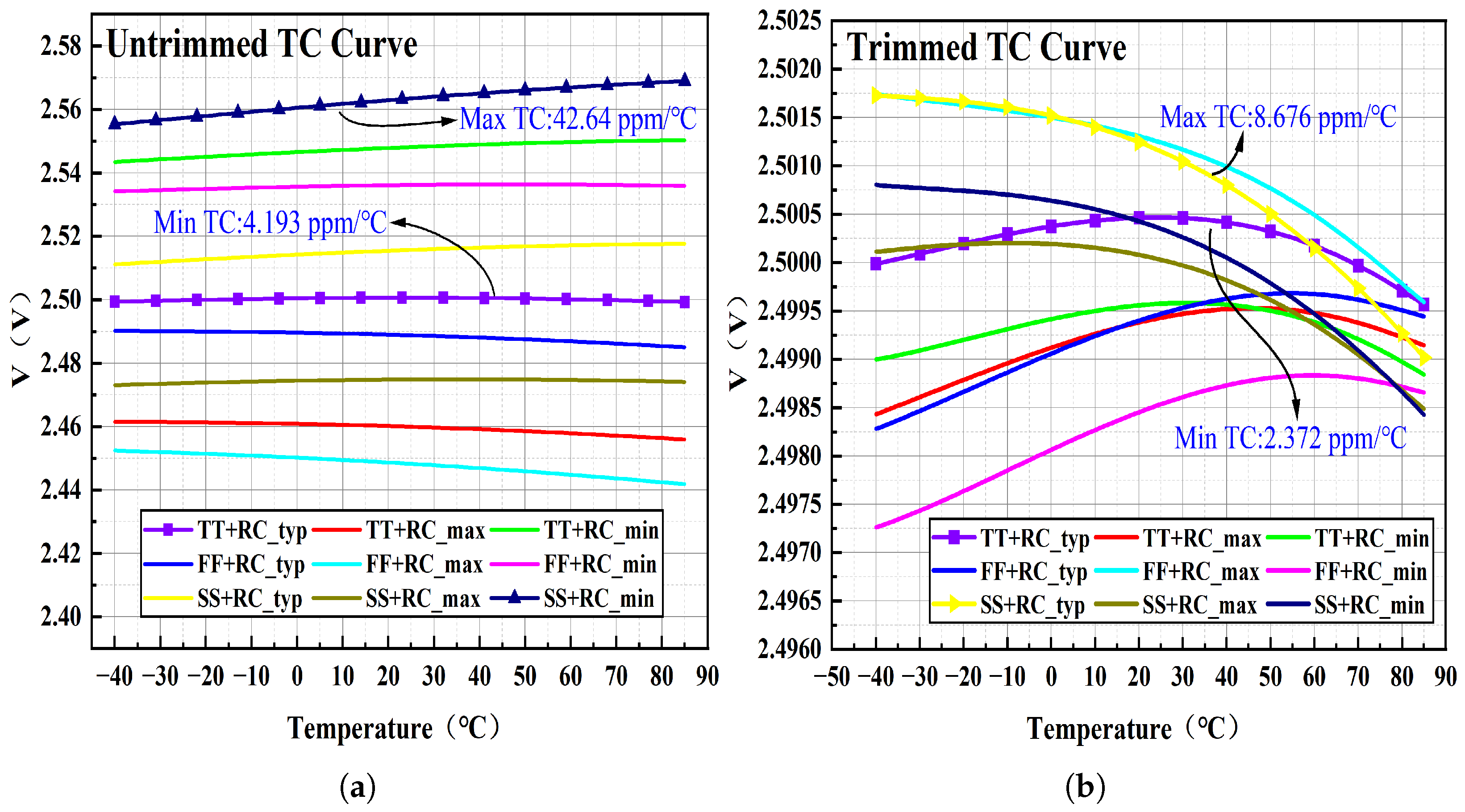

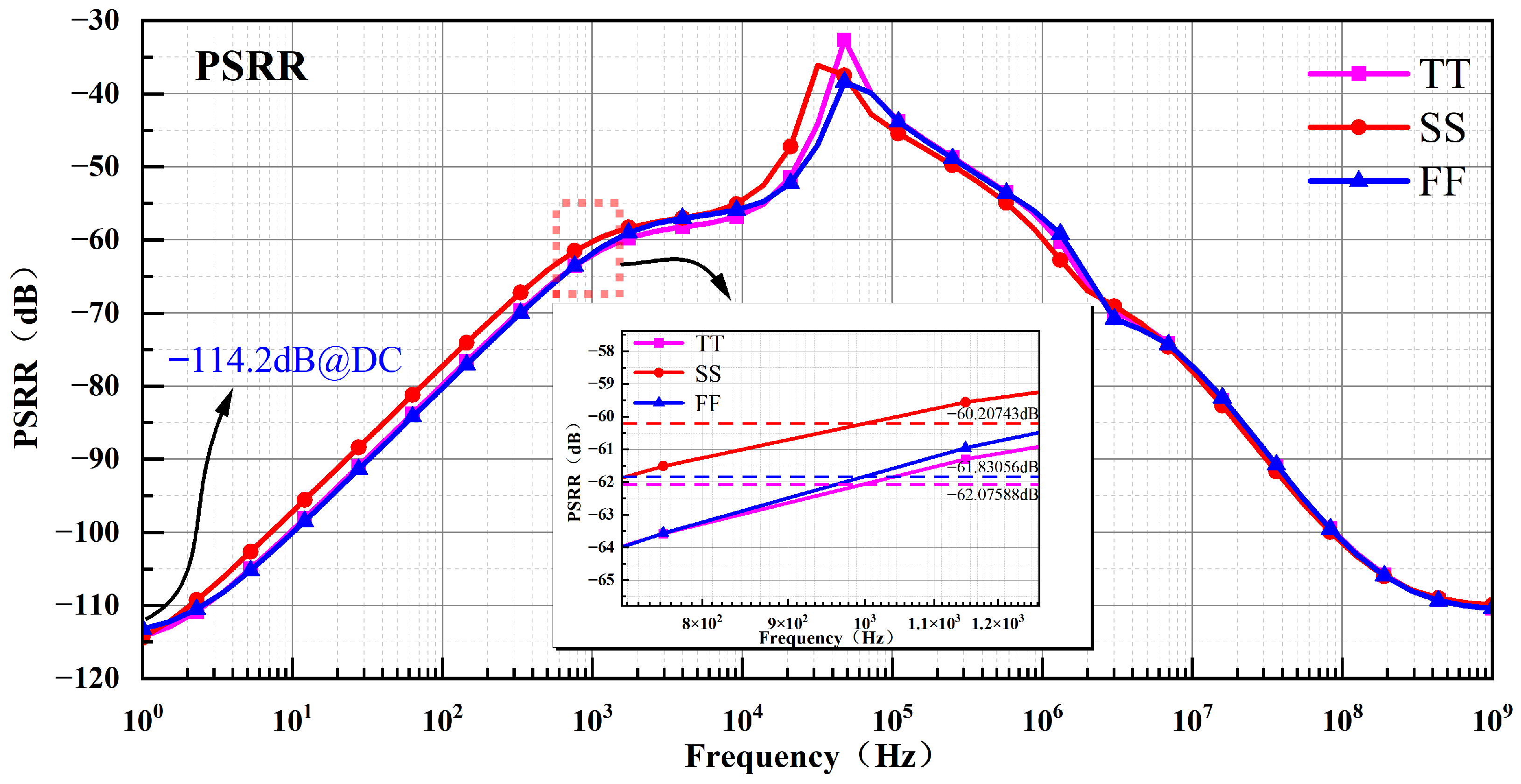

5. Simulation Results and Analysis

6. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Azimi, M.; Habibi, M.; Crovetti, P. A Two-Stage Sub-Threshold Voltage Reference Generator Using Body Bias Curvature Compensation for Improved Temperature Coefficient. Electronics 2024, 13, 1390. [Google Scholar] [CrossRef]

- Gagliardi, F.; Bruschi, P.; Piotto, M.; Sakouhi, S.; Dei, M. Single-Branch NMOS-Only Self-Cascoded Voltage Reference Operating Down to 0.28-V Supply. In Proceedings of the 23rd IEEE Interregional NEWCAS Conference (NEWCAS), Paris, France, 22–25 June 2025. [Google Scholar]

- Xue, W.; Yu, X.; Zhang, Y.; Ming, X.; Fang, J.; Ren, J. A 3.0-V 4.2-μA 2.23-ppm/°C BGR with Cross-Connected NPNs and Base-Current Compensation. Microelectron. J. 2024, 152, 106354. [Google Scholar] [CrossRef]

- Park, B.; Ji, Y.; Sim, J.Y. A 490-pW SAR Temperature Sensor with a Leakage-Based Bandgap-Vth Reference. IEEE Trans. Circuits Syst. II Express Briefs 2020, 67, 1549–1553. [Google Scholar] [CrossRef]

- Verma, D.; Shehzad, K.; Kim, S.J.; Pu, Y.G.; Yoo, S.-S.; Hwang, K.C.; Yang, Y.; Lee, K.-Y. A Design of 10-Bit Asynchronous SAR ADC with an On-Chip Bandgap Reference Voltage Generator. Sensors 2022, 22, 5393. [Google Scholar] [CrossRef] [PubMed]

- Tang, Z.; Liu, Y.; Chen, P.; Wang, H.; Yu, X.P.; Makinwa, K.A.; Tan, N.N. A 14-b BW/Power Scalable Sensor Interface with a Dynamic Bandgap Reference. IEEE J. Solid-State Circuits 2024, 59, 4077–4087. [Google Scholar] [CrossRef]

- Zhu, G.; Yang, Y.; Zhang, Q. A 4.6-ppm/°C High-Order Curvature Compensated Bandgap Reference for BMIC. IEEE Trans. Circuits Syst. II Express Briefs 2019, 66, 1492–1496. [Google Scholar] [CrossRef]

- Huang, S.; Li, M.; Li, H.; Yin, P.; Shu, Z.; Bermak, A.; Tang, F. A Sub-1-ppm/°C Bandgap Voltage Reference with High-Order Temperature Compensation in 0.18-μm CMOS Process. IEEE Trans. Circuits Syst. I Regul. Pap. 2022, 69, 1408–1416. [Google Scholar] [CrossRef]

- Hunter, B.L.; Matthews, J. A ±3 ppm/°C Single-Trim Switched Capacitor Bandgap Reference for Battery Monitoring Applications. IEEE Trans. Circuits Syst. I Regul. Pap. 2017, 64, 777–786. [Google Scholar] [CrossRef]

- Jia, S.; Ye, T.; Xiao, S. A 2.25 ppm/°C High-Order Temperature-Segmented Compensation Bandgap Reference. Electronics 2024, 13, 1499. [Google Scholar] [CrossRef]

- Nageib, E.; Ibrahim, S.; Dessouky, M. Resistor Variation Compensation for Enhanced Current Matching in Bandgap References. Electronics 2025, 14, 3808. [Google Scholar] [CrossRef]

- Zhu, X.; Cui, J.; Li, M.; Zhang, Y. A Piecewise Temperature-Curvature Compensation Bandgap with Internal Chopper-Stabilized Amplifiers. Microelectron. J. 2023, 142, 106021. [Google Scholar] [CrossRef]

- Zhuang, H.; Chen, X.; Zhang, E.; Li, Q. High-Accuracy Bandgap Reference of <20 ppm/·C: A Review. Chips 2025, 4, 5. [Google Scholar] [CrossRef]

- Xu, J.; Wang, Y.; Wu, M.; Zhang, R.; Wei, S.; Zhang, G.; Yang, C.F. A High-Accuracy Ultra-Low-Power Offset-Cancellation On–Off Bandgap Reference for Implantable Medical Electronics. Electronics 2019, 8, 814. [Google Scholar] [CrossRef]

- Ren, J.; Niu, Y.; Liu, B.; Li, M.; Bai, Y.; Chen, Y. Design of an SAR-Assisted Offset-Calibrated Chopper CFIA for High-Precision 4–20 mA Transmitter Front Ends. Appl. Sci. 2025, 15, 9084. [Google Scholar] [CrossRef]

- Chen, E.; Wu, T.; Yu, J.; Yin, L. A High-Precision Bandgap Reference with Chopper Stabilization and V-Curve Compensation Technique. Micromachines 2023, 15, 74. [Google Scholar] [CrossRef]

- Krolák, D.; Plojhar, J.; Horský, P. An Automotive Low-Power EMC Robust Brokaw Bandgap Voltage Reference. IEEE Trans. Electromagn. Compat. 2020, 62, 2277–2284. [Google Scholar] [CrossRef]

- Krolák, D.; Horský, P. An EMI Susceptibility Improved, Wide Temperature Range Bandgap Voltage Reference. IEEE Trans. Electromagn. Compat. 2024, 66, 801–808. [Google Scholar] [CrossRef]

- Yang, F.; Liu, Y.; Wang, C.; Zhao, Y.; Li, Y. High Precision Radiation Resistant Bandgap Voltage Regulator for Aerospace Applications. IEEE Trans. Circuits Syst. I Regul. Pap. 2025, 72, 6449–6457. [Google Scholar] [CrossRef]

- Liao, X.; Zhang, Y.; Zhang, S.; Liu, L. A 3.0 μVrms, 2.4 ppm/°C BGR with Feedback Coefficient Enhancement and Bowl-Shaped Curvature Compensation. IEEE Trans. Circuits Syst. I Regul. Pap. 2024, 71, 2424–2433. [Google Scholar] [CrossRef]

- Huang, W.; Liu, Y.; Zhu, Z. A Sub-200 nW All-in-One Bandgap Voltage and Current Reference Without Amplifiers. IEEE Trans. Circuits Syst. II Express Briefs 2021, 68, 121–125. [Google Scholar] [CrossRef]

- Khan, A.A.; Palani, R. Analysis and Design of Low-Noise Voltage Regulator with Integrated Single BJT Bandgap Reference up to 10 mA Loads. IEEE Trans. Circuits Syst. II Express Briefs 2024, 71, 2966–2970. [Google Scholar] [CrossRef]

- Chen, K.; Petruzzi, L.; Hulfachor, R.; Onabajo, M. A 1.16 V 5.8-to-13.5 ppm/°C Curvature-Compensated CMOS Bandgap Reference Circuit with a Shared Offset-Cancellation Method for Internal Amplifiers. IEEE J. Solid-State Circuits 2021, 56, 267–276. [Google Scholar] [CrossRef]

- Qi, E.; Fang, C.; Zhang, Y.; Cheng, Y.; Wang, N. A wide input low quiescent current without operational amplifier bandgap reference circuit. In Proceedings of the 2023 8th International Conference on Integrated Circuits and Microsystems (ICICM), Nanjing, China, 20–23 October 2023. [Google Scholar] [CrossRef]

- Zhu, G.; Huang, X.; You, Y.; Li, Y.; Guo, W.; Zhu, Z. Multi-Cell Battery Sensing and Protection IC with Integrated Low-Temperature-Drift Reference for Series Battery Pack Management. IEEE Trans. Circuits Syst. I Regul. Pap. 2025, 72, 5634–5645. [Google Scholar] [CrossRef]

- Lee, C.-F.; U, C.-W.; Martins, R.P.; Lam, C.S. 0.4-V Supply, 12-nW Reverse Bandgap Voltage Reference with Single BJT and Indirect Curvature Compensation. IEEE Trans. Circuits Syst. I Regul. Pap. 2024, 71, 5040–5053. [Google Scholar] [CrossRef]

- Wang, Z.; Li, Z.; Xia, X.; Yu, J.; Zhou, P.; Chen, J.; Guo, Y.; Hong, W. A 247–272-GHz SiGe Frequency Doubler with 8.2-dBm Psat Enhanced by Optimized Fundamental Load Impedance and Hybrid-Mode Driver Amplifier. IEEE Trans. Microw. Theory Tech. 2025, 73, 6477–6490. [Google Scholar] [CrossRef]

- Hou, Y.; Yu, W.; Yu, Q.; Wang, B.; Sun, Y.; Cheng, W.; Zhou, M. A 56–161 GHz Common-Emitter Amplifier with 16.5 dB Gain Based on InP DHBT Process. Electronics 2021, 10, 1654. [Google Scholar] [CrossRef]

- Kantor, M.; Molinazzi, N.; Shmilovich, T.; Krylov, S. Low-Cost Polymeric Energy Harvester as Vibration Intensity Sensor. IEEE Sens. Lett. 2025, 9, 2500604. [Google Scholar] [CrossRef]

- Albalooshi, A.; Jallad, A.-H.M.; Marpu, P.R. Fault Analysis and Mitigation Techniques of the I2C Bus for Nanosatellite Missions. IEEE Access 2023, 11, 34709–34717. [Google Scholar] [CrossRef]

- Huang, Z.; Tang, Z.; Yu, X.-P.; Shi, Z.; Lin, L.; Tan, N.N. A BJT-Based CMOS Temperature Sensor with Duty-Cycle-Modulated Output and ±0.5 °C (3σ) Inaccuracy from -40°C to 125 °C. IEEE Trans. Circuits Syst. II Express Briefs 2021, 68, 2780–2784. [Google Scholar] [CrossRef]

- Yousefzadeh, B.; Heidary Shalmany, S.; Makinwa, K.A. A BJT-Based Temperature-to-Digital Converter with ±60 mK (3σ) Inaccuracy from -55°C to +125°C in 0.16-μm CMOS. IEEE J. Solid-State Circuits 2017, 52, 1044–1052. [Google Scholar] [CrossRef]

- Ren, J.; Wang, H.; Li, M.; Liu, B.; Xiao, J.; Zhao, W. A Wide-Input-Range LDO with High Output Accuracy Based on Digital Trimming Technique. Electronics 2025, 14, 4299. [Google Scholar] [CrossRef]

| Parameter | This Work | [20] | [21] | [22] | [23] |

|---|---|---|---|---|---|

| Technology (nm) | 180 | 180 | 180 | 180 | 180 |

| Temperature Range (°C) | −40~85 | −45~125 | −45~125 | −45~125 | −40~150 |

| Supply Voltage (V) | 2.7~9.2 | 1.1~1.8 | 2.0~5.0 | 1.2 | 3.3 |

| Current Consumption (μA) | 69 | 60 | – | 400 | 120 |

| Reference Voltage (V) | 2.5 | 0.6 | 1.2 | 0.955 | 1.16 |

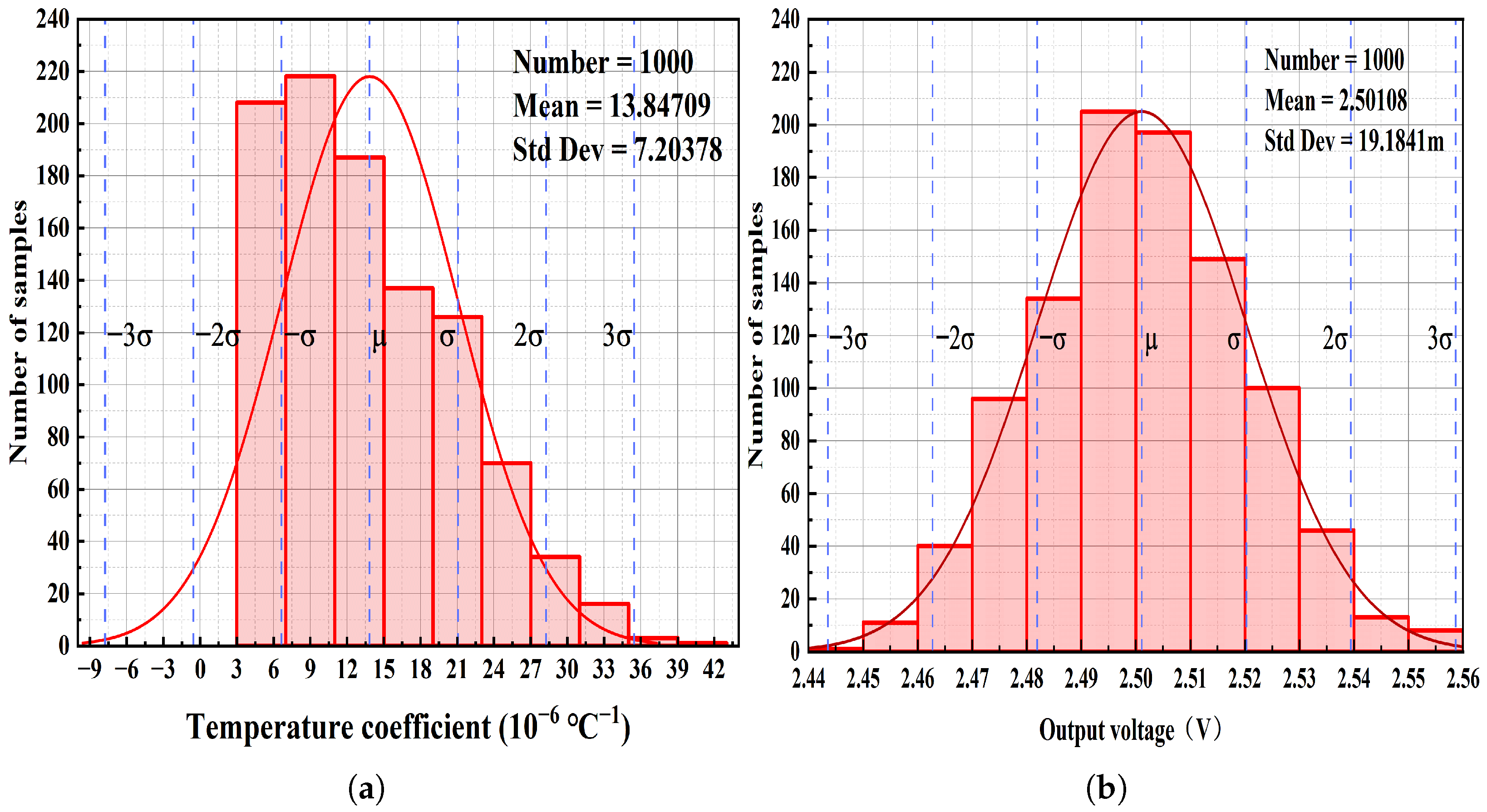

| TC (ppm/°C) | 2.372 | 2.4 | 32.7 | 23 | 5.78 |

| PSRR (dB) | −114.2@DC | −76@DC | −85@100 Hz | −30@1 kHz | −82@10 kHz |

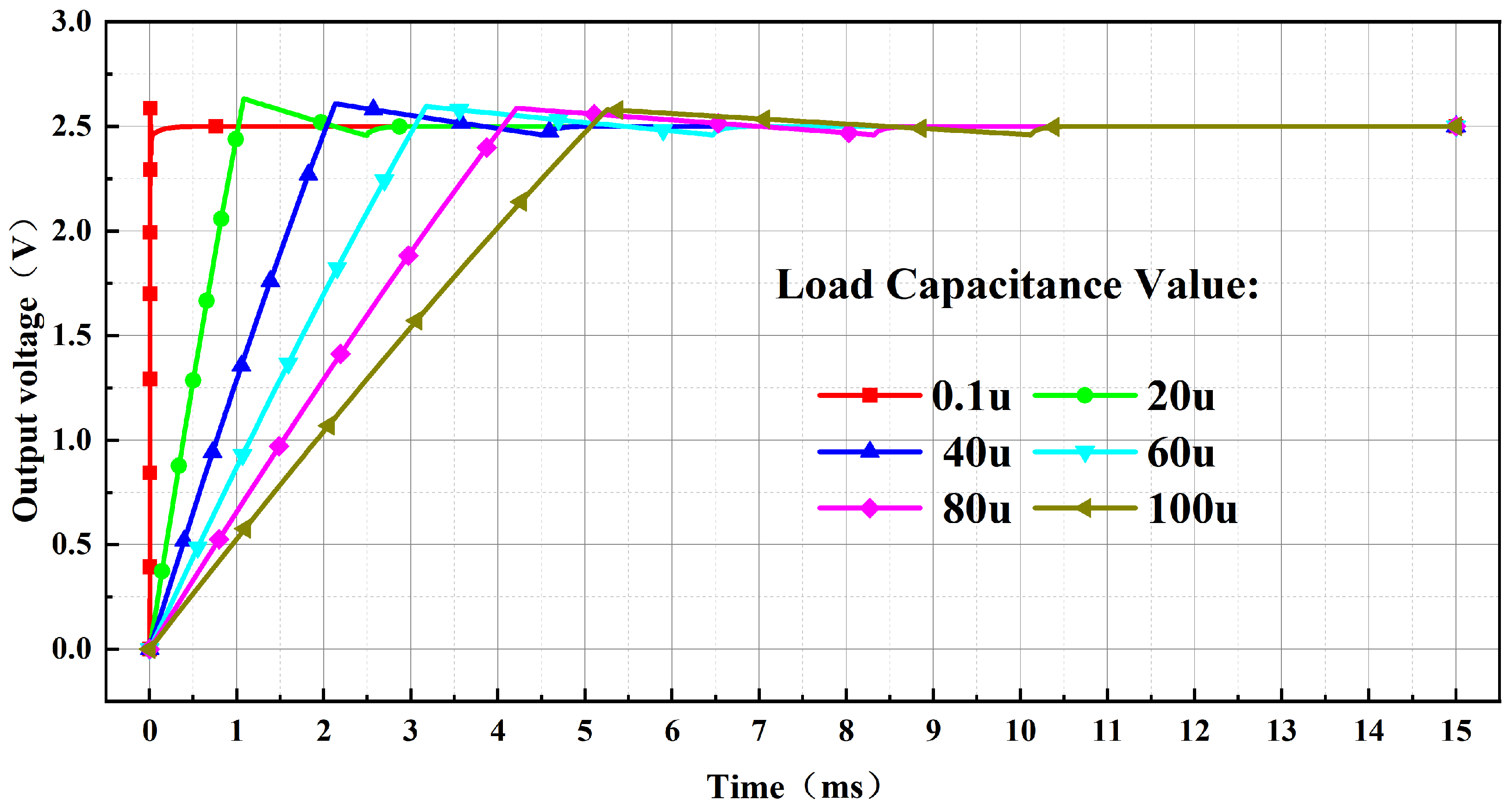

| Load Capacitance (μF) | 0.1~100 μF | 2.4 pF | – | – | – |

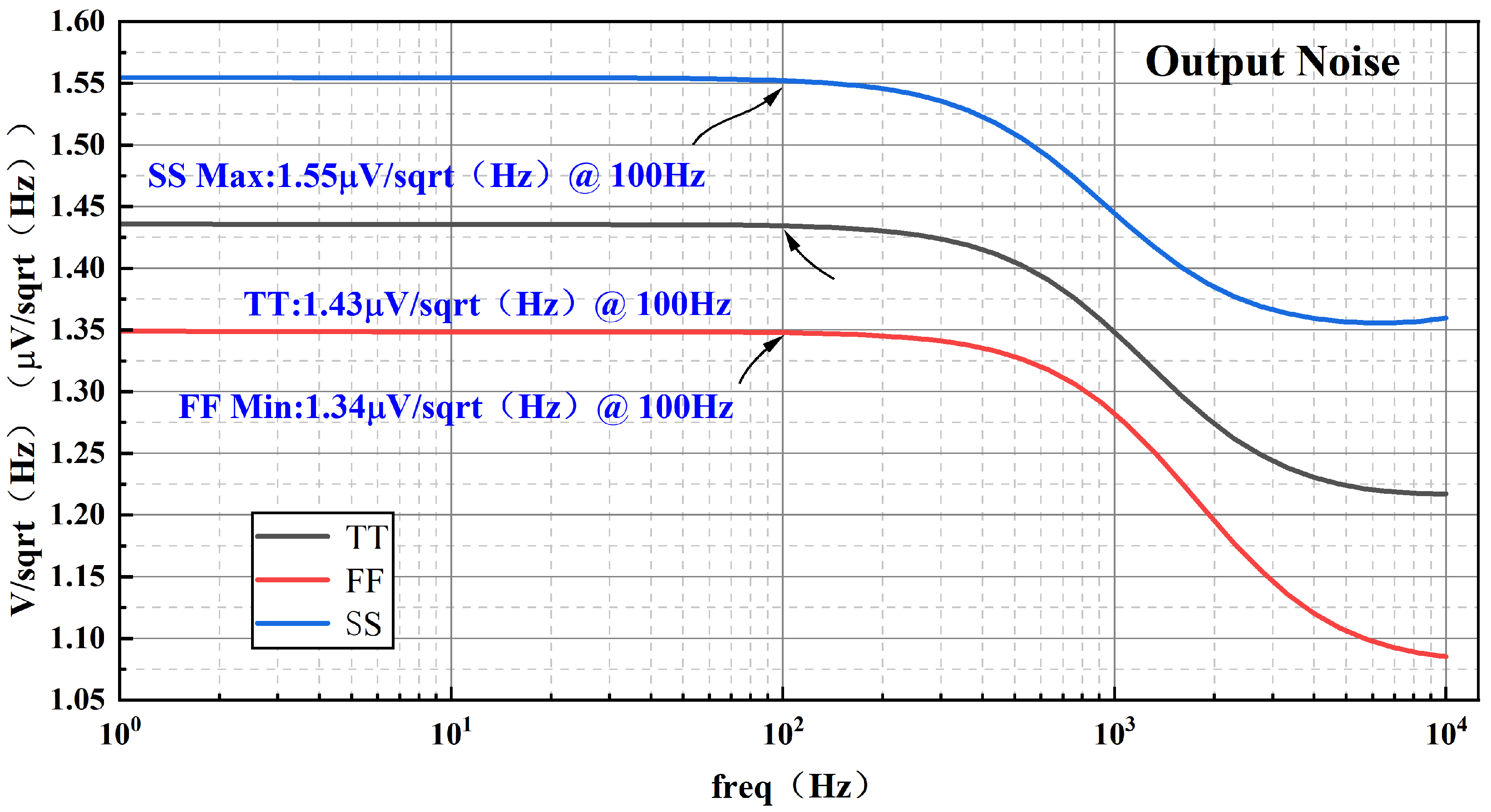

| Noise (μV/sqrt(Hz)) | 1.43 (1~100 Hz) | 3.0 (0.1~10 Hz) | – | 10@1 Hz | – |

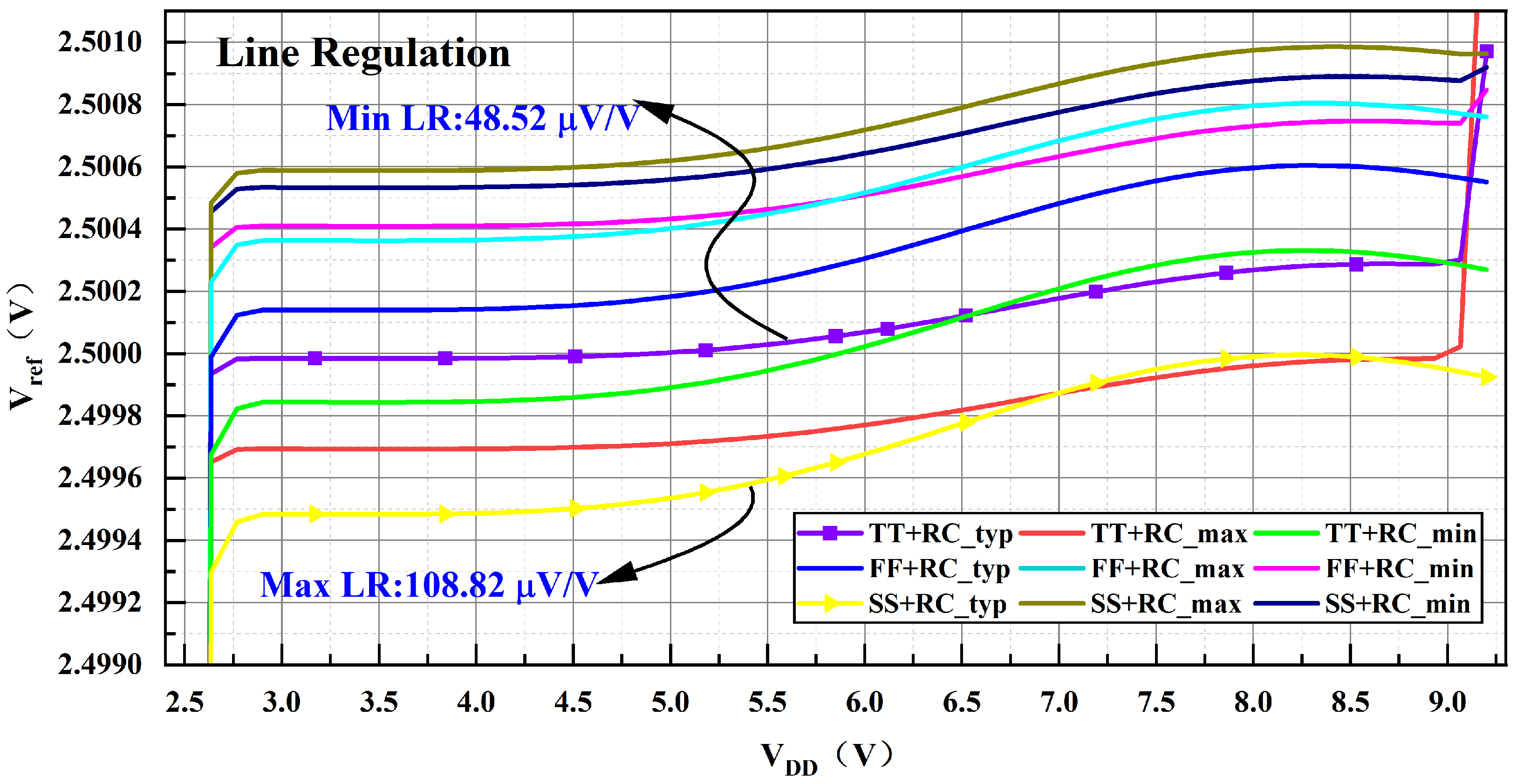

| Line Regulation (μV/V) | 48.52 | 30 | 580 | 500 | 300 |

| Chip Area (mm2) | 0.125 | 0.088 | 0.063 | 0.0121 | 0.08 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license.

Share and Cite

Li, M.; Guo, L.; Liu, B.; Qi, L.; He, B.; Cao, Y.; Ren, J. Design of a Bandgap Reference with a High PSRR and Strong Load-Driving Capability. Micromachines 2026, 17, 50. https://doi.org/10.3390/mi17010050

Li M, Guo L, Liu B, Qi L, He B, Cao Y, Ren J. Design of a Bandgap Reference with a High PSRR and Strong Load-Driving Capability. Micromachines. 2026; 17(1):50. https://doi.org/10.3390/mi17010050

Chicago/Turabian StyleLi, Meng, Lei Guo, Bin Liu, Lin Qi, Binghui He, Yu Cao, and Jian Ren. 2026. "Design of a Bandgap Reference with a High PSRR and Strong Load-Driving Capability" Micromachines 17, no. 1: 50. https://doi.org/10.3390/mi17010050

APA StyleLi, M., Guo, L., Liu, B., Qi, L., He, B., Cao, Y., & Ren, J. (2026). Design of a Bandgap Reference with a High PSRR and Strong Load-Driving Capability. Micromachines, 17(1), 50. https://doi.org/10.3390/mi17010050