Abstract

As the scaling of silicon-based CMOS technology approaches its physical limits, two-dimensional (2D) materials have emerged as promising alternatives for future electronic devices. Among them, MoS2 is a leading candidate due to its fascinating semiconducting nature and compatibility with CMOS processes. However, high contact resistance at the metal–MoS2 interface remains a major bottleneck, limiting device performance. In this study, we report the fabrication and characterization of graphene–MoS2 (Gr–MoS2) lateral heterostructure FETs, where monolayer graphene, synthesized by inductively coupled plasma chemical vapor deposition (ICP-CVD), is directly used as the source and drain. Bilayer MoS2 is selectively grown along graphene edges via edge-guided CVD, forming a chemically bonded in-plane junction without transfer steps. Electrical measurements reveal that the Gr–MoS2 FETs exhibit a threefold increase in average field-effect mobility (3.9 vs. 1.1 cm2 V−1 s−1) compared to conventional MoS2 FETs. Y-function analysis shows that the contact resistance is significantly reduced from 85.8 kΩ to 20.5 kΩ at VG = 40 V. These improvements are attributed to the replacement of the conventional metal–MoS2 contact with a graphene–metal contact. Our results demonstrate that lateral heterostructure engineering with graphene provides an effective and scalable strategy for high-performance 2D electronics.

1. Introduction

The continuous scale-down of semiconductor devices has approached fundamental physical and materials limits within traditional silicon-based complementary metal-oxide semiconductor (CMOS) platforms [1]. In response, two-dimensional (2D) materials have garnered significant interest as promising channel and contact materials owing to their atomically thin geometry and rich diversity in electronic properties [2,3,4]. Among them, semiconducting transition metal dichalcogenides (TMDs), particularly molybdenum disulfide (MoS2), have emerged as leading candidates due to their sizable bandgap, high on/off current ratio, and compatibility with CMOS processing [5,6,7,8]. However, one of the key bottlenecks in TMDs-based field-effect transistors (FETs) lies in the high contact resistance at the metal–semiconductor junction [9,10,11,12]. The absence of strong chemical bonding at the 2D material surface, combined with Fermi level pinning, often leads to the formation of significant Schottky barriers that inhibit efficient carrier injection [13,14]. Various approaches have been explored to mitigate this issue, including phase engineering [15,16], work function modulation [17,18], and the introduction of interfacial layers [19,20]. Despite these advances, scalable and reproducible contact engineering strategies remain limited. In this context, graphene has been proposed as a practical alternative to conventional metals for contacting 2D semiconductors [4,21,22,23]. Its work function tunability, high electrical conductivity, and atomically smooth surface make it an ideal interfacial material that can potentially form low-barrier van der Waals (vdW) contacts with semiconducting TMDs. In particular, laterally connected graphene–MoS2 (Gr–MoS2) heterostructures, fabricated via bottom-up chemical vapor deposition (CVD), offer a clean, scalable platform for seamless integration without the need for transfer or lithographic alignment steps [24,25,26]. Several studies have demonstrated that lateral Gr–MoS2 heterostructures offer superior electrical characteristics over conventional MoS2 FETs, largely attributed to the formation of low-resistance, atomically sharp Gr–MoS2 interfaces [27,28,29].

Building upon these results, the present study systematically investigates the role of graphene contacts in lateral heterostructure-based FETs by quantitatively analyzing their resistance components and comparing them against those of conventional MoS2 FETs. By utilizing identical growth and device fabrication conditions, we isolate the impact of contact geometry on device performance. We further explore the effect of channel length scaling and provide direct comparisons of contact and channel resistance components. To the best of our knowledge, a systematic and quantitative decomposition of resistance contributions in Gr–MoS2 heterostructure FETs under strictly identical fabrication conditions has not been reported. This direct side-by-side comparison with conventional MoS2 FETs enables us to clearly isolate the intrinsic effect of the Gr–MoS2 lateral interface on device performance. By employing the Y-function method to separately evaluate contact and channel resistances, our study provides new insight into the role of graphene contacts that goes beyond the general understanding that graphene reduces Schottky barriers. These results highlight the effectiveness of the Gr–MoS2 lateral interface in optimizing parasitic resistances and enhancing carrier transport, emphasizing its potential for future nanoscale electronics and contact-limited device platforms.

2. Experimental Section

2.1. Device Fabrication Process

Following the growth process, both the MoS2–graphene lateral heterostructure and reference MoS2 samples were coated with a negative photoresist to define the device structure. Source and drain regions were patterned using a photolithography process. For metallization, Pd (15 nm)/Au (35 nm) was deposited on the heterostructure devices, while Ti (15 nm)/Au (35 nm) was used for the MoS2-only devices, both via thermal evaporation under a high vacuum of approximately 10−6 Torr. Subsequent lithography was performed to define the channel region, and unneeded MoS2 outside the active area was removed using oxygen plasma etching (ICP-asher, Korea Vacuum Tech Co., LTD, Gimpo-si, Gyeonggi-do, Republic of Korea). The fabricated devices featured channel lengths and widths ranging from a few micrometers to several tens of micrometers.

2.2. Electrical Property Characterization

Before electrical measurements, all fabricated devices were annealed at 250–300 °C for 2 h under high vacuum (~10−6 Torr) to eliminate residual moisture on the channel surface. Electrical characterization was carried out using a semiconductor parameter analyzer (4200 SCS, Keithley Instruments, Cleveland, OH, USA) in conjunction with a probe station (MS-TECH). All measurements were performed under vacuum conditions (~50 mTorr) and in the dark to minimize the effects of ambient gas adsorption and photogenerated electrons.

3. Results and Discussion

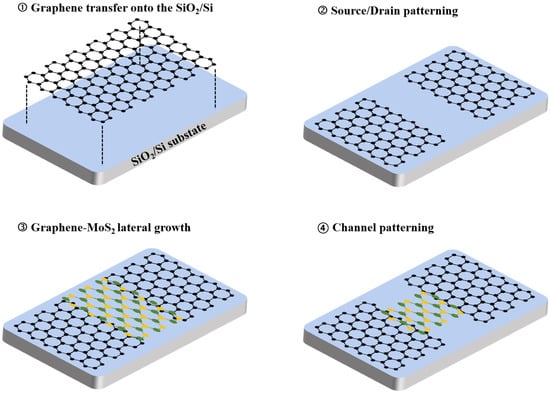

The overall fabrication process of the graphene–MoS2 (Gr–MoS2) lateral heterostructure is schematically illustrated in Figure 1. Monolayer graphene was first synthesized on a four-inch SiO2/Si wafer coated with a 300 nm-thick Cu film using inductively coupled plasma chemical vapor deposition (ICP-CVD). A gas mixture of C2H2 (1 sccm) and Ar (100 sccm) was introduced into the chamber under 50 W RF plasma at 980 °C to promote monolayer graphene growth [30,31]. After synthesis, the graphene was transferred onto a SiO2 (90 nm)/Si substrate via a metal-etching-free transfer method, which avoids contamination and prevents structural damage to the graphene layer during transfer [30]. Photolithography and oxygen plasma etching were then employed to define patterned graphene regions, selectively exposing windows for subsequent MoS2 growth. MoS2 was synthesized using atmospheric pressure chemical vapor deposition (APCVD) in a four-inch tube furnace equipped with two independently controlled heating zones. MoO3 (Sigma Aldrich, St. Louis, MO, USA, ≥99.5%) and sulfur (Sigma Aldrich, 99.98%) powders were placed in alumina crucibles at the downstream (700 °C) and upstream (320 °C) regions, respectively. The growth proceeded under a 100 sccm Ar flow for 30 min, and perylene-3,4,9,10-tetracarboxylic acid tetrapotassium (PTAS) was used as a seeding promoter to facilitate nucleation. To favor lateral rather than vertical heterostructure formation, the MoS2 growth temperature was carefully optimized to 700 °C, a regime known to suppress MoS2 nucleation on the graphene basal plane while promoting edge-selective lateral growth [32]. The graphene edges served as nucleation sites, enabling MoS2 to grow laterally from both sides of the patterned graphene. As growth progressed, the MoS2 domains coalesced between adjacent graphene regions, forming a continuous semiconductor channel laterally stitched to the graphene source and drain electrodes. Unlike conventional vertical stacking methods, this in-plane heterostructure offers a chemically bonded interface and facilitates scalable, transfer-free fabrication, making it suitable for large-area integration. For field-effect transistor (FET) fabrication, photolithography was used to define the channel region, and the MoS2 outside the channel region was removed by O2 plasma etching, ensuring that only the MoS2 within the channel area remained.

Figure 1.

Schematic illustration of the fabrication process for a graphene–MoS2 lateral heterostructure.

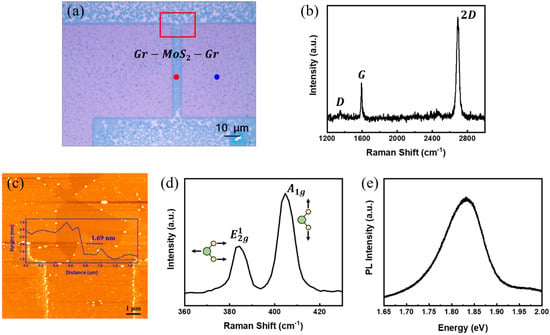

To verify the structural integrity and layer thickness of the synthesized MoS2 within the lateral heterostructure, we conducted a series of morphological and spectroscopic characterizations. Figure 2a shows an optical microscope (OM) image of a representative Gr–MoS2 lateral heterostructure where the MoS2 is contacted laterally by graphene edges. As shown in Figure 2b, the Raman spectrum of the graphene film, measured at the blue-marked point in Figure 2a, exhibits a prominent 2D peak with a 2D/G intensity ratio greater than 2 and a negligible D peak, confirming the monolayer thickness and high crystalline quality of the synthesized graphene [33]. The red box indicates the region selected for atomic force microscopy (AFM) analysis. The AFM image, shown in Figure 2c, confirms the formation of a uniform MoS2 film at the heterointerface, with the measured step height of approximately 1.69 nm. Although the theoretical thickness of monolayer MoS2 is ~0.62 nm, the AFM measurements typically yield ~0.8 nm per layer due to substrate effects and surface adsorbates [34,35,36], making the observed step height consistent with a bilayer film. To evaluate the structure and crystallographic properties of the MoS2 domain, Raman spectroscopy was performed at the red-marked point in Figure 2a. As shown in Figure 2d, the characteristic Raman peaks of MoS2, corresponding to the in-plane mode and the out-of-plane mode, appear at ~384.4 and ~404.7 cm−1, respectively. The positions of these peaks are consistent with the semiconducting 2H phase of MoS2 [37], further confirming the structural integrity of the synthesized layer. The peak separation (~20.3 cm−1) further confirms that the MoS2 is in the bilayer regime [34,38], in good agreement with AFM results. Photoluminescence (PL) spectroscopy was also conducted to assess the optical quality of the MoS2 layer. The spectrum in Figure 2e exhibits a pronounced A-exciton emission peak near 1.83 eV, showing a sharp and intense PL response that indicates high optical quality with minimal defect-related nonradiative recombination. Collectively, these structural and optical characterizations verify the successful formation of a bilayer MoS2 channel laterally stitched to graphene, forming a well-defined, clean, and electronically functional in-plane heterojunction suitable for FET fabrication.

Figure 2.

(a) Optical microscope (OM) image of the as-grown graphene–MoS2 lateral heterostructure. (b) Raman spectrum of graphene measured at the blue-marked point in (a). (c) Atomic force microscopy (AFM) image of the red-boxed region in (a), confirming the MoS2 thickness to be approximately 1.69 nm. (d) Raman spectrum and (e) photoluminescence (PL) of MoS2, both acquired at the red-marked point in (a).

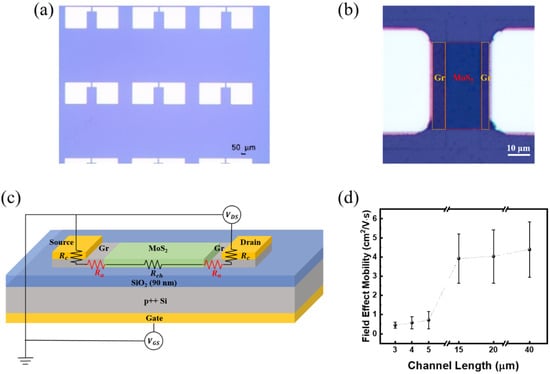

To evaluate the electrical properties of the Gr–MoS2 lateral heterostructure, we fabricated back-gated field-effect transistors (FETs). Figure 3a shows an OM image of the fabricated device array, where multiple devices with varying channel lengths and widths were prepared to facilitate statistical transport analysis. A representative single device is shown in Figure 3b, highlighting the laterally stitched MoS2 channel region (red dashed region) between two patterned graphene (Gr) source and drain (yellow dashed regions). The channel geometry was precisely defined by photolithography and O2 plasma etching, and Pd (15 nm)/Au (35 nm) contact metals were deposited on graphene to ensure low-resistance ohmic contact [39]. A schematic of the fabricated FET and its associated electrical resistance components is illustrated in Figure 3c. The total resistance between the source and drain electrodes consists of three major components: (i) the contact resistance () between metal and graphene; (ii) the access resistance () arising from the Gr–MoS2 transition region, which is less effectively modulated by the back-gate field; and (iii) the intrinsic channel resistance () of the MoS2 layer. This decomposition allows for a detailed assessment of how contact engineering and channel length scaling influence overall device behavior. To investigate the scaling effects, we extracted the field-effect mobility () as a function of channel length, as shown in Figure 3d. The mobility was calculated using the transconductance in the linear regime of the transfer curve. exhibits a clear decreasing trend with decreasing channel length. Since the graphene regions corresponding to the access resistance () are fixed at 5 µm in length, their relative contribution becomes more significant as the MoS2 channel length decreases. This result highlights the importance of carefully engineering the contact and transition regions, especially for scaled devices, where parasitic resistances can severely degrade performance. To minimize the influence of access resistance and ensure accurate extraction of intrinsic transport properties, our analysis was limited to devices with MoS2 channel lengths greater than 15 µm.

Figure 3.

(a) Optical microscope (OM) image of the fabricated device array based on graphene–MoS2 lateral heterostructures. (b) Enlarged OM image of a representative device, showing the MoS2 channel region contacted by graphene. (c) Schematic illustration of the device structure and resistance components, including the contact resistance (), access resistance (), and channel resistance (). (d) Field-effect mobility as a function of MoS2 channel length, showing a decreasing trend with shorter channels due to the increasing influence of access resistance.

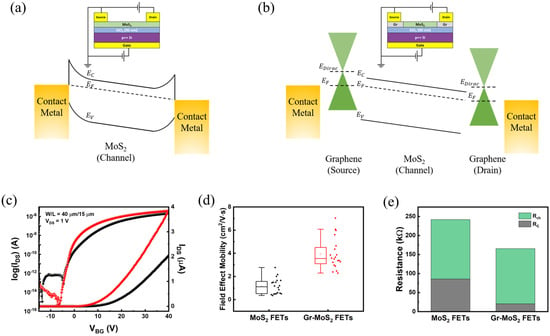

To assess the impact of contact engineering using graphene, we fabricated and compared conventional MoS2 FETs and Gr–MoS2 lateral heterostructure FETs. Figure 4a,b schematically illustrate the device architectures and corresponding band alignments under positive gate and drain bias. In conventional MoS2 FETs, metal–semiconductor interfaces typically suffer from Fermi-level pinning [11,40] and large Schottky barriers [41,42], which hinder efficient carrier injection. In contrast, the Gr–MoS2 FET structure replaces the conventional metal–MoS2 contact with a metal–graphene interface, in which graphene serves as an atomically thin, highly conductive bridge between the metal electrode and the MoS2 channel. This configuration enables a smoother and more uniform electron injection pathway. As a result, carrier injection is significantly improved, contributing to enhanced device performance. Figure 4c shows representative transfer characteristics of both device types. Gr–MoS2 FETs (red) exhibit significantly enhanced on-state current and improved subthreshold swing (SS) compared to conventional MoS2 FETs (black), reflecting more efficient carrier injection and better gate control. In addition, both device types maintain high on/off current ratios exceeding 106, indicating that the introduction of graphene contacts does not degrade the switching characteristics. To quantitatively compare carrier transport, the field-effect mobility values for both FET types were extracted using maximal gm and statistically analyzed. As shown in Figure 4d, Gr–MoS2 FETs exhibit a significantly higher average field-effect mobility of 3.9 cm2 V−1s−1, compared to 1.1 cm2 V−1s−1 for conventional MoS2 FETs. The performance enhancement is primarily attributed to the use of graphene as the source and drain, which effectively replaces the conventional metal–MoS2 contacts and leads to a significant reduction in contact resistance, thereby enabling more efficient charge injection into the MoS2 channel. Figure 4e presents a comparative analysis of the resistance components for both devices. All values were extracted using the Y-function method [43], which relates the drain current () and transconductance () as follows:

where is the intrinsic mobility excluding contact resistance, and is the gate dielectric (SiO2) capacitance per unit area. In addition, W and L denote the channel width and length, respectively, while , , and correspond to the drain-to-source voltage, gate-to-source voltage, and the threshold voltage. The extracted resistance components at VG = 40 V clearly show that the contact resistance () in Gr–MoS2 FETs is significantly lower than that in conventional MoS2 FETs. Specifically, the average value for Gr–MoS2 FETs is 20.5 kΩ, compared to 85.8 kΩ for MoS2 FETs with metal contacts. In contrast, the channel resistance () remains relatively comparable between the two device types. This pronounced reduction in contact resistance for the Gr-MoS2 FETs confirms that the enhancement in mobility and overall device performance is primarily attributed to the improved contact properties enabled by the use of graphene as source and drain. This comparative analysis underscores the critical role of contact engineering in 2D material-based devices and demonstrates that replacing conventional metal contacts with graphene is an effective strategy for enhancing transport performance.

Figure 4.

Schematic illustration of (a) a conventional MoS2 FET structure and (b) Gr–MoS2 FET, along with their corresponding energy band diagrams under positive gate and drain bias. (c) Transfer characteristics of MoS2 FETs (black) and Gr–MoS2 FETs (red). (d) Extracted field-effect mobility values for both FET types. (e) Comparison of the contact and channel resistance components in MoS2 and Gr–MoS2 FETs.

4. Conclusions

In this work, we successfully fabricated and characterized Gr–MoS2 lateral heterostructure FETs, in which monolayer graphene functions directly as the source and drain. The heterostructure was synthesized via an edge-selective CVD process that enables lateral stitching of bilayer MoS2 onto patterned graphene, forming a chemically bonded and well-defined interface. Electrical measurements revealed that the Gr–MoS2 FETs exhibit superior performance compared to conventional MoS2 FETs. The average field-effect mobility increased from 1.1 to 3.9 cm2 V−1s−1, while the contact resistance decreased markedly from 85.8 kΩ to 20.5 kΩ at VG = 40 V. This study highlights the effectiveness of graphene as a contact material for 2D semiconductors and demonstrates that lateral heterostructure engineering offers a scalable and CMOS-compatible route to reduce contact resistance and enhance carrier injection. The Gr–MoS2 platform presented here holds strong potential for future high-performance, large-area 2D electronic applications.

Funding

The present research was supported by the research fund of Dankook University in 2023.

Data Availability Statement

The original contributions presented in this study are included in the article. Further inquiries can be directed to the corresponding author.

Conflicts of Interest

The author declares no conflicts of interest.

References

- Waldrop, M.M. The chips are down for Moore’s law. Nat. News 2016, 530, 144. [Google Scholar] [CrossRef] [PubMed]

- Radisavljevic, B.; Radenovic, A.; Brivio, J.; Giacometti, V.; Kis, A. Single-layer MoS2 transistors. Nat. Nanotechnol. 2011, 6, 147–150. [Google Scholar] [CrossRef]

- Desai, S.B.; Madhvapathy, S.R.; Sachid, A.B.; Llinas, J.P.; Wang, Q.; Ahn, G.H.; Pitner, G.; Kim, M.J.; Bokor, J.; Hu, C. MoS2 transistors with 1-nanometer gate lengths. Science 2016, 354, 99–102. [Google Scholar] [CrossRef]

- Xie, L.; Liao, M.; Wang, S.; Yu, H.; Du, L.; Tang, J.; Zhao, J.; Zhang, J.; Chen, P.; Lu, X. Graphene-contacted ultrashort channel monolayer MoS2 transistors. Adv. Mater. 2017, 29, 1702522. [Google Scholar] [CrossRef]

- Ryou, J.; Kim, Y.-S.; Kc, S.; Cho, K. Monolayer MoS2 bandgap modulation by dielectric environments and tunable bandgap transistors. Sci. Rep. 2016, 6, 29184. [Google Scholar] [CrossRef]

- Pradhan, N.R.; Rhodes, D.; Zhang, Q.; Talapatra, S.; Terrones, M.; Ajayan, P.; Balicas, L. Intrinsic carrier mobility of multi-layered MoS2 field-effect transistors on SiO2. Appl. Phys. Lett. 2013, 102, 123105. [Google Scholar] [CrossRef]

- Zhang, Y.; Zhao, H.L.; Huang, S.; Hossain, M.A.; van der Zande, A.M. Enhancing carrier mobility in monolayer MoS2 transistors with process-induced strain. ACS Nano 2024, 18, 12377–12385. [Google Scholar]

- Kang, M.; Hong, W.; Lee, I.; Park, S.; Park, C.; Bae, S.; Lim, H.; Choi, S.-Y. Tunable doping strategy for few-layer MoS2 field-effect transistors via NH3 plasma treatment. ACS Appl. Mater. Interfaces 2024, 16, 43849–43859. [Google Scholar] [CrossRef]

- Shen, P.-C.; Su, C.; Lin, Y.; Chou, A.-S.; Cheng, C.-C.; Park, J.-H.; Chiu, M.-H.; Lu, A.-Y.; Tang, H.-L.; Tavakoli, M.M. Ultralow contact resistance between semimetal and monolayer semiconductors. Nature 2021, 593, 211–217. [Google Scholar] [CrossRef] [PubMed]

- Sun, Z.; Kim, S.Y.; Cai, J.; Shen, J.; Lan, H.-Y.; Tan, Y.; Wang, X.; Shen, C.; Wang, H.; Chen, Z. Low contact resistance on monolayer MoS2 field-effect transistors achieved by CMOS-compatible metal contacts. ACS Nano 2024, 18, 22444–22453. [Google Scholar] [CrossRef] [PubMed]

- Ngo, T.D.; Huynh, T.; Jung, H.; Ali, F.; Jeon, J.; Choi, M.S.; Yoo, W.J. Modulation of Contact Resistance of Dual-Gated MoS2 FETs Using Fermi-Level Pinning-Free Antimony Semi-Metal Contacts. Adv. Sci. 2023, 10, 2301400. [Google Scholar] [CrossRef]

- Li, H.; Cheng, M.; Wang, P.; Du, R.; Song, L.; He, J.; Shi, J. Reducing contact resistance and boosting device performance of monolayer MoS2 by in situ Fe doping. Adv. Mater. 2022, 34, 2200885. [Google Scholar] [CrossRef]

- Liu, X.; Choi, M.S.; Hwang, E.; Yoo, W.J.; Sun, J. Fermi level pinning dependent 2D semiconductor devices: Challenges and prospects. Adv. Mater. 2022, 34, 2108425. [Google Scholar] [CrossRef] [PubMed]

- Xie, J.; Patoary, N.M.; Zhou, G.; Sayyad, M.Y.; Tongay, S.; Esqueda, I.S. Analysis of Schottky barrier heights and reduced Fermi-level pinning in monolayer CVD-grown MoS2 field-effect-transistors. Nanotechnol 2022, 33, 225702. [Google Scholar] [CrossRef] [PubMed]

- Zhang, W.; Wang, Q.; Hu, L.; Wu, J.; Shi, X. Electrical contacts to few-layer MoS2 with phase-engineering and metal intercalation for tuning the contact performance. J. Chem. Phys. 2021, 154, 184705. [Google Scholar] [CrossRef]

- Kappera, R.; Voiry, D.; Yalcin, S.E.; Branch, B.; Gupta, G.; Mohite, A.D.; Chhowalla, M. Phase-engineered low-resistance contacts for ultrathin MoS2 transistors. Nat. Mater. 2014, 13, 1128–1134. [Google Scholar] [CrossRef] [PubMed]

- Lee, S.Y.; Kim, U.J.; Chung, J.; Nam, H.; Jeong, H.Y.; Han, G.H.; Kim, H.; Oh, H.M.; Lee, H.; Kim, H. Large work function modulation of monolayer MoS2 by ambient gases. ACS Nano 2016, 10, 6100–6107. [Google Scholar] [CrossRef]

- Baik, S.S.; Im, S.; Choi, H.J. Work function tuning in two-dimensional MoS2 field-effect-transistors with graphene and titanium source-drain contacts. Sci. Rep. 2017, 7, 45546. [Google Scholar] [CrossRef]

- Park, W.; Min, J.W.; Shaikh, S.F.; Hussain, M.M. Stable MoS2 Field-Effect Transistors Using TiO2 Interfacial Layer at Metal/MoS2 Contact. Phys. Status Solidi (A) 2017, 214, 1700534. [Google Scholar] [CrossRef]

- Wang, J.; Yao, Q.; Huang, C.W.; Zou, X.; Liao, L.; Chen, S.; Fan, Z.; Zhang, K.; Wu, W.; Xiao, X. High Mobility MoS2 transistor with low Schottky barrier contact by using atomic thick h-BN as a tunneling layer. Adv. Mater. 2016, 28, 8302–8308. [Google Scholar] [CrossRef]

- Lee, Y.T.; Choi, K.; Lee, H.S.; Min, S.W.; Jeon, P.J.; Hwang, D.K.; Choi, H.J.; Im, S. Graphene Versus Ohmic Metal as Source-Drain Electrode for MoS2 Nanosheet Transistor Channel. Small 2014, 10, 2356–2361. [Google Scholar] [CrossRef] [PubMed]

- Tang, Z.; Liu, C.; Huang, X.; Zeng, S.; Liu, L.; Li, J.; Jiang, Y.-G.; Zhang, D.W.; Zhou, P. A steep-slope MoS2/graphene Dirac-source field-effect transistor with a large drive current. Nano Lett. 2021, 21, 1758–1764. [Google Scholar] [CrossRef]

- Zou, Y.; Li, P.; Su, C.; Yan, J.; Zhao, H.; Zhang, Z.; You, Z. Flexible high-temperature MoS2 field-effect transistors and logic gates. ACS Nano 2024, 18, 9627–9635. [Google Scholar] [CrossRef]

- Subramanian, S.; Xu, K.; Wang, Y.; Moser, S.; Simonson, N.A.; Deng, D.; Crespi, V.H.; Fullerton-Shirey, S.K.; Robinson, J.A. Tuning transport across MoS2/graphene interfaces via as-grown lateral heterostructures. npj 2D Mater. Appl. 2020, 4, 9. [Google Scholar] [CrossRef]

- Behranginia, A.; Yasaei, P.; Majee, A.K.; Sangwan, V.K.; Long, F.; Foss, C.J.; Foroozan, T.; Fuladi, S.; Hantehzadeh, M.R.; Shahbazian-Yassar, R. Direct growth of high mobility and low-noise lateral MoS2–Graphene heterostructure electronics. Small 2017, 13, 1604301. [Google Scholar] [CrossRef] [PubMed]

- Deng, W.; Chen, Y.; You, C.; Liu, B.; Yang, Y.; Shen, G.; Li, S.; Sun, L.; Zhang, Y.; Yan, H. High detectivity from a lateral graphene–MoS2 Schottky photodetector grown by chemical vapor deposition. Adv. Electron. Mater. 2018, 4, 1800069. [Google Scholar] [CrossRef]

- Schneider, D.S.; Lucchesi, L.; Reato, E.; Wang, Z.; Piacentini, A.; Bolten, J.; Marian, D.; Marin, E.G.; Radenovic, A.; Wang, Z. CVD graphene contacts for lateral heterostructure MoS2 field effect transistors. npj 2D Mater. Appl. 2024, 8, 35. [Google Scholar] [CrossRef]

- Houssa, M.; Iordanidou, K.; Dabral, A.; Lu, A.; Meng, R.; Pourtois, G.; Afanas’ev, V.; Stesmans, A. Contact resistance at graphene/MoS2 lateral heterostructures. Appl. Phys. Lett. 2019, 114, 163101. [Google Scholar] [CrossRef]

- Houssa, M.; Meng, R.; Afanas’ev, V.; Stesmans, A. First-principles study of the contact resistance at 2D metal/2D semiconductor heterojunctions. Appl. Sci. 2020, 10, 2731. [Google Scholar] [CrossRef]

- Yang, S.Y.; Oh, J.G.; Jung, D.Y.; Choi, H.; Yu, C.H.; Shin, J.; Choi, C.G.; Cho, B.J.; Choi, S.Y. Metal-etching-free direct delamination and transfer of single-layer graphene with a high degree of freedom. Small 2015, 11, 175–181. [Google Scholar] [CrossRef] [PubMed]

- Song, S.M.; Park, J.K.; Sul, O.J.; Cho, B.J. Determination of work function of graphene under a metal electrode and its role in contact resistance. Nano Lett. 2012, 12, 3887–3892. [Google Scholar] [CrossRef]

- Gong, Y.; Lin, J.; Wang, X.; Shi, G.; Lei, S.; Lin, Z.; Zou, X.; Ye, G.; Vajtai, R.; Yakobson, B.I. Vertical and in-plane heterostructures from WS2/MoS2 monolayers. Nat. Mater. 2014, 13, 1135–1142. [Google Scholar] [CrossRef]

- Ferrari, A.C.; Meyer, J.C.; Scardaci, V.; Casiraghi, C.; Lazzeri, M.; Mauri, F.; Piscanec, S.; Jiang, D.; Novoselov, K.S.; Roth, S. Raman spectrum of graphene and graphene layers. Phys. Rev. Lett. 2006, 97, 187401. [Google Scholar] [CrossRef]

- Majee, B.P.; Jangra, P.; Mishra, A.K. CVD grown bi-layer MoS2 as SERS substrate: Nanomolar detection of R6G and temperature response. Mater. Lett. X 2024, 22, 100229. [Google Scholar]

- Yin, Z.; Li, H.; Li, H.; Jiang, L.; Shi, Y.; Sun, Y.; Lu, G.; Zhang, Q.; Chen, X.; Zhang, H. Single-layer MoS2 phototransistors. ACS Nano 2012, 6, 74–80. [Google Scholar] [CrossRef]

- Senthilkumar, V.; Tam, L.C.; Kim, Y.S.; Sim, Y.; Seong, M.-J.; Jang, J.I. Direct vapor phase growth process and robust photoluminescence properties of large area MoS2 layers. Nano Res. 2014, 7, 1759–1768. [Google Scholar] [CrossRef]

- Yin, Y.; Miao, P.; Zhang, Y.; Han, J.; Zhang, X.; Gong, Y.; Gu, L.; Xu, C.; Yao, T.; Xu, P. Significantly increased Raman enhancement on MoX2 (X = S, Se) monolayers upon phase transition. Adv. Funct. Mater. 2017, 27, 1606694. [Google Scholar] [CrossRef]

- Hong, W.; Park, C.; Shim, G.W.; Yang, S.Y.; Choi, S.-Y. Wafer-scale uniform growth of an atomically thin MoS2 film with controlled layer numbers by metal—organic chemical vapor deposition. ACS Appl. Mater. Interfaces 2021, 13, 50497–50504. [Google Scholar] [CrossRef] [PubMed]

- Zhong, H.; Zhang, Z.; Chen, B.; Xu, H.; Yu, D.; Huang, L.; Peng, L. Realization of low contact resistance close to theoretical limit in graphene transistors. Nano Res. 2015, 8, 1669–1679. [Google Scholar] [CrossRef]

- Hong, W.; Park, C.; Shim, G.W.; Yang, S.Y.; Choi, S.Y. Enhanced Electrical Properties of Metal-Organic Chemical Vapor Deposition-Grown MoS2 Thin Films through Oxygen-Assisted Defect Control. Adv. Electron. Mater. 2022, 8, 2101325. [Google Scholar] [CrossRef]

- Choi, D.; Jeon, J.; Park, T.-E.; Ju, B.-K.; Lee, K.-Y. Schottky barrier height engineering on MoS2 field-effect transistors using a polymer surface modifier on a contact electrode. Discov. Nano 2023, 18, 80. [Google Scholar] [CrossRef] [PubMed]

- Vaknin, Y.; Dagan, R.; Rosenwaks, Y. Schottky barrier height and image force lowering in monolayer MoS2 field effect transistors. Nanomaterials 2020, 10, 2346. [Google Scholar] [CrossRef] [PubMed]

- Chang, H.Y.; Zhu, W.; Akinwande, D. On the mobility and contact resistance evaluation for transistors based on MoS2 or two-dimensional semiconducting atomic crystals. Appl. Phys. Lett. 2014, 104, 113504. [Google Scholar] [CrossRef]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the author. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).