A Limited Common-Mode Current Switched-Capacitor Multilevel Inverter Topology and Its Performance and Lifetime Evaluation in Grid-Connected Photovoltaic Applications

Abstract

1. Introduction

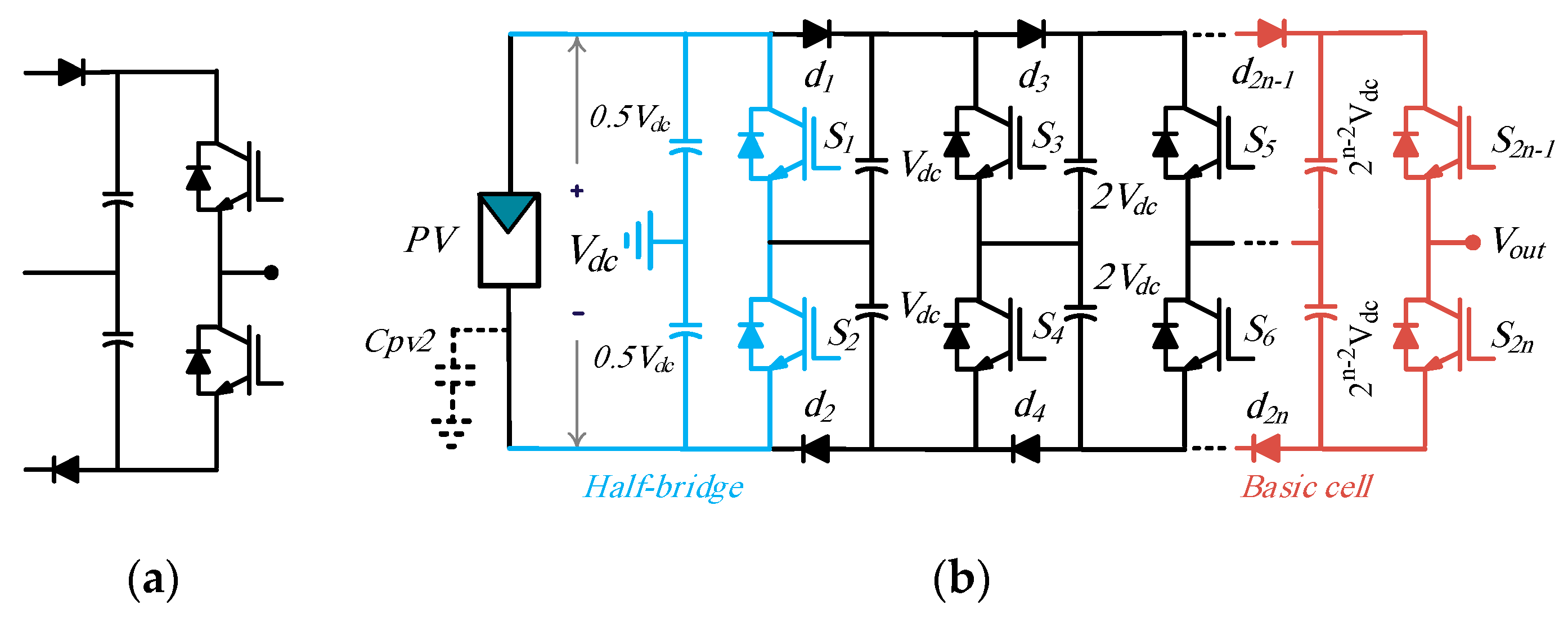

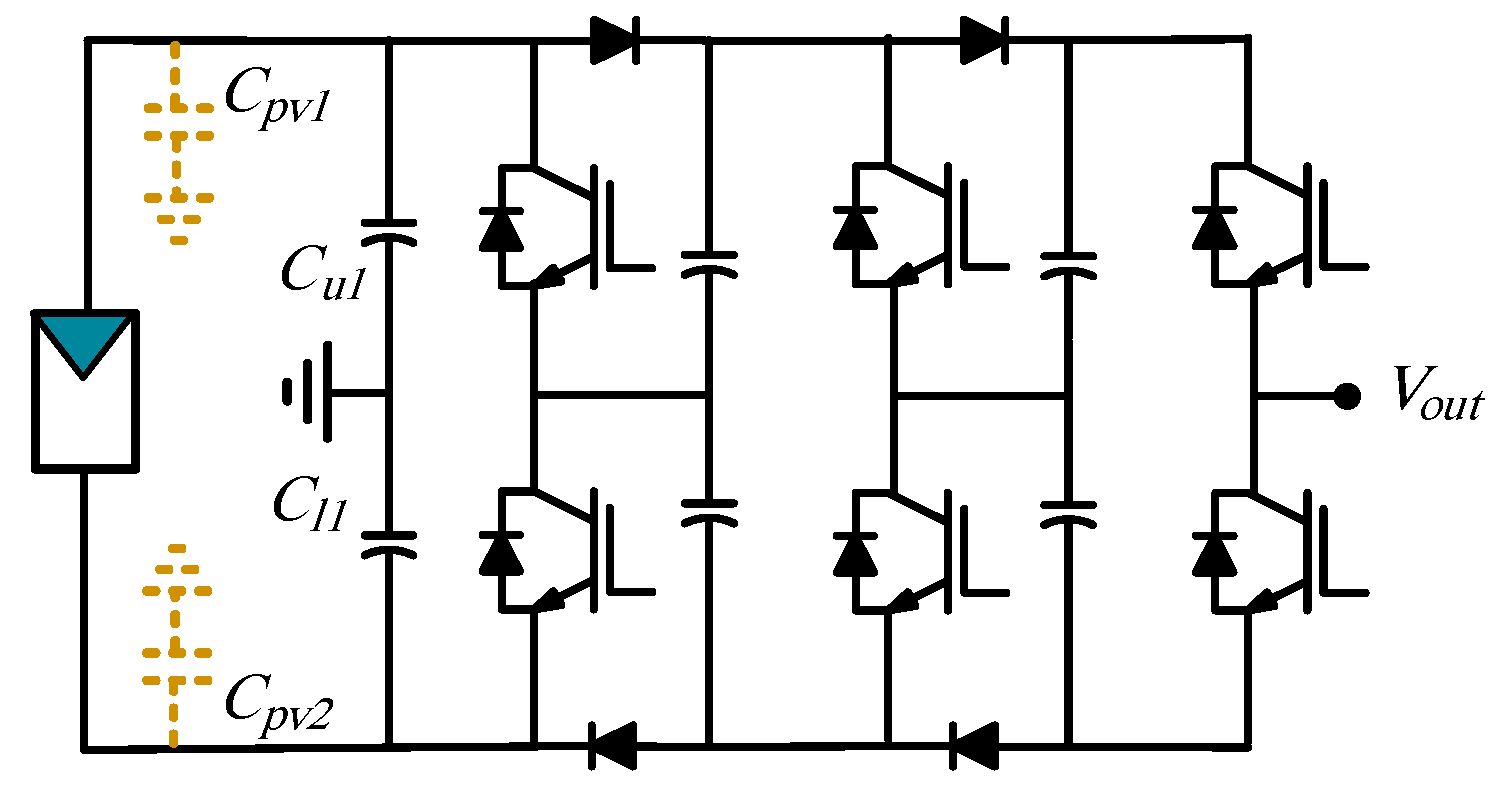

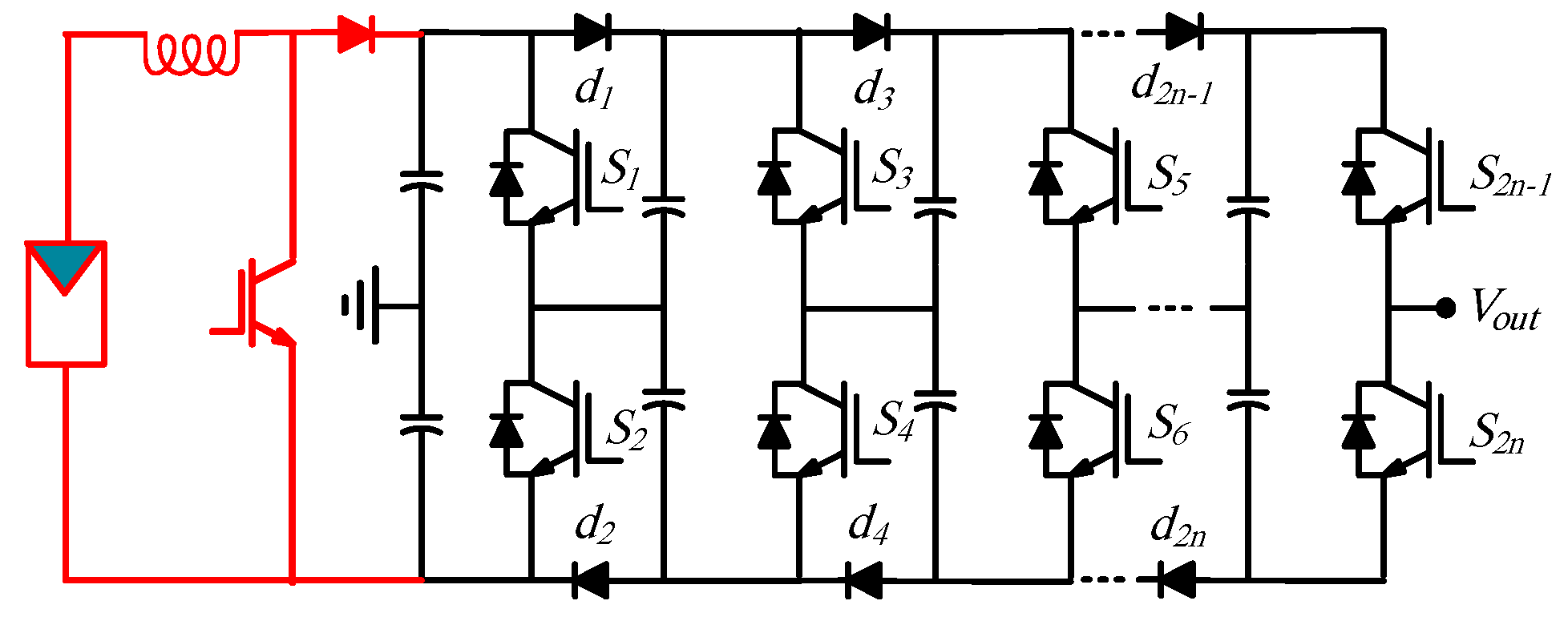

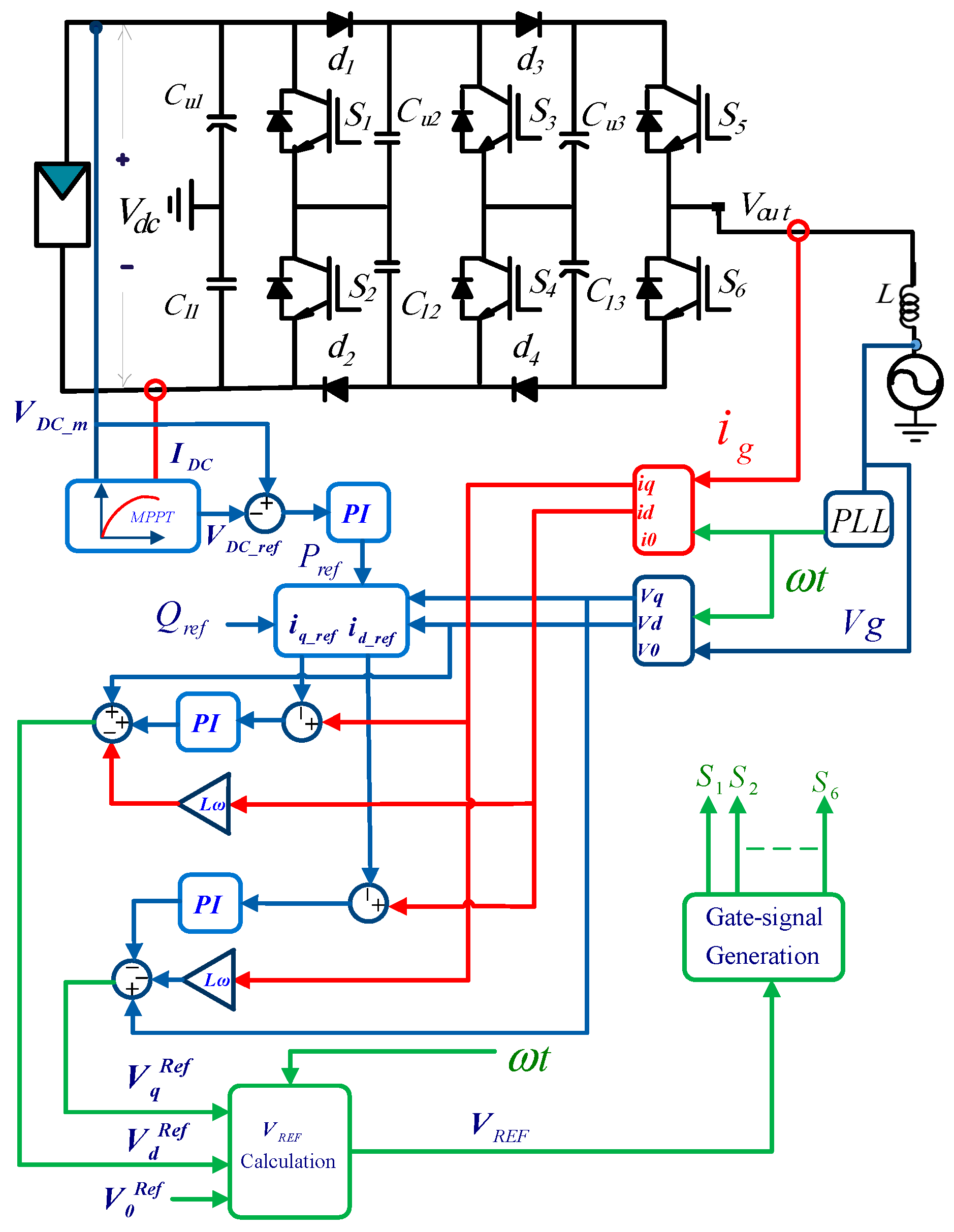

2. Structure and Operational Principle

2.1. Proposed Topology with N Stages

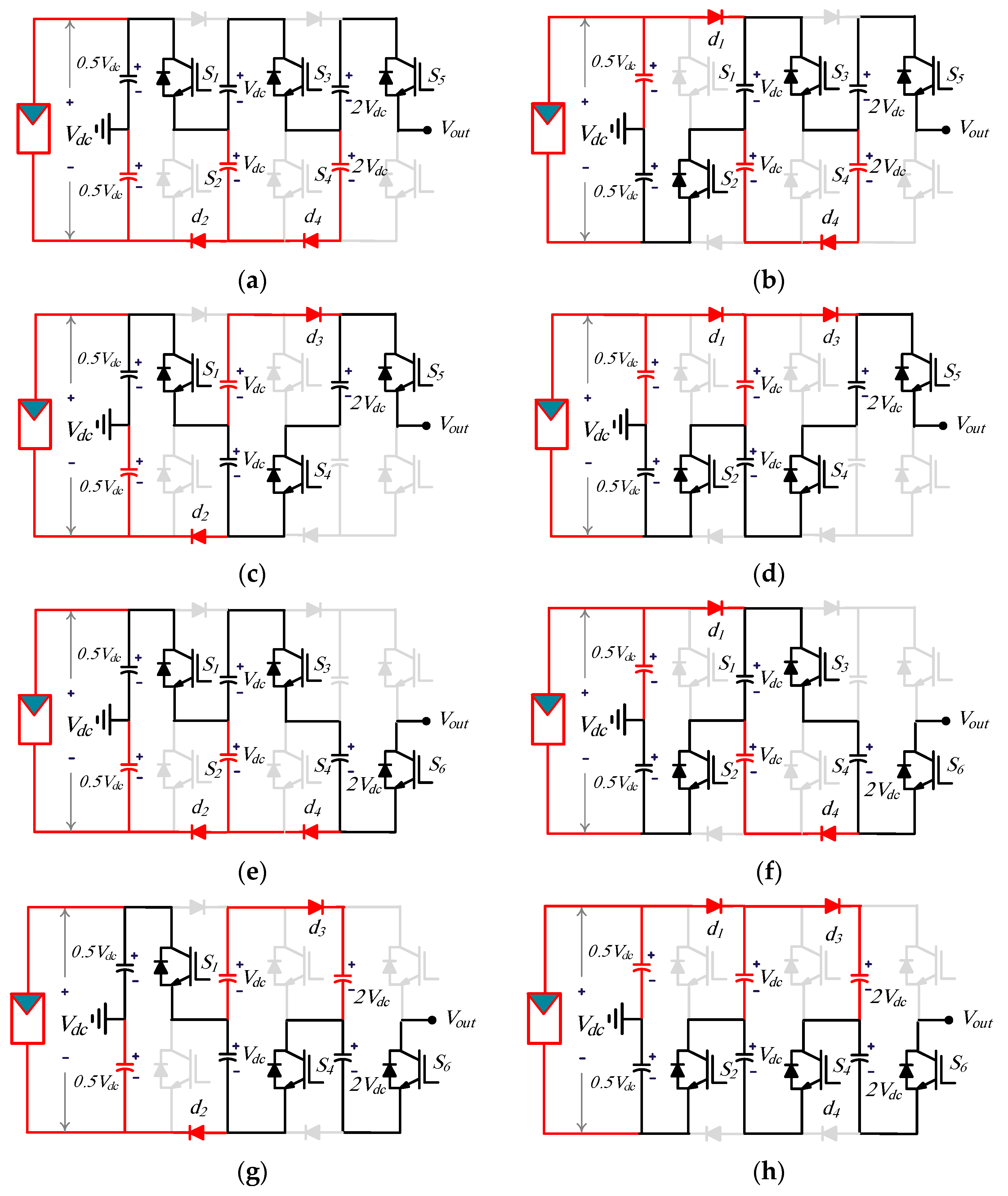

2.2. Operational Principle

3. Voltage Boosting and Leakage Current Suppression Features

4. Power Loss Calculation

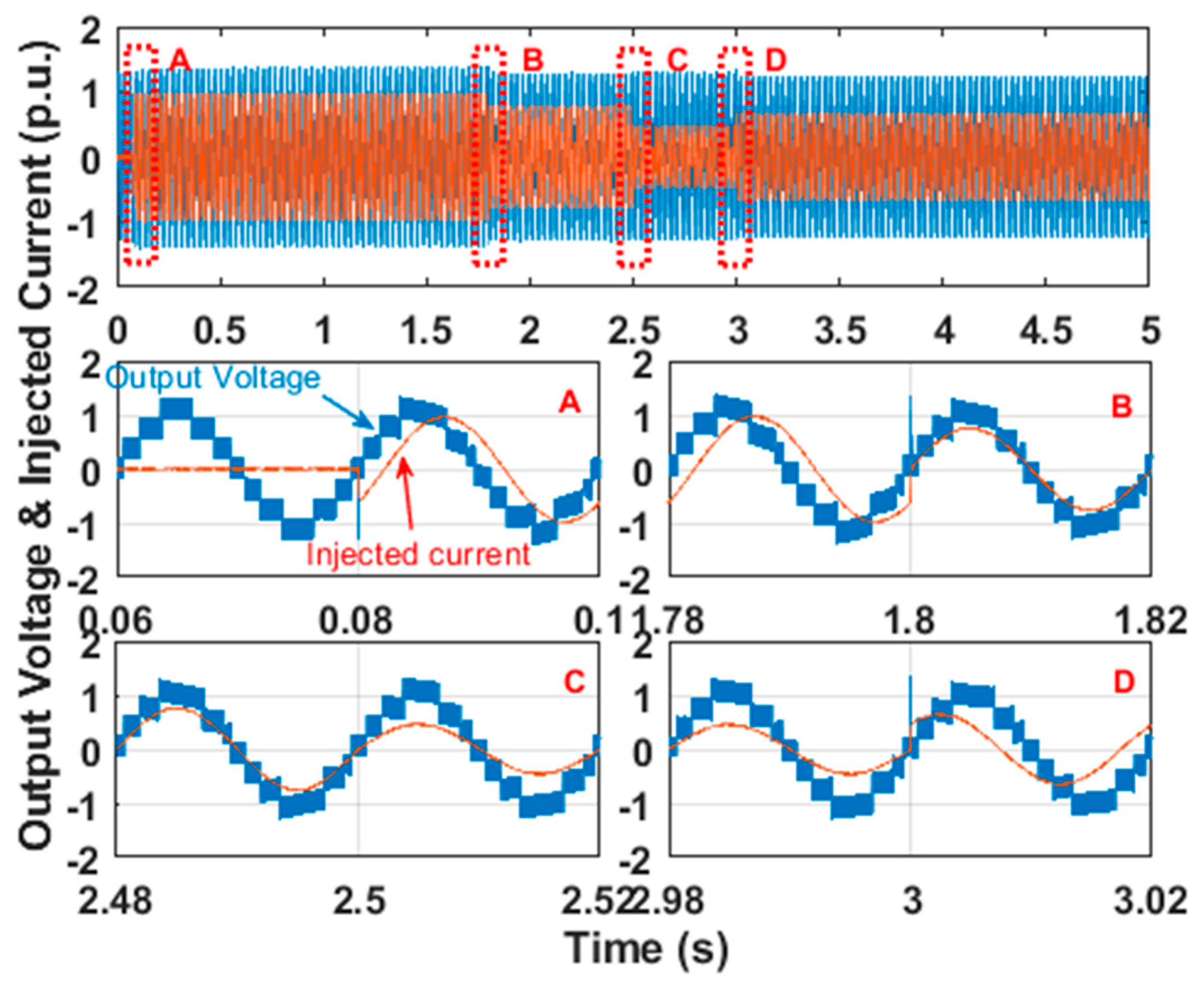

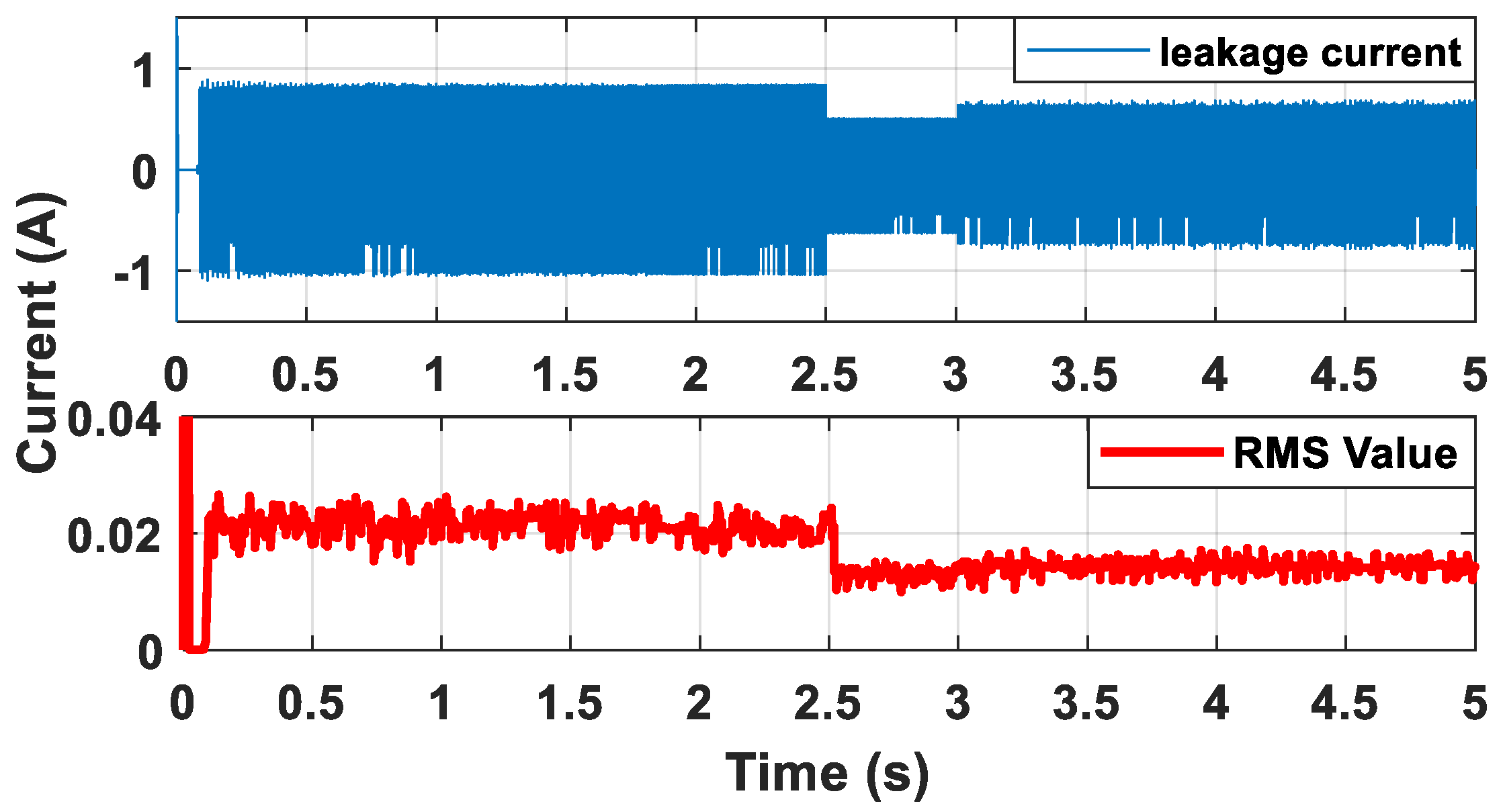

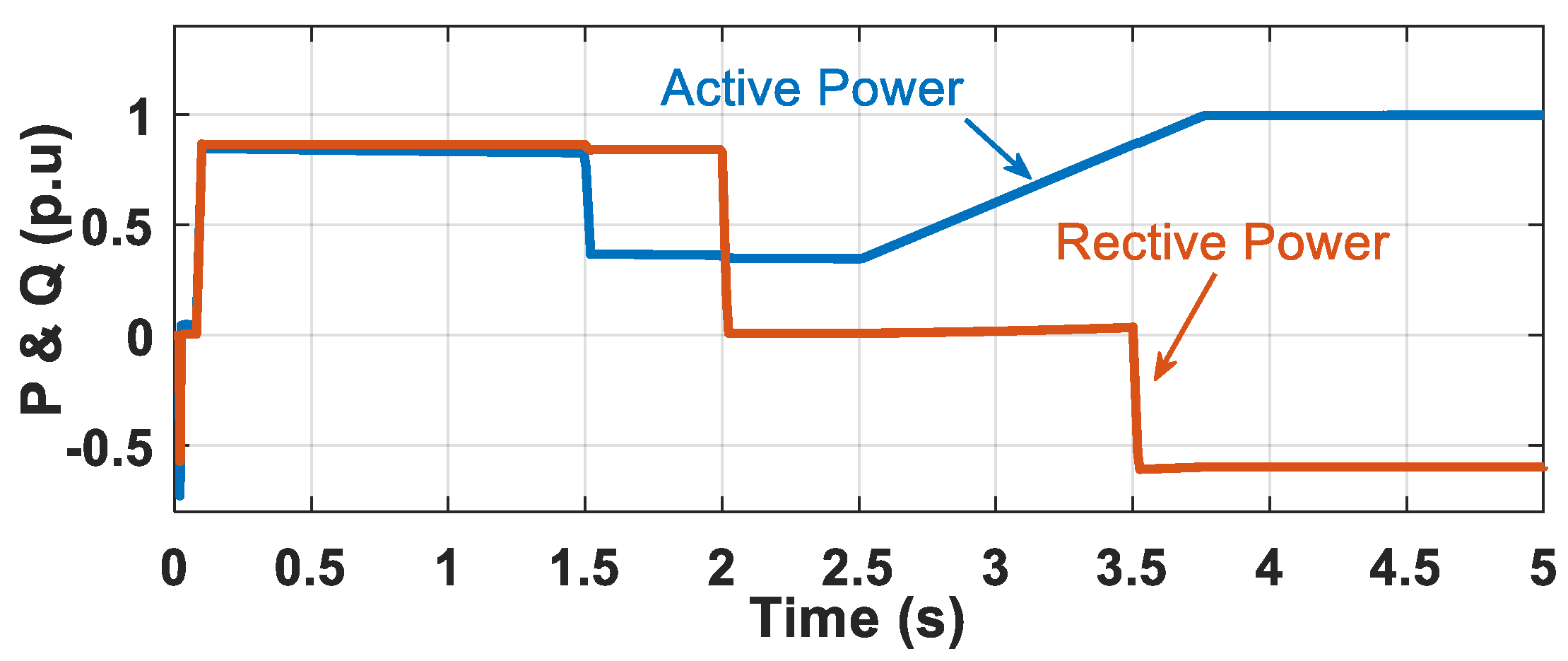

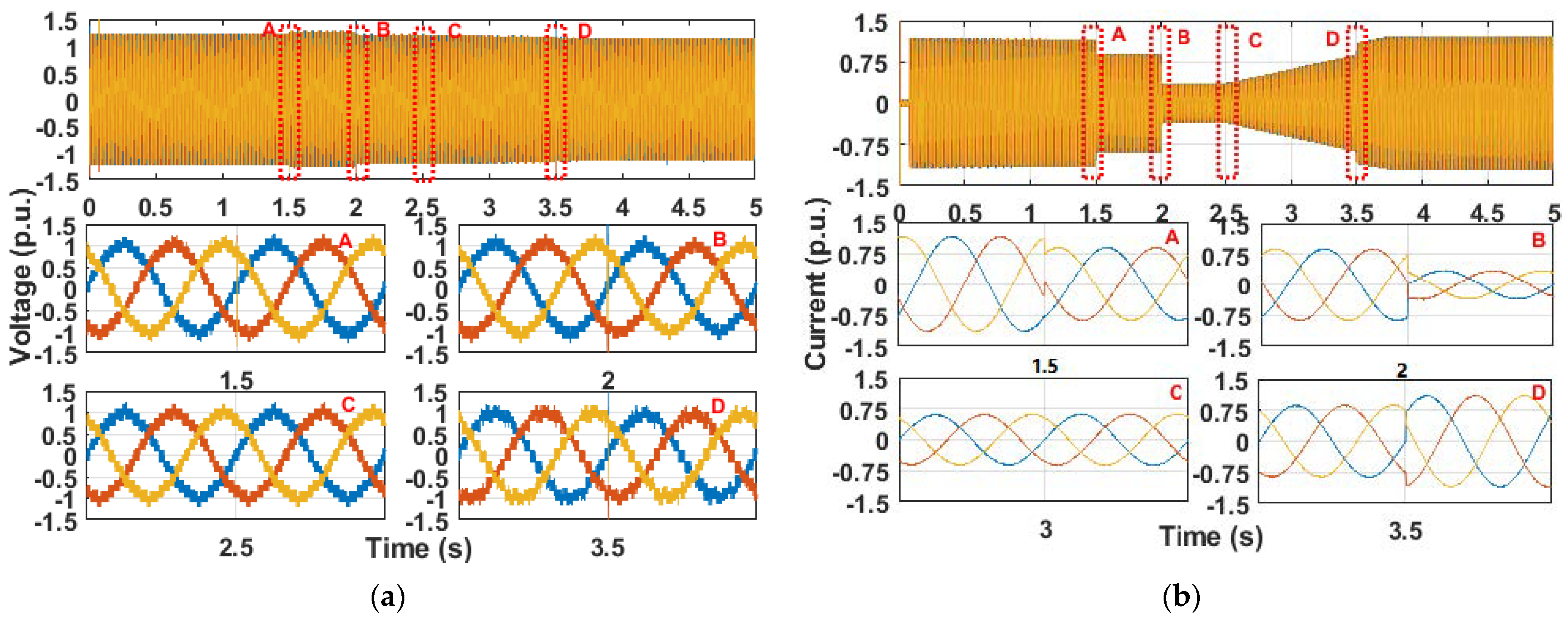

5. Simulation Results of Grid-Tied Mode

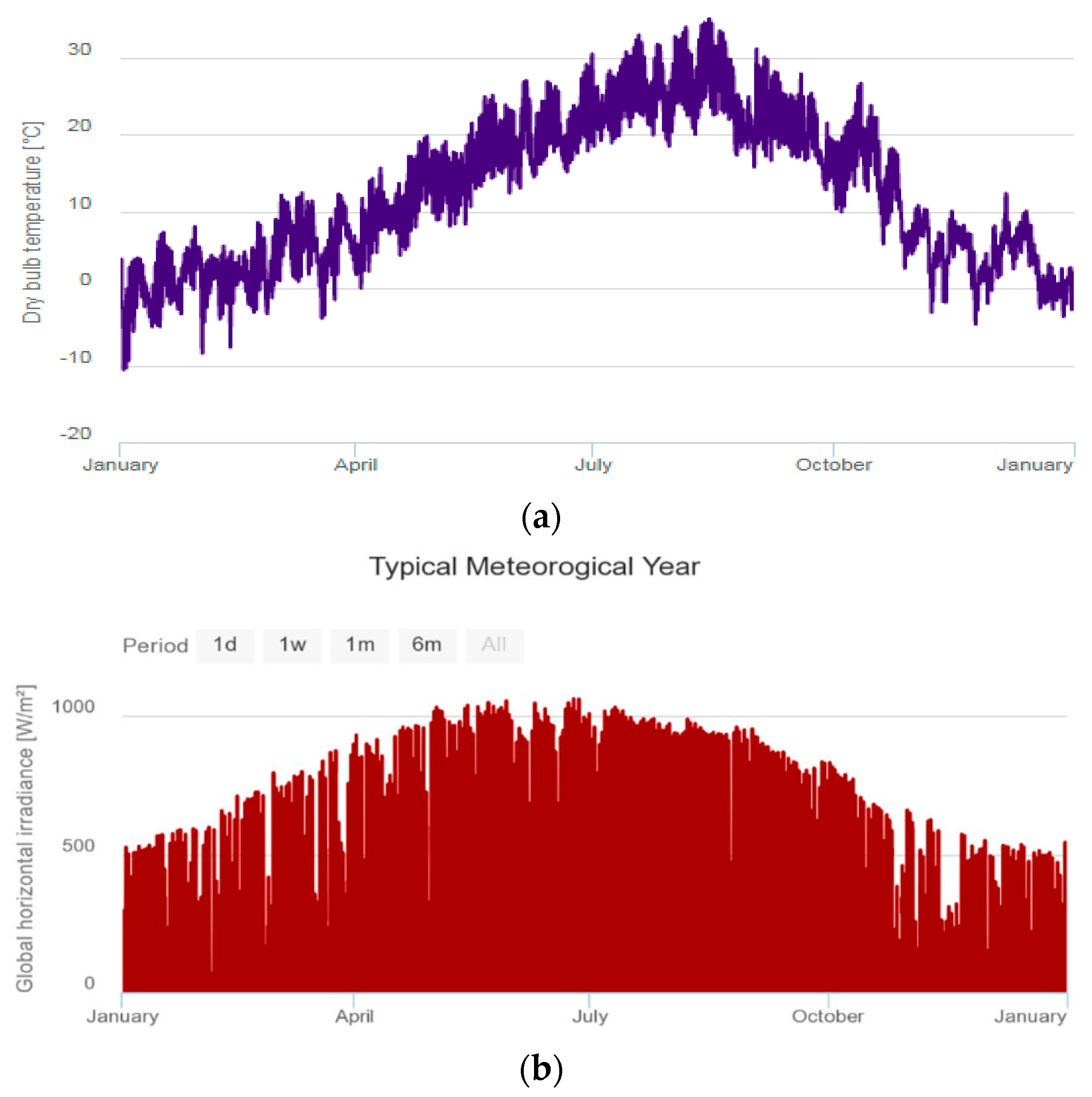

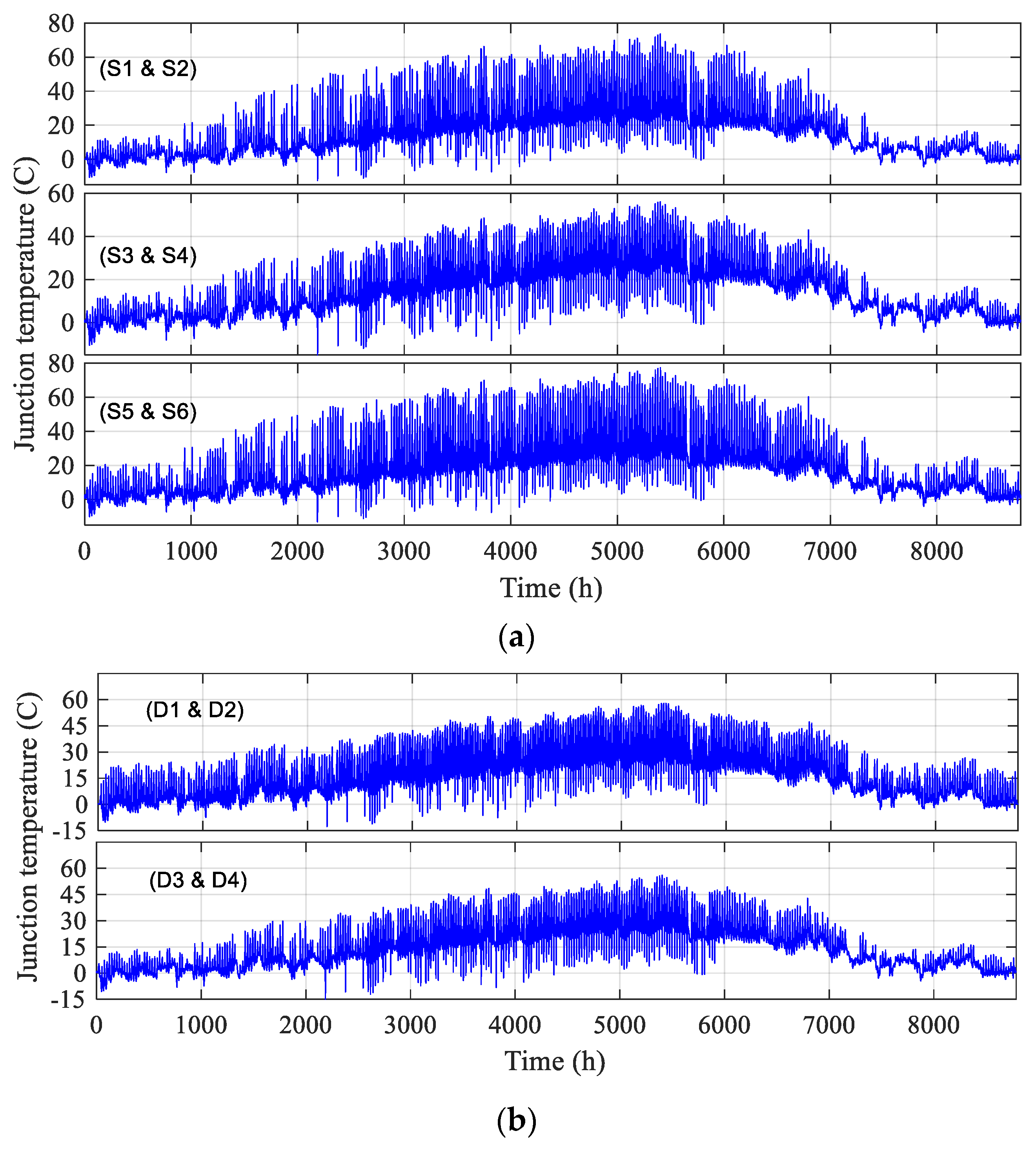

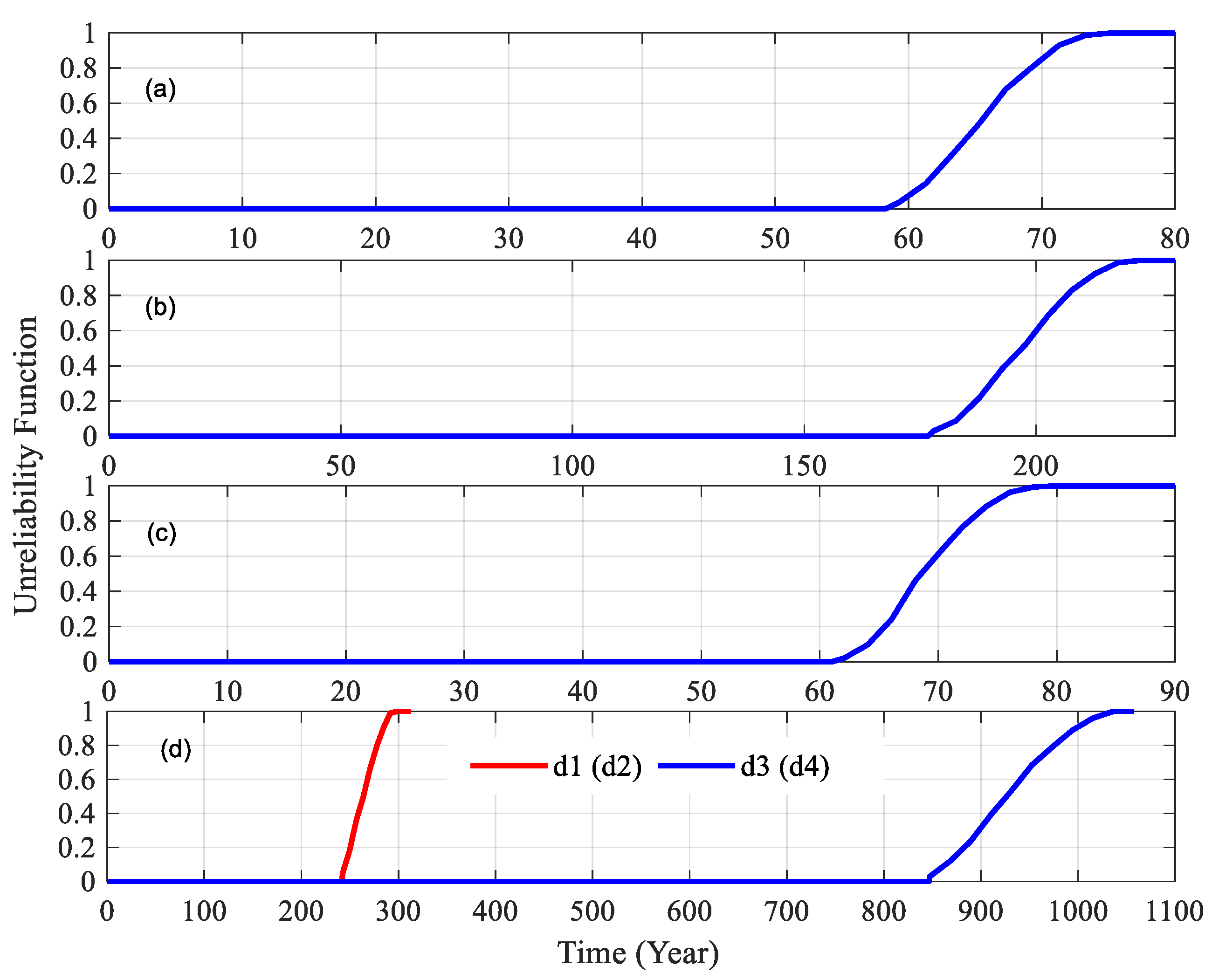

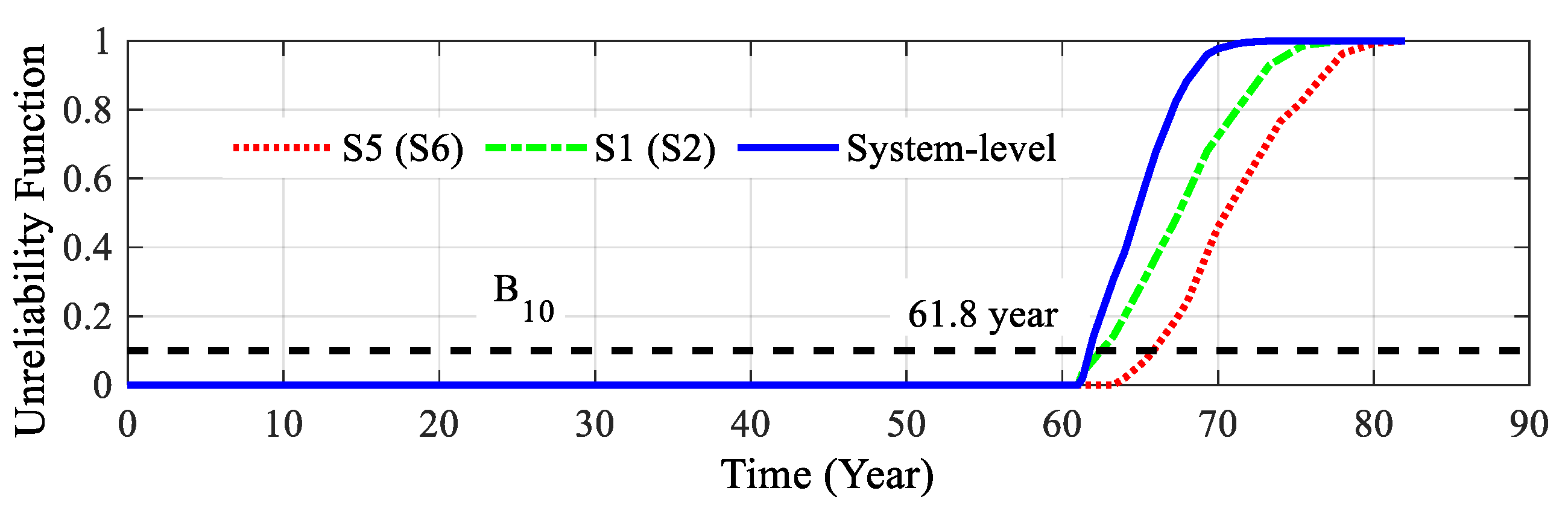

6. Lifetime Evaluation of the Proposed Inverter

7. Comparison and Discussion

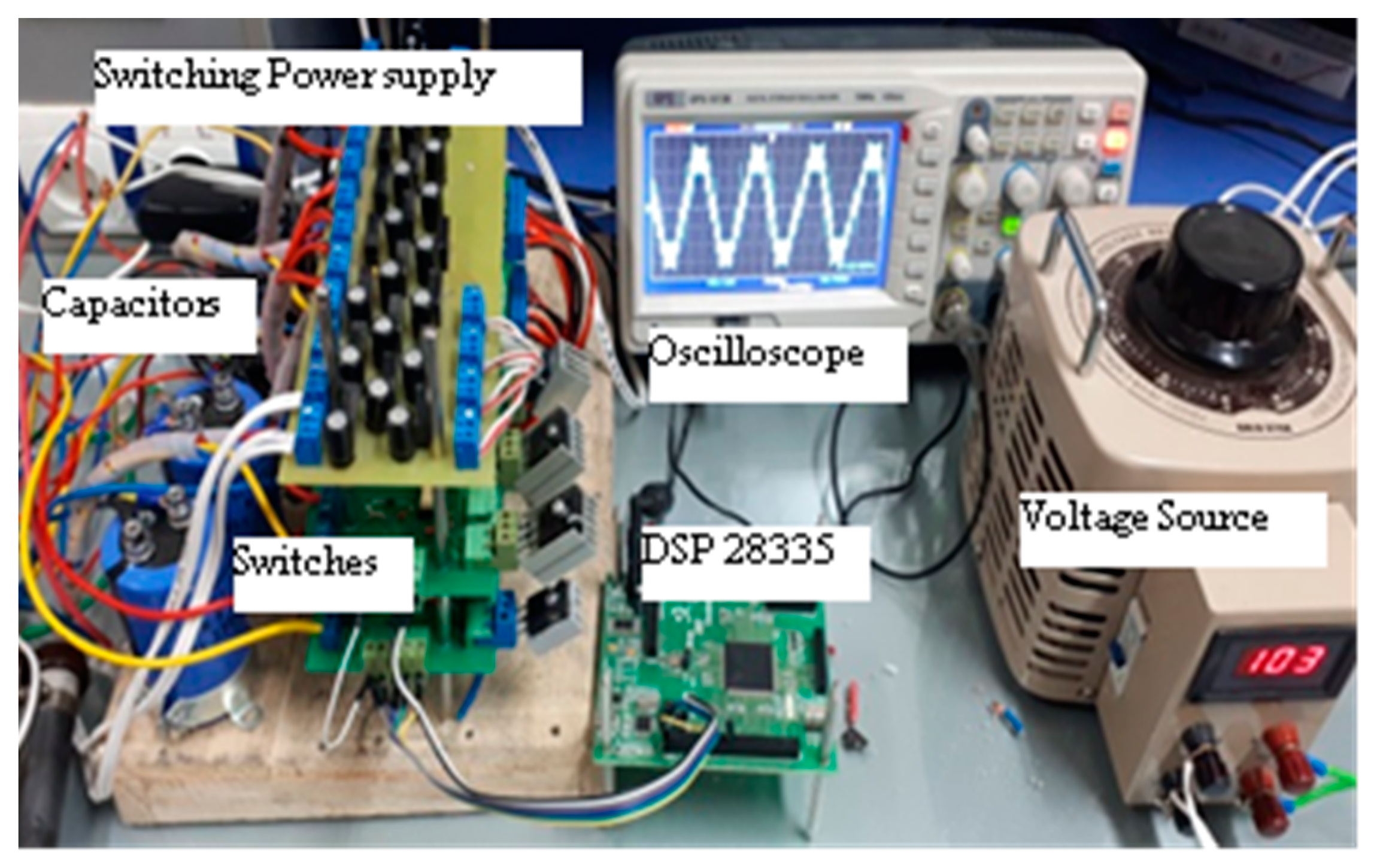

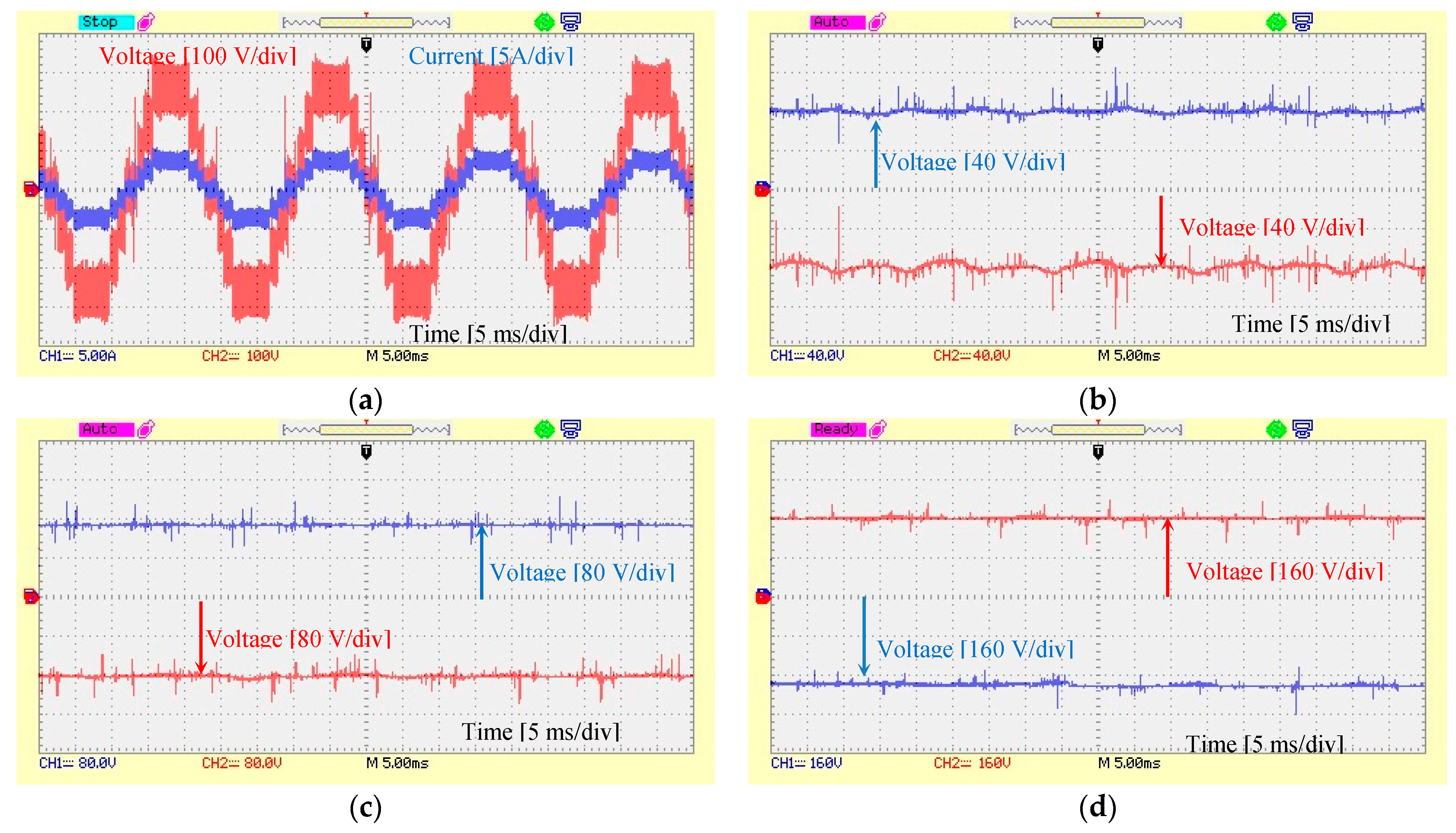

8. Experimental Results

9. Conclusions and Future Works

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Eskandari, R.; Babaei, E.; Sabahi, M.; Ojaghkandi, S.R. Interleaved high step-up zero-voltage zero-current switching boost DC–DC converter. IET Power Electron. 2020, 13, 96–103. [Google Scholar] [CrossRef]

- Vazquez, N.; Rosas, M.; Hernandez, C.; Vazquez, E.; Perez-Pinal, F.J. A New Common-Mode Transformerless Photovoltaic Inverter. IEEE Trans. Ind. Electron. 2015, 62, 6381–6391. [Google Scholar] [CrossRef]

- Vazquez, N.; Vazquez, J.; Vaquero, J.; Hernandez, C.; Vazquez, E.; Osorio, R. Integrating Two Stages as a Common-Mode Transformerless Photovoltaic Converter. IEEE Trans. Ind. Electron. 2017, 64, 7498–7507. [Google Scholar] [CrossRef]

- Xiao, H.; Xie, S.; Chen, Y.; Huang, R. An Optimized Transformerless Photovoltaic Grid-Connected Inverter. IEEE Trans. Ind. Electron. 2011, 58, 1887–1895. [Google Scholar] [CrossRef]

- Yu, W.; Lai, J.-S.; Qian, H.; Hutchens, C.; Zhang, J.; Lisi, G.; Djabbari, A.; Smith, G.; Hegarty, T. High-efficiency inverter with H6-type configuration for photovoltaic non-isolated ac module applications. In Proceedings of the 2010 Twenty-Fifth Annual IEEE Applied Power Electronics Conference and Exposition (APEC), Palm Springs, CA, USA, 21–25 February 2010; pp. 1056–1061. [Google Scholar]

- Victor, M.; Greizer, F.; Bremicker, S.; Hübler, U. Method of Converting a Direct Current Voltage from a Source of Direct Current Voltage, More Specifically from a Photovoltaic Source of Direct Current Voltage, into a Alternating Current Voltage. U.S. Patent 7,411,802, 12 August 2008. [Google Scholar]

- Yang, B.; Li, W.; Gu, Y.; Cui, W.; He, X. Improved Transformerless Inverter With Common-Mode Leakage Current Elimination for a Photovoltaic Grid-Connected Power System. IEEE Trans. Power Electron. 2012, 27, 752–762. [Google Scholar] [CrossRef]

- Su, X.; Sun, Y.; Lin, Y. Analysis on Leakage Current in Transformerless Single-Phase PV Inverters Connected to the Grid. In Proceedings of the 2011 Asia-Pacific Power and Energy Engineering Conference, Wuhan, China, 25–28 March 2011; pp. 1–5. [Google Scholar]

- Gu, Y.; Li, W.; Zhao, Y.; Yang, B.; Li, C.; He, X. Transformerless Inverter With Virtual DC Bus Concept for Cost-Effective Grid-Connected PV Power Systems. IEEE Trans. Power Electron. 2013, 28, 793–805. [Google Scholar] [CrossRef]

- Bruckner, T.; Bernet, S.; Guldner, H. The Active NPC Converter and Its Loss-Balancing Control. IEEE Trans. Ind. Electron. 2005, 52, 855–868. [Google Scholar] [CrossRef]

- Xia, Y.; Roy, J.; Ayyanar, R. A Capacitance-Minimized, Doubly Grounded Transformer less Photovoltaic Inverter with Inherent Active-Power Decoupling. IEEE Trans. Power Electron. 2017, 32, 5188–5201. [Google Scholar] [CrossRef]

- Eskandari, R.; Jahan, H.K.; Shotorbani, A.M.; Abapour, M.; Peyghami, S.; Blaabjerg, F. Asymmetric Cascaded Multilevel Inverter with Capacitor-based Half-bridge Cells and Reduced Number of Components. In Proceedings of the 2020 IEEE 21st Workshop on Control and Modeling for Power Electronics (COMPEL), Aalborg, Denmark, 9–12 November 2020; pp. 1–6. [Google Scholar]

- Bertilson, K.; Alishah, S.R.; Hosseini, H.S.; Babaei, E.; Aalami, M.; Ali, S.M.J.; Gharehpetian, B.G. A new generalized cascade multilevel converter topology and its improved modulation technique. Int. J. Circ. Theor. Appl. 2020. [Google Scholar] [CrossRef]

- Alishah, R.S.; Hosseini, S.H.; Babaei, E.; Sabahi, M.; Gharehpetian, G.B. New high step-up multilevel converter topology with self-voltage balancing ability and its optimization analysis. IEEE Trans. Ind. Electron. 2017, 64, 7060–7070. [Google Scholar] [CrossRef]

- Falck, J.; Felgemacher, C.; Rojko, A.; Liserre, M.; Zacharias, P. Reliability of Power Electronic Systems: An Industry Perspective. IEEE Ind. Electron. Mag. 2018, 12, 24–35. [Google Scholar] [CrossRef]

- Rahimi, T.; Hosseini, S.H.; Sabahi, M.; Gharehpetian, G.B.; Abapour, M. Reliability evaluation of a fault-tolerant three-phase interleaved DC-DC boost converter. Trans. Inst. Meas. Control 2019, 41, 1278–1289. [Google Scholar] [CrossRef]

- Flicker, J. PV inverter performance and component-level reliability. Presented at the 2014 NREL PV Module Reliability Workshop (PVMRW), Golden, CO, USA, 25–26 February 2014. [Google Scholar] [CrossRef]

- Cupertino, A.F.; Lenz, J.M.; Brito, E.M.S.; Pereira, H.A.; Pinheiro, J.R.; Seleme, S.I. Impact of the mission profile length on lifetime prediction of PV inverters. Microelectron. Reliab. 2019, 100–101, 113427. [Google Scholar] [CrossRef]

- Sintamarean, N.-C.; Blaabjerg, F.; Wang, H.; Yang, Y. Real Field Mission Profile Oriented Design of a SiC-Based PV-Inverter Application. IEEE Trans. Ind. Appl. 2014, 50, 4082–4089. [Google Scholar] [CrossRef]

- Haji-Esmaeili, M.M.; Naseri, M.; Khoun-Jahan, H.; Abapour, M. Fault-tolerant structure for cascaded H-bridge multilevel inverter and reliability evaluation. IET Power Electron. 2017, 10, 59–70. [Google Scholar] [CrossRef]

- Peyghami, S.; Wang, Z.; Blaabjerg, F. A Guideline for Reliability Prediction in Power Electronic Converters. IEEE Trans. Power Electron. 2020, 35, 10958–10968. [Google Scholar] [CrossRef]

- Rahimi, T.; Jahan, H.; Blaabjerg, F.; Bahman, A.; Hosseini, S. Fuzzy-Logic-Based Mean Time to Failure (MTTF) Analysis of Interleaved Dc-Dc Converters Equipped with Redundant-Switch Configuration. Appl. Sci. 2018, 9, 88. [Google Scholar] [CrossRef]

- Rahimi, T.; Ding, L.; Faraji, R.; Kheshti, M.; Pou, J. Performance Improvement of a Three-Phase Interleaved DC-DC Converter without Requiring Anti-Saturation Control for Post-Fault Conditions. IEEE Trans. Power Electron. 2020. [Google Scholar] [CrossRef]

- Sayed, A.; El-Shimy, M.; El-Metwally, M.; Elshahed, M. Reliability, Availability and Maintainability Analysis for Grid-Connected Solar Photovoltaic Systems. Energies 2019, 12, 1213. [Google Scholar] [CrossRef]

- Yang, Y.; Sangwongwanich, A.; Blaabjerg, F. Design for Reliability of Power Electronics for Grid-Connected Photovoltaic Systems. CPSS Trans. Power Electron. Appl. 2016, 1, 92–103. [Google Scholar] [CrossRef]

- Anurag, A.; Yang, Y.; Blaabjerg, F. Thermal Performance and Reliability Analysis of Single-Phase PV Inverters with Reactive Power Injection Outside Feed-In Operating Hours. IEEE J. Emerg. Sel. Top. Power Electron. 2015, 3, 870–880. [Google Scholar] [CrossRef]

- Sangwongwanich, A.; Yang, Y.; Sera, D.; Blaabjerg, F. Mission Profile-Oriented Control for Reliability and Lifetime of Photovoltaic Inverters. IEEE Trans. Ind. Appl. 2020, 56, 601–610. [Google Scholar] [CrossRef]

- Huld, T.; Müller, R.; Gambardella, A. A new solar radiation database for estimating PV performance in Europe and Africa. Sol. Energy 2012, 86, 1803–1815. [Google Scholar] [CrossRef]

- Lee, S. Single-Stage Switched-Capacitor Module (S3CM) Topology for Cascaded Multilevel Inverter. IEEE Trans. Power Electron. 2018, 33, 8204–8207. [Google Scholar] [CrossRef]

- Phanikumar, C.; Roy, J.; Agarwal, V. A Hybrid Nine-Level, 1-ϕ Grid Connected Multilevel Inverter with Low Switch Count and Innovative Voltage Regulation Techniques across Auxiliary Capacitor. IEEE Trans. Power Electron. 2019, 34, 2159–2170. [Google Scholar] [CrossRef]

- Liu, J.; Lin, W.; Wu, J.; Zeng, J. A Novel Nine-Level Quadruple Boost Inverter with Inductive-Load Ability. IEEE Trans. Power Electron. 2019, 34, 4014–4018. [Google Scholar] [CrossRef]

- Sandeep, N.; Yaragatti, U.R. Operation and Control of an Improved Hybrid Nine-Level Inverter. IEEE Trans. Ind. Appl. 2017, 53, 5676–5686. [Google Scholar] [CrossRef]

- Radwan, E.; Nour, M.; Awada, E.; Baniyounes, A. Fuzzy Logic Control for Low-Voltage Ride-Through Single-Phase Grid-Connected PV Inverter. Energies 2019, 12, 4796. [Google Scholar] [CrossRef]

- Miret, J.; Camacho, A.; Castilla, M.; García de Vicuña, J.L.; de la Hoz, J. Reactive current injection protocol for low-power rating distributed generation sources under voltage sags. IET Power Electron. 2015, 8, 879–886. [Google Scholar] [CrossRef]

- Leal, A.C.; Trujillo, C.; Piedrahita, F.S. Comparative of Power Calculation Methods for Single-Phase Systems under Sinusoidal and Non-Sinusoidal Operation. Energies 2020, 13, 4322. [Google Scholar] [CrossRef]

| Level | Switches States | Diodes States | Capacitors States | Vout |

|---|---|---|---|---|

| S1,S2,S3,S4,S5,S6 | d1,d2,d3,d4 | Cu2, Cl2, Cu3, Cl4 | ||

| 4 | 101010 | 0101 | D, C, D, C | 3.5 Vdc |

| 3 | 011010 | 1001 | C, F, D, C | 2.5 Vdc |

| 2 | 100110 | 0110 | F, C, C, F | 1.5 Vdc |

| 1 | 010110 | 1010 | C, N, C, F | 0.5 Vdc |

| −1 | 101001 | 0101 | N, C, F, C | −0.5 Vdc |

| −2 | 011001 | 1001 | C, F, F, C | −1.5 Vdc |

| −3 | 100101 | 0110 | F, C, C, D | −2.5 Vdc |

| −4 | 010101 | 1010 | C, D, C, D | −3.5 Vdc |

| Parameters | Values |

|---|---|

| Input voltage | 135 V |

| Cu1,Cl1,Cu2,Cl2,Cu3,Cl3 | 2200 µF |

| Switching strategy | Ls-SPWM |

| Grid voltage & frequency | 20 kHz |

| Base apparent power | 6.5 kVA |

| Base voltage (peak) | 320 V |

| L (grid voltage) | 1.7 mH |

| Number of cells | 2 |

| Topology | Nswitch | Ndiode | Ncapacitor | GV | TStand_voltage | Leakage Current Limiting Capability |

|---|---|---|---|---|---|---|

| [29] | 12 | - | 2 | 2 | 5.5 | no |

| [30] | 10 | - | 2 | 0.5 | 8 | yes |

| [31] | 8 | 3 | 3 | 4 | 5.75 | no |

| [32] | 12 | - | 3 | 4 | 5.25 | no |

| [Proposed] | 6 | 4 | 6 | 3.5 | 4.86 | yes |

| Components | Type |

|---|---|

| Switches | IRFP450 |

| Opto-coupler | TLP250 |

| Microprocessor | DSP-F28335 |

| Capacitors | 3300 µF |

| Switching power supply | iS0515s |

| Diodes | FFPF20UP40S |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Khoun Jahan, H.; Eskandari, R.; Rahimi, T.; Shalchi Alishah, R.; Ding, L.; Bertilsson, K.; Sabahi, M.; Blaabjerg, F. A Limited Common-Mode Current Switched-Capacitor Multilevel Inverter Topology and Its Performance and Lifetime Evaluation in Grid-Connected Photovoltaic Applications. Energies 2021, 14, 1915. https://doi.org/10.3390/en14071915

Khoun Jahan H, Eskandari R, Rahimi T, Shalchi Alishah R, Ding L, Bertilsson K, Sabahi M, Blaabjerg F. A Limited Common-Mode Current Switched-Capacitor Multilevel Inverter Topology and Its Performance and Lifetime Evaluation in Grid-Connected Photovoltaic Applications. Energies. 2021; 14(7):1915. https://doi.org/10.3390/en14071915

Chicago/Turabian StyleKhoun Jahan, Hossein, Reyhaneh Eskandari, Tohid Rahimi, Rasoul Shalchi Alishah, Lei Ding, Kent Bertilsson, Mehran Sabahi, and Frede Blaabjerg. 2021. "A Limited Common-Mode Current Switched-Capacitor Multilevel Inverter Topology and Its Performance and Lifetime Evaluation in Grid-Connected Photovoltaic Applications" Energies 14, no. 7: 1915. https://doi.org/10.3390/en14071915

APA StyleKhoun Jahan, H., Eskandari, R., Rahimi, T., Shalchi Alishah, R., Ding, L., Bertilsson, K., Sabahi, M., & Blaabjerg, F. (2021). A Limited Common-Mode Current Switched-Capacitor Multilevel Inverter Topology and Its Performance and Lifetime Evaluation in Grid-Connected Photovoltaic Applications. Energies, 14(7), 1915. https://doi.org/10.3390/en14071915