Abstract

In this work, a multi-mode radar transceiver supporting pulse, FMCW and CW modes was designed as an integrated circuit. The radars mainly detect the targets move by using the Doppler frequency which is significantly affected by flicker noise of the receiver from several Hz to several kHz. Due to this flicker noise, the long-range detection performance of the radars is greatly reduced, and the accuracy of range to the target and velocity is also deteriorated. Therefore, we propose a transmitter that suppresses LO leakage in consideration of long-range detection, target distance, velocity, and noise figure. We also propose a receiver structure that suppresses DC offset due to image signal and LO leakage. The design was conducted with TSMC 65 nm CMOS process, and the designed and fabricated circuit consumes a current of 265 mA at 1.2 V supply voltage. The proposed transmitter confirms the LO leakage suppression of 37 dB at 24 GHz. The proposed receiver improves the noise figure by about 20 dB at 100 Hz by applying a double conversion architecture and an image rejection, and it illustrates a DC rejection of 30 dB. Afterwards, the operation of the pulse, FMCW, and CW modes of the designed radar in integrated circuit was confirmed through experiment using a test PCB.

1. Introduction

Radar is an electronic device that detects and discriminates targets regardless of weather or day light condition. In various environments that cannot be easily identified by human eyes, radars are being used to effectively detect targets, especially in the case of military applications, evolving into complex, multi-period surveillance and reconnaissance radars that perform anti-drones, and civilian and scientific missions. It has been applied to the automotive and aerospace fields and is continuously being advanced.

The FMCW radar is mainly used as a long-range radar (LRR) by adjusting the frequency modulation bandwidth and frequency modulation time [1,2]. On the other hand, the UWB radar is used as a short-range radar (SRR) because it shows a high range resolution [3,4]. However, the FMCW radar is difficult to use as an LRR if the frequency modulation bandwidth and frequency modulation time are not sufficiently secured, and there is a disadvantage in that high output power must be provided. In addition, as the UWB radar should secure a wide bandwidth, it may affect other communication services and shows a disadvantage of limiting the maximum output power. As such, each radar has been usually implemented separately due to very different characteristics such as output power, bandwidth, and center frequency.

As a result, the number of radar sensors increases depending upon various applications, making the structure of the radar system very complex, bulky, and costly. Therefore, a technology for implementing a multi-mode radar with one IC is required, and research has been conducted to realize a radar transmitter supporting FMCW/UWB mode with a single chip [5]. However, radar transceivers that support three modes such as pulse, FMCW, CW modes have not been studied so far. Therefore, in this work, we propose multi-mode radar transceivers for pulse mode for long-range target detection and for FMCW and CW modes for detection and identification of short-range targets integrated in a single chip [6].

The conventional radar transceivers show some constraints. For the transmitters, the TX blocker in which the transmitted signal directly enters the receiver called self-interference (SI) and the LO leakage in which the LO signal is immediately radiated occur. This creates DC offset in the receiver, contaminates the received signal and makes it impossible to accurately identify the targets. Therefore, it is necessary to suppress LO leakage by removing the DC offset generated in the baseband of the transmitter.

For the receivers, a radar system uses a Doppler frequency of several Hz to several kHz to detect targets. A very low frequency flicker noise is created between SiO and the channel of MOSFETs comprising the receiver circuitry, leading to worsening the S/N ratio of the receiver [7]. Furthermore, as DC offset occurs due to SI and LO leakage of the transmitted signal, the noise figure is deteriorated, and the long-range detection is greatly degraded due to contamination of the received signal. Therefore, there is a need for the receiver that can improve noise figure and effectively suppress DC offset [8].

Section 2 shows the design requirements of transceivers for multi-mode radar systems. Section 3 explains the proposed transceiver, and describes the principle of suppressing LO leakage by applying an 8-bit current DAC to the baseband of the transmitter [9]. We also describe the proposed receiver, by analyzing the direct conversion and a double conversion structures with image rejection and explain about DC offset rejection [10,11,12,13,14]. In Section 4, simulation results of the designed transceiver is shown. After that, we describe the design and fabrication of a test PCB for measuring transceivers and radar tests for multi-mode applications. Finally, in Section 5 we conclude the measurement and radar test results of the transceiver for the proposed multi-mode radar system.

2. Design Requirements for Multi-Mode Radar Transceivers

In this work, three different modes—pulse, FMCW, and CW—are considered for the multi-mode radar transceivers. Design specifications are decided based on these three modes.

2.1. Pulse Radar

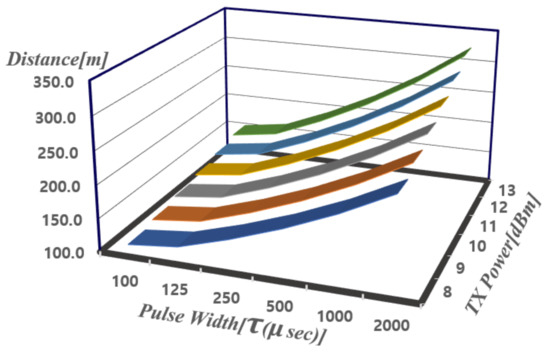

In pulse radar, the maximum detection distance () depends on the transmit power and pulse width () which is the reciprocal of bandwidth (BW). The maximum detection distance according to the pulse width () is obtained as follows. The Friis formula as shown in (1) can be used for calculating where the minimum received power () is obtained from Equation (2). Equation (3) derives using Equations (1) and (2) where is the transmit power; is the received power; and are the transmit/receive antenna gains, respectively; is RCS of the target; is the total noise figure of the receiver; is the thermal noise power density; and is the bandwidth which is the reciprocal of the pulse width [15]. Figure 1 shows the calculated maximum detection distance () according to transmit power, pulse width () and noise figure of 12.9 dB which is derived for the design specification later in Section 2.2.

Figure 1.

Radar detection distance () according to transmit power and pulse width ().

As the pulse width increases, radar can detect farther targets as shown in Figure 1. Furthermore, if the transmitter can emit high transmit power, it can detect farther targets. The maximum distance to target of 322 m can be obtained using of 2 ms and transmit power of 13 dBm using Equation (3) where can be computed from RF carrier frequency of 24 GHz used for this work. Therefore, the output power of the transmitter is designed to be greater than 13 dBm in this work.

2.2. FMCW Radar

The purpose of the multi-mode radar in consideration is to detect targets from a long distance in the pulse radar mode, and to continuously detect and identify targets in a short range in FMCW and CW modes when a moving target approaches from the very long distance. Therefore, to design the transceiver of the multi-mode radar system in FMCW mode, the maximum detection distance needs to be confirmed by analyzing the transmit power of the transmitter, the noise figure of the receiver, the frequency modulation bandwidth, and frequency modulation time.

Radar systems can detect targets through Doppler shift appearing in several kHz. However, in transceivers implemented in CMOS, flicker noise causes a significant problem in the Doppler shift. If the flicker noise is severe, the radar’s long-distance detection is rapidly deteriorated because the Doppler frequency of several kHz cannot be detected. Therefore, the maximum noise figure allowed to detect the Doppler frequency can be determined using sensitivity analysis as shown in Equations (4) and (5) which are rewritten from Equations (1) and (2), respectively.

The detectable minimum input signal level can be expressed as shown in Equation (4). of −115.1 dBm is calculated by substituting the transmit power () of 13 dBm, the transmit/receive antenna gains of 25 dBi, the free space loss (LOSS) of −94 dB, and the drone’s Radar Cross Section (RCS) of 0.001 into Equation (4). If SNR is set to 16 dB, the maximum allowable noise figure of 12.9 dB can be obtained by substituting 1 kHz Doppler shift (BW) into Equation (5).

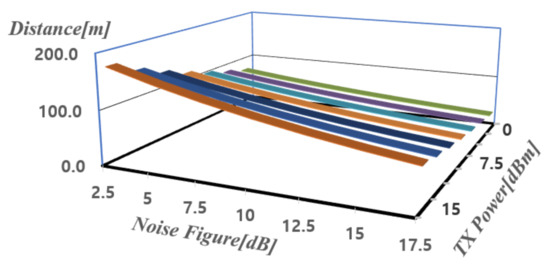

Figure 2 shows the maximum detectable distance () calculated according to the transmit power and the noise figure using Equations (1)–(3) for FMCW mode [15]. In Figure 2, the x-axis represents the noise figure, the y-axis represents the transmit power, and the z-axis represents the distance. It can be seen that as the transmit power increases and the noise figure decreases, the detectable distance increases. More calculated results for maximum detectable distance are tabulated as shown in Figure 2. When the maximum detection distance in FMCW mode is calculated using the noise figure of 12.9 dB and the transmission power of 13 dBm obtained earlier, a detection distance of 84.4 m can be obtained.

Figure 2.

Calculation of maximum detection distance for FMCW radars.

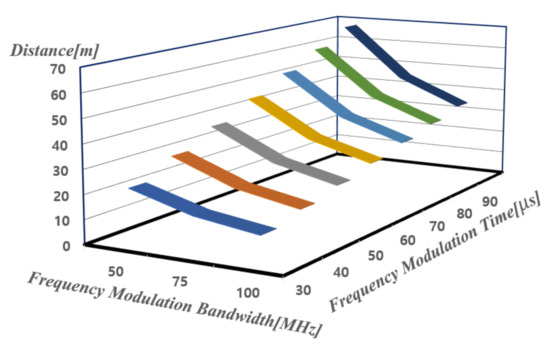

In order to secure the range resolution in FMCW mode, the frequency modulation bandwidth (B), frequency modulation time (T), and beat frequency need to be calculated and set as the design requirements of the radar. Beat frequency () and the distance to the target (R) in the FMCW radar can be expressed as shown in Equation (6) and range resolution can be computed using a specific beat frequency of kHz which is hardly affected by flicker noise [14,16]. Figure 3 shows the target range calculation according to frequency modulation time (T) and frequency modulation bandwidth (B).

Figure 3.

Target range calculation according to frequency modulation time (T) and frequency modulation bandwidth (B) with kHz.

The beat frequency is also calculated according to the distance and velocity of targets by setting B to 75 MHz and T to 50 s specified from Table 1. As flicker noise appears in the range of 0 to several kHz, it is confirmed that targets with a distance of 10 to 100 m and a velocity of 10 to 100 km/h can be detected by measuring beat frequency of the 30 kHz to 300 kHz, which is less affected by the flicker noise. The detailed calculation is summarized in Table 1. In this work, only UP chirp has been used due to the limitation of test equipment.

Table 1.

Beat frequency calculation of FMCW radar (only UP chirp).

2.3. CW Radar

The CW radar can detect the Doppler frequency of an approaching or retreating target, determining the presence or absence of a target and the target’s velocity. Because CW radar can only know the velocity of the target, it must be used together with the FMCW radar to detect the distance to target. In addition, as the FMCW radar has multiple-target ambiguity, a CW waveform is usually added after one period of the FMCW waveform to distinguish the components for pure Doppler shifts and find a frequency that matches the intrinsic Doppler component to resolve the multiple-target ambiguity. In this work, CW radar is applied only for the verification of transceiver operation.

2.4. Design Specification Summary

The design requirements for the proposed multi-mode radar transceiver is summarized. The minimum input signal, maximum noise figure, maximum detection distance, frequency modulation bandwidth in FMCW mode, and detection distance according to modulation time are confirmed in Table 2. It can be seen that the RCS is set for a drone [17], and the transmit/receive antenna gains are also obtained by horn antenna manufactured for this work. For a reasonable NF requirement (7∼13 dB for overall receiver), the antenna gain will need to be quite high based on a wide BW leading to sufficient radar detection performance. Moreover, the thermal noise power density at normal temperature is −174 dBm/Hz. As it has a bandwidth of 1 kHz, the maximum thermal noise power density is −144 dBm/Hz. Afterwards, design requirements are verified by measuring the transceiver and testing the radar.

Table 2.

Radar transceiver design requirements.

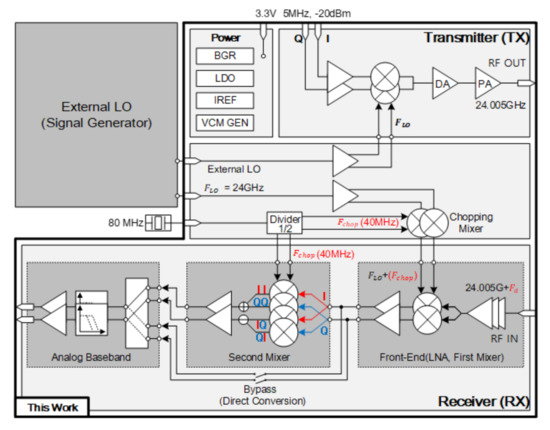

3. Design of the Proposed Transceiver

Figure 4 is the block diagram for the proposed multi-mode radar transceiver. In the transmitter side, LO leakage in RF TX output is suppressed by devising a current DAC. In the receiver side, a chopping frequency is generated from LO block used for mixers for avoiding the flicker noise, leading to lower noise figure. In addition, LO leakage and TX blocker rejection are suppressed using the 2nd mixer. The transceiver is composed of transmitter (TX), receiver (RX), buffer to input external LO signal and auxiliary circuits such as VCM generator to generate common mode voltage, current generators (IREF), bandgap-reference (BGR), low drop regulator (LDO), and an SPI. The TX is composed of analog baseband (ABB), up conversion mixer, and power amplifier (PA). Moreover, RX consists of ABB, mixers, and low noise amplifier (LNA). BGR generates internal bias current and voltage, and LDO supplies 1.2 V of voltage to each block. Furthermore, SPI controls all functions of the blocks. The supply voltage is 3.3 V, and an external LO signal is applied to the mixer of the transmitter and the first mixer of the receiver. The baseband input frequency of the transmitter is 5 MHz, and it radiates 24.005 GHz signal at the output of the transmitter. The receiver receives the frequency of 24.005 GHz + and obtains from the baseband output of the receiver. At this time, in order to reduce the flicker noise of the receiver, the LO frequency of the first mixer of the receiver was designed in a structure in which 40 MHz (Chopper frequency) was added to 24 GHz. In this section, the structure of the proposed transmitter and the principle of LO leakage suppression are described. The structure of the proposed receiver is then described compared with direct conversion receiver. In particular, as the proposed receiver can reduce the influence of flicker noise, a lower noise figure can be obtained compared to the direct conversion receiver.

Figure 4.

Block diagram of the proposed multi-mode radar transceiver.

3.1. Architecture of Direct Conversion Transmitter

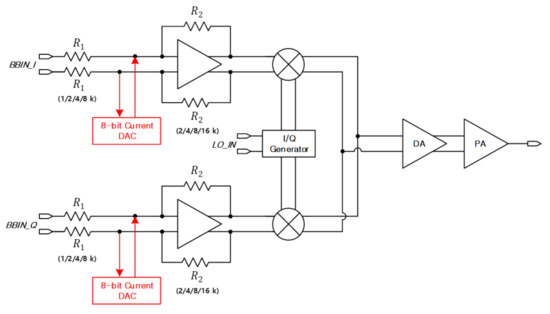

The transmitter is designed in a direct-conversion architecture. This architecture guarantees high linearity compared to other types of transmitters. However, if the LO leakage is generated by the DC offset originated in the baseband, and the signal power of the LO leakage can become larger than the transmit power, it is impossible for receiver to obtain the desired signal. This problem saturates the receiver as well as the transmitter, directly affecting the far-field detection performance of the radar system. Therefore, there is a need for a method that can effectively remove the DC offset. An 8-bit current DAC is devised for removing the DC offset as shown in Figure 5. In addition, as a double balanced mixer can structurally suppress the LO leakage signal, a conventional passive mixer is employed for the proposed transmitter [8]. The PGA uses a complementary two stage op-amp to secure sufficient gain and phase margin for the transmitter [18].

Figure 5.

Block diagram of direct conversion structure transmitter.

3.1.1. LO Leakage Suppression through DAC

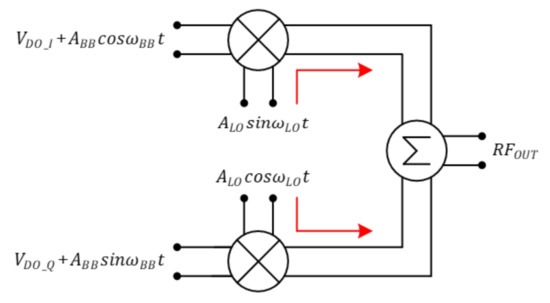

Figure 6 shows the principle that LO leakage occurs in a direct conversion transmitter. A signal including DC offset enters into the I/Q phase and is mixed with the LO signal, going to the . can be expressed as shown in Equation (7).

where occurs due to DC offset and causes LO leakage. This does not occur when there is no DC offset.

Figure 6.

LO leakage generation in direct conversion transmitter.

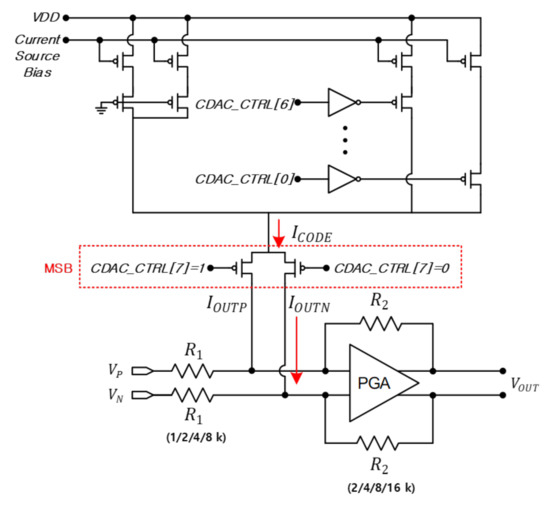

Figure 7 shows the circuit diagram for CDAC where the current can be sequentially adjusted by multiples of 300 nA from LSB to MSB. Current can be adjusted up to 19.2 A, and the input values of the P and N nodes are reversed through the MSB. For example, if 1 is set to MSB, the PMOS of the P node is turned off and the PMOS of the N node is turned on.

Figure 7.

CDAC circuit diagram.

If DAC is connected to the P and N nodes of the PGA, respectively, and the current according to the 8-bit CODE is supplied to the P node and the current comes out of the N node, a DC voltage is obtained by the product of the equivalent resistance of the PGA and the current according to the CODE of the DAC as in Equation (8). The voltage as much as the offset can be generated, and DC offset is removed. Through SPI, we adjust the CODE of 8 bits, check the LO leakage on the spectrum analyzer, and adjust the CODE in the direction that LO leakage decreases.

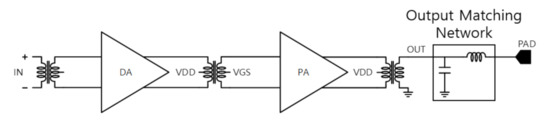

3.1.2. Power Amplifier (PA) Design

The maximum transmit power () is set to 13 dBm in design requirement. For this purpose, a power amplifier and a drive amplifier with matching networks are designed as in Figure 8.

Figure 8.

PA and Drive Amplifier (DA) block diagram.

As the PA must supply a high power to the antenna, the power gain is compensated additively through the DA. Therefore, inter-stage matching between DA and PA is also required, and the DA output and the PA input are matched using a transformer [19,20].

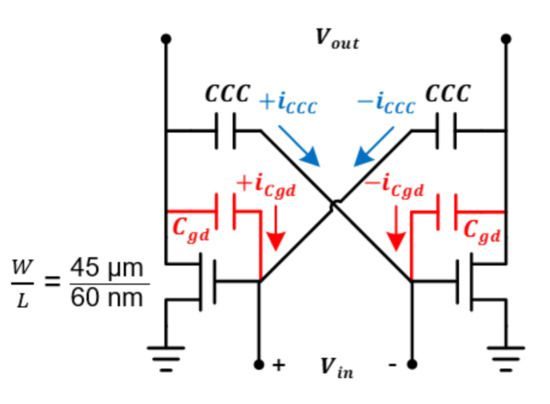

Because PA consumes a lot of current, the transistor size becomes very large, and as the transistor size increases, the parasitic capacitance also increases. In particular, as a leakage current is generated by the parasitic capacitor between the drain and the gate, and the gain and efficiency of the power amplifier decrease. Therefore, it is designed to cancel the leakage current by applying a cross-coupled capacitor (CCC) as shown in Figure 9. If and are the same, the leakage current is canceled effectively.

Figure 9.

PA and DA circuits diagram.

The impedance of the maximum power transfer was confirmed through the power amplifier design. As the impedance seen from the drain of MOSFET used for PA at a specific bias is 62.68 − j50.22, conjugate matching was employed for maximum power transfer. At this time, the small signal impedance of the PA was also checked and matched so that the viewed from the output of the PA could come out below −10 dB, and the simulation result of the maximum output power of about 12 dBm was confirmed.

At this time, the gate bias voltages of DA and PA having the same circuit configuration but different bias are designed to 480 mV and 650 mV, respectively. In Table 3, design parameters for transmitter are summarized using the design philosophy introduced in Section 3.1.

Table 3.

Transmitter design requirements.

3.2. Architecture of Receiver

3.2.1. Conventional Receiver Architecture

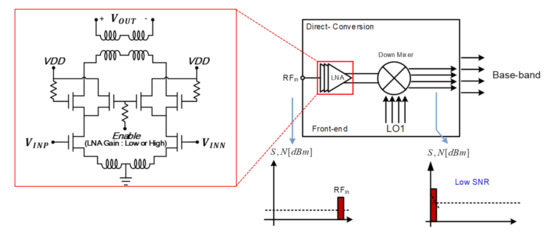

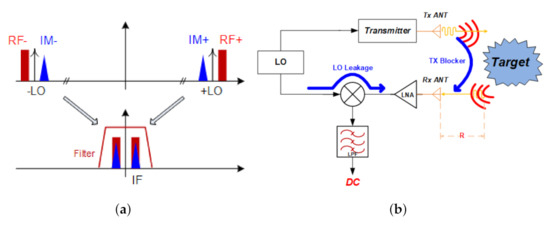

Figure 10 shows the conventional receiver architecture using the direct conversion structure where 3-stage inductively degenerated differential LNA [7] and down mixer are usually adopted. As the direct conversion receiver directly down-converts the RF signal to the baseband, it is highly affected by the flicker noise in the baseband. Therefore, the double conversion is alternatively employed for this work.

Figure 10.

Direct conversion receiver architecture.

Figure 11a shows that SNR decreases due to the image signal generated in direct down-conversion, and Figure 11b shows the LO leakage and transmission signal generated by the parasitic components of the mixer. This illustrates that DC offset is generated due to TX blocker directly inserted from the transmitter. Therefore, we propose a double conversion receiver and add a DC Offset rejection circuit to suppress the flicker noise.

Figure 11.

Disadvantage of direct conversion receiver architecture. (a) Image signal. (b) LO and TX leakage.

3.2.2. Proposed Receiver Architecture

The proposed receiver consists of a 3-stage LNA, 1st down mixer, 2nd down mixer, and baseband circuitry such as the high-pass filter. The degenerated inductive differential configuration is employed for LNA as drawn inside Figure 10. In order to reduce the flicker noise, improve noise figure, and remove DC offset, three techniques are applied to the 2nd down mixer.

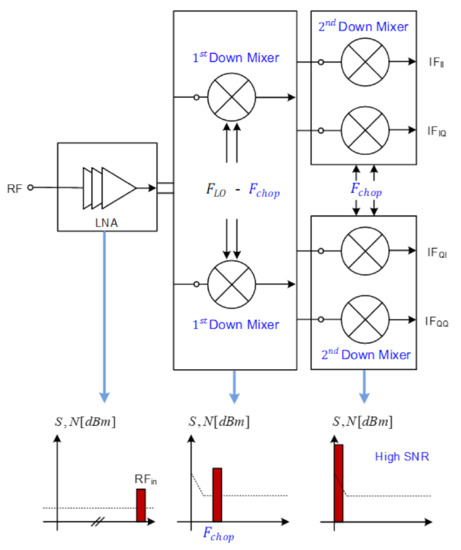

3.2.3. Proposed Double Conversion Receiver

Figure 12 shows the proposed double conversion architecture and SNR in each block. The received signal is down-converted to the baseband through the IF band less affected by flicker noise. Compared to the direct conversion architecture of Figure 10, the receiver gain increases as much as the gain of the 2nd down mixer with Transimpedance Amplifier (TIA) included, and thus a lower noise figure can be obtained.

Figure 12.

Double conversion receiver architecture.

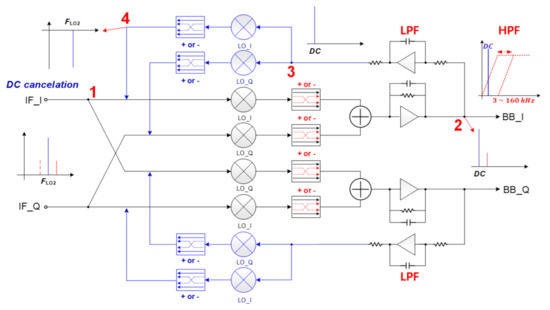

3.2.4. LO Leakage and TX Blocker Rejection Technique

The LO leakage generated by mixer and LNA parasitics, and the TX blocker where the transmitted signal directly enters the receiver port, create a DC offset in the baseband of the receiver. This DC offset contaminates the received signal from the target and should be removed as much as possible. Figure 13 shows the proposed DC offset cancellation principle. Here, the signal path from node 1 to node 2 becomes the main path, and the feedback path from node 2 to node 4 operates as an LPF. The whole transfer function from IF_I to BB_I becomes an HPF as shown in the right top of Figure 13. The cut-off frequency of HPF can be set to 3 kHz or 160 kHz by adjusting the capacitance. When the LO leakage indicated in blue enters the mixer’s input node (node 1), the LO leakage is down-converted through the mixer and appears as a DC at the 2nd mixer’s output node. The signal to be detected is marked in red at the baseband node (node 2) where the cut-off frequency of the low-pass filter (LPF) of the feedback loop is set lower than the detected signal so that only the DC component passes the LPF. Thereafter, the fed-back DC signal is up-converted to the LO frequency and transmitted to node 4. If the phase of the DC signal delivered to node 4 through the switch becomes out of , LO leakage can be effectively eliminated at the output node (node 2).

Figure 13.

DC offset cancellation technique in the receiver.

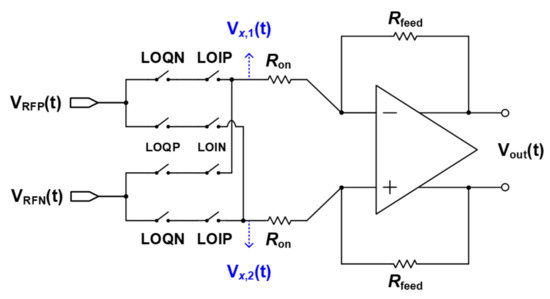

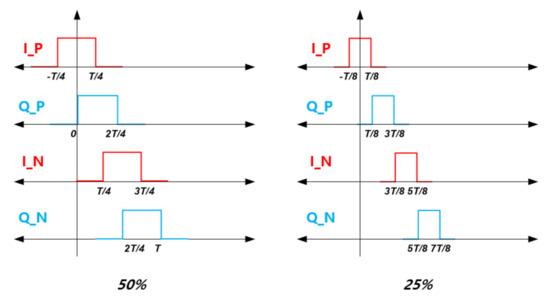

Figure 14 is a diagram for the mixer and TIA used in the 1st mixer and the 2nd mixer where a passive mixer configuration is employed to increase linearity. In the quadrature structure, when the mixer is driven with a 50% duty cycle, there is an overlapped period in which the I and Q-paths are turned on at the same time as shown in Figure 15. In this case, current flows simultaneously through the I- and Q-paths. The current flowing between the I- and Q-paths passes through the channel of the switching transistor, creating additional flicker noise. For this reason, the mixer was devised to be driven with a 25% duty cycle to prevent the I- and Q-paths from being turned on at the same time, and the generation of such additional flicker noise was suppressed [10].

Figure 14.

Mixer and Transimpedance Amplifier (TIA) circuit diagram in 25% duty cycle.

Figure 15.

50% and 25% duty cycles for differential I and Q phases of the mixer.

When the mixer adopts a 25% duty cycle for LO injection, a waveform for the positive I phase () having a duty of [−T/8, T/8] in Figure 15 can be expressed by Equation (9) where means the duty ratio. Therefore, one can find , , and .

can be expressed as shown in Equation (10).

Using Equation (10), the conversion gain of the switching cell of the mixer is calculated, and the final gain considering the TIA can be expressed by Equation (11), and the gain is determined by the on−resistance of the mixer and the feedback resistance of the TIA.

Furthermore, the total gain can be expressed by Equation (12).

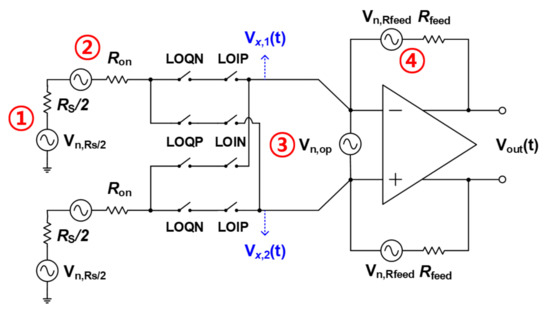

In the meantime, for mixer’s noise analysis, as shown in Figure 16, it can be expressed as an equivalent model. Internal resistance is expressed as a resistance of at each input node in consideration of differential input, and noise generated by OP AMP is expressed as as an input referred noise source. The noise source at each resistance is expressed in voltage, the switching operation occurs in the mixer, and the RF signal is converted into an IF signal.

Figure 16.

Equivalent noise analysis model of proposed mixer.

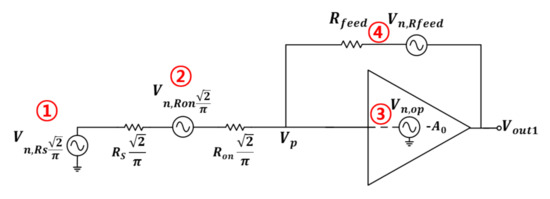

NF is found using 4 noise sources (①∼④) represented as shown in Figure 17. As it can be expressed as , and are found using Equations (12) and (13).

Figure 17.

Equivalent noise analysis using half circuit modeling.

Substituting the Equations (12) and (13) into , the final noise figure can be expressed by Equation (14).

As described in Equation (14), when the mixer is driven with a 25% duty cycle, there is no period in which the I- and Q-paths are turned on at the same time, so the flicker noise does not affect the mixer noise performance. The final noise figure is only represented by the internal resistance of the input source (), the on−resistance of the mixer (), and the feedback resistance of the TIA (). Therefore, the noise figure for mixer with 25% duty cycle is significantly improved compared to that with a 50% duty cycle [10,11,12]. The 1st mixer operates with 50% duty cycle used for pulse mode, on the contrary, the 2nd mixer operates with 25% duty cycle used for FMCW and CW modes. PRF for the pulse is not affected by this proposed scheme.

Summarized design parameters are illustrated in Table 4 in considering the design philosophy explained in Section 3.2.

Table 4.

Receiver design requirements.

4. Simulation & Measurement Results

4.1. Simulation

4.1.1. Transmitter Simulation

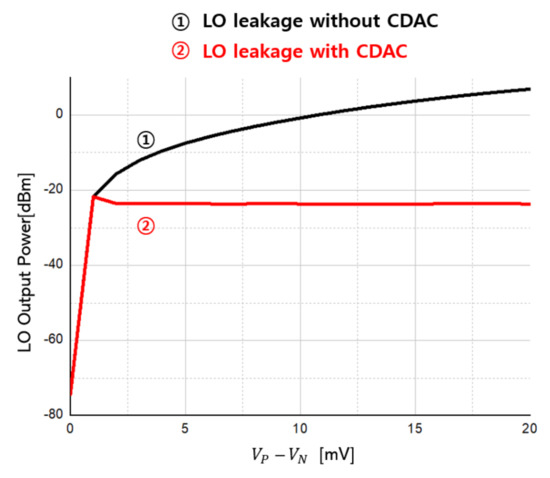

600 mV DC is applied to of the PGA for the transmitter, and DC inputs varying from 600 mV to 620 mV are applied to as shown in Figure 7, and a DC offset is created by amount of in simulation. Figure 18 shows simulated LO leakage according to . When DC offset is created by making 10 mV difference between the and nodes, LO leakage of about 0 dBm occurs. In design stage, the PGA was designed to provide −6–24 dB gain using 6 dB gain step. The PGA simulation confirms this performance accurately. At this time, the PGA gain is set to 24 dB, and the resistances of and set to 1 k and 16 k, respectively. Therefore, is about 1 k, and if a current of about 10 A is passed from the DAC, the voltage as much as DC offset can be generated. The red line is the simulation result of suppressing the LO leakage using CDAC, and it can be seen that the LO leakage can be maintained lower around −23 dBm using CDAC.

Figure 18.

Simulation of LO leakage suppression by the proposed transmitter.

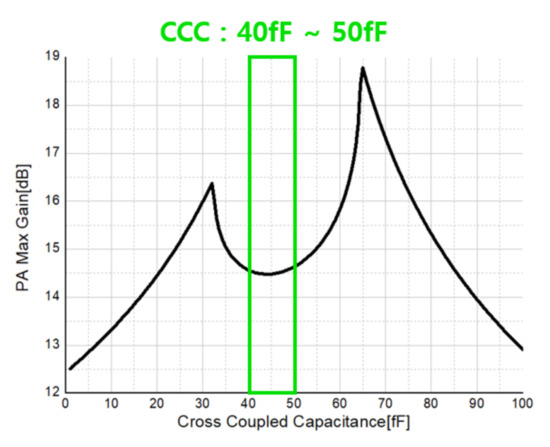

In addition, the maximum output power of the transmitter is simulated. Through the simulation, a maximum output of 12 dBm was obtained using the PA circuitry. Figure 19 confirms that the maximum gain of PA becomes stable according to the CCC value, and through this simulation result, the CCC value was determined as 48 fF. In addition, the passive up mixer provides −6 dB gain in simulation. The total current consumption of the transmitter results in 86 mA where the PA consumes 60 mA, the DA does 12 mA and the baseband circuitry does 14 mA in simulation.

Figure 19.

Maximum gain simulation according to CCC value as in Figure 9.

4.1.2. Receiver Simulation

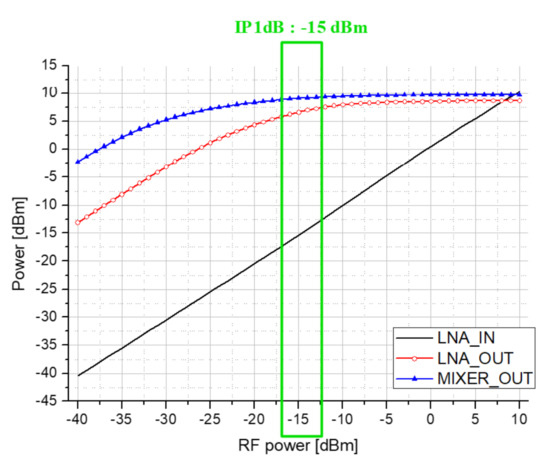

Figure 20 shows the P1dB simulation result of the receiver. The RF frequency was set to 24 GHz, the LO frequency was set to 23.96 GHz, and RF power was used as a variable. The solid black line represents the input, the red circular symbol represents the LNA output, and the blue triangle symbol represents the output of the mixer.

Figure 20.

Front-end P1dB simulation result.

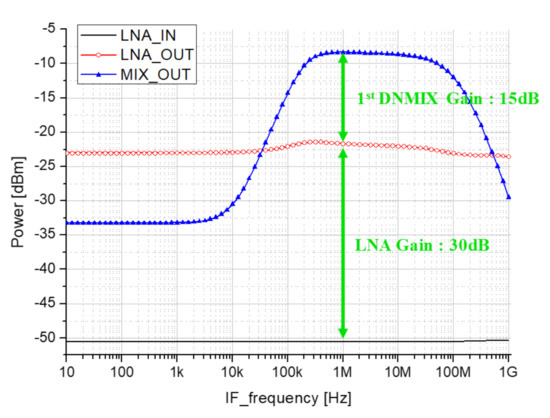

Figure 21 shows the result of gain simulation with the IF frequency as a variable. The solid black line represents the input, the red circular symbol represents the LNA output, and the blue triangle symbol represents the output of the mixer. The gain of the 3-stage LNA is about 30 dB, and the gain of the 1st down mixer is about 15 dB.

Figure 21.

Front-end gain simulation result.

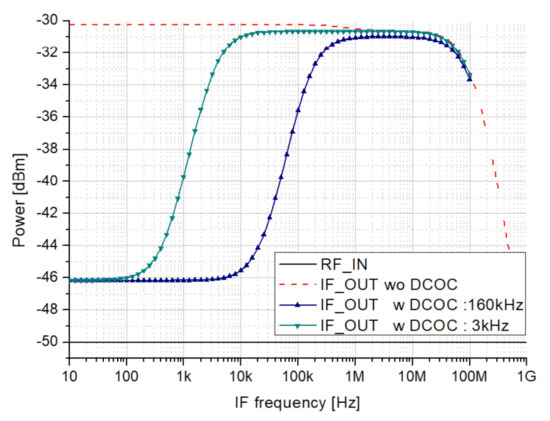

Figure 22 shows the result of the transfer function simulation of IF-stage. The black solid line represents the input, the red dotted line represents the output of the 2nd down mixer when DCOC (DC Offset Cancellation) mode is turned off, and the blue triangle symbol and the green inverted triangle symbol represent the output of the 2nd down mixer when DCOC mode is turned on. The gain is obtained about 19 dB, and high-pass filter (HPF) cut-off frequencies are achieved about 160 kHz and 3 kHz.

Figure 22.

IF-stage gain simulation result.

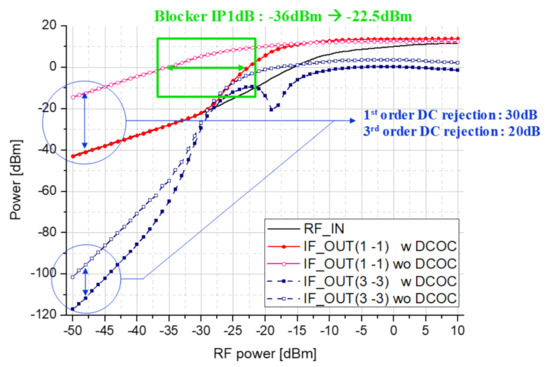

Figure 23 shows of simulation results to check the blocker P1dB and DC rejection characteristics of the proposed receiver. The black solid line is the blocker input signal, and the red solid line symbol indicates the power of the DC component from the IF output. The blue dotted symbol indicates the DC component from the IF output by the third order term. Filled symbols indicate when DCOC mode is turned on, and empty symbols indicate when DCOC mode is turned off. Blocker OP1dB was set to 0 dBm, which is judged not to contaminate the desired signal in IF output, and it was confirmed that the blocker P1dB is improved by about 13.5 dB compared to the case where DCOC mode was turned off. In addition, it can be seen that the DC rejection effect of about 30 dB is achieved at the input less than −30 dBm.

Figure 23.

Blocker P1dB and DC rejection simulation result of proposed receiver.

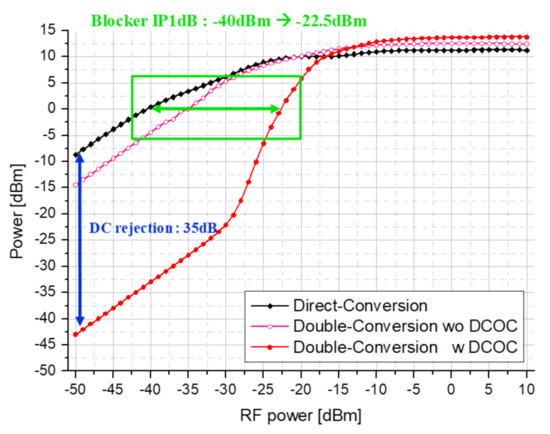

For comparison with direct conversion receiver, the blocker test is performed. Figure 24 shows the comparison result of the block test between the proposed double conversion receiver and a general direct conversion receiver. First, looking at the blocker P1dB, the blocker IP1dB of about 17.5 dB is improved in the proposed receiver compared to the direct conversion receiver. This means that even at 17.5 dB higher than the transmit power, the received signal is not contaminated. In addition, the DC offset removal that may occur due to Tx blocker and LO leakage is improved by about 35 dB. However, for inputs above −30 dBm, this effect gradually decreases.

Figure 24.

Simulation result of blocker P1dB and DC rejection for comparison.

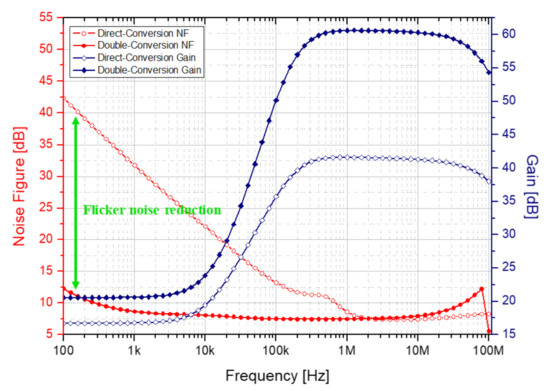

Figure 25 shows the noise figures of the proposed double conversion receiver and the direct conversion receiver. The red circular symbol represents the noise figure and the blue diamond symbol represents the gain. An empty symbol indicates a direct conversion receiver, and a filled symbol indicates a proposed receiver. The proposed receiver has an additional gain in the 2nd down mixer. An image rejection and DCOC loop are added to lower noise by about 30 dB compared to direct conversion at 100 Hz, which is susceptible to flicker noise. Looking at the simulation result, it can be seen that the noise figure is significantly reduced below 1 MHz.

Figure 25.

Noise simulation result for comparison.

4.2. Measurement

The length from the connector port to transceiver pads can vary according to the test PCB type fabricated for measurement. In order to verify a circuit in the millimeter wave band, a board that can guarantee performance in a high frequency band, modeling of wire bonding, and an appropriate impedance matching circuit are required. Therefore, a ceramic-based RO4003C substrate was used for PCB fabrication, and after modeling the wire bonding and matching circuit using a 3D CAD tool, the S-parameter was confirmed through simulation and then the final fabrication was carried out.

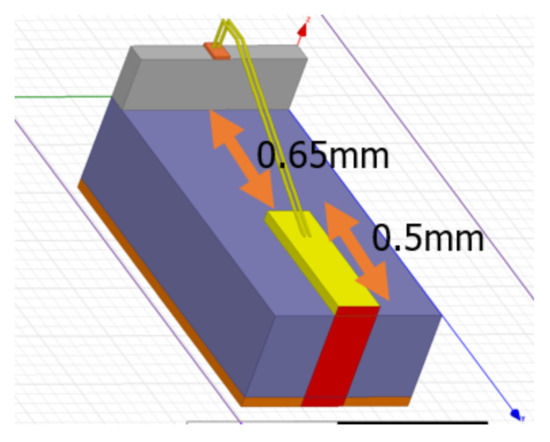

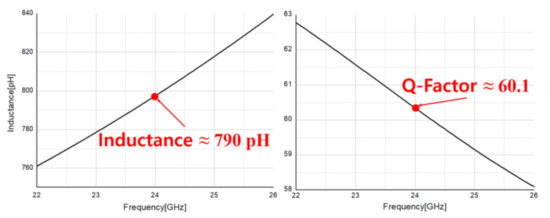

Figure 26 shows the modeling of the double bond wire carried out for connecting the transceiver pads to the connector port using a 3D EM-simulator, and Figure 27 shows the Q-factor and inductance of the modeled double bond wire. The Q-factor of bond wire was confirmed to be about 60 in the 24 GHz band, and the inductance was confirmed to be about 800 pH. The voltage and ground bond wires were modeled in the same way, and inductances of 1 nH and 700 pH were confirmed, respectively. In the meantime, in the circuit design stage, the design was carried out by considering the inductance of the bond wire to the RF input, output and all voltage sources. As the Q-factor and inductance of the bond wire have a great influence on the RF input and output of the IC, it is important to design it close to the ideal condition. Therefore, the length of the bond wire is reduced as much as possible and the Q-factor is designed as large as possible, so that it is designed close to the ideal inductor.

Figure 26.

3D modeled double bond wire.

Figure 27.

Simulated Q-factor and inductance of 3D modeled double bond wire.

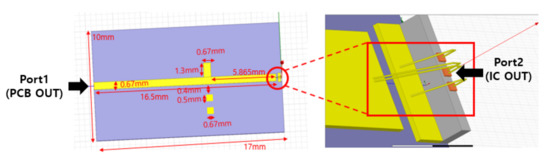

Figure 28 shows a stub circuit designed including bond wire for PCB fabrication. The signal pads we double wire bonded, and all stub circuits including wire bonding were modeled and applied to the IC to confirm the S-parameters. In addition, in order to prevent frequency shift due to errors in the actual manufacturing process, a pad that can be additionally wire-bonded to the stub circuit is designed so that the frequency can be changed appropriately.

Figure 28.

Wire bonding matching circuit applying stub circuit.

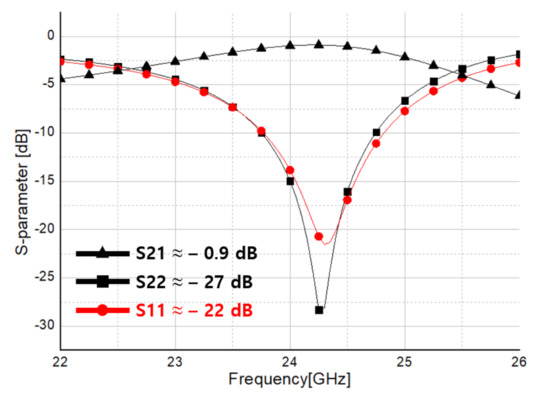

Figure 29 shows the simulation result of S-parameter of transceiver including stub circuit from port 1 and port 2 as seen in Figure 28. At 24.25 GHz, is −22 dB, is −27 dB, and is −0.9 dB, confirming that the circuit operates normally at 24 GHz. Considering the frequency shift according to parasitic capacitance and corner variation of the IC in the actual production stage, the working frequency was adjusted to 24.25 GHz in the design stage.

Figure 29.

RF Front-End S-parameter simulation result including stub circuit.

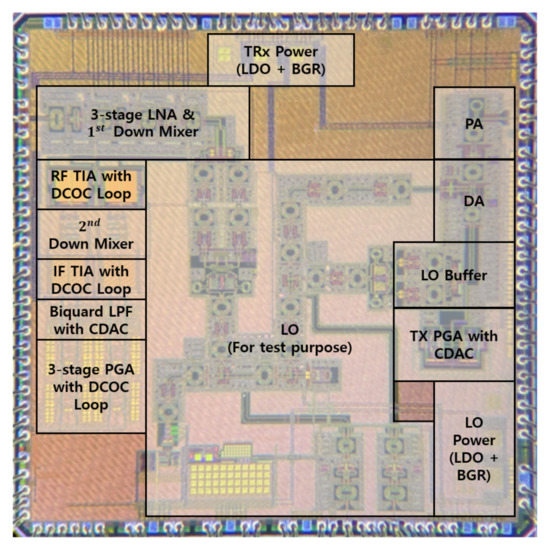

The transceiver for the CMOS multi-mode radar system was fabricated in a TSMC CMOS 65 nm process as shown in Figure 30, and the total area of the die takes up 3.54 mm × 3.54 mm including the test LO circuit. A 3.3 V supply voltage was used and the measurement was carried out after wire bonding the IC to the PCB.

Figure 30.

Transceiver die micrograph for RADAR System.

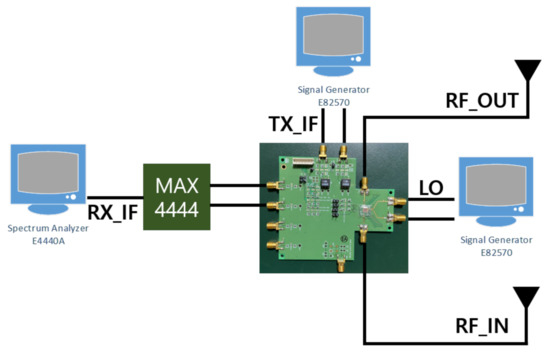

Figure 31 illustrates the fabricated PCB integrating the transceiver chip and radar test environment. The size of the manufactured PCB is 100 mm × 100 mm, the matching circuit of each transceiver was exposed to the side of the PCB, and the total length of the matching circuit was reduced to 17 mm.

Figure 31.

PCB and radar test environment.

4.3. Transceiver Measurement Results

4.3.1. Transmitter Measurement Results

For the transmitter measurement, the PGA gain of the baseband was set to 24 dB, and at the input frequency of 30 MHz, the input power of the I phase was set to −20 dBm, and the input power of the Q phase was also set to −20 dBm. LO power is also set to 10 dBm. The transmitter consumes about 86 mA of current.

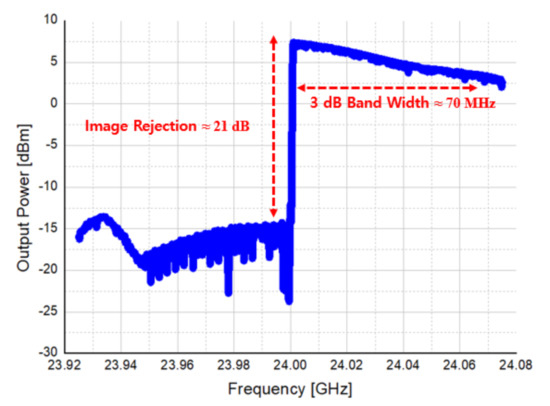

Figure 32 shows the measured frequency response of the transmitter. As it was designed by applying the direct conversion and the image rejection, the image rejection is confirmed about 21 dB, and the 3 dB bandwidth is measured 70 MHz.

Figure 32.

Measurement result of transmitter frequency response.

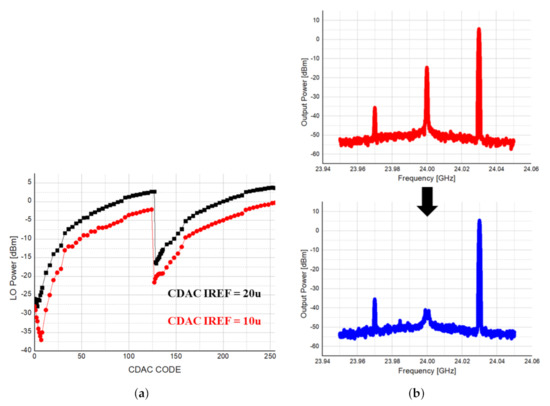

Figure 33a shows LO leakage according to 8-bit CDAC code. The optimal code was confirmed by adjusting the reference current of the CDAC to 20 A and 10 A, and Figure 33b is the result of the output spectrum of the transmitter by applying the optimal code. By optimizing the CDAC code, it was possible to suppress LO leakage of about 30 dB as expected.

Figure 33.

LO leakage power according to 8-bit CDAC code. (a) LO leakage according to 8-bit CDAC code; (b) the result of the output spectrum of the transmitter by applying the optimal code.

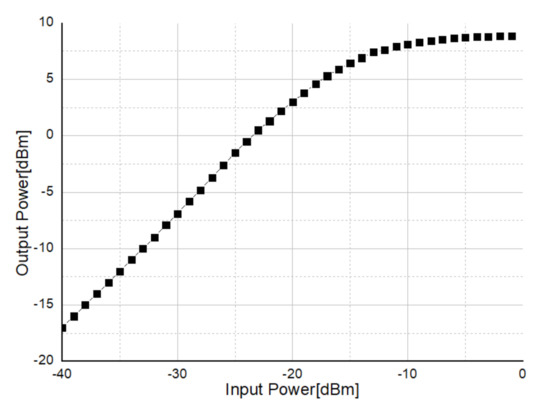

The measurement result of the maximum output power of the transmitter is shown in Figure 34. Through the measurement, a maximum output of 8.8 dBm was measured which is bit lower than simulation. The lower output power may be originated from the imperfect matching between DA and PA, and inaccurate bonding wire modeling.

Figure 34.

Measurement result of transmitter maximum output.

4.3.2. Receiver Measurement Results

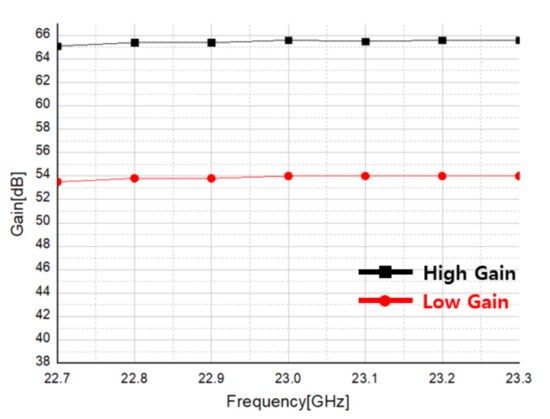

The receiver was measured by setting RF input power of −50 dBm and LO power of 5 dBm, and Figure 35 shows the result of measuring the bandwidth of the receiver. The black graph is the measurement result by setting the front-end and baseband of the receiver to the maximum gain of 66 dB, and the red graph is the measurement result by lowering the gain of the front-end by 10 dB. In both cases, a 3 dB bandwidth of 2 GHz was measured.

Figure 35.

Bandwidth measurement result of the proposed receiver.

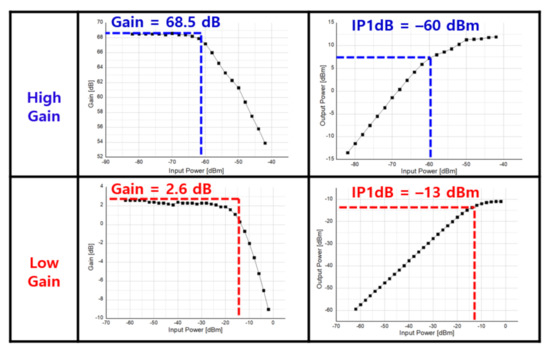

Figure 36 shows the P1dB measurement result of the receiver. In the high gain column of Figure 36, by setting the receiver gain to 68.5 dB, IP1dB of −60 dBm were obtained. In the low gain column of Figure 36, with the gain set to 2.6 dB, it is found that −13 dBm of IP1dB were measured.

Figure 36.

Receiver RF Front-End P1dB measurement result.

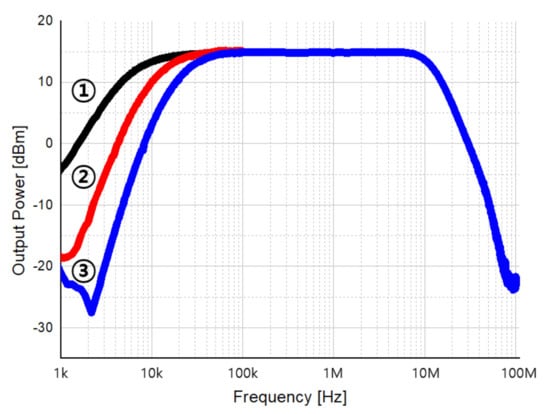

Figure 37 is the measured result the frequency response of HPF. In a radar system, as the received power decreases as the distance to the target increases, the decrease of the received power according to the distance must be compensated for through HPF. Therefore, the slope of HPF was set to a maximum of 40 dB/dec, and the measurement results according to turn on and off of a total of three DCOCs are shown. Graph ① is the measurement result with only the DCOC of RF TIA on, and shows the cut-off characteristic of 20 dB/dec and 10 kHz. In the graph ②, two DCOCs were turned on, and the cut-off characteristics of 30 dB/dec and 20 kHz were confirmed. Finally, graph ③ was measured with three DCOCs turned on, and showed cut-off characteristics of 40 dB/dec, 20 kHz, and it was confirmed that the Doppler frequency can be detected properly.

Figure 37.

Measurement result of high-pass filter frequency response. Graph ① is the measurement result with only the DCOC of RF TIA on, and shows the cut-off characteristic of 20 dB/dec and 10 kHz. In the graph ②, two DCOCs were turned on, and the cut-off characteristics of 30 dB/dec and 20 kHz were confirmed. Finally, graph ③ was measured with three DCOCs turned on, and showed cut-off characteristics of 40 dB/dec, 20 kHz, and it was confirmed that the Doppler frequency can be detected properly.

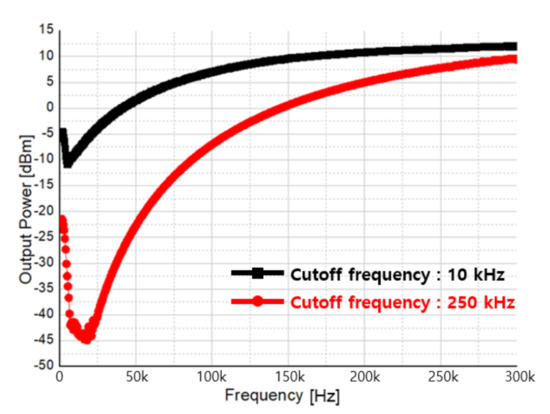

Figure 38 shows the measurement result by the cut-off frequency of DCOC, and it was confirmed that the cutoff frequency can be adjusted from a minimum of 10 kHz to a maximum of 250 kHz considering the CW and FMCW modes. Furthermore, DC rejection of up to 40 dB is confirmed as is Figure 38.

Figure 38.

Measurement result of DCOC cut-off control.

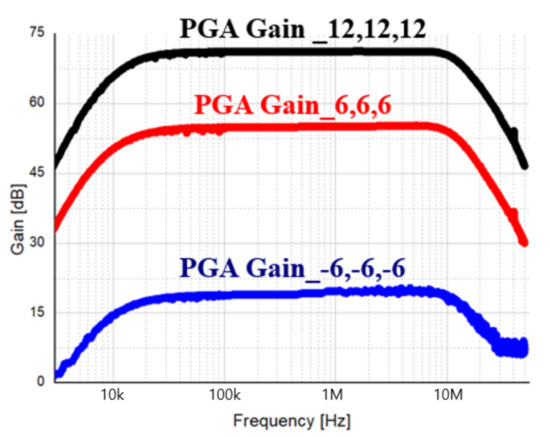

Figure 39 is measured result of the PGA gain of the receiver where the input power is −42 dBm, the LO frequency is 23 GHz, and the LO power is 5 dBm. At this time, the measurement was performed by setting the gain step of the PGA to 6 dB each. From the measurement results, a maximum gain of 68.5 dB was obtained.

Figure 39.

Measurement result of PGA gain of receiver.

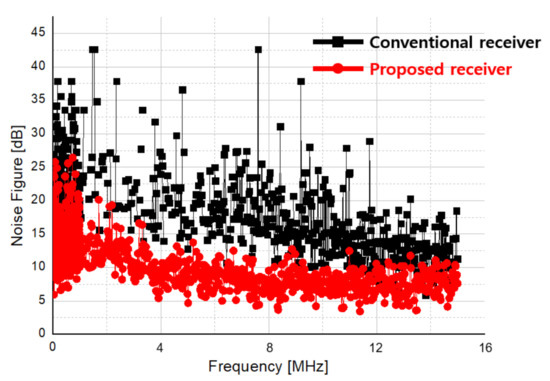

Figure 40 compares the noise figures of a direct conversion receiver and a proposed double conversion receiver. The black graph is the noise figure of the direct conversion receiver, and the red graph is that of the double conversion receiver. The proposed receiver provides an additional gain in the 2nd down mixer. By adding image rejection and DCOC loop, a lower noise figure compared to the direct conversion receiver at 100 Hz, which is vulnerable to flicker noise, was confirmed through measurement. From the measurement results, it is confirmed that the proposed double conversion at 15 MHz shows a lower noise figure.

Figure 40.

Noise figure result of conventional and proposed receivers.

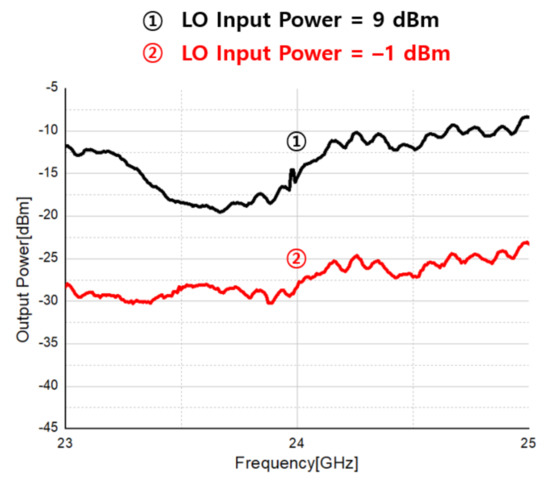

Figure 41 shows the receiver’s LO leakage measurement. The LO leakage of the receiver is measured with the LO power radiated to the input terminal of the receiver through the LNA by applying the LO input power to the 1st down mixer. When the LO input power is 9 dBm and −1 dBm, the LO leakage is measured as −16 dBm and −28 dBm, respectively.

Figure 41.

Measurement result of receiver LO leakage.

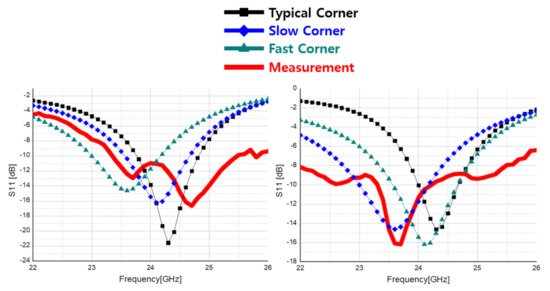

Figure 42 compares the measurement result of the transceiver’s S-parameter with the simulation. In the S-parameter simulation, after checking the output impedance by setting the corner variation of the transceiver to Slow, Fast, and Typical Corner, respectively, it was set as the input impedance of the matching circuit to confirm . The transmitter confirms of about −11 dB at 24 GHz, and the receiver confirms of about −10 dB at 24 GHz through simulation.

Figure 42.

measurement and comparison with simulation: transmitter (left), receiver (right).

4.4. Radar Test

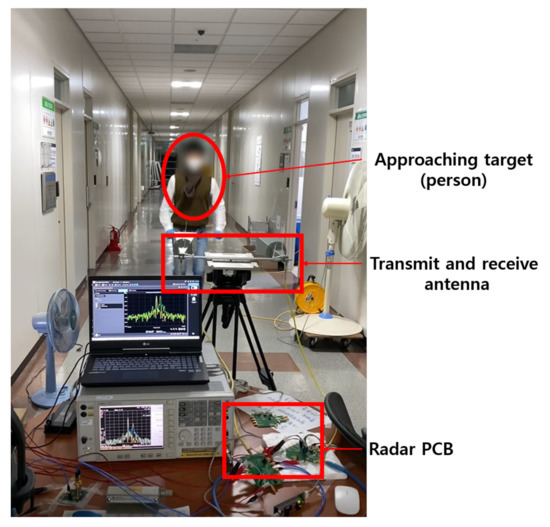

The fabricated test PCB with the proposed transceiver chip was used for radar test in multi-modes. Figure 43 shows the measurement environment for the proposed transceiver in a real radar test. The IF of the transmitter is set to 5 MHz, the LO frequency is set to 24 GHz, and the Doppler frequency or the beat frequency is received along with 24.005 GHz at the receiving end, and the measurement was performed by checking with a spectrum analyzer. A hum target is approached to check its movement. The Doppler frequency was measured using the CW mode and the speed of the target was calculated to confirm the measurement accuracy. In addition, the position of the target at rest was confirmed through the beat frequency using the FMCW mode.

Figure 43.

Measurement environment for radar test.

4.4.1. CW Mode

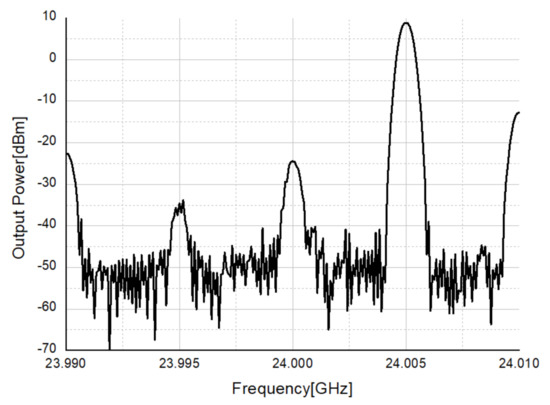

The transmitter’s IF is set to 5 MHz and the LO frequency is set to 24 GHz, so the output power of 8.8 dBm is measured at 24.005 GHz as shown in Figure 44. Before radiating the output power from the transmitter, the code of the CDAC was adjusted to find the code that suppresses LO leakage as much as possible. The LO leakage was set to −30 dBm or less and the signal power at 24.005 GHz was set to 8.8 dBm for radar test.

Figure 44.

Transmitter output power measurement in CW radar.

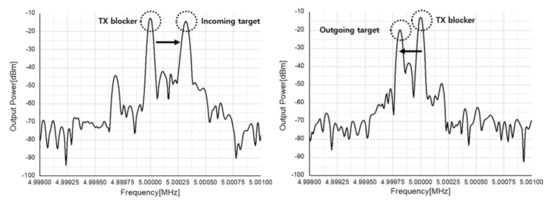

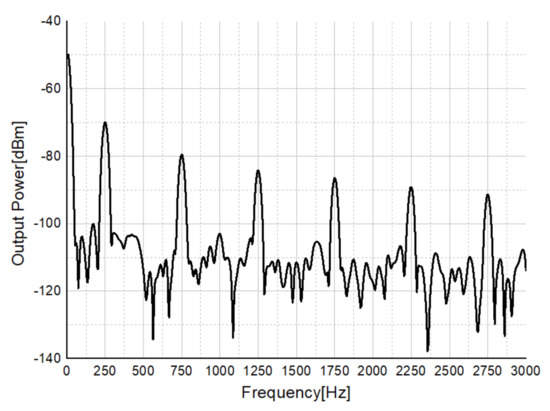

Figure 45 shows the measurement results of an incoming target and an outgoing target. It can be seen that the Doppler frequency rises by about 270 Hz for the incoming target, and the speed of the target is calculated from the Doppler frequency formula, which is 1.7 m/s. In addition, it can be seen that the Doppler frequency decreases by about 180 Hz for the target moving away, and the speed of the target is 1.13 m/s from the Doppler frequency formula. This is similar to people’s average walking speed of 1.4 m/s, so it can be seen that the CW mode works appropriately.

Figure 45.

Measurement result of incoming (left) and outgoing targets (right).

4.4.2. FMCW Mode

When measuring the FMCW mode radar, a large frequency modulation bandwidth and a short modulation time are required to ensure sufficient distance resolution. Therefore, the IF of the transmitter was modulated from 0 to 70 MHz with a time of 50 s, and the measurement was performed. The beat frequency against the distance was measured to check whether the FMCW mode operates properly.

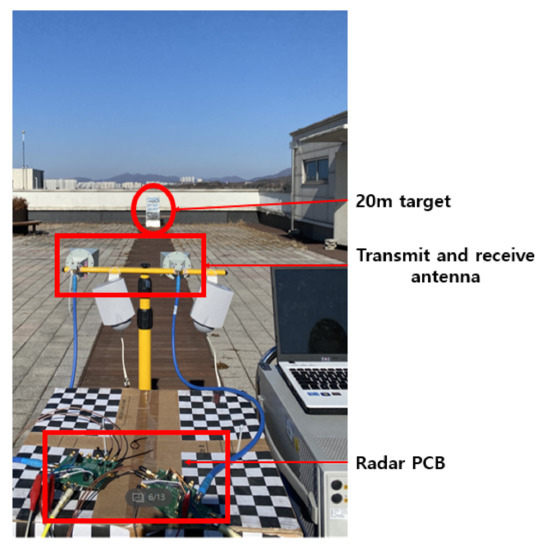

As FMCW mode can only use upstream frequency modulation in the current test environment as shown in Figure 46, speed information cannot be obtained, and a test was conducted to check the distance at which the target is located through the bit frequency according to the distance to the target. First aid kit made of steel with high RCS were placed at about 15 m and 20 m away to check the frequency on the spectrum and converted it into distance to confirm the operation of the FMCW mode.

Figure 46.

FMCW mode radar test environment.

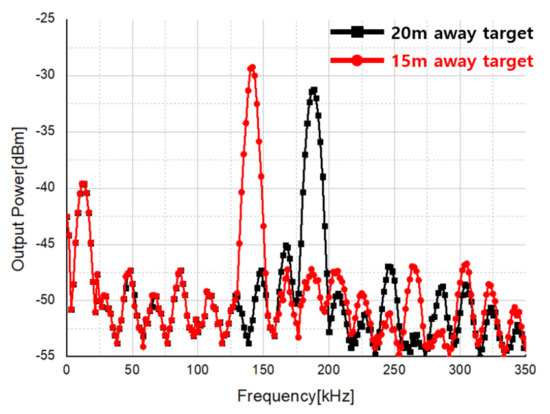

As a result of calculating the distance to the target by substituting the beat frequency of the stationary target into Equation (6), the calculated values of 15 m and 20 m were obtained when the beat frequency was 140 kHz and 186.67 kHz, respectively, as shown in Figure 47. Consistently, it was possible to confirm whether the FMCW mode also works properly.

Figure 47.

Measurement result of a stationary target using FMCW mode.

4.4.3. Pulse Mode

As in Section 2.1, the maximum detection distance varies according to the transmit power and pulse width. Therefore, in the pulse radar test, the square wave was confirmed by spectrum analyzer by appropriately adjusting the transmit power and the distance to the stationary target. Through this, it was confirmed whether the pulse radar operates properly.

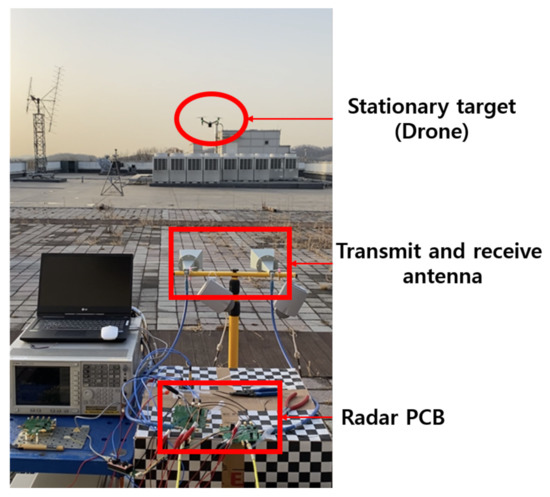

Figure 48 shows the pulse radar test environment. The square wave was confirmed through the spectrum analyzer by changing the distance while the drone was fixed at a constant height. When the duty cycle of the pulse is 50%, it appears as the sum of odd-order harmonics in the spectrum, so the measurement was performed by setting the transmit power to −20 dBm, the pulse width to 2 ms and pulse repetition frequency (PRF) to 250 Hz.

Figure 48.

Pulse mode radar test environment.

In Figure 49, it can be seen that odd-order harmonics of 250 Hz appear, and through this, it can be seen that the pulsed radar operates properly.

Figure 49.

Measurement result of a stationary target using pulse mode with a hovering drone.

Table 5 summarizes the measurement results of the proposed transceiver compared with other works. In particular, the direct conversion receiver was mainly compared, bypassing the 2nd down mixer of the proposed receiver. Finally, the radar test results are summarized in Table 6. The proposed radar transceiver is built in a test PCB to verity the multi-mode operation such as pulse, FMCW, and CW modes. If this transceiver is employed with radar signal processing system, more accurate operation for various mode radar can be evaluated precisely.

Table 5.

Summary and comparison of radar transceiver measurement results.

Table 6.

Summary of the radar test.

5. Conclusions

In this paper, we described the design and measurement of a transceiver for multi-mode radar and performed the radar test in pulse, FMCW, and CW modes. As the LO leakage occurs in the transmitter, the image rejection is applied and the DC offset generated in the baseband is removed by using an 8-bit current DAC (CDAC) of the baseband to suppress LO leakage. As a result, the result of LO leakage rejection of 37 dB was obtained at 24 GHz. In order to improve the flicker noise and the noise figure, the proposed receiver uses a double conversion structure to down-convert through an intermediate frequency where the influence of flicker noise is relatively small, and thereby reduce flicker noise. In addition, by applying the double quadrature structure, it improves a noise figure by 3 dB through image signal removal, and is designed to distinguish when the target is moving away or when it is moving closer. Finally, it is designed to have an isolation of about 30 dB in the middle frequency band by properly suppressing DC Offset that may occur due to LO leakage and TX blocker signals. As a result, it was possible to measure a noise figure of at least 12 dB at 100 kHz and 15 dB at 100 Hz, which was improved by 20 dB compared to that of about 35 dB in the direct conversion modes receiver.

Pulse, FMCW, and CW mode measurements were performed for radar tests, and the CW mode was used to detect the Doppler frequency incoming or outgoing targets. It succeeded in detecting the distance to the target, and it was possible to check whether the CW and FMCW mode radar operate properly.

Author Contributions

Conceptualization, Y.J.K. and C.S.C.; methodology, Y.J.K. and C.S.C.; validation, J.K.H. and Y.J.K.; formal analysis, Y.J.K. and C.S.C.; investigation, J.K.H.; resources, C.S.C.; data curation, J.K.H., C.K.N., H.J.K., Y.M.K., T.H.K., H.N.J., S.H.L. and J.S.L.; writing—original draft preparation, J.K.H.; writing—review and editing, C.S.C.; visualization, J.K.H.; supervision, C.S.C.; project administration, C.S.C.; funding acquisition, C.S.C. All authors have read and agreed to the published version of the manuscript.

Funding

This work was supported by Institute for Information & communications Technology Promotion (IITP) grant funded by the Korea government (MSIT) (No. 2017-0-00528, The Basic Research Lab for Intelligent Semiconductor Working for the Multi-Band Smart Radar).

Institutional Review Board Statement

Not applicable.

Informed Consent Statement

Not applicable.

Data Availability Statement

Data available on reasonable request from the corresponding author.

Conflicts of Interest

The authors declare no conflict of interest.

References

- Sanders, D.; Bingham, S.; Menon, G.; Crockett, D.; Tor, J.; Mende, R.; Behrens, M.; Jain, N.; Alexanian, A. A single-chip 24 GHz SiGe BiCMOS transceiver for FMCW automotive radars. In Proceedings of the 2009 IEEE Radio Frequency Integrated Circuits Symposium, Boston, MA, USA, 7–9 June 2009; pp. 425–428. [Google Scholar]

- Kim, S.K.; Cui, C.; Kim, B.S.; Kim, S. A Fully-Integrated Low Power K-band Radar Transceiver in 130nm CMOS Technology. J. Semicond. Technol. Sci. 2012, 12, 426–432. [Google Scholar] [CrossRef]

- Krishnaswamy, H.; Hashemi, H. A 4-channel 4-beam 24-to-26GHz spatio-temporal RAKE radar transceiver in 90nm CMOS for vehicular radar applications. In Proceedings of the 2010 IEEE International Solid-State Circuits Conference, San Franscisco, CA, USA, 7–11 February 2010; pp. 214–215. [Google Scholar]

- Gresham, I.; Jenkins, A.; Egri, R.; Eswarappa, C.; Kinayman, N.; Jain, N.; Anderson, R.; Kolak, F.; Wohlert, R.; Bawell, S.P.; et al. Ultra-wideband radar sensors for short-range vehicular applications. IEEE Trans. Microw. Theory Tech. 2004, 52, 2105–2122. [Google Scholar] [CrossRef]

- Pyo, G.; Yang, J.; Kim, C.Y.; Hong, S.C. K-Band Single-Path Dual-Mode CMOS Transmitter for FMCW/UWB Radar. IEEE Microw. Wirel. Components Lett. 2016, 26, 858–860. [Google Scholar] [CrossRef]

- Kim, S.; Kim, D.; Jin, Y.; Lee, J. Human Identification by Measuring Respiration Patterns Using Vital FMCW Radar. J. Electromagn. Eng. Sci. 2020, 20, 302–306. [Google Scholar] [CrossRef]

- Thomas H, L. The Design of CMOS Radio-Frequency Integrated Circuits, 2nd ed.; Cambidge University Press: New York, NY, USA, 2003; pp. 325–399. [Google Scholar]

- Razavi, B. RF Microelectronics, 2nd ed.; Pearson: Los Angeles, CA, USA, 2012; pp. 169–458. [Google Scholar]

- Palmers, P.; Steyaert, M.S.J. A 10–Bit 1.6-GS/s 27-mW Current-Steering D/A Converter With 550-MHz 54-dB SFDR Bandwidth in 130-nm CMOS. IEEE Trans. Circuits Syst. 2010, 57, 2870–2879. [Google Scholar] [CrossRef]

- Kim, J.Y.; Kim, Y.J.; Han, J.H.; Shin, J.H.; Cho, C.S. Newly Proposed Duty-Generator-Less Passive DownConversion Mixer. J. Semicond. Technol. Sci. 2019, 19, 426–433. [Google Scholar] [CrossRef]

- Lee, J.S.; Jeong, C.J.; Jang, Y.S.; Lee, I.Y.; Lee, S.S.; Han, S.K.; Lee, S.G. A high linear low flicker noise 25% duty cycle LO I/Q mixer for a FM radio receiver. In Proceedings of the 2011 IEEE International Symposium of Circuits and Systems (ISCAS), Rio de Janeiro, Brazil, 15–18 May 2011; pp. 1399–1402. [Google Scholar]

- Poobuapheun, N.; Chen, W.H.; Boos, Z.; Niknejad, A.M. A 1.5-V 0.7–2.5-GHz CMOS Quadrature Demodulator for Multiband Direct-Conversion Receivers. IEEE J. Solid State Circuits 2007, 42, 1669–1677. [Google Scholar] [CrossRef]

- Choi, W.H.; Song, W.H.; Lee, W.J. Broadband Radar Absorbing Structures with a Practical Approach from Design to Fabrication. J. Electromagn. Eng. Sci. 2020, 20, 254–261. [Google Scholar] [CrossRef]

- Ha, K.W.; Lee, J.Y.; Ko, G.H.; Kim, Y.J.; Kim, J.G.; Baek, D. Fully Integrated Dual-Mode X-Band Radar Transceiver Using Configurable Receiver and Local Oscillator. IEEE Access 2020, 8, 151403–151414. [Google Scholar] [CrossRef]

- Lee, J.; Li, Y.A.; Hung, M.H.; Huang, S.J. A Fully-Integrated 77-GHz FMCW Radar Transceiver in 65-nm CMOS Technology. IEEE J. Solid State Circuits 2010, 45, 2746–2756. [Google Scholar] [CrossRef]

- Richards, M.A.; Scheer, J.A.; Holm, W.A. Principles of Modern Radar: Basic Principles, 1st ed.; Scitech: New York, NY, USA, 2010; pp. 17–249. [Google Scholar]

- Rahman, S.; Robertson, A.D. In-flight RCS measurements of drones and birds at K-band and W-band. IET Radar Sonar Navig. 2019, 13, 300–309. [Google Scholar] [CrossRef]

- Razavi, B. Design Of Analog Cmos Integrated Circuit, 2nd ed.; MC GRAW HILL Education: New York, NY, USA, 2016; pp. 344–390. [Google Scholar]

- Park, J.; Kang, S.; Hong, S. Design of a Ka-Band Cascode Power Amplifier Linearized With Cold-FET Interstage Matching Network. IEEE Trans. Microw. Theory Tech. 2020, 69, 1429–1438. [Google Scholar]

- Ahn, H.; Back, S.; Nam, I.; An, D.; Lee, J.; Jeong, M.; Kim, B.E.; Lee, Y.T.; Kim, H.T.; Ho, Y.C.; et al. A Fully Integrated -32-dB EVM Broadband 802.11abgn/ac PA With an External PA Driver in WLP 40-nm CMOS. IEEE Trans. Microw. Theory Tech. 2019, 67, 1870–1882. [Google Scholar] [CrossRef]

- Manstretta, D.; Castello, R.; Gatta, F.; Rossi, P.; Svelto, F. A 018µm CMOS directconversion receiver front-end for UMTS. In Proceedings of the 2002 IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 7 February 2002; pp. 240–241. [Google Scholar]

- Wang, S.; Tsai, K.H.; Huang, K.K.; Li, S.X.; Wu, H.S.; Tzuang, C.K.C. Design of X-Band RF CMOS Transceiver for FMCW Monopulse Radar. IEEE Trans. Microw. Theory Tech. 2008, 57, 61–70. [Google Scholar] [CrossRef]

- Kim, Y.; Han, J.; Lee, J.S.; Jin, T.; Jang, P.; Shin, H.; Lee, J.; Cho, T.B. Power-Efficient CMOS Cellular RF Receivers for Carrier Aggregation According to RF Front-End Configuration. IEEE Trans. Microw. Theory Tech. 2020, 69, 452–468. [Google Scholar] [CrossRef]

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).