THz CMOS On-Chip Antenna Array Using Defected Ground Structure

Abstract

1. Introduction

2. Design of THz CMOS On-Chip Antenna Array

2.1. THz CMOS On-Chip Antenna Element

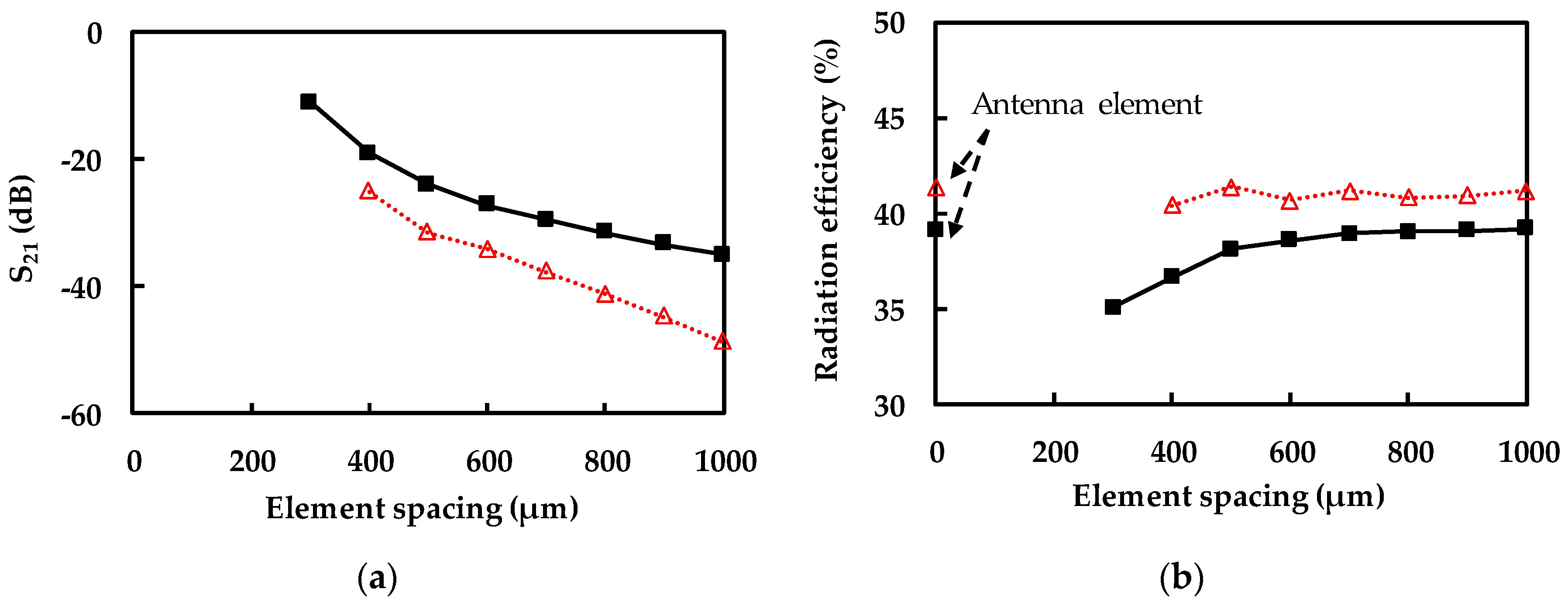

2.2. THz CMOS On-Chip Array

2.3. Simulation Results

3. Experimental Results

3.1. Reflection Coefficient

3.2. Antenna Gain

3.3. Radiation Pattern

4. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Marchese, L.E.; Terroux, M.; Bolduc, M.; Cantin, M.; Desnoyers, N.; Bergeron, A. A 0.1 megapixel THz camera with 17-degree field of view for large area single shot imaging. In Proceedings of the 2014 39th International Conference on Infrared, Millimeter, and Terahertz waves (IRMMW-THz), Tuicson, AZ, USA, 14–19 September 2014; pp. 1–2. [Google Scholar] [CrossRef]

- Kašalynas, I.; Venckevičius, R.; Minkevičius, L.; Wahaia, F.; Janonis, V.; Tamošiônas, V.; Valušis, D.; Valušis, G.; Sešek, A.; Trontelj, J.; et al. High spatial resolution terahertz imaging of carcinoma tissues at 0.6 THz frequencies. In Proceedings of the 2016 41st International Conference on Infrared, Millimeter, and Terahertz Waves (IRMMW-THz), Copenhagen, Denmark, 25–30 September 2016; pp. 1–2. [Google Scholar] [CrossRef]

- Seok, E.; Shim, D.; Mao, C.; Han, R.; Sankaran, S.; Cao, C.; Knap, W. Progress and Challenges Towards Terahertz CMOS Integrated Circuits. IEEE J. Solid-State Circuits 2010, 45, 1554–1564. [Google Scholar] [CrossRef]

- Hu, S.; Xiong, Y.Z.; Zhang, B.; Wang, L.; Lim, T.G.; Je, M.; Madihian, M. A SiGe BiCMOS Transmitter/Receiver Chipset With On-Chip SIW Antennas for Terahertz Applications. IEEE J. Solid-State Circuits 2012, 47, 2654–2664. [Google Scholar] [CrossRef]

- Sherry, H.; Hadi, R.A.; Grzyb, J.; Öjefors, E.; Chthelina, A.; Kaiser, A.; Pfeiffer, U.R. Lens-integrated THz imaging arrays in 65-nm CMOS technologies. In Proceedings of the IEEE Radio Frequency Integrated Circuits Symposium (RFIC), Baltimore, MD, USA, 5–7 June 2011; pp. 365–368. [Google Scholar] [CrossRef]

- Grzyb, J.; Zhao, Y.; Pfeiffer, U.R. A 288-GHz Lens-Integrated Balanced Triple-Push Source in a 65-nm CMOS Technology. IEEE J. Solid-State Circuits 2013, 48, 1751–1761. [Google Scholar] [CrossRef]

- Babakhani, A.; Rutledge, D.B.; Hajimiri, A. mm-wave phased arrays in silicon with integrated antennas. In Proceedings of the IEEE Antennas Propag. Int. Symp., Honolulu, HI, USA, 9–15 June 2007; pp. 4369–4372. [Google Scholar] [CrossRef]

- Schmalz, K.; Borngraber, J.; Debski, W.; Elkhouly, M.; Wang, R.; Neumaier, P.F.; Kissinger, D.; Hubers, H. 245-GHz Transmitter Array in SiGe BiCMOS for Gas Spectroscopy. IEEE Trans. Terahertz Sci. Technol. 2016, 6, 318–327. [Google Scholar] [CrossRef]

- Tajima, T.; Song, H.J.; Yaita, M. Compact THz LTCC Receiver Module for 300 GHz Wireless Communications. IEEE Microw. Wirel. Compon. Lett. 2016, 26, 291–293. [Google Scholar] [CrossRef]

- Deng, X.D.; Li, Y.; Liu, C.; Wu, W.; Xiong, Y.Z. 340 GHz On-Chip 3-D Antenna With 10 dBi Gain and 80% Radiation Efficiency. IEEE Trans. Terahertz Sci. Technol. 2015, 5, 619–627. [Google Scholar] [CrossRef]

- Kim, H.; Choe, W.; Jeong, J. A Terahertz CMOS V-Shaped Patch Antennas with Defected Ground Structure. Sensors 2018, 18, 2432. [Google Scholar] [CrossRef] [PubMed]

- Han, R.; Afshari, E. A CMOS High-Power Broadband 260-GHz Radiator Array for Spectroscopy. IEEE J. Solid-State Circuits 2013, 48, 3090–3104. [Google Scholar] [CrossRef]

- Balanis, C.A. Antenna Theory: Analysis and Design, 4th ed.; Wiley: New York, NY, USA, 2016. [Google Scholar]

- Pozar, D.M. Surface wave effects for millimeter wave printed antennas. In Proceedings of the 1983 Antennas and Propagation Society Int. Symp., Houston, TX, USA, 23–26 May 1983; pp. 692–695. [Google Scholar] [CrossRef]

- Yoon, S.J.; Choi, J. A Low-Profile Broadband Array Antenna for Home Repeater Applications. J. Electromagn. Eng. Sci. 2018, 18, 261–266. [Google Scholar] [CrossRef]

- Kothapudi, V.K.; Kumar, V. SFCFOS Uniform and Chebyshev Amplitude Distribution Linear Array Antenna for K-Band Applications. J. Electromagn. Eng. Sci. 2019, 19, 64–70. [Google Scholar] [CrossRef]

- Kang, J.S.; Kim, J.H.; Park, J.I. Comparison of antennas parameters of R-/S-band standard gain antennas. In Proceedings of the 2015 International Workshop on Antenna Technology (iWAT), Seoul, Korea, 4–6 March 2015; pp. 369–371. [Google Scholar] [CrossRef]

- Li, C.H.; Chiu, T.Y. 340-GHz Low-Cost and High-Gain On-Chip Higher Order Mode Dielectric Resonator Antenna for THz Applications. IEEE Trans. Terahertz Sci. Technol. 2017, 7, 284–294. [Google Scholar] [CrossRef]

| Wp | Lp | WPR | LPR | GPR | WDGS | LDGS | GDGS | GM |

|---|---|---|---|---|---|---|---|---|

| 250 | 200 | 60 | 180 | 10 | 90 | 85 | 20 | 60 |

| Reference | Antenna Type | Process | Frequency (GHz) | Bandwidth (%) | Gain (dBi) | Size (mm2) | Additional Process |

|---|---|---|---|---|---|---|---|

| [6] | Dipole (single) | 65 nm CMOS | 288 | n.a. | 18.3 * | 0.29 × 0.29 | Lens |

| [8] | Dipole (1 × 4 array) | 180 nm BiCMOS | 245 | 16.3 * | 11.0 ** | 3.7 × 5.4(with IC) | LBE 1 |

| [12] | Patch (single) | 130 nm CMOS | 340 | n.a. | 3.3 * | n.a. | none |

| 12.0 | 10.0 | 0.8 × 0.9 | DR 2 | ||||

| [18] | Patch (single) | 180 nm CMOS | 341 | 7.0 * | 7.9 * | 0.4 × 0.3 | DR |

| This work | Patch (element) | 65 nm CMOS | 300 | 14.0 | 3.1 | 0.23 × 0.42 | none |

| Patch (1 × 2 array) | 21.3 | 7.2 | 0.30 × 0.92 | ||||

| Patch ( 2× 2 array) | 28.0 | 8.2 | 0.92 × 0.79 |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Lee, C.; Jeong, J. THz CMOS On-Chip Antenna Array Using Defected Ground Structure. Electronics 2020, 9, 1137. https://doi.org/10.3390/electronics9071137

Lee C, Jeong J. THz CMOS On-Chip Antenna Array Using Defected Ground Structure. Electronics. 2020; 9(7):1137. https://doi.org/10.3390/electronics9071137

Chicago/Turabian StyleLee, Changmin, and Jinho Jeong. 2020. "THz CMOS On-Chip Antenna Array Using Defected Ground Structure" Electronics 9, no. 7: 1137. https://doi.org/10.3390/electronics9071137

APA StyleLee, C., & Jeong, J. (2020). THz CMOS On-Chip Antenna Array Using Defected Ground Structure. Electronics, 9(7), 1137. https://doi.org/10.3390/electronics9071137