A Highly Stabilized Current Source Topology with Slope Compensation for a High-Power Microwave Guiding Coil

Abstract

1. Introduction

- (a).

- Peak current: 3∼5 kA;

- (b).

- Rising/falling edge duration: <5 ms (to minimize Joule heating and ensure high repetition rates);

- (c).

- Flat-top duration: ∼20 ms (non-critical);

- (d).

- Current stability/accuracy: ≤1000 ppm.

- (a).

- City grid + rectifier: Unacceptable grid harmonics and ripple (15%).

- (b).

- Pulse generator + rectifier: Prohibitively high cost, limited stability (5000 ppm) and slow current rise (>100 ms).

- (c).

- Battery bank: Slow current rise (>100 ms) due to electrochemical inertia.

- (d).

- Capacitor bank in the form of an optimized SFPFN: Fast current rise rate (<2 ms rise time) but slow fall rate (>10 ms) and unacceptably high ripple ().

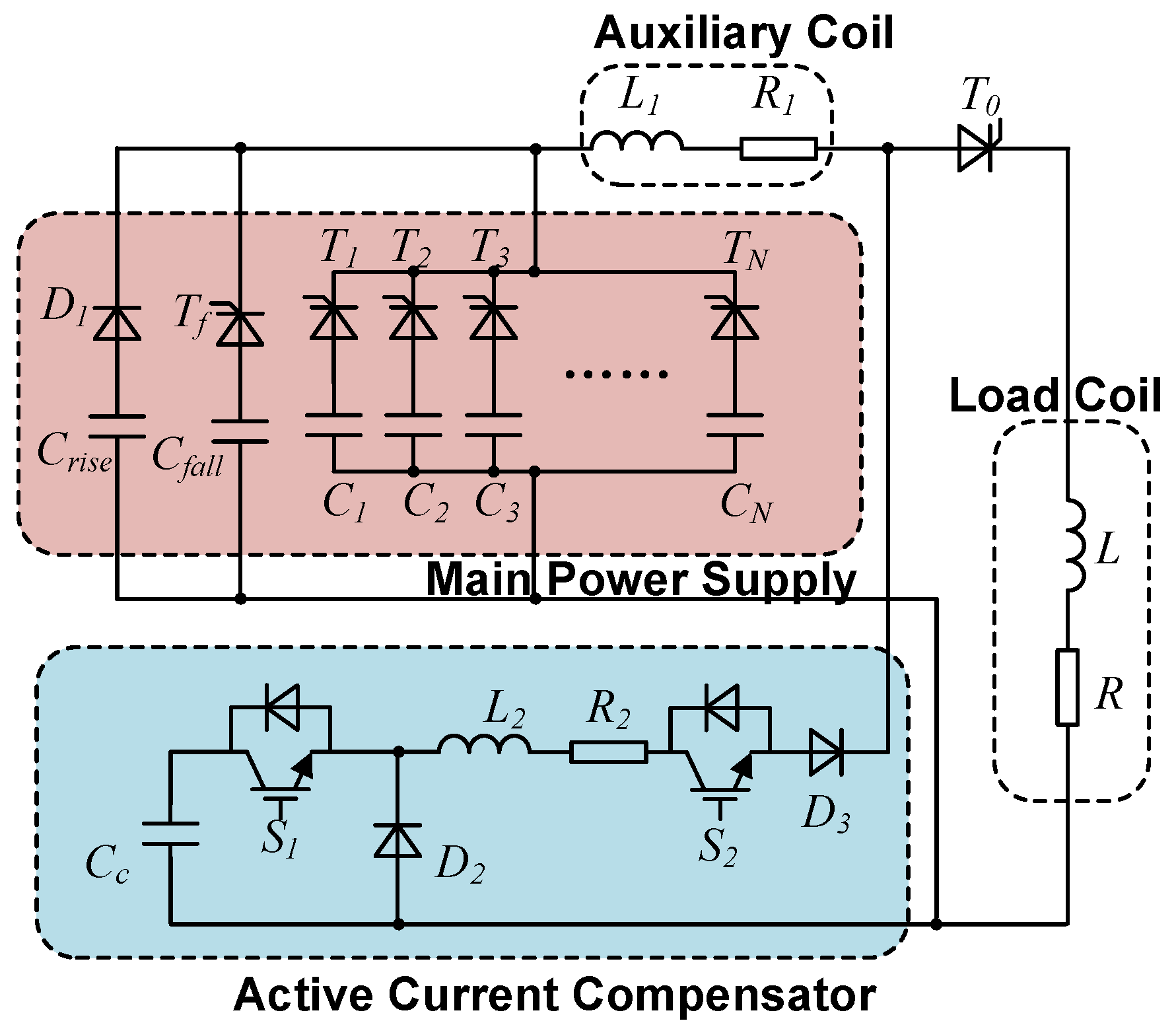

2. Proposed Current Source Topoplogy Based on an Optimized SFPFN

2.1. Original Optimized SFPFN with Open-Loop Control Scheme

2.2. Proposed Topology

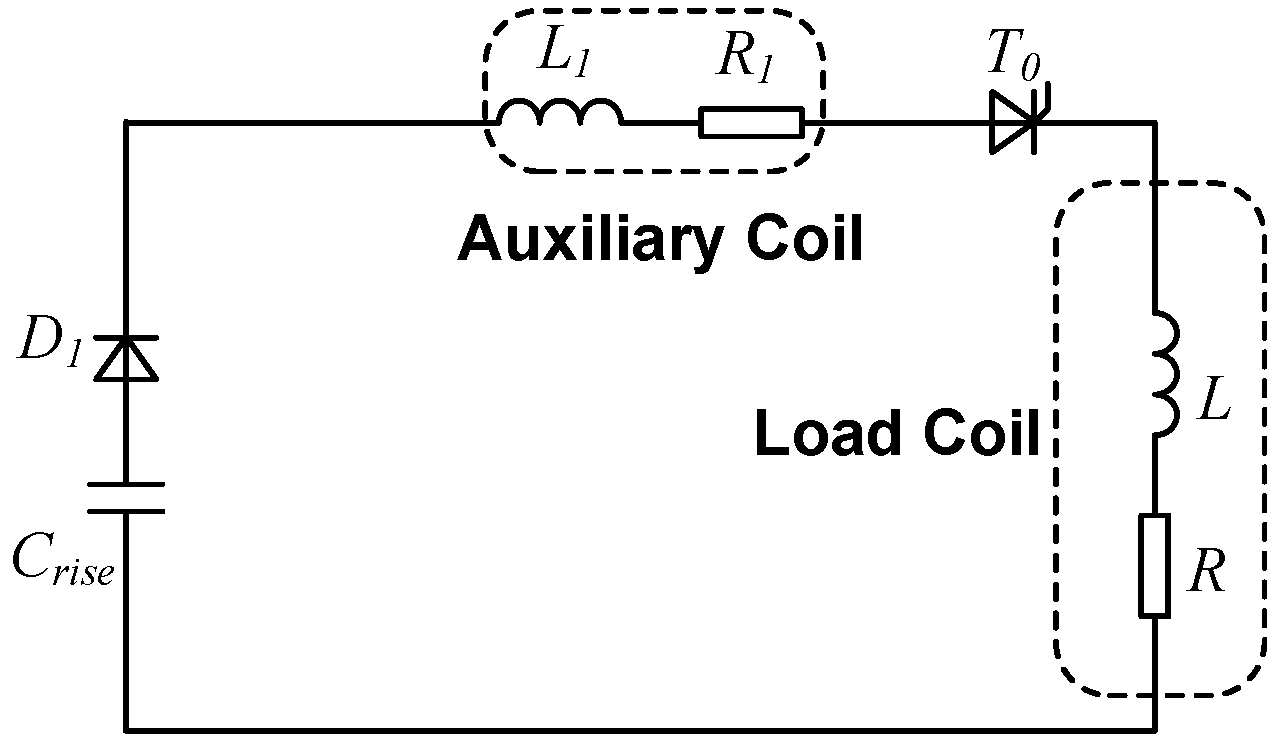

2.2.1. Mode 1: Rise Mode

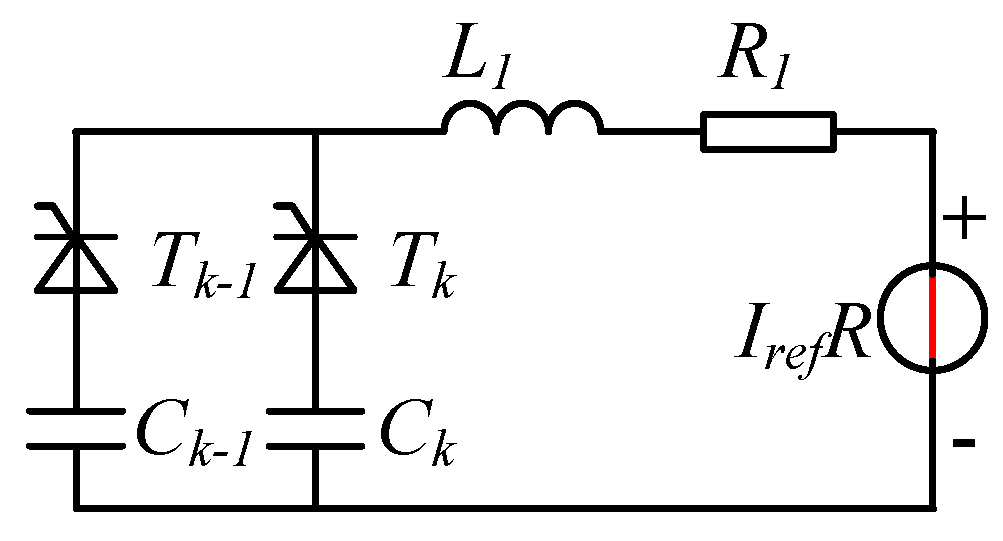

2.2.2. Mode 2: Flat-Top Mode

2.2.3. Mode 3: Fall Mode

3. Parameter Design and Controller Design

3.1. Ripple of the Output Current of the ACC

3.2. Parameter Design for the Topology

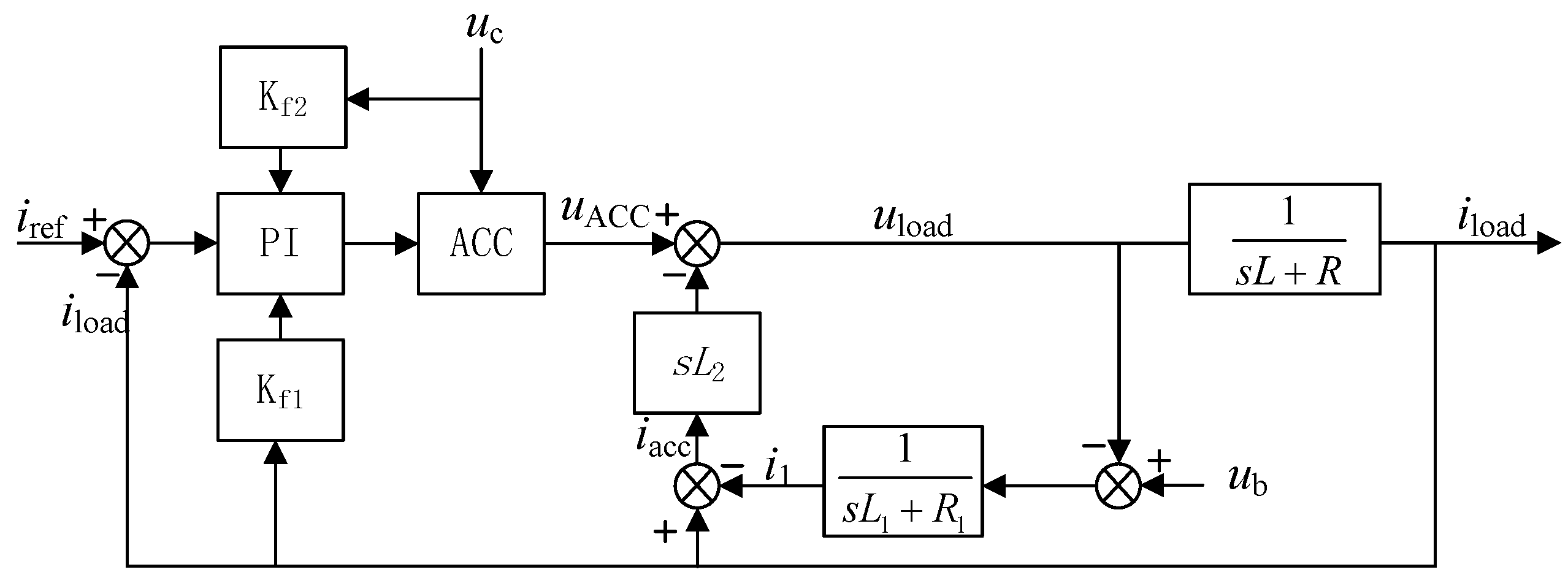

3.3. Controller Design with Slope Compensation

4. Simulation Results

4.1. The Optimized SFPFN

4.2. The Proposed Topology

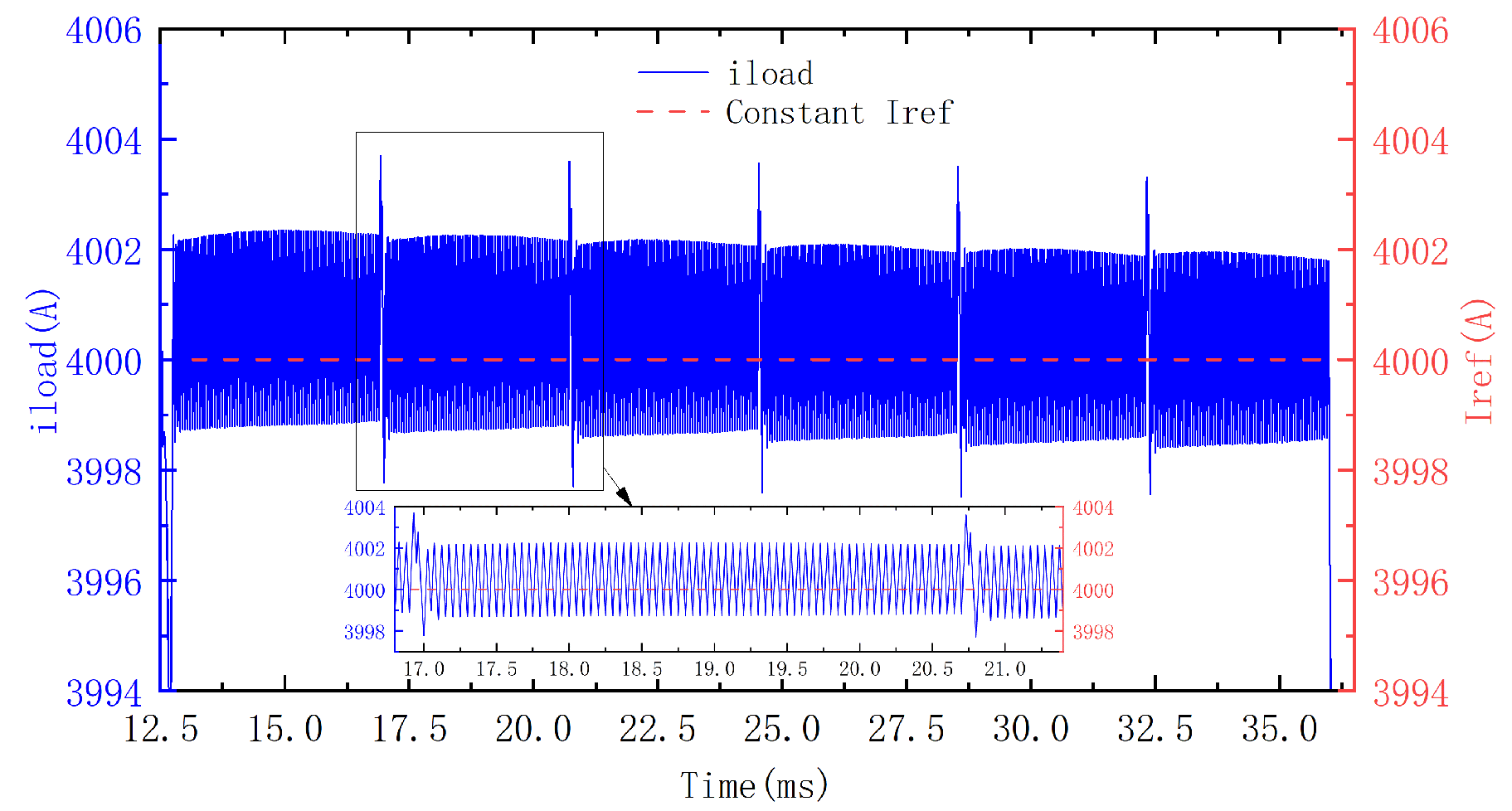

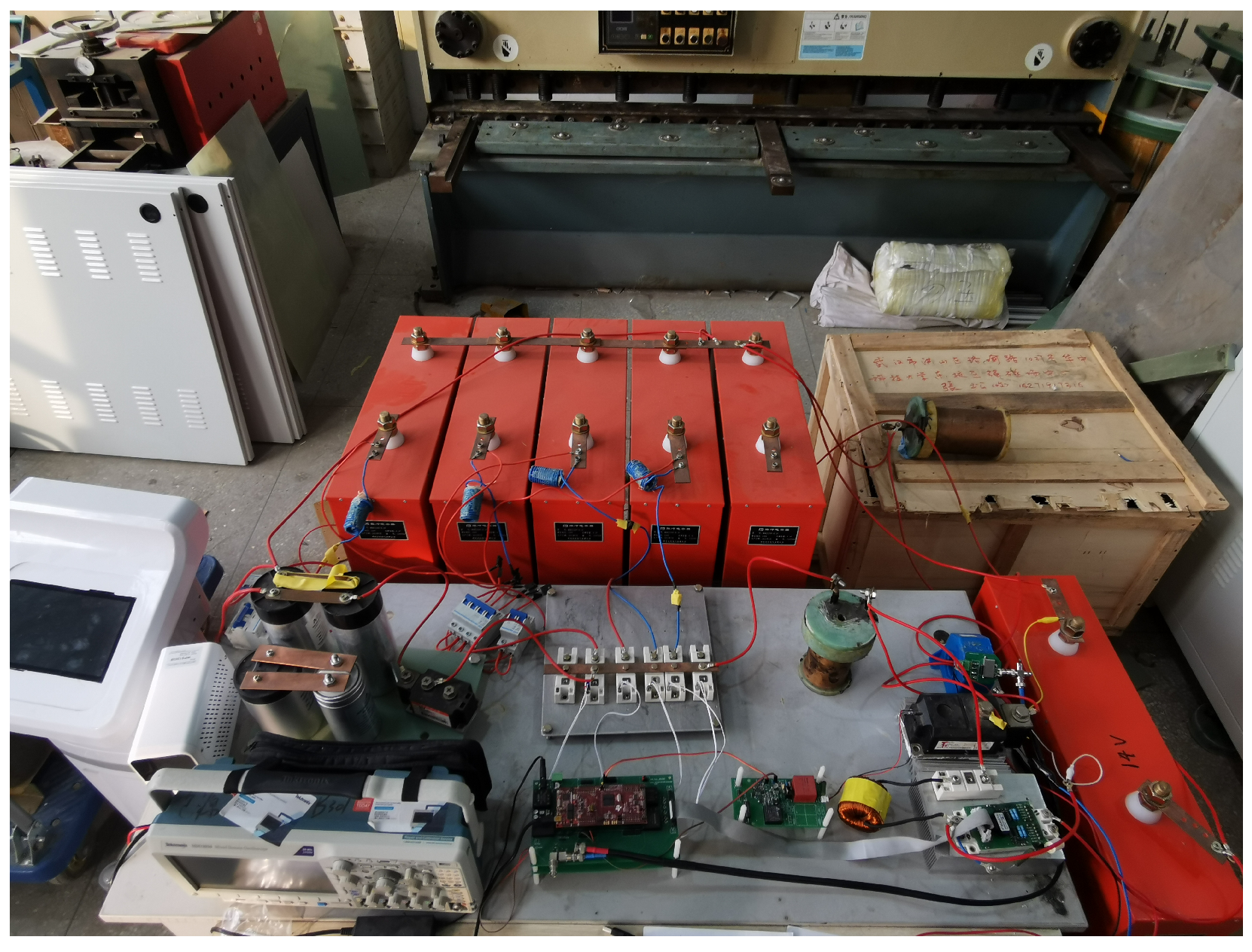

5. Experiment Results

6. Discussion

- (a).

- High-frequency switching devices, including the switches in the main circuit and components in the switching power supply on the PCB board, which generate EMI during their operation;

- (b).

- Pulse transformers on the switching driver board, contributing additional EMI;

- (c).

- Rapid magnetic field changes caused by the fast rise and fast fall of load coil currents.

- (a).

- Advanced Control Strategies: We aim to develop hybrid control architectures combining model predictive control (MPC) and AI-based ripple cancellation to achieve sub-100 ppm stability for precision applications like quantum magnetometry.

- (b).

- Wide-Bandgap Semiconductor Integration: We aim to replace silicon-based IGBTs with GaN/SiC MOSFETs to enable sub-100 ns switching and reduce switching losses, while characterizing trade-offs between device ruggedness and high di/dt capability.

- (c).

- AI-Driven Lifetime Prediction: We aim to use digital twins and federated learning to predict component lifetimes and enable proactive maintenance, addressing capacitor aging and contact erosion in high-current pulsing.

7. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Chandra, R.; Sharma, V.; Singh, S.K.; Kalyanasundaram, S.; Mitra, S.; Patel, A.; Mondal, J.; Roy, A.; Sharma, A. Design and Operation of Gigawatt Level RBWO Device for HPM Generation in S-band Frequency. In Proceedings of the 2023 First International Conference on Microwave, Antenna and Communication (MAC), Prayagraj, India, 24–26 March 2023; pp. 1–5. [Google Scholar]

- Wang, D.; Teng, Y.; Li, S.; Chen, C.; Liu, W.; Su, J.; Zhang, L.; Cheng, J.; Du, Z.; Gao, L. Pulse Lengthening of the Microwave Generated by TM02 Mode Ka-Band RBWO Operating With Low Guiding Magnetic Field. IEEE Trans. Electron Devices 2021, 68, 3015–3020. [Google Scholar] [CrossRef]

- Xiao, R.; Chen, K.; Wang, H.; Wang, D.; Shi, Y.; Gao, L. Theoretical calculation and particle-in-cell simulation of a multi-mode relativistic backward wave oscillator operating at low magnetic field. Phys. Plasmas 2022, 29, 29. [Google Scholar] [CrossRef]

- Yang, C.; Wang, H.; Meng, J.; Deng, B. The Method of Reducing the Guiding Magnetic Field of High-Band O-Type High-Power Microwave Generator. IEEE Trans. Plasma Sci. 2023, 51, 1900–1904. [Google Scholar] [CrossRef]

- Takahashi, M.; Kikuchi, S.; Inoue, N.; Sakai, N.; Murakami, M.; Yokoyama, K.; Oka, T.; Nakamura, T. NMR Relaxometry Using Outer Field of Single-Sided HTS Bulk Magnet Activated by Pulsed Field. IEEE Trans. Appl. Supercond. 2022, 32, 4602404. [Google Scholar] [CrossRef]

- Tu, P.; Ding, H.; Zhang, D.; Zhang, Z.; He, Z. A Novel Design of Multilevel Repetitive Pulse Magnetic Field System. In The Proceedings of 2023 International Conference on Wireless Power Transfer (ICWPT2023), Weihai, China, 13–15 October 2023; Springer: Singapore, 2023; Volume 1161, pp. 412–425. [Google Scholar]

- Singh, A.P.; Gopal, K.; Goswami, Y.; Kundu, M.; Varshney, P. Terahertz field generation from laser interaction with spherical nano-particles: Effect of external magnetic field. Opt. Quant. Electron. 2024, 56, 199. [Google Scholar] [CrossRef]

- Lelekhov, S.A.; Sytnikov, V.E. Conductor Design for Toroidal Field Coils of a High Magnetic Field Tokamak TRT20. IEEE Trans. Appl. Supercond. 2022, 24, 4201805. [Google Scholar] [CrossRef]

- Grössinger, R.; Schönhart, M.; Kriegisch, M.; Haas, M.; Sassik, H. High Field Facilities at TU Vienna. J. Low Temp. Phys. 2010, 159, 394–401. [Google Scholar] [CrossRef]

- Ding, H.; Hu, J.; Liu, W.; Xu, Y.; Jiang, C.; Ding, T. Design of a 135 MW Power Supply for a 50 T Pulsed Magnet. IEEE Trans. Appl. Supercond. 2012, 22, 5400504. [Google Scholar] [CrossRef]

- Zhang, S.; Wang, Z.; Ding, T.; Xiao, H.; Xie, J.; Han, X. Realization of High-Stability Flat-Top Pulsed Magnetic Fields by a Bypass Circuit of IGBTs in the Active Region. IEEE Trans. Power Electron. 2020, 35, 2436–2444. [Google Scholar] [CrossRef]

- Ling, P.E.W.; Mao, A.; Guan, J.; Ma, X.; Li, H.; Yu, Z.; Ding, M. A Pulsed Power Supply Based on an Optimized SFPFN Scheme Producing Large Currents With a Flat Top on a Heavily Inductive Load. IEEE Trans. Power Electron. 2021, 36, 11221–11233. [Google Scholar]

- Zhou, Y.; Huang, J.; Wang, S.; Jiang, W.; Chen, J. Principle of designing slope compensation in PFC Boost converter. Sci. China Ser. F Inf. Sci. 2009, 52, 2226–2233. [Google Scholar] [CrossRef]

- Aroudi, A.E.; Mandal, K.; Al-Numay, M.S.; Giaouris, D.; Banerjee, S. Piecewise Quadratic Slope Compensation Technique for DC-DC Switching Converters. IEEE Trans. Circuits Syst. I Regul. Pap. 2020, 67, 5574–5585. [Google Scholar] [CrossRef]

| Power Supply | Load | Peak | Duration | Rise Time | Fall Time | Stability | Application | [Ref.] |

|---|---|---|---|---|---|---|---|---|

| City power grid with a rectifier | N/A | 13 kA | 1000 ms | >1 s | >1 s | >15% | N/A | [9] |

| Pulse generator with a rectifier | 48.5 mH | 25 kA | 100 ms | 770 ms | >1 s | 5000 ppm | N/A | [10] |

| Battery bank with a bypass circuit | 8 mH | 30 kA | 100 ms | >100 ms | >100 ms | 65 ppm | Terahertz | [11] |

| Capacitor bank in the form of an SFPFN | 40 μH | 26 kA | 12 ms | ∼2 ms | >10 ms | >15% | Pulsed magnetic window | [12] |

| The proposed topology | 1 mH | 4 kA | 20 ms | ∼4 ms | ∼4 ms | 1000 ppm | HPM Source | N/A |

| Parameter | Value Range |

|---|---|

| Peak magnetic flux density | 2–3.7 T |

| Peak load current | 3–5 kA |

| Load coil inductance | 1–5 mH |

| Load coil resistance | 100–250 mΩ |

| Flat-top duration | 15–20 ms |

| Rising time | <5 ms |

| Falling time | <5 ms |

| Precision | <1000 ppm |

| Stability | <1000 ppm |

| Parameters | Symbol | Value |

|---|---|---|

| Auxiliary coil inductance | 1.2 mH | |

| Auxiliary coil resistance | 112 mΩ | |

| ACC inductor inductance | 4 mH | |

| Capacitance of one branch from the capacitor bank | 100 mF | |

| Discharge interval of the capacitor bank | 4 ms | |

| Number of branches of the capacitor bank | N | 6 |

| ACC bus capacitor | 100 mF | |

| Rise mode capacitor | 1200 μF | |

| Fall mode capacitor | 80 μF | |

| ACC Switching frequency | 20 kHz | |

| Initial voltage of one branch from the capacitor bank | 957 V | |

| Initial voltage of the rise mode capacitor | 6100 V | |

| Initial voltage of the fall mode capacitor | 4000 V | |

| Initial voltage of the ACC bus capacitor | 680 V |

| Parameters | Symbol | Value |

|---|---|---|

| Pulse-forming inductor | 1.2 mH | |

| Number of branches of the capacitor bank | N | 6 |

| Capacitance of the first capacitor | 36 mF | |

| Discharge interval of the first capacitor | 13.5 ms | |

| Capacitance of other capacitors | 13 mF | |

| Discharge interval of other capacitors | 4.5 ms | |

| Initial voltage of all capacitors | 1100 V | |

| Crowbar branch resistance | 1 μΩ |

| Symbol | Value | Symbol | Value |

|---|---|---|---|

| L | 1.0 mH | 100 mF | |

| R | 100 mΩ | 1200 μF | |

| 1.2 mH | 80 μF | ||

| 112 mΩ | 10 kHz | ||

| 2 mH | 118 V | ||

| 100 mF | 598 V | ||

| 4 ms | 400 V | ||

| N | 4 | 100 V |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Zhang, D.; Ding, H.; He, Z.; Zhou, W.; Zhang, Z. A Highly Stabilized Current Source Topology with Slope Compensation for a High-Power Microwave Guiding Coil. Electronics 2025, 14, 739. https://doi.org/10.3390/electronics14040739

Zhang D, Ding H, He Z, Zhou W, Zhang Z. A Highly Stabilized Current Source Topology with Slope Compensation for a High-Power Microwave Guiding Coil. Electronics. 2025; 14(4):739. https://doi.org/10.3390/electronics14040739

Chicago/Turabian StyleZhang, Dandi, Hongfa Ding, Zhou He, Wentao Zhou, and Ziqi Zhang. 2025. "A Highly Stabilized Current Source Topology with Slope Compensation for a High-Power Microwave Guiding Coil" Electronics 14, no. 4: 739. https://doi.org/10.3390/electronics14040739

APA StyleZhang, D., Ding, H., He, Z., Zhou, W., & Zhang, Z. (2025). A Highly Stabilized Current Source Topology with Slope Compensation for a High-Power Microwave Guiding Coil. Electronics, 14(4), 739. https://doi.org/10.3390/electronics14040739