Total Ionizing Dose Effects in Advanced 28 nm Charge Trapping 3D NAND Flash Memory

Abstract

1. Introduction

2. Devices and Experimental Details

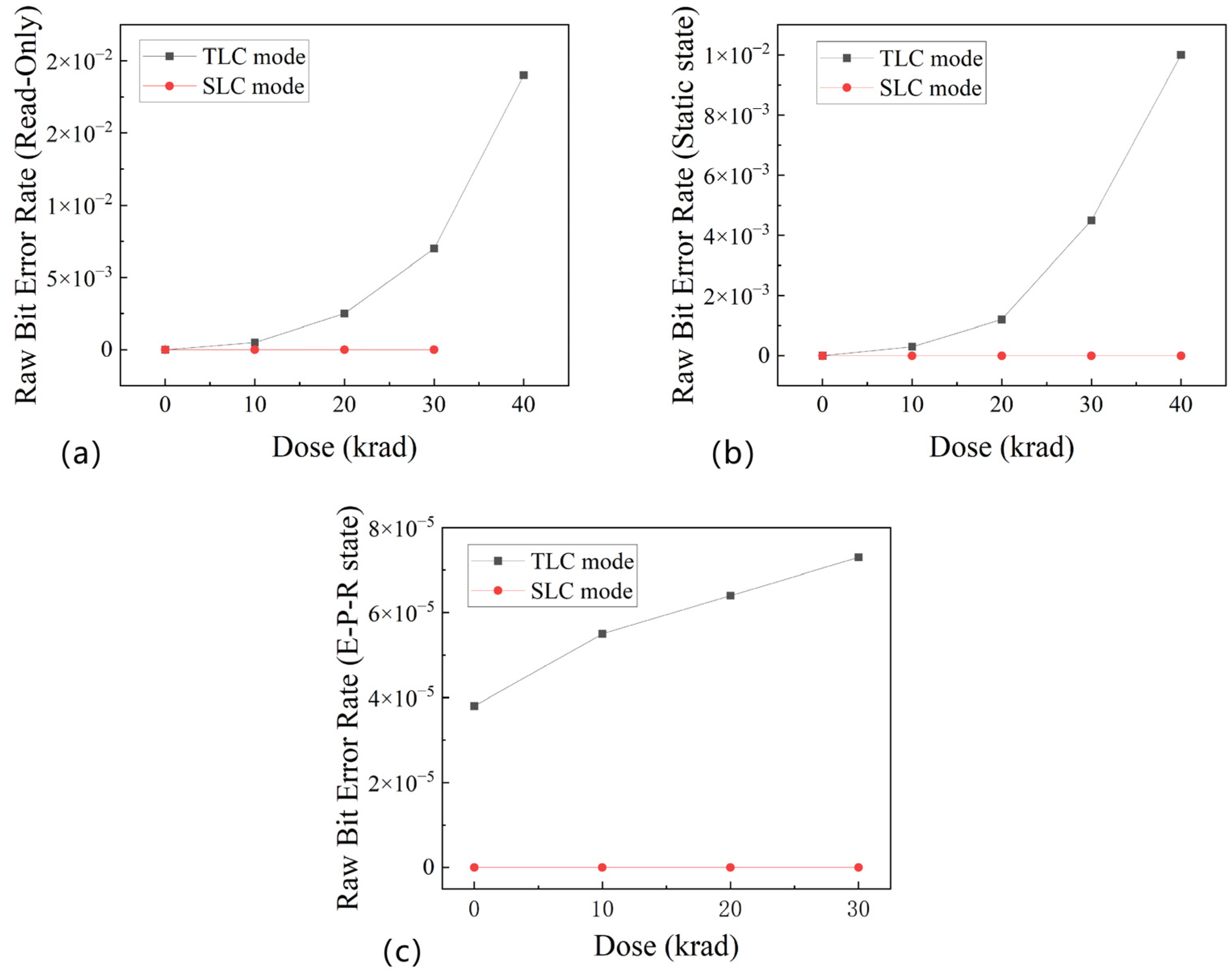

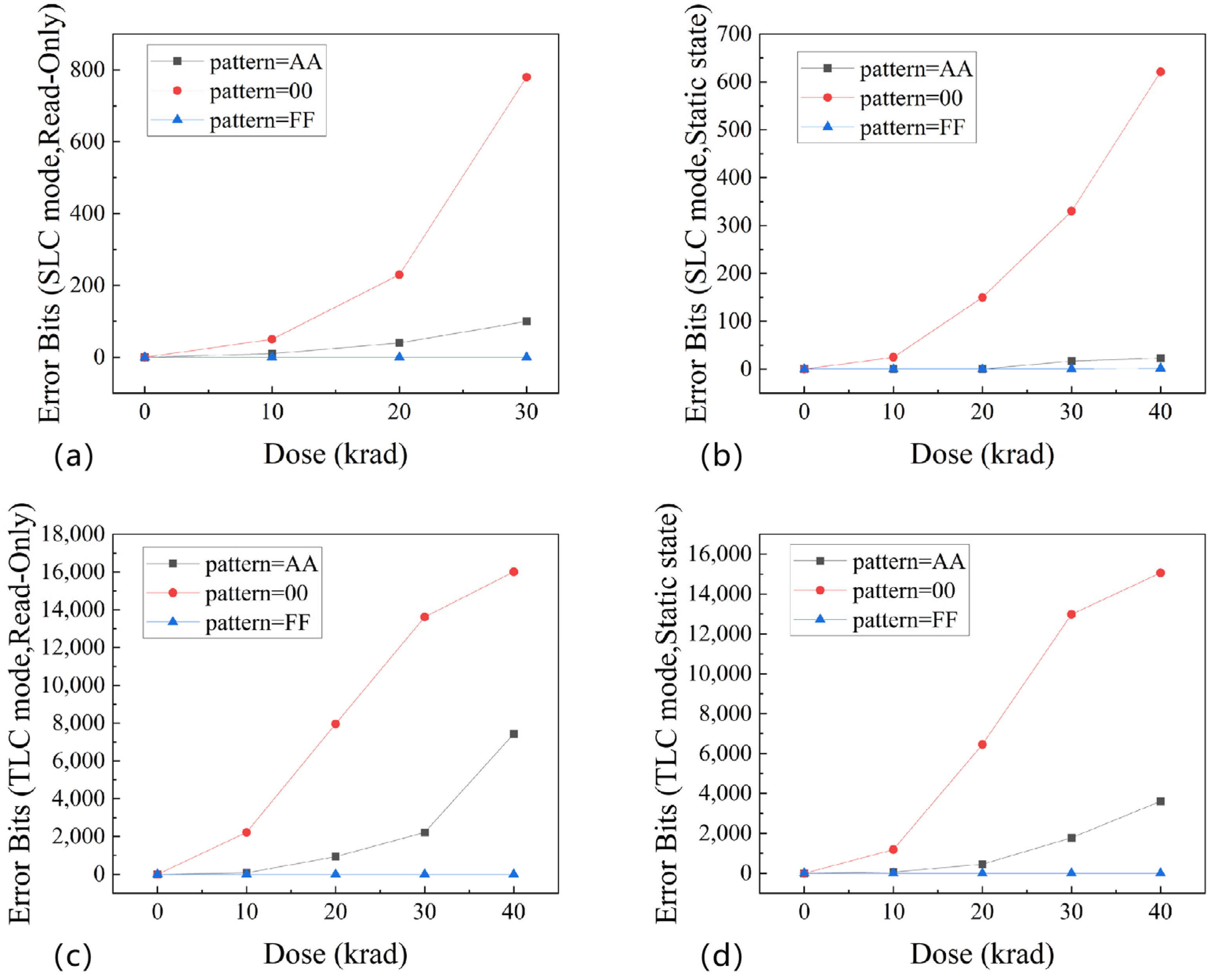

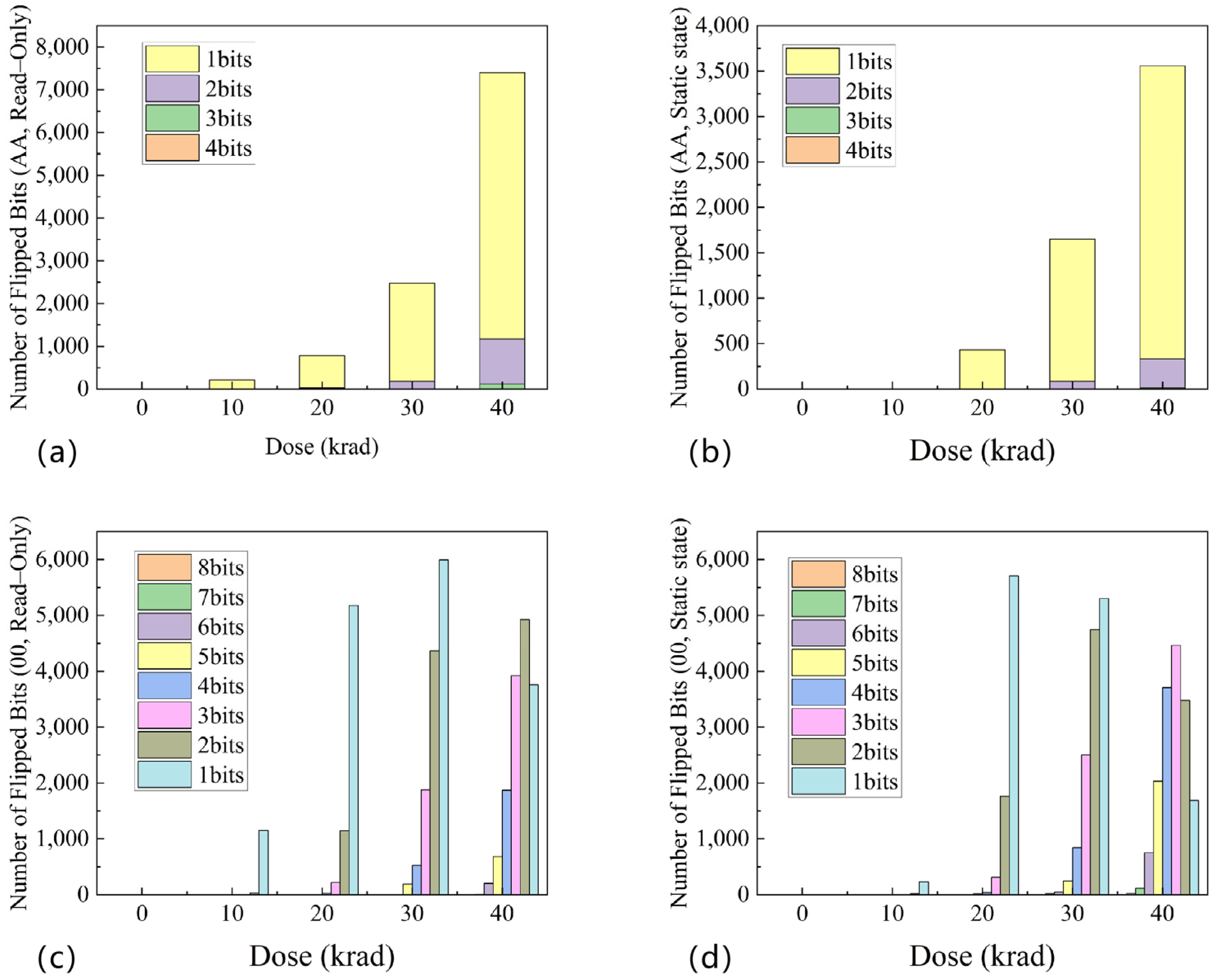

3. Results and Discussions

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Jooq, M.K.; Moaiyeri, M.H.; Al-Shidaifat, A.; Song, H. Ultra-efficient and robust auto-nonvolatile schmitt trigger-based latch design using ferroelectric CNTFET technology. IEEE Trans. Ultrason. Ferroelectr. Freq. Control 2022, 69, 1829–1840. [Google Scholar] [CrossRef] [PubMed]

- Cappelletti, P. Non volatile memory evolution and revolution. In Proceedings of the 2015 IEEE International Electron Devices Meeting (IEDM), Washington, DC, USA, 7–9 December 2015; pp. 10.11.11–10.11.14. [Google Scholar]

- Monzio Compagnoni, C.; Goda, A.; Spinelli, A.S.; Feeley, P.; Lacaita, A.L.; Visconti, A. Reviewing the Evolution of the NAND Flash Technology. Proc. IEEE 2017, 105, 1609–1633. [Google Scholar] [CrossRef]

- Lee, S.; Kim, C.; Kim, M.; Joe, S.-m.; Jang, J.; Kim, S.; Lee, K.; Kim, J.; Park, J.; Lee, H.-J. A 1Tb 4b/cell 64-stacked-WL 3D NAND flash memory with 12MB/s program throughput. In Proceedings of the 2018 IEEE International Solid-State Circuits Conference-(ISSCC), San Francisco, CA, USA, 11–15 February 2018; pp. 340–342. [Google Scholar]

- Tanaka, H.; Kido, M.; Yahashi, K.; Oomura, M.; Katsumata, R.; Kito, M.; Fukuzumi, Y.; Sato, M.; Nagata, Y.; Matsuoka, Y. Bit cost scalable technology with punch and plug process for ultra high density flash memory. In Proceedings of the 2007 IEEE Symposium on VLSI Technology, Kyoto, Japan, 12–14 June 2007; pp. 14–15. [Google Scholar]

- Jang, J.; Kim, H.-S.; Cho, W.; Cho, H.; Kim, J.; Shim, S.I.; Jeong, J.-H.; Son, B.-K.; Kim, D.W.; Shim, J.-J. Vertical cell array using TCAT (Terabit Cell Array Transistor) technology for ultra high density NAND flash memory. In Proceedings of the 2009 Symposium on VLSI Technology, Kyoto, Japan, 15–17 June 2009; pp. 192–193. [Google Scholar]

- Whang, S.; Lee, K.; Shin, D.; Kim, B.; Kim, M.; Bin, J.; Han, J.; Kim, S.; Lee, B.; Jung, Y. Novel 3-dimensional dual control-gate with surrounding floating-gate (DC-SF) NAND flash cell for 1Tb file storage application. In Proceedings of the 2010 International Electron Devices Meeting, San Francisco, CA, USA, 6–8 December 2010; pp. 29.27.21–29.27.24. [Google Scholar]

- Choi, E.-S.; Park, S.-K. Device considerations for high density and highly reliable 3D NAND flash cell in near future. In Proceedings of the 2012 International Electron Devices Meeting, San Francisco, CA, USA, 10–13 December 2012; pp. 9.4.1–9.4.4. [Google Scholar]

- Micheloni, R. 3D Flash Memories; Springer: Dordrecht, The Netherlands, 2016. [Google Scholar]

- Bagatin, M.; Gerardin, S.; Paccagnella, A.; Beltrami, S. Total Ionizing Dose Effects in 3D NAND Replacement Gate Flash Memory Cells. IEEE Trans. Nucl. Sci. 2023, 71, 412–417. [Google Scholar] [CrossRef]

- Kumari, P.; Huang, S.; Wasiolek, M.; Hattar, K.; Ray, B. Layer-Dependent Bit Error Variation in 3-D NAND Flash Under Ionizing Radiation. IEEE Trans. Nucl. Sci. 2020, 67, 2021–2027. [Google Scholar] [CrossRef]

- Bagatin, M.; Gerardin, S.; Paccagnella, A.; Beltrami, S.; Costantino, A.; Muschitiello, M.; Zadeh, A.; Ferlet-Cavrois, V. Total Ionizing Dose Effects in 3-D NAND Flash Memories. IEEE Trans. Nucl. Sci. 2019, 66, 48–53. [Google Scholar] [CrossRef]

- Kumar, M.A.; Raquibuzzaman, M.; Buddhanoy, M.; Wasiolek, M.; Hattar, K.; Boykin, T.; Ray, B. Total-Ionizing-Dose Effects on Threshold Voltage Distribution of 64-Layer 3D NAND Memories. In Proceedings of the 2022 IEEE Radiation Effects Data Workshop (REDW) (in Conjunction with 2022 NSREC), Provo, UT, USA, 18–22 July 2022; pp. 1–5. [Google Scholar]

- Schwank, J.R.; Shaneyfelt, M.R.; Fleetwood, D.M.; Felix, J.A.; Dodd, P.E.; Paillet, P.; Ferlet-Cavrois, V. Radiation Effects in MOS Oxides. IEEE Trans. Nucl. Sci. 2008, 55, 1833–1853. [Google Scholar] [CrossRef]

- Buddhanoy, M.; Kumari, P.; Surendranathan, U.; Wasiolek, M.; Hattar, K.; Ray, B. Total Ionizing Dose Effects on Long-Term Data Retention Characteristics of Commercial 3-D NAND Memories. IEEE Trans. Nucl. Sci. 2022, 69, 390–396. [Google Scholar] [CrossRef]

- Surendranathan, U.; Wasiolek, M.; Hattar, K.; Fleetwood, D.M.; Ray, B. Total Ionizing Dose Effects on Read Noise of MLC 3-D NAND Memories. IEEE Trans. Nucl. Sci. 2022, 69, 321–326. [Google Scholar] [CrossRef]

- Hu, H.; Feng, Y.; Zhan, X.; Xi, K.; Ji, L.; Chen, J.; Liu, J. Experimental characterizations on TID Radiation Impacts in Charge-trap 3D NAND Flash Memory. In Proceedings of the 2021 Silicon Nanoelectronics Workshop (SNW), Kyoto, Japan, 13 June 2021; pp. 1–2. [Google Scholar]

- Hansen, D.; Meraz, F.; Montoya, J.; Roberg, S.; Williamson, G. Radiation Testing of a Flash NAND Device. In Proceedings of the 2017 IEEE Radiation Effects Data Workshop (REDW), New Orleans, LA, USA, 17–21 July 2017; pp. 1–4. [Google Scholar]

- Buddhanoy, M.; Sakib, S.; Surendranathan, U.; Wasiolek, M.; Hattar, K.; Milenkovic, A.; Ray, B. New Total-Ionizing-Dose Resistant Data Storing Technique for NAND Flash Memory. IEEE Trans. Device Mater. Reliab. 2022, 22, 438–446. [Google Scholar] [CrossRef]

- Wilcox, E.P.; Campola, M.J. A TID and SEE characterization of multi-terabit COTS 3D NAND flash. In Proceedings of the 2019 IEEE Radiation Effects Data Workshop, San Antonio, TX, USA, 8–12 July 2019; pp. 1–7. [Google Scholar]

- Gadlage, M.J.; Bruce, D.I.; Ingalls, J.D.; Bossev, D.P.; McKinney, M.; Kay, M.J. Directional Dependence of Co-60 Irradiation on the Total Dose Response of Flash Memories. IEEE Trans. Nucl. Sci. 2019, 66, 148–154. [Google Scholar] [CrossRef]

- Bi, J. Radiation effects of floating-gate (FG) and charge-trapping (CT) Flash memory technologies. In Proceedings of the 2019 International Conference on IC Design and Technology (ICICDT), Suzhou, China, 17–19 June 2019; pp. 1–3. [Google Scholar]

- Bagatin, M.; Gerardin, S.; Paccagnella, A.; Beltrami, S. Depth Dependence of Threshold Voltage Shift in 3-D Flash Memories Exposed to X-Rays. IEEE Trans. Nucl. Sci. 2021, 68, 659–664. [Google Scholar] [CrossRef]

- Bagatin, M.; Gerardin, S.; Cellere, G.; Paccagnella, A.; Visconti, A.; Bonanomi, M.; Beltrami, S. Error Instability in Floating Gate Flash Memories Exposed to TID. IEEE Trans. Nucl. Sci. 2009, 56, 3267–3273. [Google Scholar] [CrossRef]

- Surendranathan, U.; Kumari, P.; Wasiolek, M.; Hattar, K.; Boykin, T.; Ray, B. Gamma-Ray-Induced Error Pattern Analysis for MLC 3-D NAND Flash Memories. IEEE Trans. Nucl. Sci. 2021, 68, 733–739. [Google Scholar] [CrossRef]

- Irom, F.; Nguyen, D.N.; Harboe-Sorensen, R.; Virtanen, A. Evaluation of Mechanisms in TID Degradation and SEE Susceptibility of Single- and Multi-Level High Density NAND Flash Memories. IEEE Trans. Nucl. Sci. 2011, 58, 2477–2482. [Google Scholar] [CrossRef]

- Allen, G.R.; Irom, F.; Edmonds, L.; Nguyen, D.; Scheick, L.Z.; Vartanian, S.; McClure, S.S.; Stanford, K. Total ionizing dose measurements of a commercial samsung NAND flash memory for a high dose mission. In Proceedings of the 2018 IEEE Radiation Effects Data Workshop (REDW), Waikoloa, HI, USA, 16–20 July 2018; pp. 1–9. [Google Scholar]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Zheng, X.; Wang, Y.; Mo, R.; Liu, C.; Wang, T.; Huo, M.; Xiao, L. Total Ionizing Dose Effects in Advanced 28 nm Charge Trapping 3D NAND Flash Memory. Electronics 2025, 14, 473. https://doi.org/10.3390/electronics14030473

Zheng X, Wang Y, Mo R, Liu C, Wang T, Huo M, Xiao L. Total Ionizing Dose Effects in Advanced 28 nm Charge Trapping 3D NAND Flash Memory. Electronics. 2025; 14(3):473. https://doi.org/10.3390/electronics14030473

Chicago/Turabian StyleZheng, Xuesong, Yuhang Wang, Rigen Mo, Chaoming Liu, Tianqi Wang, Mingxue Huo, and Liyi Xiao. 2025. "Total Ionizing Dose Effects in Advanced 28 nm Charge Trapping 3D NAND Flash Memory" Electronics 14, no. 3: 473. https://doi.org/10.3390/electronics14030473

APA StyleZheng, X., Wang, Y., Mo, R., Liu, C., Wang, T., Huo, M., & Xiao, L. (2025). Total Ionizing Dose Effects in Advanced 28 nm Charge Trapping 3D NAND Flash Memory. Electronics, 14(3), 473. https://doi.org/10.3390/electronics14030473