Research and Analysis of an LLCL-Type Active Power Filter with Control Delay Compensation Mechanism

Abstract

1. Introduction

- The proposed control achieves effective delay compensation without requiring additional sensors or predictive controllers.

- Only the inner-loop compensation is used, resulting in lower cost and higher fault tolerance.

- For LLCL-type APFs, this work provides a novel perspective that fills a research gap in the existing literature.

2. Materials and Methods

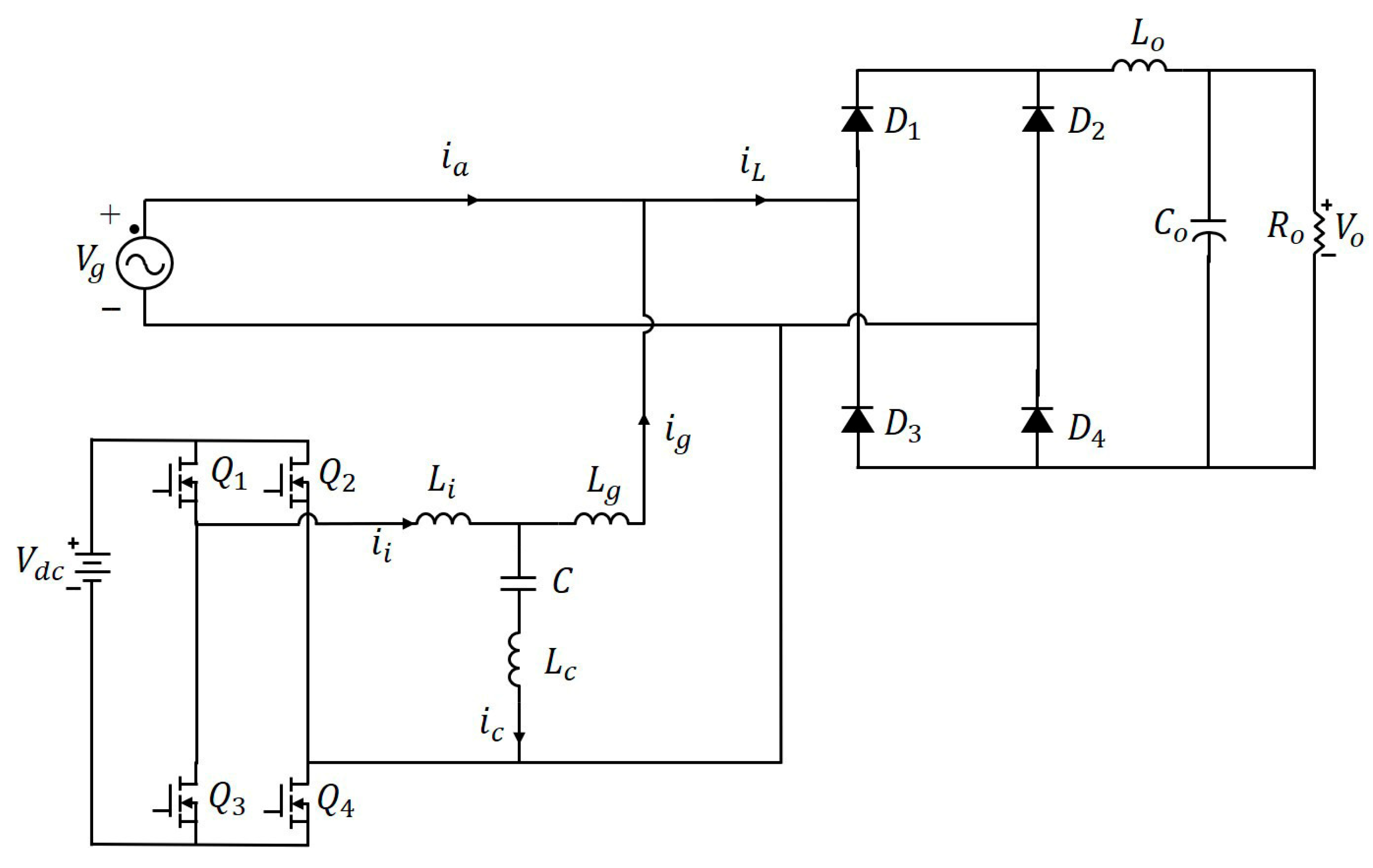

2.1. Architecture of LLCL-Type Active Power Filter

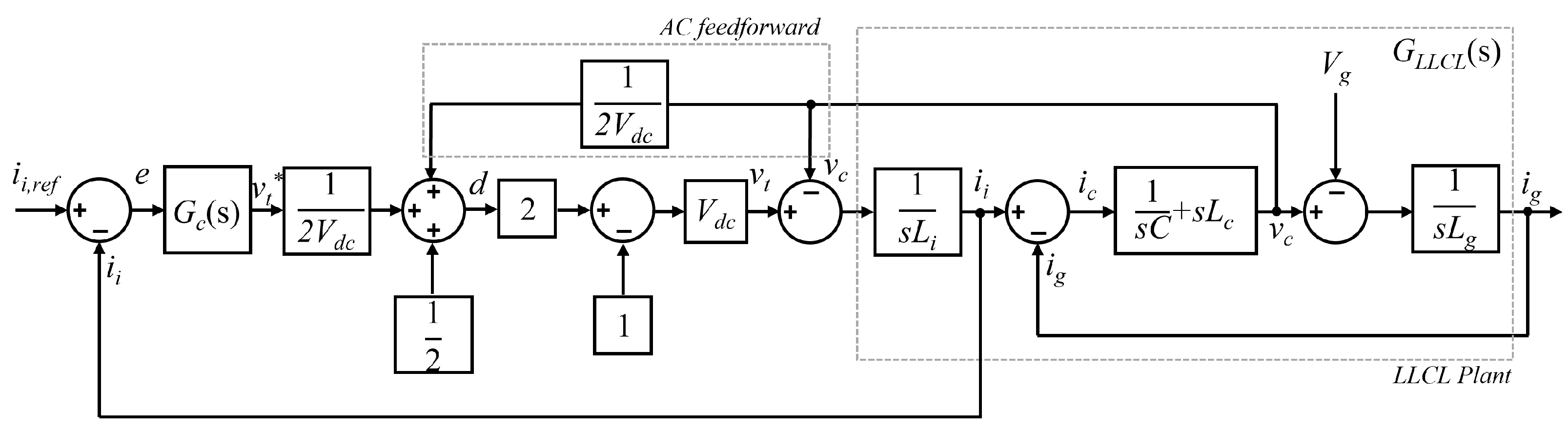

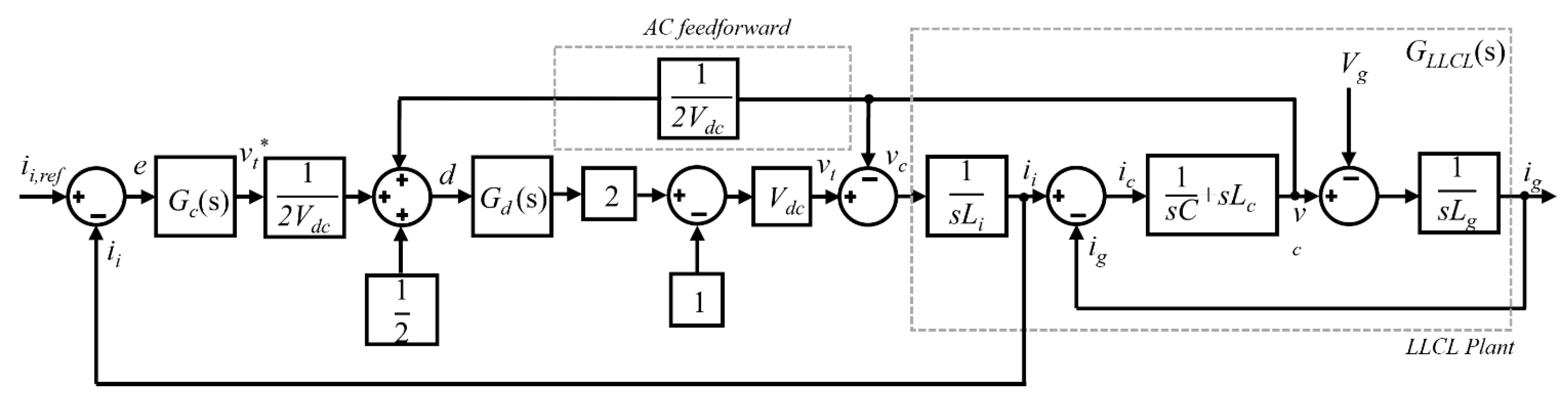

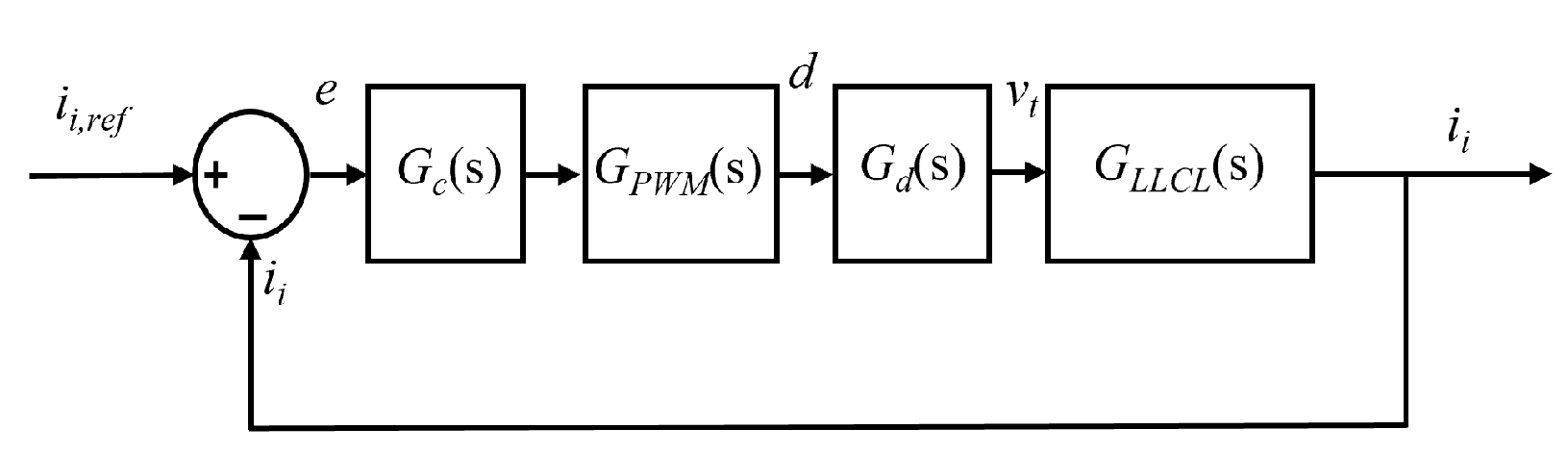

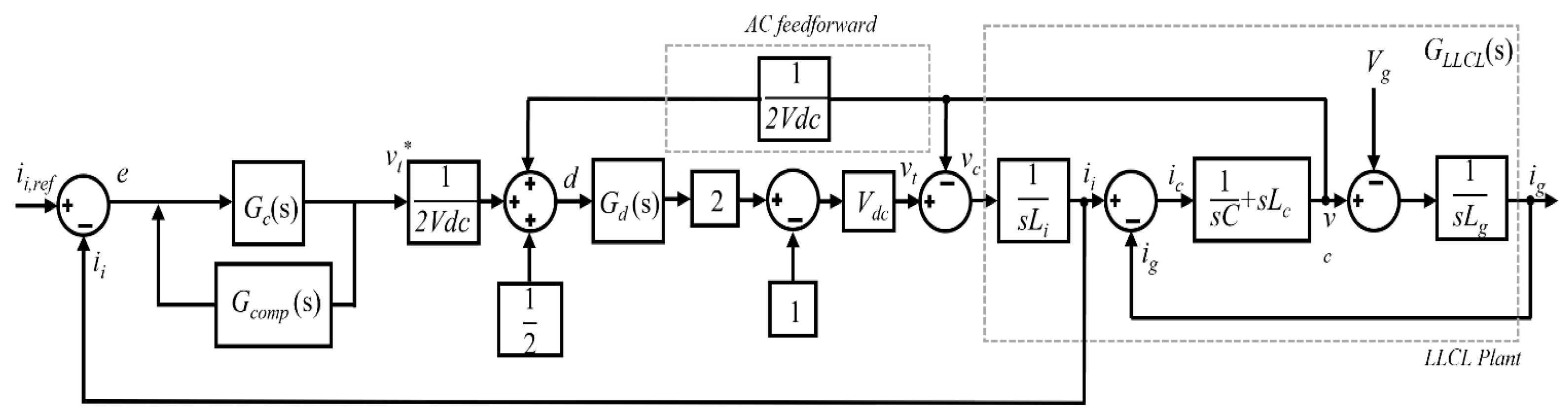

2.2. Control Delay Compensation Mechanism

2.3. Multiple Resonance and Stability Issues in LLCL-Type System

3. Results and Discussion

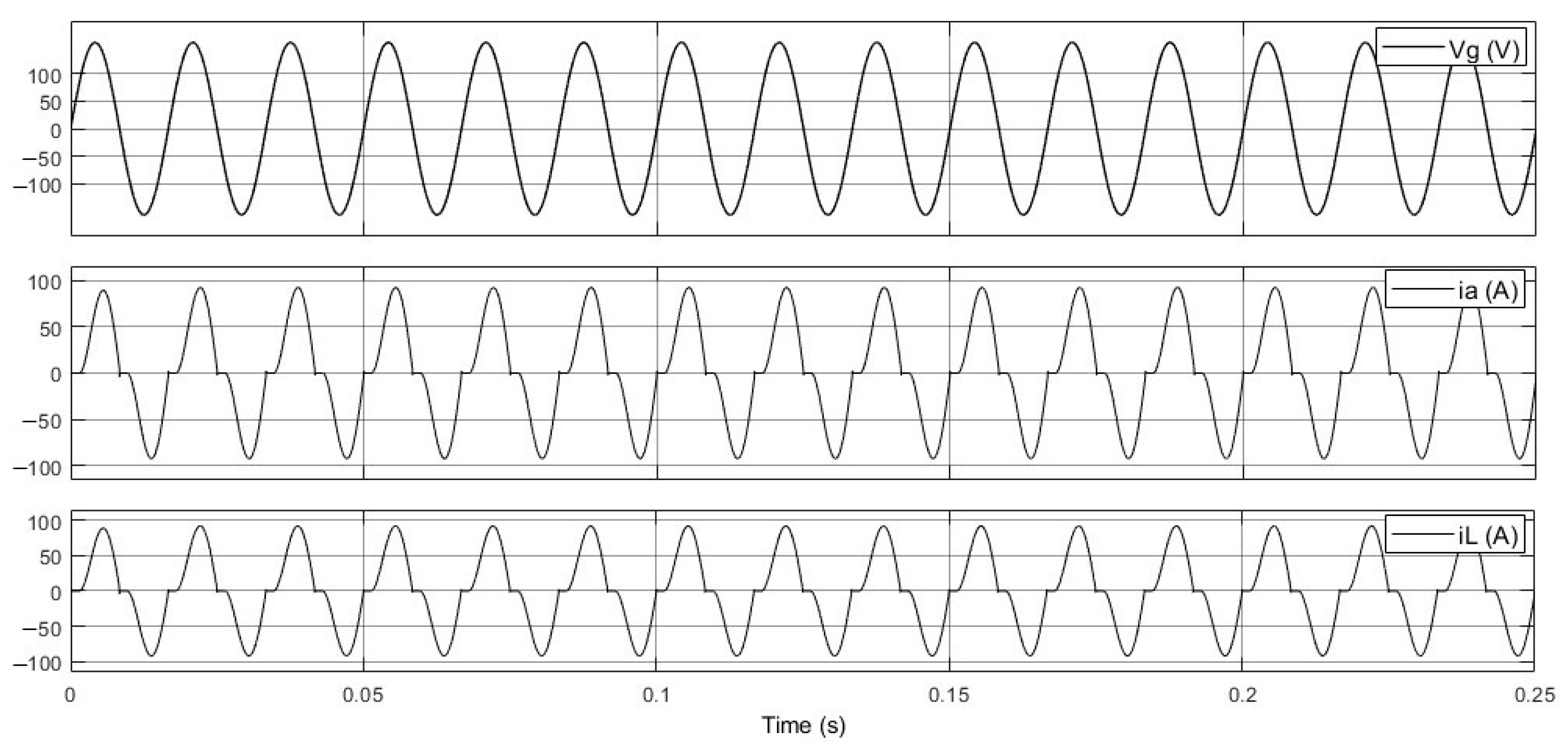

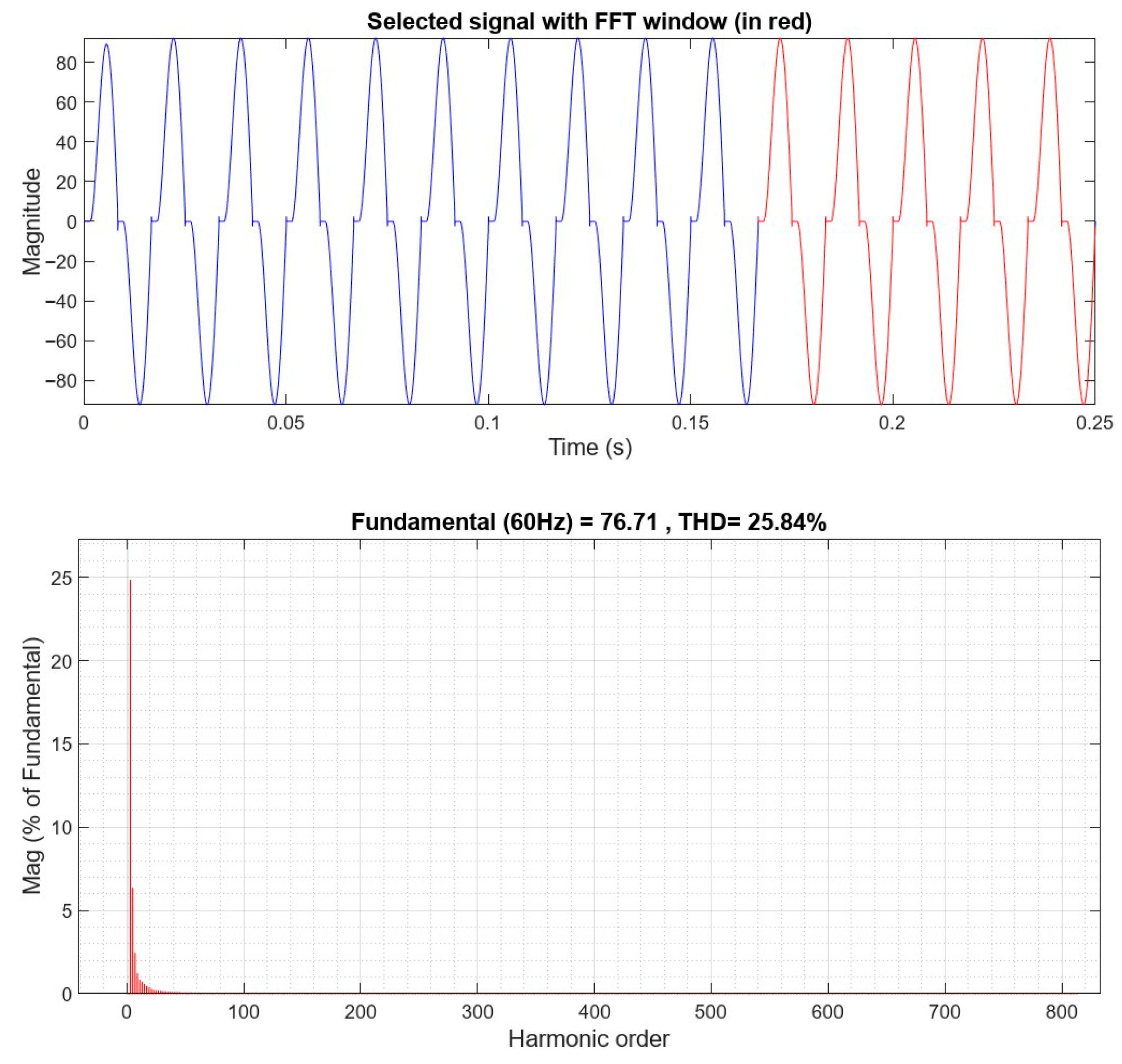

3.1. Scenario 1-Rectifier Only (No APF)

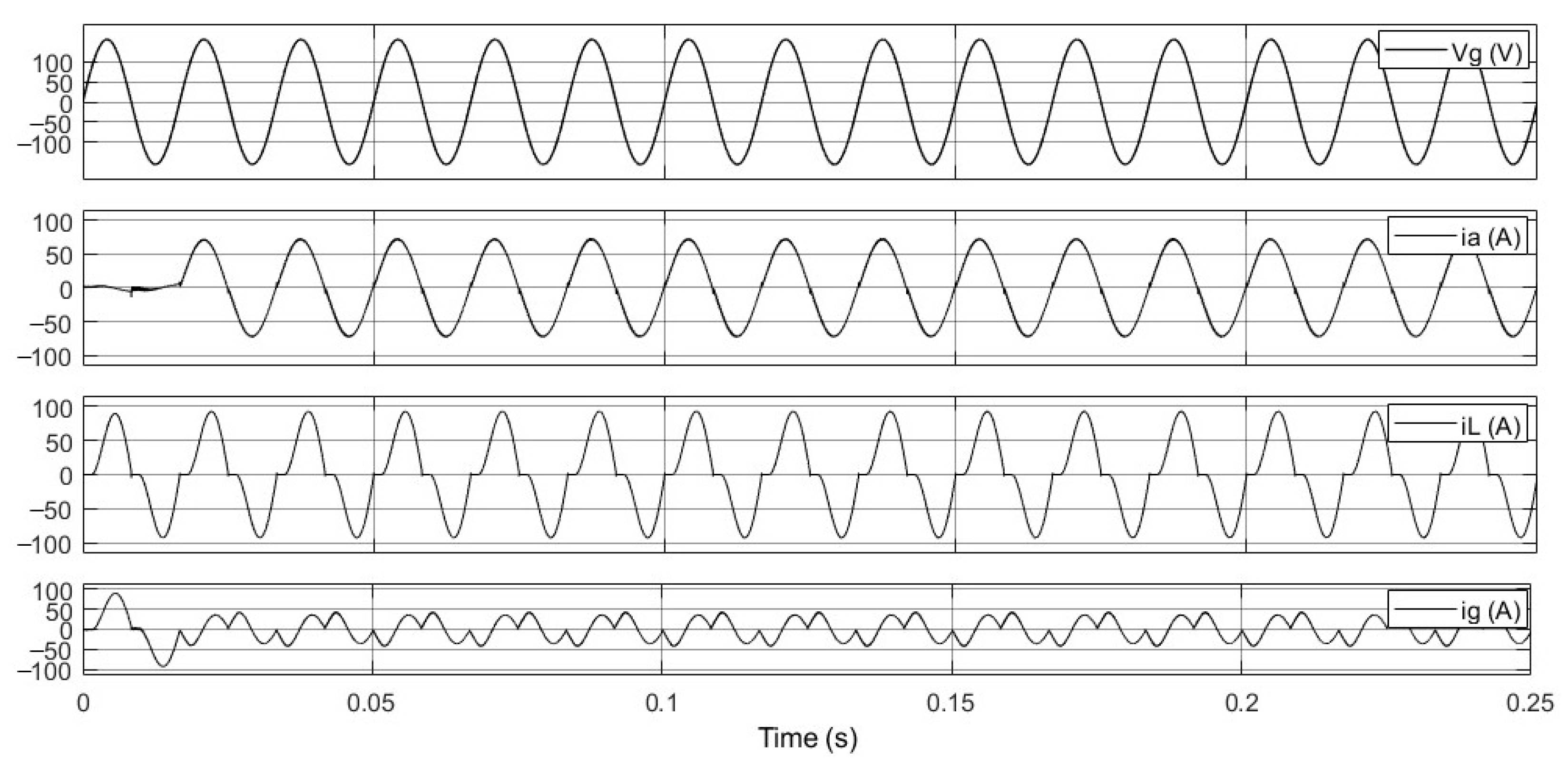

3.2. Scenario 2-APF Without Digital Control Delay

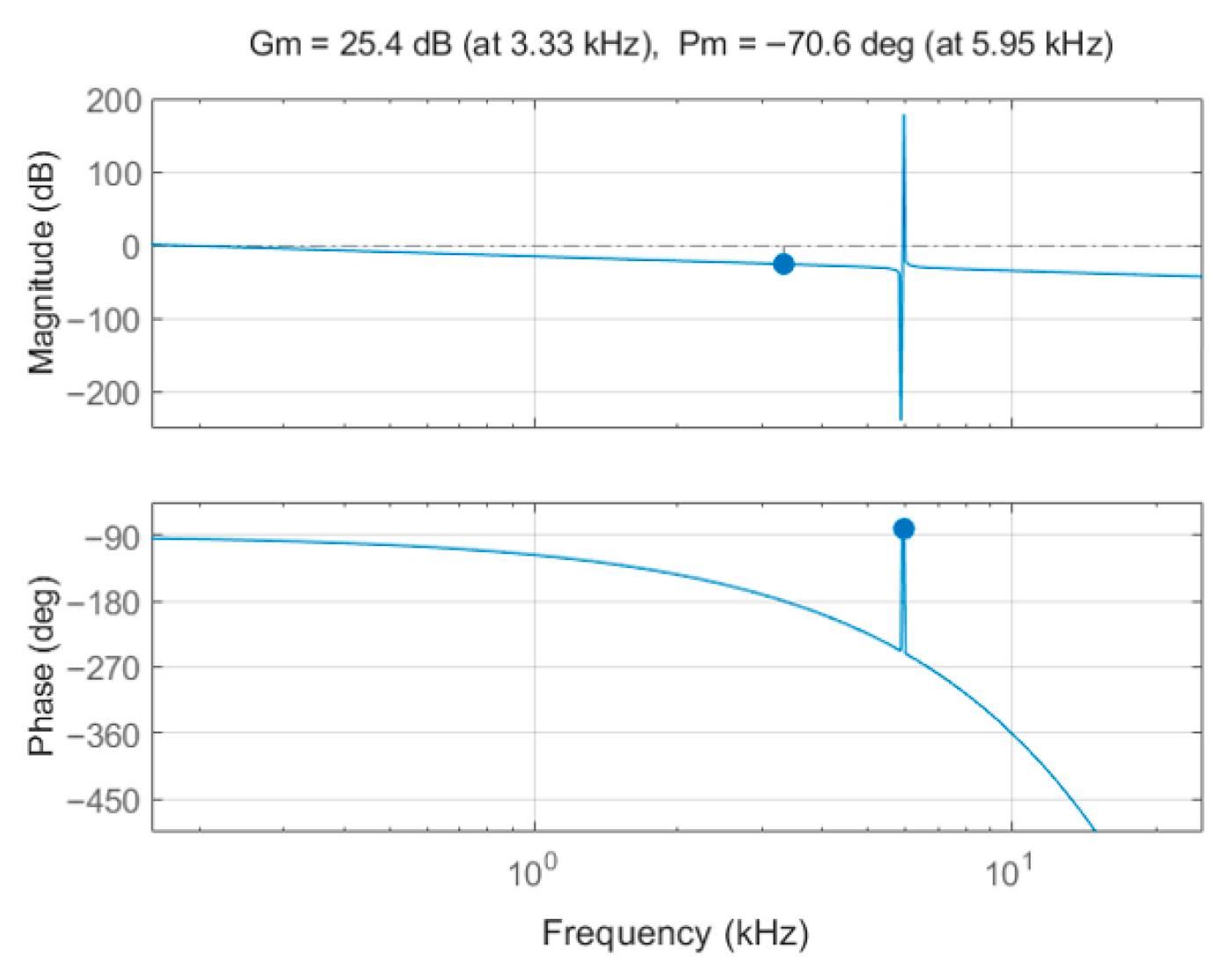

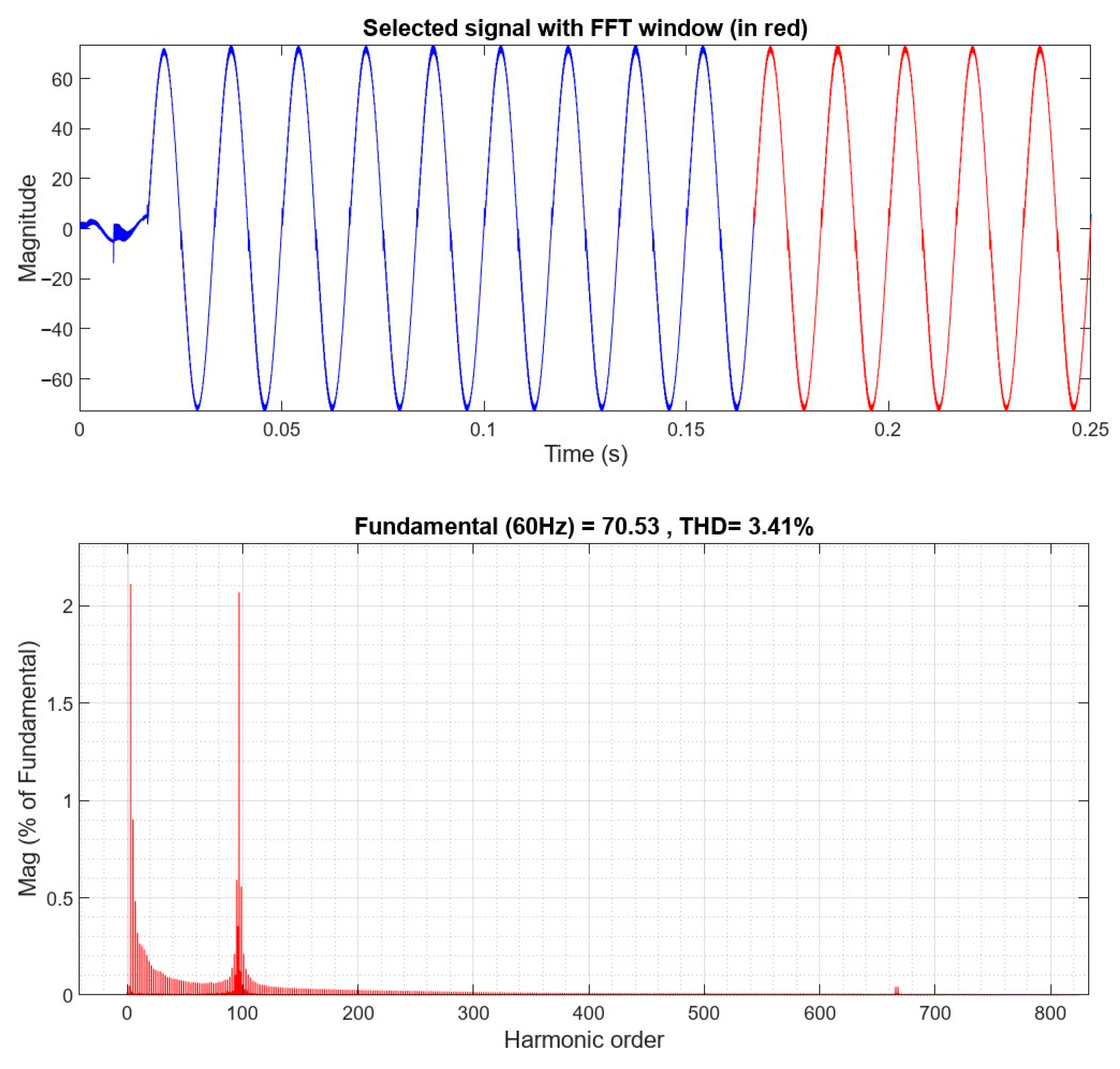

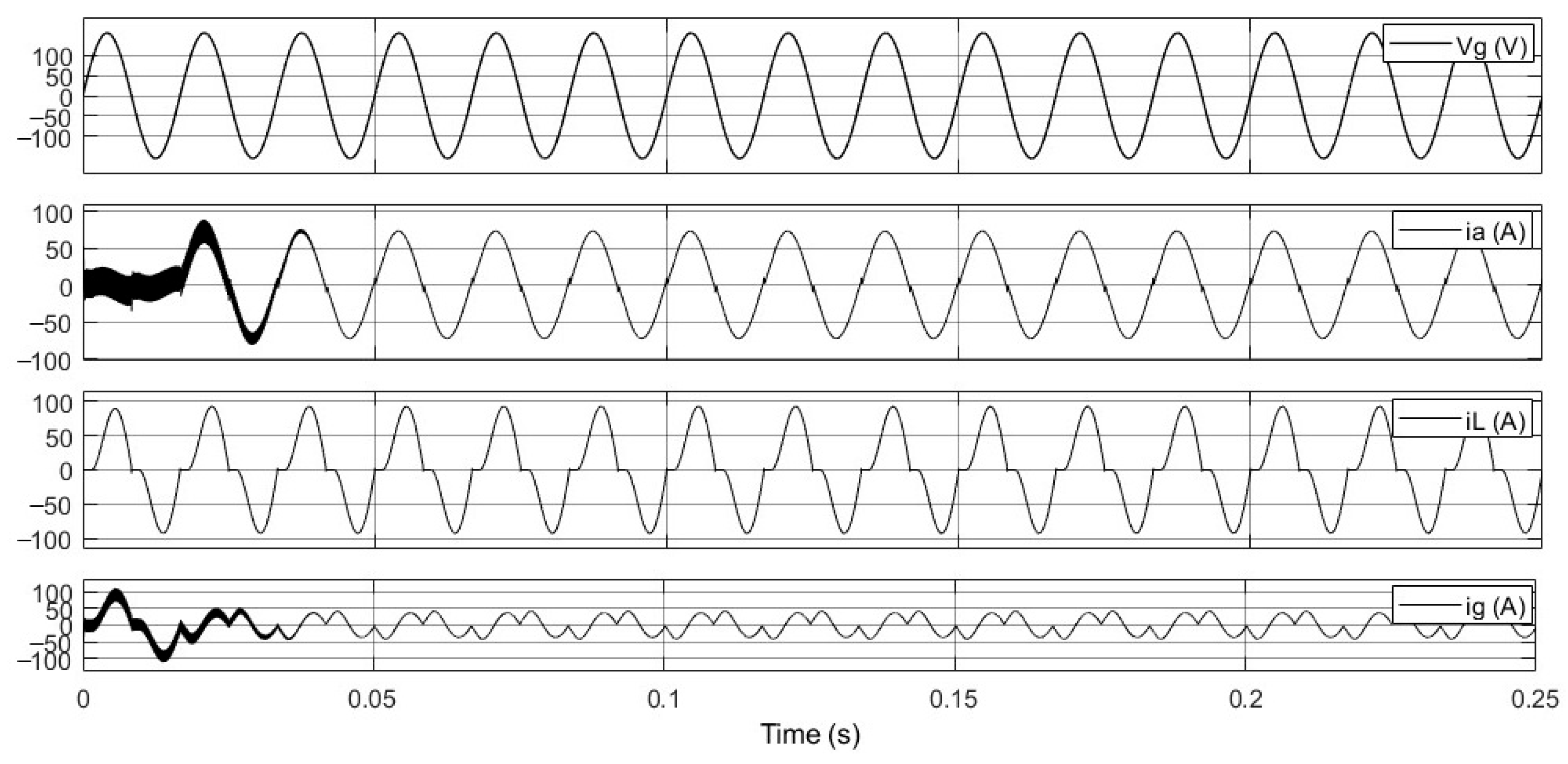

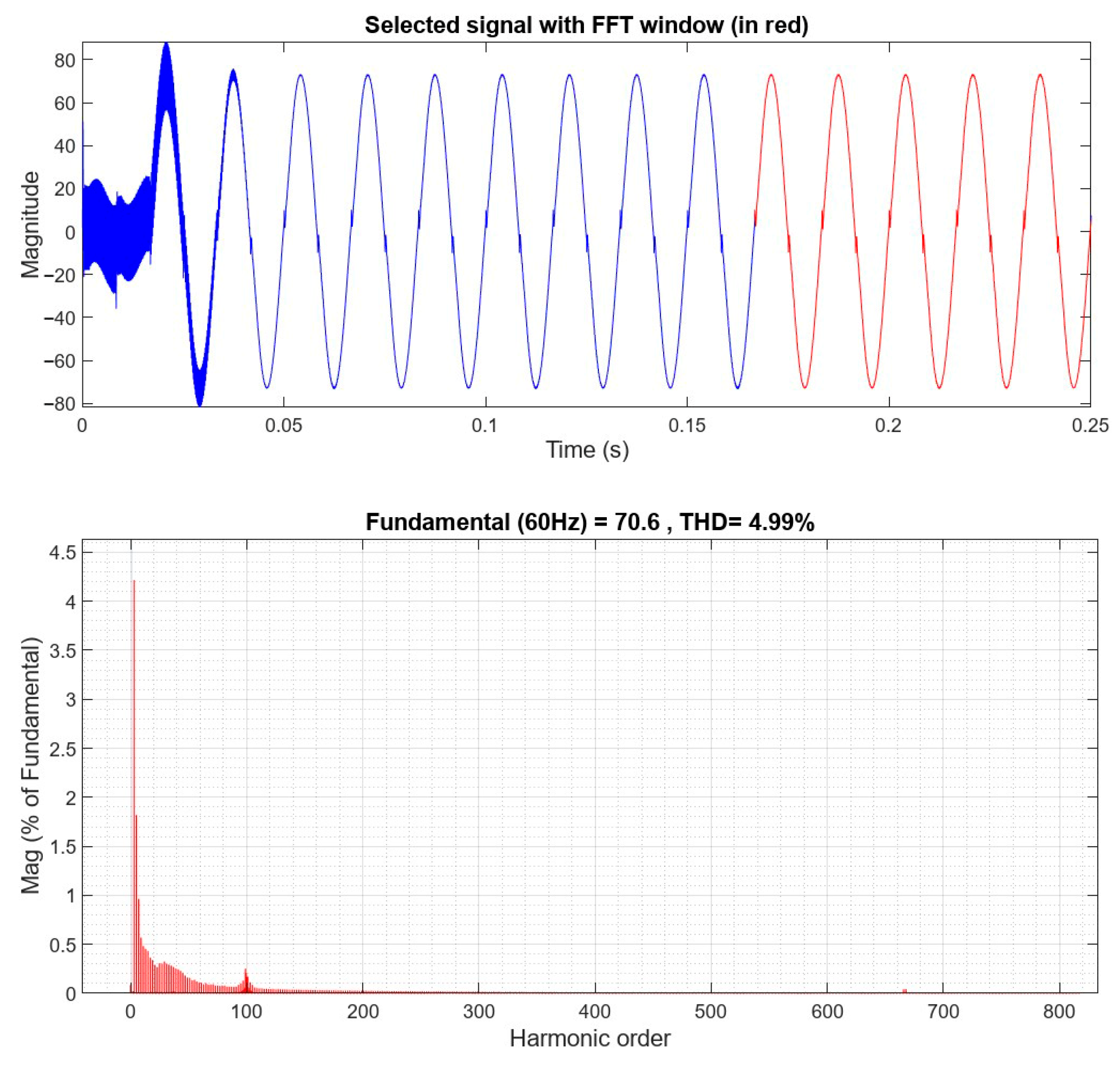

3.3. Scenario 3-APF with Digital Control Delay

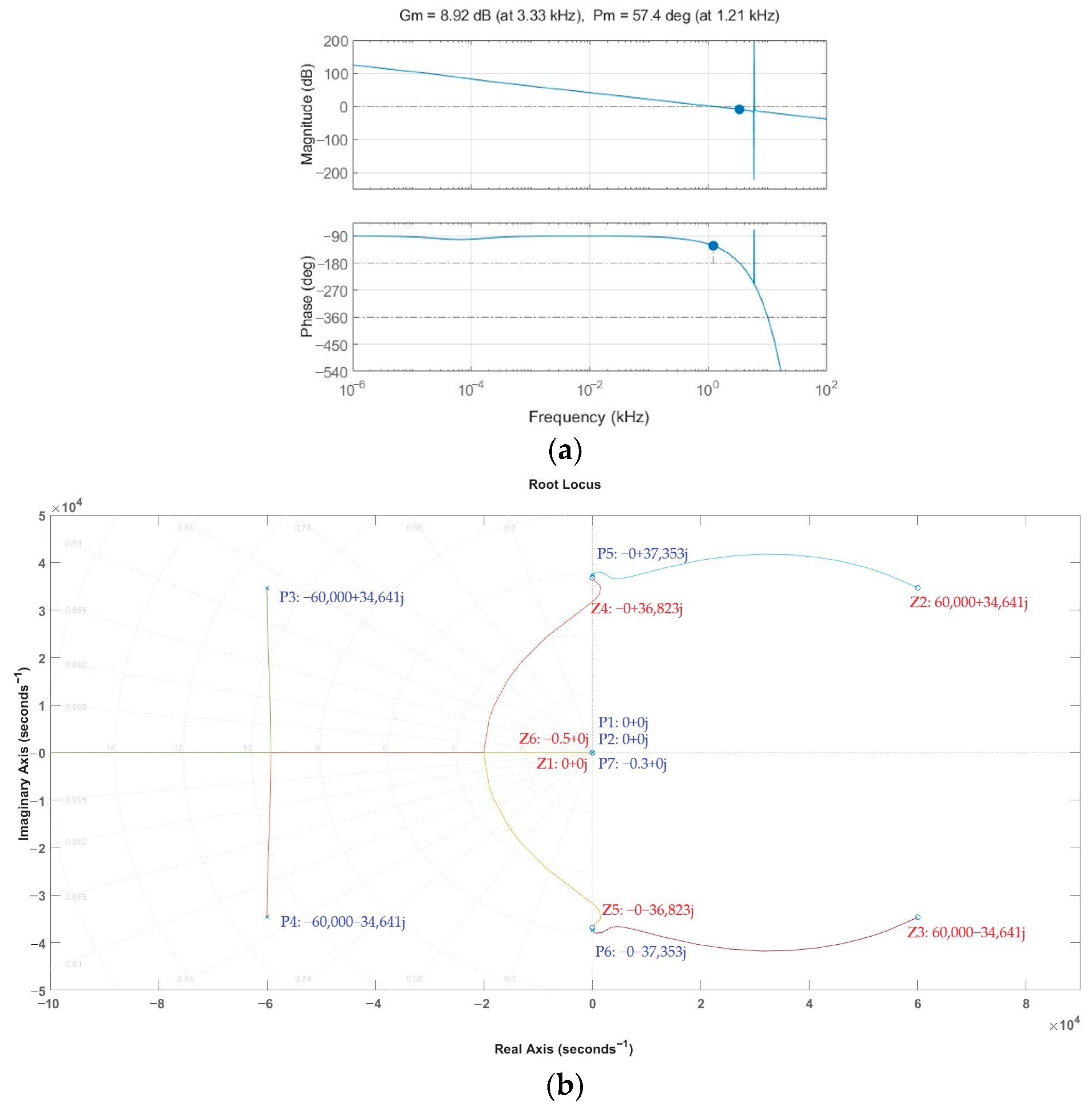

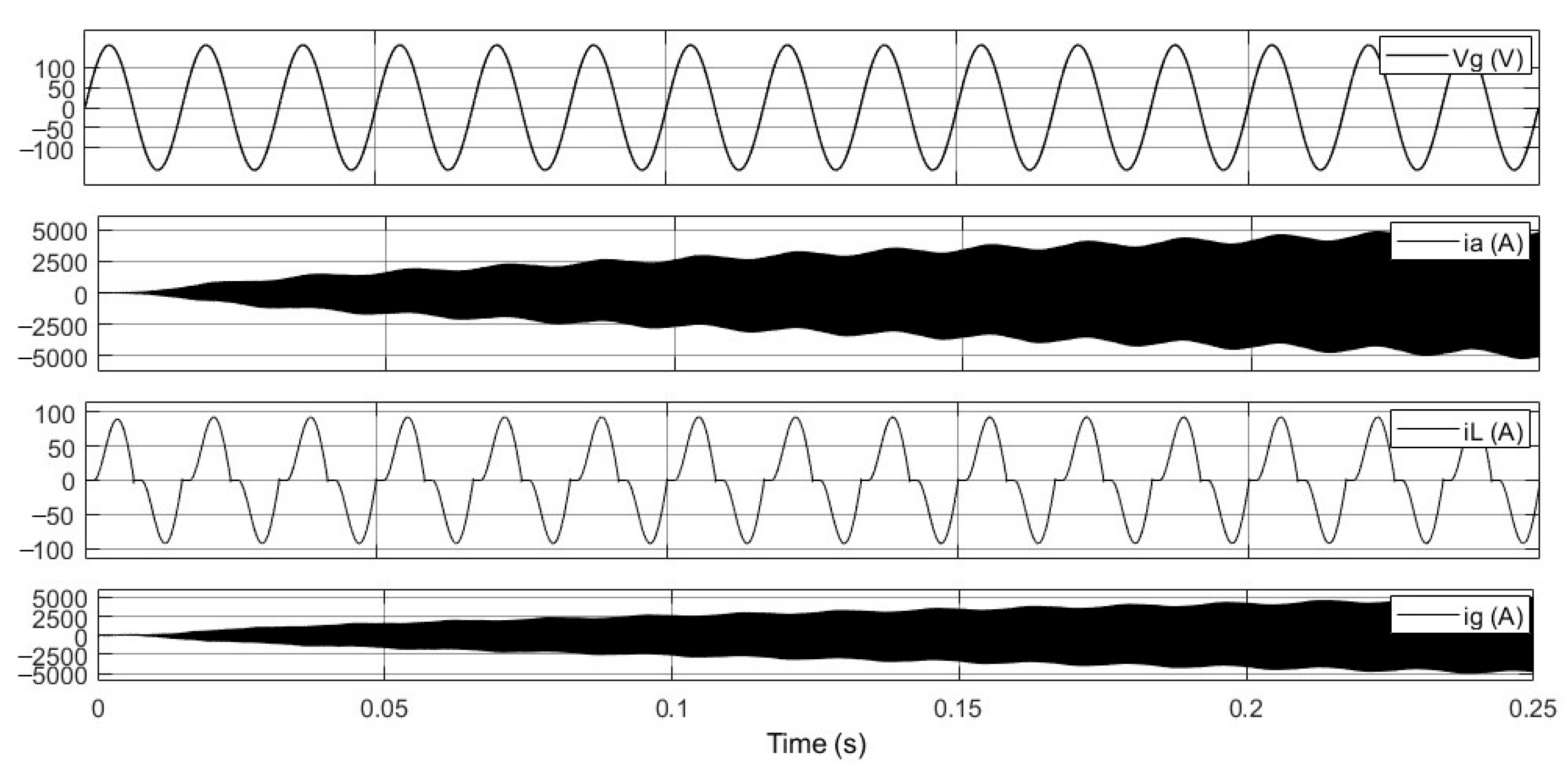

3.4. Scenario 4-APF with Proposed Delay Compensation

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Luo, A.; Xu, Q.M.; Ma, F.J.; Chen, Y.D. Overview of power quality analysis and control technology for the smart grid. J. Mod. Power Syst. Clean Energy 2016, 4, 1–9. [Google Scholar] [CrossRef]

- Fei, J.T.; Wang, H. Experimental Investigation of Recurrent Neural Network Fractional-Order Sliding Mode Control of Active Power Filter. IEEE Trans. Circuits Syst. II Express Br. 2020, 67, 2522–2526. [Google Scholar] [CrossRef]

- Gao, C.; He, S.; Fang, X.F.; Davari, P.; Leung, K.N.; Loh, P.C.; Blaabjerg, F. Current-Limiting Control Strategy for Indirect-Current-Controlled Active Power Filter. IEEE Trans. Power Deliv. 2024, 39, 3551–3554. [Google Scholar] [CrossRef]

- Karbasforooshan, M.S.; Monfared, M. Adaptive Self-Tuned Current Controller Design for an LCL-Filtered LC-Tuned Single-Phase Shunt Hybrid Active Power Filter. IEEE Trans. Power Deliv. 2022, 37, 2747–2756. [Google Scholar] [CrossRef]

- Indragandhi, V.; Boopathi, R. Experimental Investigations on Photovoltaic Interface Neutral Point Clamped Multilevel Inverter-Based Shunt Active Power Filter to Enhance Grid Power Quality. IEEE Access 2024, 12, 74482–74498. [Google Scholar] [CrossRef]

- Rai, K.B.; Kumar, N.; Singh, A. Three-Phase Grid Connected Shunt Active Power Filter Based on Adaptive Q-LMF Control Technique. IEEE Trans. Power Electron. 2024, 39, 10216–10225. [Google Scholar] [CrossRef]

- Xin, Z.; Wang, X.F.; Loh, P.C.; Blaabjerg, F. Grid-Current-Feedback Control for LCL-Filtered Grid Converters with Enhanced Stability. IEEE Trans. Power Electron. 2017, 32, 3216–3228. [Google Scholar] [CrossRef]

- Ding, X.; Xue, R.N.; Zheng, T.Z.; Kong, F.N.; Chen, Y.M. Robust Delay Compensation Strategy for LCL-Type Grid-Connected Inverter in Weak Grid. IEEE Access 2022, 10, 67639–67652. [Google Scholar] [CrossRef]

- Wu, W.; Wang, W.G. Research on FCS-MPC Control of LCL Grid-Connected Inverter Based on Optimized i1-i2-uc Prediction. In Proceedings of the 2019 International Conference on Computer Network, Electronic and Automation, Xi’an, China, 27–29 September 2019. [Google Scholar]

- Lin, Z.H.; Ruan, X.B.; Zhang, H.; Wu, L.G. A Generalized Real-Time Computation Method with Dual-Sampling Mode to Eliminate the Computation Delay in Digitally Controlled Inverters. IEEE Trans. Power Electron. 2022, 37, 5186–5195. [Google Scholar]

| Method | Theoretical Foundation | Computational Complexity | Hardware Requirements |

|---|---|---|---|

| SOGI [7] | Utilizes a SOGI to compensate digital delay in the current feedback. Performance is sensitive to frequency deviation or PLL absence. | Requires dual integrators and multipliers, imposing a relatively high DSP burden. | Needs accurate PLL synchronization; sensitive to integrator drift, noise, and numerical stability. |

| PCI [8] | Proportional PCI controller with a second-order low-pass filter to extend compensation frequency range. | Involves complex-valued computations and precise parameter tuning. | Relies on an accurate dynamic model; increased hardware consumption may limit use in embedded systems. |

| FCS-MPC [9] | FCS-MPC with time-prediction to offset one control period of delay. | Requires high-order differential models and Lagrange extrapolation, leading to high complexity. | Strongly coupled with switching vector optimization; requires high controller capacity and stability consideration. |

| Dual-sampling [10] | Real-time dual-sampling strategy to mitigate delay effects in LCL inverters. | Substantially increases computational burden and strict synchronization requirements. | Needs two current measurements per control period; sensitive to measurement noise and filter/hardware design. |

| Proposed method | Inner-loop delay compensation applied directly; no additional predictors or complex controllers needed. | Low complexity; avoids complex-valued or predictive algorithms. | No extra sensors required; reduces cost and improves fault tolerance. |

| Parameter Name | Symbol | Value |

|---|---|---|

| Output power | Pout | 5.5 kW |

| Grid voltage | Vg | 110 Vrms |

| Grid current | ia | 50 Arms |

| DC-bus voltage | Vdc | 350 V |

| Switching frequency | fs | 20 kHz |

| Output Voltage | Vo | ≈115 V |

| Output Capacitance | Co | 1000 μF |

| Output Inductance | Lo | 2500 μH |

| Load resistor | Ro | 2.4 Ω |

| Filter Capacitance | C | 25 μF |

| Inverter-side inductance | Li | 0.85 mH |

| Grid-side inductance | Lg | 27 μH |

| Filter inductance | Lc | 2.5 μH |

| P gain | Kp | 12 |

| I gain | KI | 10 |

| Compensation gain | Gcomp | 0.08 |

| Scenario | Description | Purpose |

|---|---|---|

| 1 | Rectifier only (no APF) | Baseline case to observe harmonic distortion without compensation |

| 2 | APF without digital control delay | Evaluate the effectiveness of the designed APF under ideal conditions |

| 3 | APF with digital control delay | Assess the negative impacts of delay on stability and dynamic response |

| 4 | APF with proposed delay compensation | Validate the effectiveness of the compensation strategy in restoring stability and improving performance |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Chou, T.-C.; Lee, P.-S.; Chuang, C.-Y.; Huang, C.-W. Research and Analysis of an LLCL-Type Active Power Filter with Control Delay Compensation Mechanism. Electronics 2025, 14, 4028. https://doi.org/10.3390/electronics14204028

Chou T-C, Lee P-S, Chuang C-Y, Huang C-W. Research and Analysis of an LLCL-Type Active Power Filter with Control Delay Compensation Mechanism. Electronics. 2025; 14(20):4028. https://doi.org/10.3390/electronics14204028

Chicago/Turabian StyleChou, Tzu-Chieh, Pin-Sheng Lee, Chi-Yuan Chuang, and Chun-Wei Huang. 2025. "Research and Analysis of an LLCL-Type Active Power Filter with Control Delay Compensation Mechanism" Electronics 14, no. 20: 4028. https://doi.org/10.3390/electronics14204028

APA StyleChou, T.-C., Lee, P.-S., Chuang, C.-Y., & Huang, C.-W. (2025). Research and Analysis of an LLCL-Type Active Power Filter with Control Delay Compensation Mechanism. Electronics, 14(20), 4028. https://doi.org/10.3390/electronics14204028