1. Introduction

The exponential growth of Internet of Things (IoT) devices and mobile communication systems has created unprecedented demands for frequency synthesizers about fast frequency acquisition, high spectral purity, and power efficiency [

1,

2,

3]. Modern wireless standards such as 5G NR, Wi-Fi 6E, and emerging sub-6 GHz IoT protocols, require fast-locking frequency synthesizer with a lock time in the microsecond range, while maintaining phase noise performance below −100 dBc/Hz at critical offset frequencies for adjacent channel interference rejection [

4,

5].

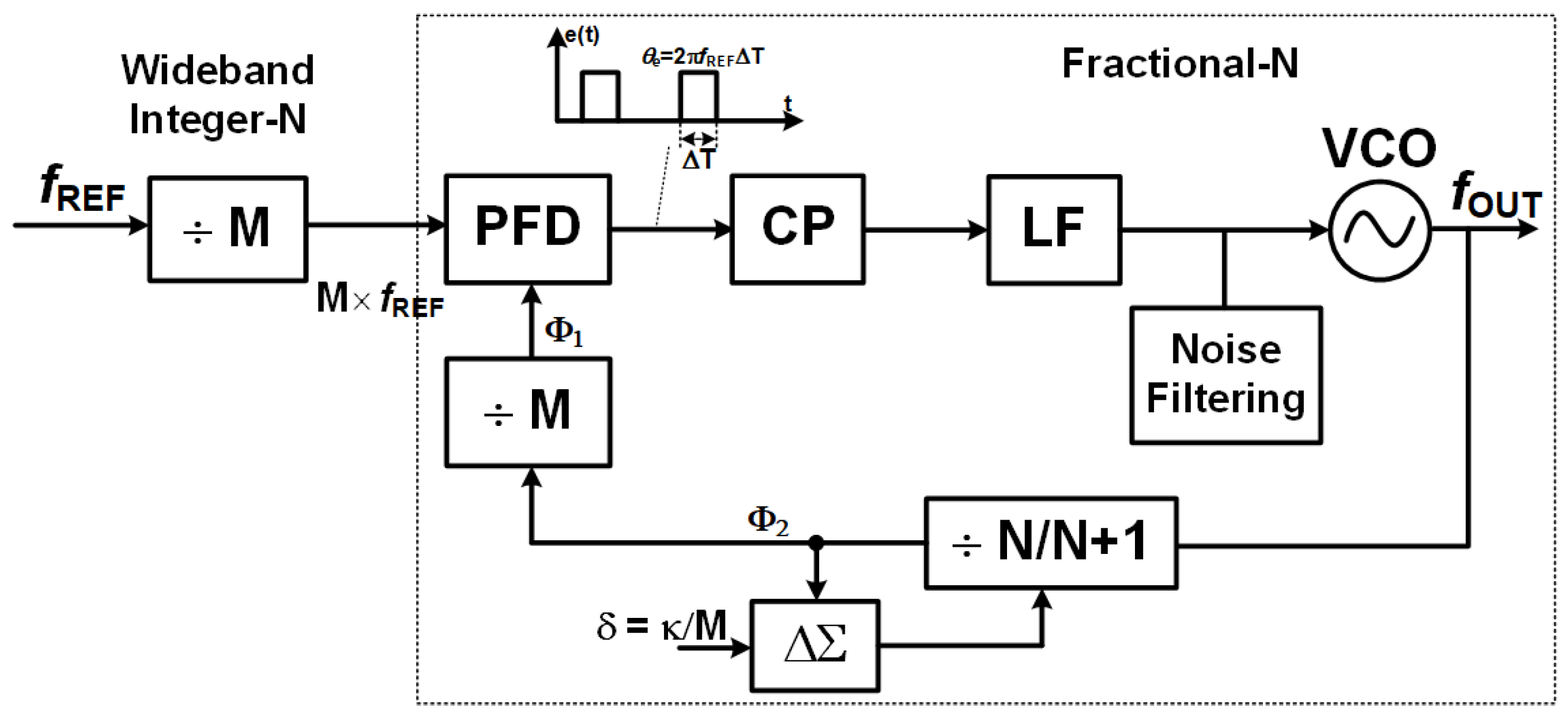

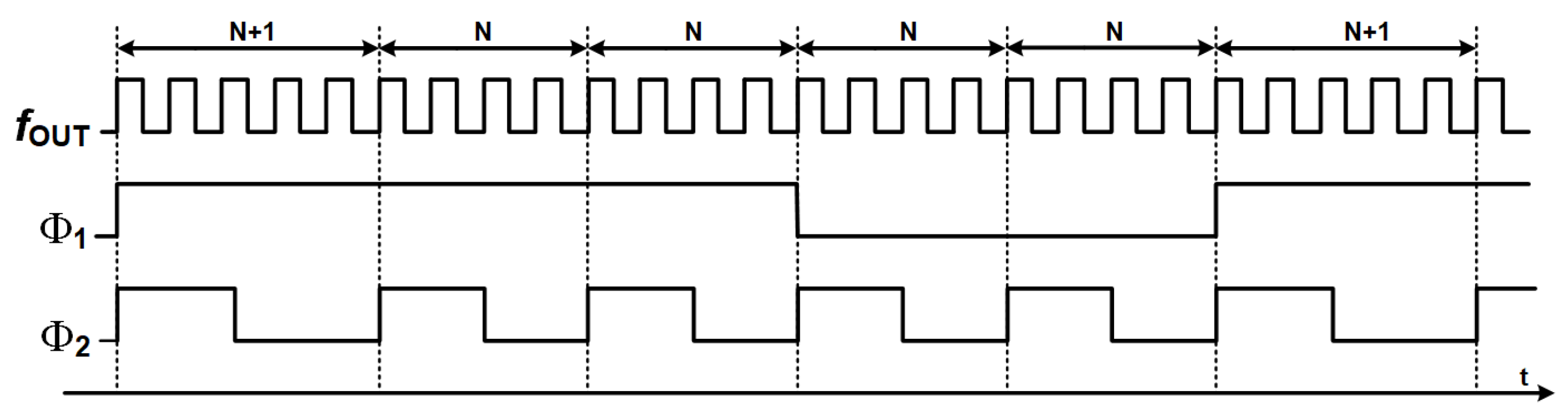

Traditional PLL-based frequency synthesizers often rely on two main architectures: integer-N and fractional-N, each type with its own advantages and disadvantages. With integer-N, the PLL structure has superior phase noise performance and simplified loop dynamics, but is limited by coarse frequency resolution, as this resolution depends on the reference frequency [

6,

7,

8,

9]. Conversely, the fractional-N architecture overcomes this limitation by using delta-sigma

modulation on the feedback divider to create fractional multiplication ratios, thereby significantly improving frequency resolution. However, this approach introduces quantization noise, which degrades signal purity, especially within the loop bandwidth region [

10,

11]. Recent implementations have sought to mitigate these drawbacks by using advanced

modulators, digital pre-distortion techniques, and complex loop filter designs [

12,

13,

14]. Nevertheless, these methods often only solve one part of the performance trade-off problem and can lead to a significant increase in both power consumption and circuit complexity.

The explosion of wireless systems, energy-harvesting IoT nodes, wearable devices, and mobile devices has set a requirement to intelligently balance performance metrics with power consumption levels, especially when they must operate in strict temperature conditions [

15,

16]. Furthermore, the popularity of multi-standard transceivers demands that frequency synthesizers must be capable of supporting a very diverse range of channel spacings on the same single hardware platform [

17,

18]. This requirement spans from narrow-band IoT applications (≤25 kHz) to wide-band mobile systems (≥100 MHz).

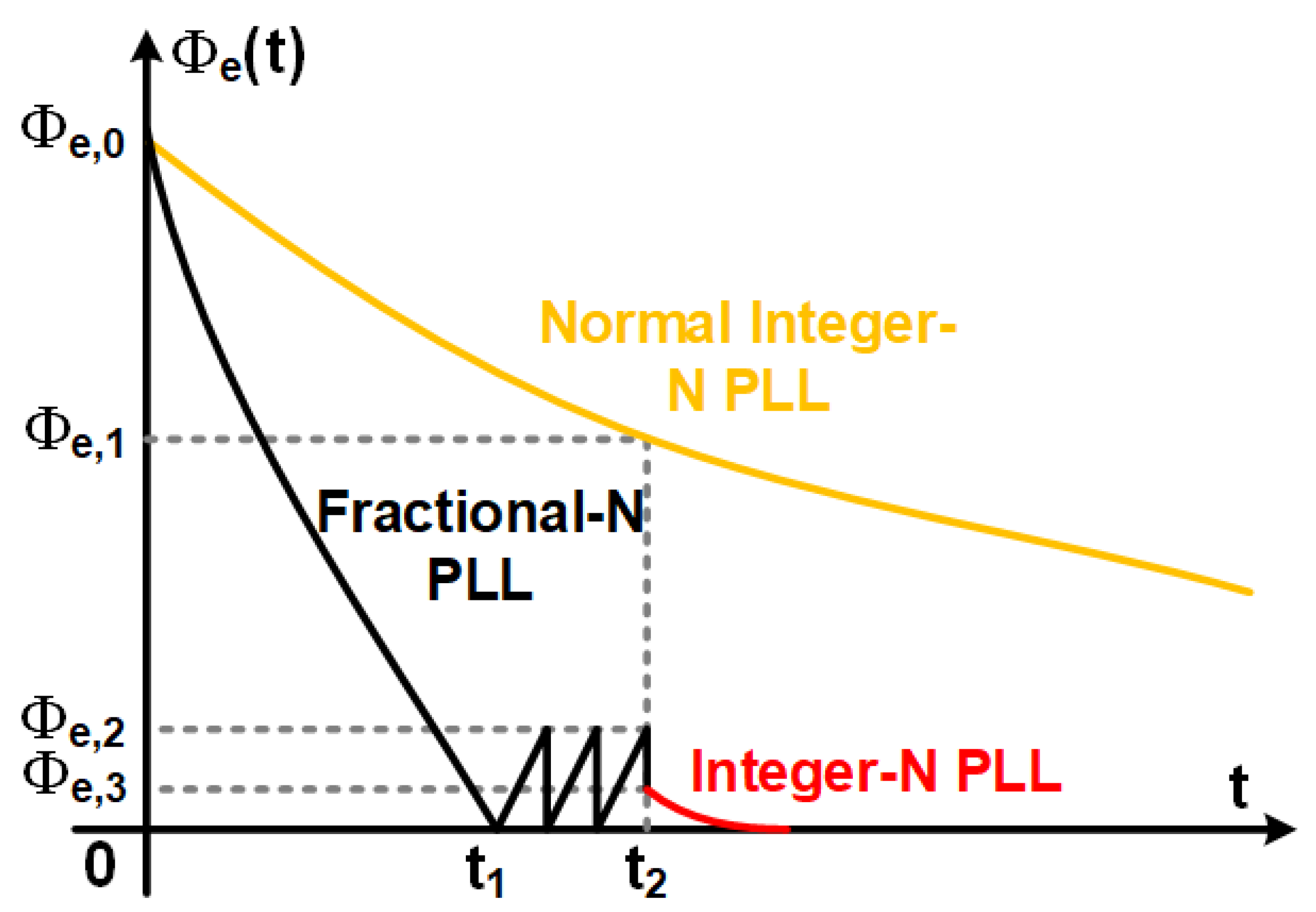

Some recent studies have explored adaptive phase-locked loop (PLL) architectures to address performance challenges [

19,

20]. These solutions include PLLs that can switch bandwidth by using reconfigurable loop filters, or dual-mode integer-N/fractional-N implementations for specialized applications [

21,

22]. However, existing adaptive PLLs face limitations that go beyond fast-lock capability and bandwidth reconfiguration. Recent dual-mode implementations have demonstrated the feasibility of mode switching but often rely on pre-determined timing mechanisms without real-time feedback from the loop dynamics. The approach can result in either premature transitions that compromise lock stability or delayed transitions that cause unnecessary power consumption. Furthermore, achieving phase noise performance better than −105 dBc/Hz at a 1 MHz offset, as required by the advanced modulation scheme, often necessitates oversized loop filters, which significantly increase both lock time and silicon area.

Additionally, the voltage-controlled oscillator (VCO)—the core frequency-generating component—is still a key factor, determining overall PLL performance in terms of phase noise, power consumption, and area [

23,

24]. The traditional LC-tank VCOs bring excellent phase noise performance but take up a large area and have a limited tuning range. Meanwhile, ring-oscillator-based VCOs are more compact but have significantly poorer phase noise characteristics. Quantitatively, LC-tank oscillators typically achieve phase noise around −120 to −125 dBc/Hz at a 1 MHz offset for frequencues near 5 GHz, but a single differential inductor can occupy 0.15–0.25 mm

2 in modern CMOS processes, which often represents 40–60% of the total PLL area. Additionally, varactor-based tuning provides limited frequency coverage (typically 15–20%)

Recently, inductorless VCO structures have emerged as a promising alternative solution to balance between area and acceptable noise performance [

25,

26]. Nevertheless, current methods still have a number of serious limitations: suboptimal switching mechanisms (based on pre-determined time), inadequate noise filtering in fractional mode, and a limited reconfigurable bandwidth range. These solutions also often consume a lot of energy for mode switching and control circuitry: (1) suboptimal switching mechanisms that rely on pre-determined timing rather than real-time loop dynamics, (2) inadequate noise filtering in fractional mode leading to spurious tone generation, (3) limited bandwidth reconfiguration range constraining adaptation flexibility, (4) substantial power overhead associated with mode switching and control circuitry, and (5) VCO designs that either consume an excessive silicon area or compromise phase noise performance [

27,

28]. Moreover, conventional approaches lack intelligent switching algorithms that can predict optimal transition points based on phase error dynamics, resulting in unnecessary switching overhead and potential stability issues [

29,

30].

Beyond architectural innovations, system-level integration plays a critical role in achieving practical efficiency. Recent ASIC implementations have shown that co-integrating frequency synthesizers with signal processing blocks reduces power consumption and enables compact designs essential for IoT and wearable devices. These hardware integration considerations further motivate adaptive PLL designs that can be efficiently embedded within larger System on Chip (SoC) platforms [

1,

4,

5].

In battery-powered IoT devices, the dual-mode allows the PLL to “wake up” and lock frequency quickly to transmit data (wide-band mode), then return to a power-saving narrow-band state, helping to extend battery life. For 5G networks, this capability is critical for agile frequency hopping to support various frequency bands and standards, where the wide-band mode ensures fast channel switching and the narrow-band mode meets the extremely low phase noise requirements of complex modulation schemes (such as 256-QAM). Therefore, the dual-mode PLL architecture directly addresses the conflicting demands of speed and precision in modern wireless communication systems [

17,

18].

This paper presents a new adaptive bandwidth PLL architecture, seamlessly integrating integer-N and fractional-N synthesis modes with smart switching control to achieve an optimal energy-performance balance in diverse operating conditions. The proposed system exploits wide-band integer-N operation for quick lock acquisition, then dynamically switches to narrow-band fractional-N mode for high-resolution synthesis and improved noise performance. The main proposals include (1) a reconfigurable bandwidth loop filter with continuous adaptation capability over more than two decades of bandwidth variation, (2) a smart switching controller monitoring real-time phase error dynamics to predict optimal mode transitions, (3) a new adaptive digital noise filter with the ability to effectively suppress quantization noise without requiring a conventional synchronous delay line, and (4) a multi-loop architecture combining high-resolution digital phase detection to enhance frequency accuracy in both operating modes.

The remainder of this paper is organized as follows:

Section 2 presents the architectural overview and theoretical analysis of the proposed adaptive PLL system.

Section 3 details the circuit implementation, including the bandwidth-reconfigurable loop filter, intelligent switching controller, and adaptive noise-filtering techniques.

Section 4 provides comprehensive experimental validation, demonstrating 70% lock time improvement, −119 dBc/Hz in-band phase noise, 1

integrated jitter, and 13.2 mW power consumption in 180 nm CMOS technology. Finally,

Section 5 concludes with performance comparisons and discusses applications in next-generation wireless communication systems.

3. Circuit Implementation

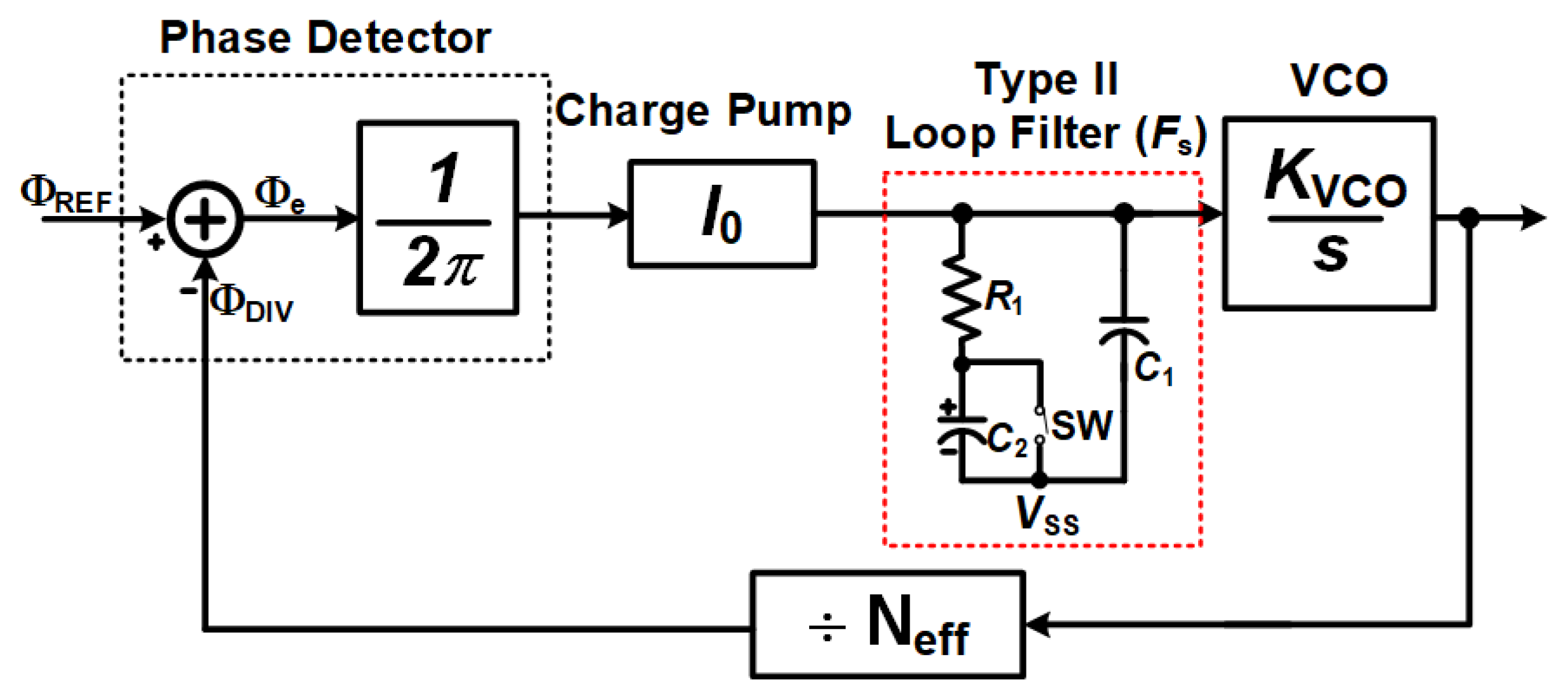

3.1. Bandwidth-Reconfigurable Loop Filter

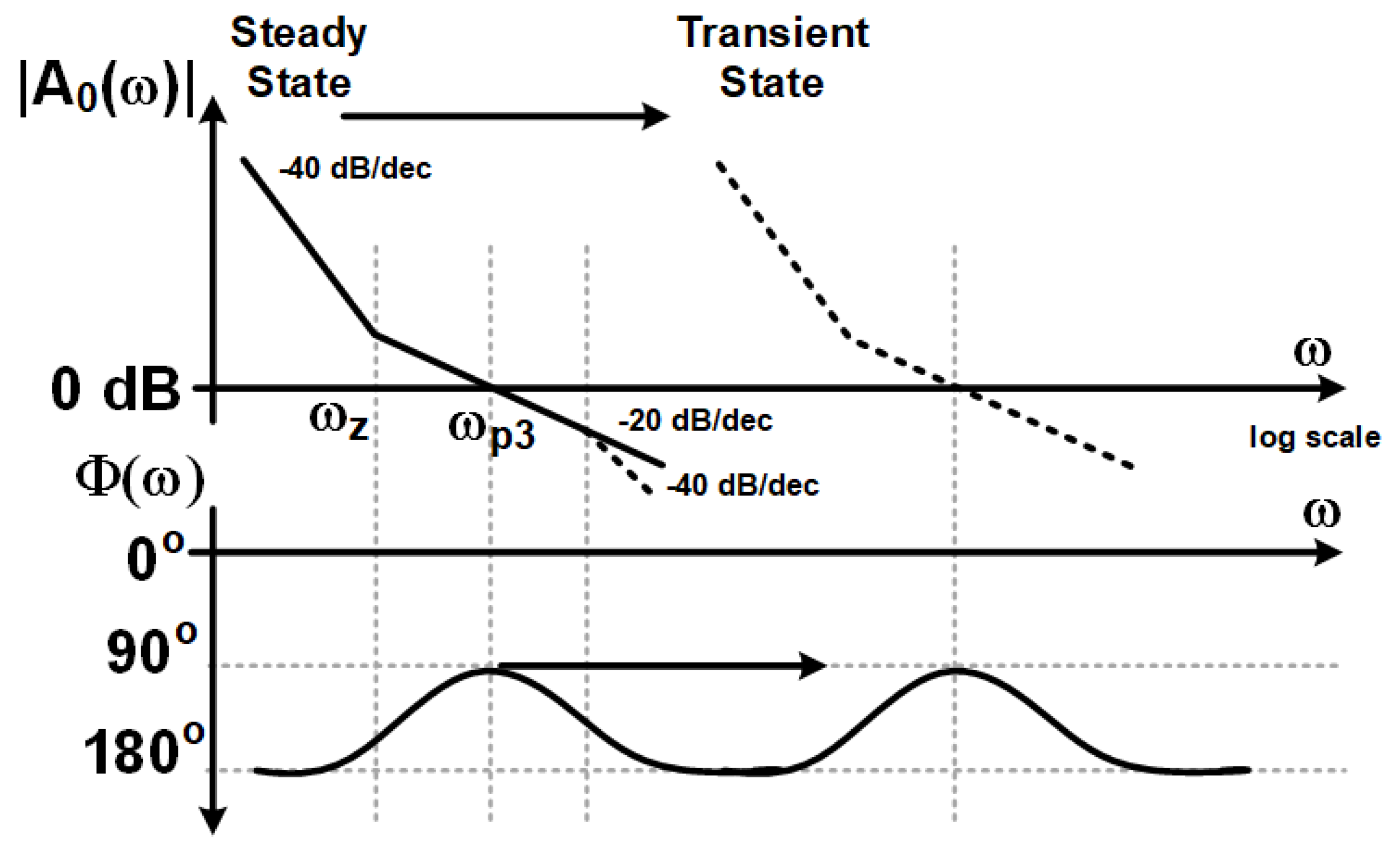

The loop filter in the proposed PLL (

Figure 5) is implemented as a type-II second-order filter with a zero, featuring bandwidth reconfigurability through the insertion of a programmable capacitor branch. In the linear model, the loop dynamics are characterized by the natural frequency

and the damping factor

. For an RC filter with a single zero, the transfer function can be expressed as shown in Equation (

6):

The open-loop gain (Equation (

7)) is given by the following:

where

denotes the gain of the PFD/charge pump,

is the VCO sensitivity, and N is the effective division ratio. Matching the characteristic equation to the standard second-order form

yields Equation (

8):

To enable bandwidth reconfiguration, an auxiliary capacitor

is switched in parallel with

. Thus, with Equation (

9),

leading to two distinct natural frequencies (Equation (

10)):

In the wide-band mode,

increases significantly, reducing the lock time according to Equation (

11).

Conversely, the narrow-band mode is activated once the PLL approaches a steady state to improve in-band noise performance. To avoid jitter peaking during the mode transition, the ratio

must be maintained constant, which can be achieved by scaling

accordingly or by employing a tunable OTA

to shift

proportionally.

From a noise perspective, the VCO noise transfer follows Equation (

12):

indicating that expanding the loop bandwidth suppresses VCO noise over a broader offset range. By contrast, reference noise, PFD/CP noise, and

quantization noise pass through the loop according to Equation (

13):

So, narrowing the bandwidth effectively reduces their impact at the output. Furthermore, quantization noise from the

modulator is further suppressed by an additional noise-filtering block

(Equation (

14)):

Finally, the transition between the two modes is governed by phase error thresholds. When both the phase error magnitude

and its slope

fall below predefined thresholds for a holding period

, the system switches from wide-band to narrow-band operation. This ensures a smooth transition without inducing overshoot or spurious tones. A schematic diagram of a zero-biased second-order type-II loop filter with a programmable condenser arm is shown in

Figure 3. The condenser arm is switched on/off via a switch to vary the time constant, allowing bandwidth reconfiguration: widening during the lock-in phase to shorten the convergence time, and narrowing during steady state to improve in-band noise.

3.2. Intelligent Switching Controller

To fully exploit the benefits of the reconfigurable loop filter, the system requires an intelligent switching controller (ISC). In conventional PLL designs, bandwidth or mode changes are typically performed through static logic signals or manual control, which can easily lead to instability or spur generation when the transition is not synchronized. In contrast, the ISC in the proposed architecture is capable of monitoring the dynamics of the phase error and the quantization noise level from the modulator, thereby making real-time adaptive decisions for mode switching.

In principle, the intelligent controller continuously monitors the output of the phase detector, tracking both the frequency and the amplitude of the phase error pulses. When the amplitude of the phase error falls below a predefined threshold and the slope of the phase error also drops below a certain limit, the ISC determines that the loop has approached a near-lock state. At this point, the loop filter is commanded to narrow its bandwidth, thereby improving noise performance. If abnormal oscillations or jitter peaking occur during the transition, the ISC can automatically reverse the configuration and restore the wide-bandwidth mode to maintain loop stability.

A key contribution of the ISC is the exploitation of modulator outputs to predict in-band noise levels. Rather than relying solely on the magnitude of the phase error, the controller also considers the spectral properties of the sequence, enabling bandwidth switching decisions to be made more appropriately and avoiding premature or delayed reconfiguration. This approach significantly reduces spurs caused by quantization noise in fractional-N mode, while maintaining a fast dynamic response in integer-N mode.

From an implementation perspective, the ISC can be realized as a finite state machine (FSM) combined with a digital monitoring unit. The FSM defines states such as acquisition, transition, and steady state, while the monitoring unit provides trigger signals based on the mean and variance of the phase error over a defined observation window. Owing to its fully digital architecture, the ISC consumes very low power, is easily integrated on-chip, and does not require complex hardware such as delay lines or auxiliary analog detectors, as shown in

Figure 6.

System-level simulations demonstrate that the ISC enables a smooth transition from integer-N mode to fractional-N mode without introducing significant jitter peaking, while ensuring the stability of the PLL control range. Furthermore, the timely reconfiguration of the loop bandwidth shortens the lock time compared to a fixed narrow-bandwidth design and reduces in-band spurs compared to a fixed wide-bandwidth design.

3.3. Adaptive Digital Noise Filter

3.3.1. Quantization Noise Suppression

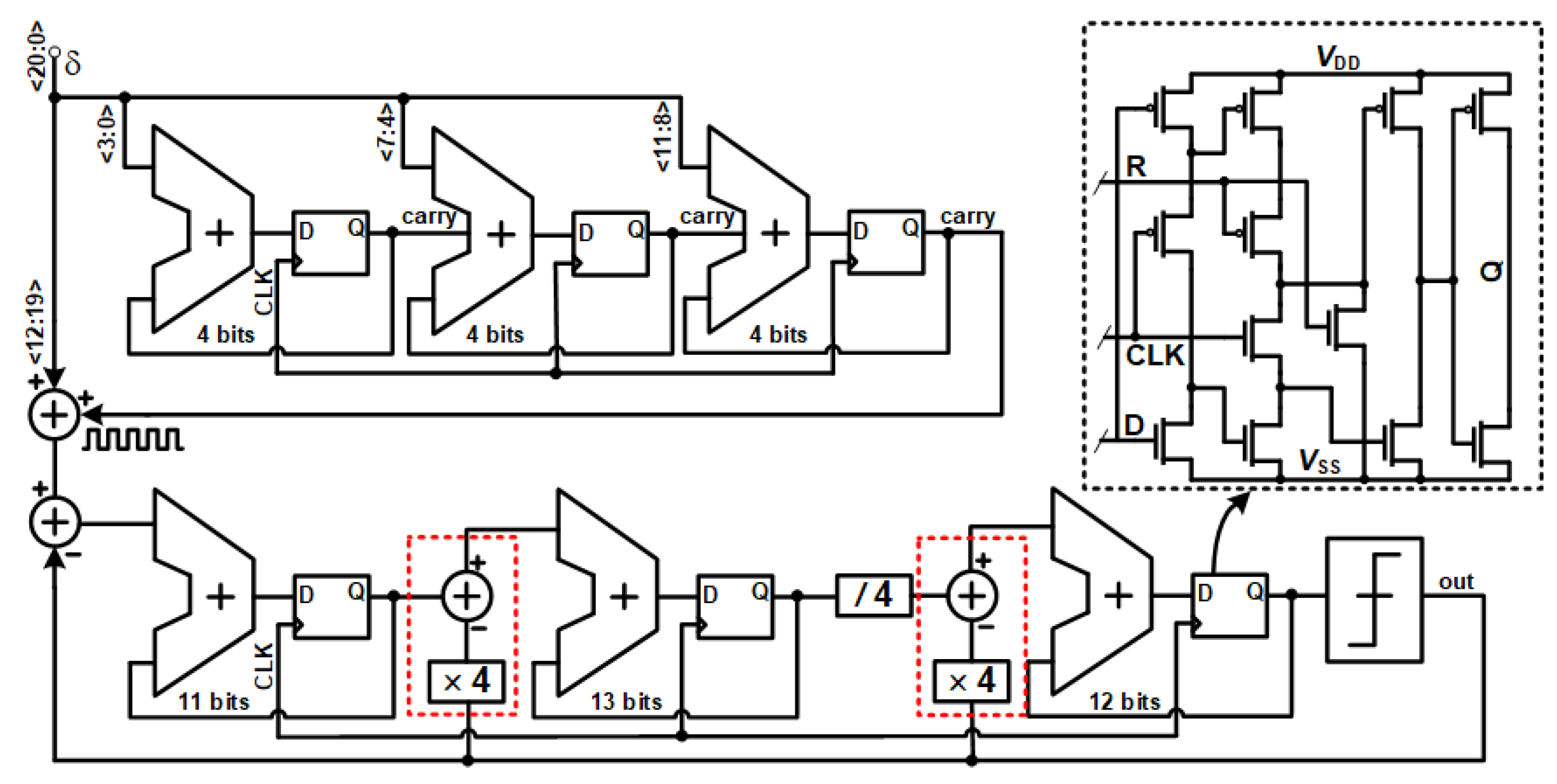

To realize a high-performance digital delta-sigma modulator in

Figure 7, the proposed hybrid architecture splits the input signal processing path (

<20:0>) into two parallel streams to optimize for speed and noise performance. The processing path for the Low-Significant Bits (LSBs), which include bits from

<0> to

<11>, uses a pipelined accumulation structure consisting of three 4-bit adders and their corresponding registers. This pipelining technique circumvents the critical transfer-memory path, allowing the entire circuit to operate at GHz clock frequencies. Furthermore, a dithering signal is introduced to linearize the quantization process and suppress spurious harmonics.

At the same time, the modulator core processes the Most Significant Bits (MSBs), from

<12> to

<20>, through a complex, high-order feedback integrator structure. This structure, which consists of an 11-bit adder and two 13-bit adders, aggressively shapes the noise transfer function (NTF). The weighted feedback coefficients (represented by ×4 and /4 bit-shifting operations) are optimized to place the NTF’s poles, thereby ensuring loop stability and limiting the out-of-band gain. At the final stage, in addition to the main 1-bit output (out) used to control the frequency divider, the architecture also extracts a multi-bit word (<10:0>) from the accumulator’s internal state. This signal enables the implementation of advanced quantization error cancellation techniques via a peripheral block such as DTC, achieving extremely high spectral purity. In terms of hardware resources, the design requires a total of six adders and approximately 50 single-bit registers (flip-flops). So, the noise transfer function of the three-order filter is shown in Equation (

15):

Figure 8 illustrates the calculated figure of merit (FoM) of the third-order

modulator in (a), and the simulated SNR and SNDR characteristics of the proposed PLL as a function of the input amplitude in (b).

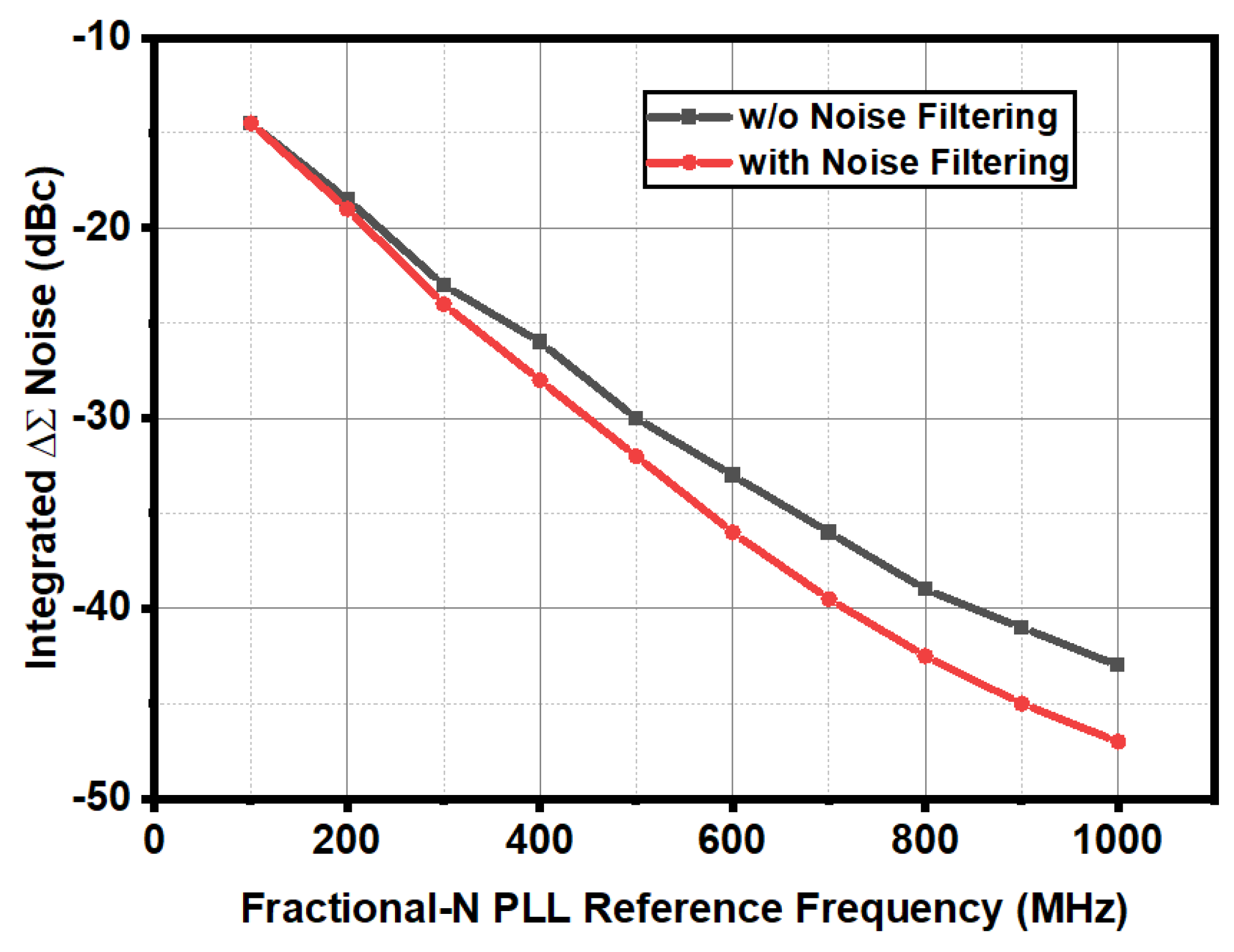

3.3.2. Noise-Filtering Architecture

This architecture presents an an advanced hybrid noise-filtering solution, combining analog and digital processing within a two-stage structure, specifically designed to suppress the complex quantization noise generated by modulators. The core principle is an effective partitioning of the filtering task: the analog stage handles the coarse, high-power processing, while the digital stage performs the fine, precise, and flexible processing.

The first stage, operating entirely in the analog domain, has the primary objective of suppressing the out-of-band noise component, where the spectral power density of the quantization noise is highest. To achieve this, a continuous-time notch filter is used. The biggest challenge in implementing this filter on a CMOS-integrated circuit is the area limitation and the low quality factor (Q-factor) of passive spiral inductors. The applied technical solution is to build an active inductor based on a gyrator structure, which is formed from two transconductors (

). This structure allows for the synthesis of an equivalent inductance (

) according to Equation (

16):

where

is a terminating capacitor and

,

are the transconductance values. This technique not only creates a virtual inductor with a large value and a high Q-factor within a compact area, but also allows for the adjustment of the notch frequency by changing the

value, providing a certain degree of flexibility to this coarse filtering stage.

The second stage, operating in the digital domain, is designed to handle the remaining noise components, especially the spurious tones that can randomly appear inside the signal band (in-band). This stage requires high precision and programmability; therefore, a Switched-Capacitor (SC) Filter is used, as shown in

Figure 9. This hybrid filtering approach offers several advantages over alternative implementations. Passive LC notch filters, while providing superior linearity, require large spiral inductors (typically >50 nH) that consume 0.1–0.2 mm

2 and exhibit low Q-factors (5–10) in standard CMOS processes, limiting their noise suppression to 20–25 dB. Purely digital FIR/IIR filters provide excellent programmability but introduce additional quantization noise and demand high-speed clocking that increases power consumption by 2–3× compared to our approach. Gm-C continuous-time filters, although compact, lack the sharp notch characteristic necessary for effective

quantization noise rejection and show higher sensitivity to PVT variations. Our gyrator-based implementation achieves >30 dB suppression at the notch frequency within <0.01 mm

2, while maintaining tunability through

adjustment. The combination with the digital SC stage enables programmable in-band spurious suppression without the power penalty of fully digital solutions, as demonstrated in

Figure 10.

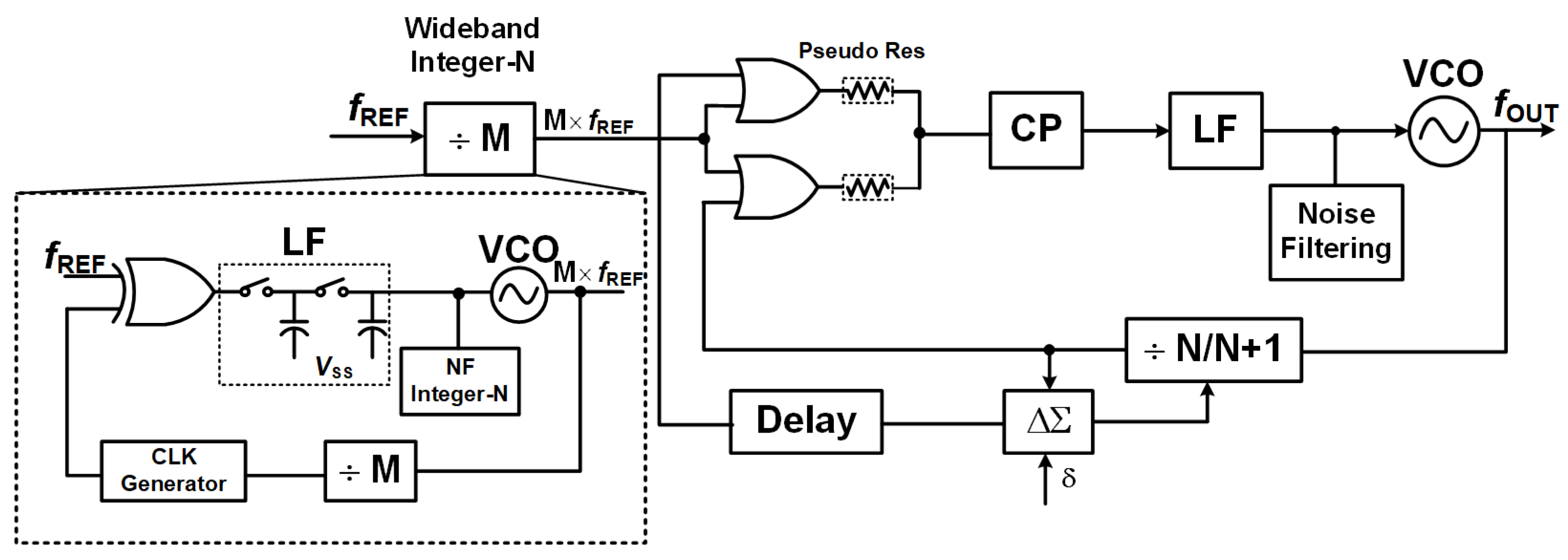

3.4. Multi-Loop Architecture with High-Resolution Phase Detector

Figure 11 shows the proposed multi-loop PLL architecture; two XOR phase detectors are used to replace the conventional PFD. The choice of XOR arises from its notable advantages: low hardware complexity, extremely-low-power consumption, and the ability to generate a phase error signal with high linearity within the ±90° range. In particular, by combining two XOR detectors operating in different modes, the system can simultaneously achieve an extended dynamic range and improved phase detection resolution.

In the multi-loop structure, one XOR detector is configured for the wide-bandwidth integer-N loop, allowing the circuit to quickly converge toward the lock state thanks to its fast response to large phase errors. The second XOR detector is connected to the narrow-bandwidth fractional-N loop, operating in the steady state after the PLL has nearly locked, and is responsible for fine phase adjustment with high resolution. By dividing the roles between the two XORs, the architecture exploits the fast convergence of the integer-N loop while ensuring optimal noise characteristics in the fractional-N loop.

To avoid spur generation and jitter peaking during the transition, the phase error signals from both XOR detectors are fed into the intelligent switching controller. This controller simultaneously monitors the amplitude of large phase errors (reported by the first XOR) and small phase errors (reported by the second XOR). When the error is determined to lie within the narrow linear region, the system gradually transfers control to the fractional-N loop. This combination ensures that the transition between the two loops occurs smoothly without causing instability.

Another important advantage of using XOR detectors instead of the conventional PFD is the significant reduction in area and power overhead. XOR requires only a small number of CMOS transistors, does not need complex reset circuitry, and does not generate wide pulses (dead-zone free). This makes it particularly suitable for IoT and mobile applications, where ultra-low power and high integration are essential.

Simulation results show that the multi-loop architecture using two XOR detectors can achieve a much faster lock time compared to a single-loop PLL using only one XOR, while maintaining low phase noise in the fractional-N mode. This combination demonstrates that even with a simple phase detection element such as XOR, when properly deployed in a multi-loop structure, it can achieve performance comparable to or better than more complex PLL designs.

3.5. Compact Inductorless VCO

Various oscillator topologies can be employed in PLL designs, each offering distinct trade-offs. Relaxation oscillators [

31,

32] provide excellent power efficiency and large tuning range but typically suffer from poor phase noise due to their switching-based operation and sensitivity to supply noise. LC-tank oscillators deliver superior phase noise performance but require large inductors that consume a significant area. This paper proposed a ring oscillator topology due to its compact silicon footprint (<0.001 mm

2), wide tuning range, and compatibility with standard digital CMOS processes without requiring specialized passive components. While the phase noise is higher than LC alternatives, this design achieves adequate performance for the target applications through careful bias current control and transmission-gate-based delay tuning.

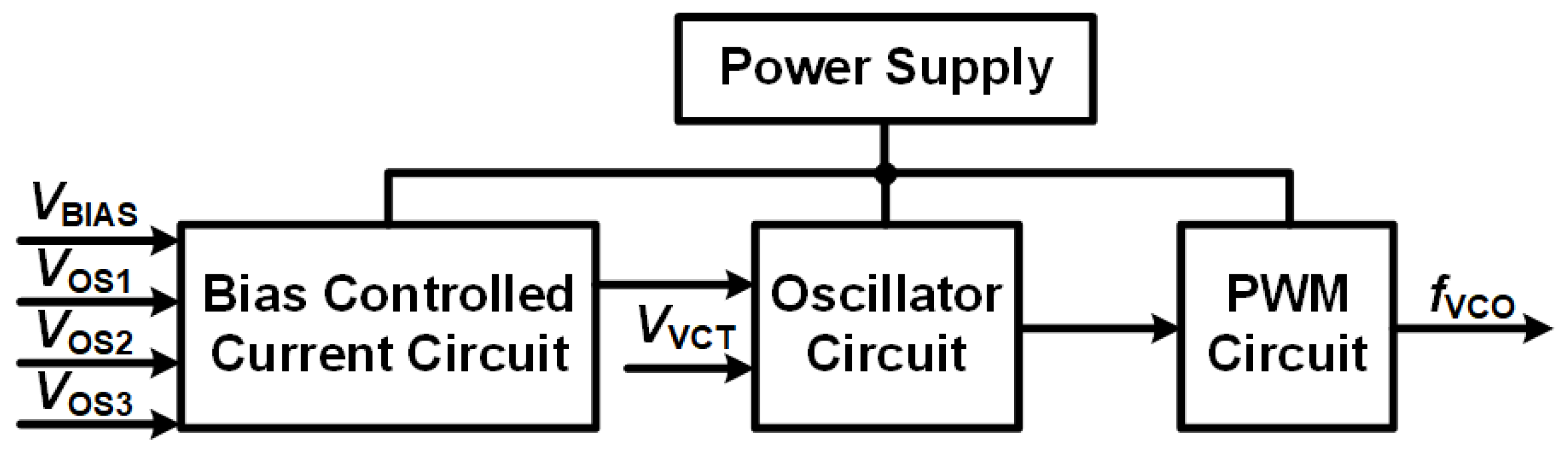

The VCO architecture consists of three main blocks: the bias current control circuit, the oscillator circuit, and the pulse-width modulation (PWM) circuit, as illustrated in

Figure 12. The focus of the whole circuit design is the bias current control circuit, which regulates the current levels supplied to the oscillator stages based on the input bias voltages

VBIAS,

VOS1,

VOS2,

VOS3. These voltages are used to independently adjust the bias conditions of the three delay stages in the ring oscillator, ensuring precise tuning and optimization of the oscillator’s performance.

The oscillator circuit is a ring oscillator composed of three stages, where the oscillation frequency is determined by the control voltage VVCT.

The bias controlled current circuit includes four current sources which are biased by a common control voltage VBIAS. By controlling the current levels in the inverters, the frequency of oscillation is adjusted. This configuration ensures precise tuning and efficient operation of the VCO while maintaining stability and linearity in its response to control inputs.

The three-stage ring oscillator in the proposed bias current-controlled VCO is designed using a combination of inverters and transmission gates to achieve precise frequency tuning, as illustrated in

Figure 13. Each stage of the ring oscillator consists of a standard CMOS inverter paired with a transmission gate. The control voltage

VVCT plays a central role in this configuration, as it modulates the resistance of the transmission gates by controlling their gate voltage. This modulation directly affects the delay introduced by each oscillator stage. As

VVCT increases or decreases, the resistance of the transmission gates adjusts accordingly, either increasing or decreasing the propagation delay in each stage of the oscillator. Since the total delay of the ring oscillator is the sum of the delays in all three stages, this mechanism provides an effective means to control the oscillation frequency of the VCO.

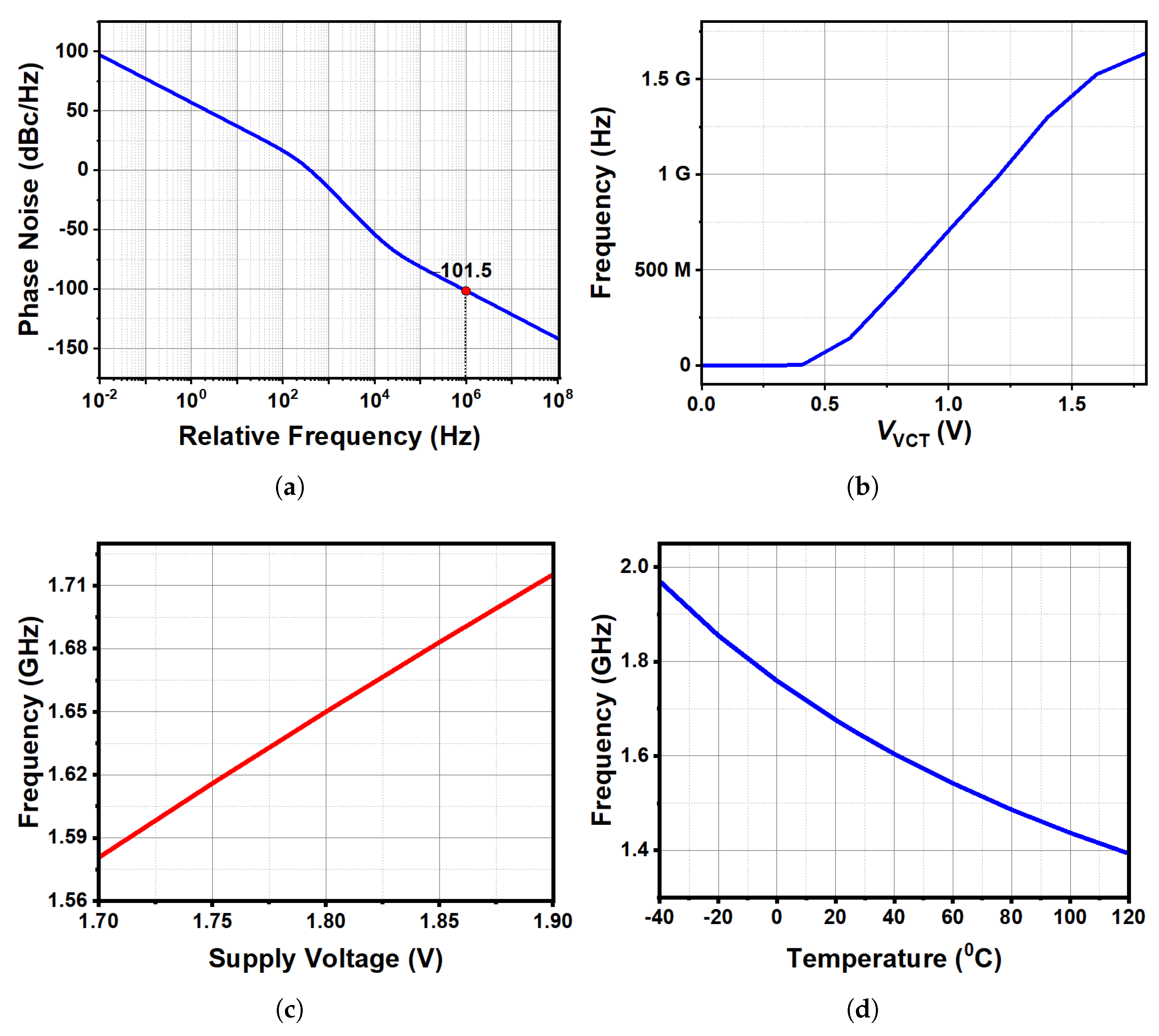

The cycle and frequency responses of the proposed three-stage VCO structure with a current control circuit, corresponding to variations in the control voltage

VVCT from 0 to 1.8 V, are illustrated in

Figure 14a. The entire system is designed and simulated using the 180 nm CMOS process, occupying an active chip area of 0.001 mm

2.

Figure 14b presents the phase noise performance of the VCO at 1 MHz of offset frequency and the oscillation frequency as a function of the control voltage

VVCT. The simulated oscillation frequency as a function of temperature is shown in

Figure 14c, and the supply voltage is shown in

Figure 14d.

This control voltage fine-tunes the delay of each stage, enabling the generation of a stable frequency output. The current control and oscillator circuits are closely integrated to achieve linear tuning behavior and minimize phase noise. Finally, the PWM circuit enhances the output signal by modulating its duty cycle. This block refines the output waveform, reducing the jitter and improving spectral purity. All blocks receive their control power from a dedicated power supply block, ensuring stable operation.

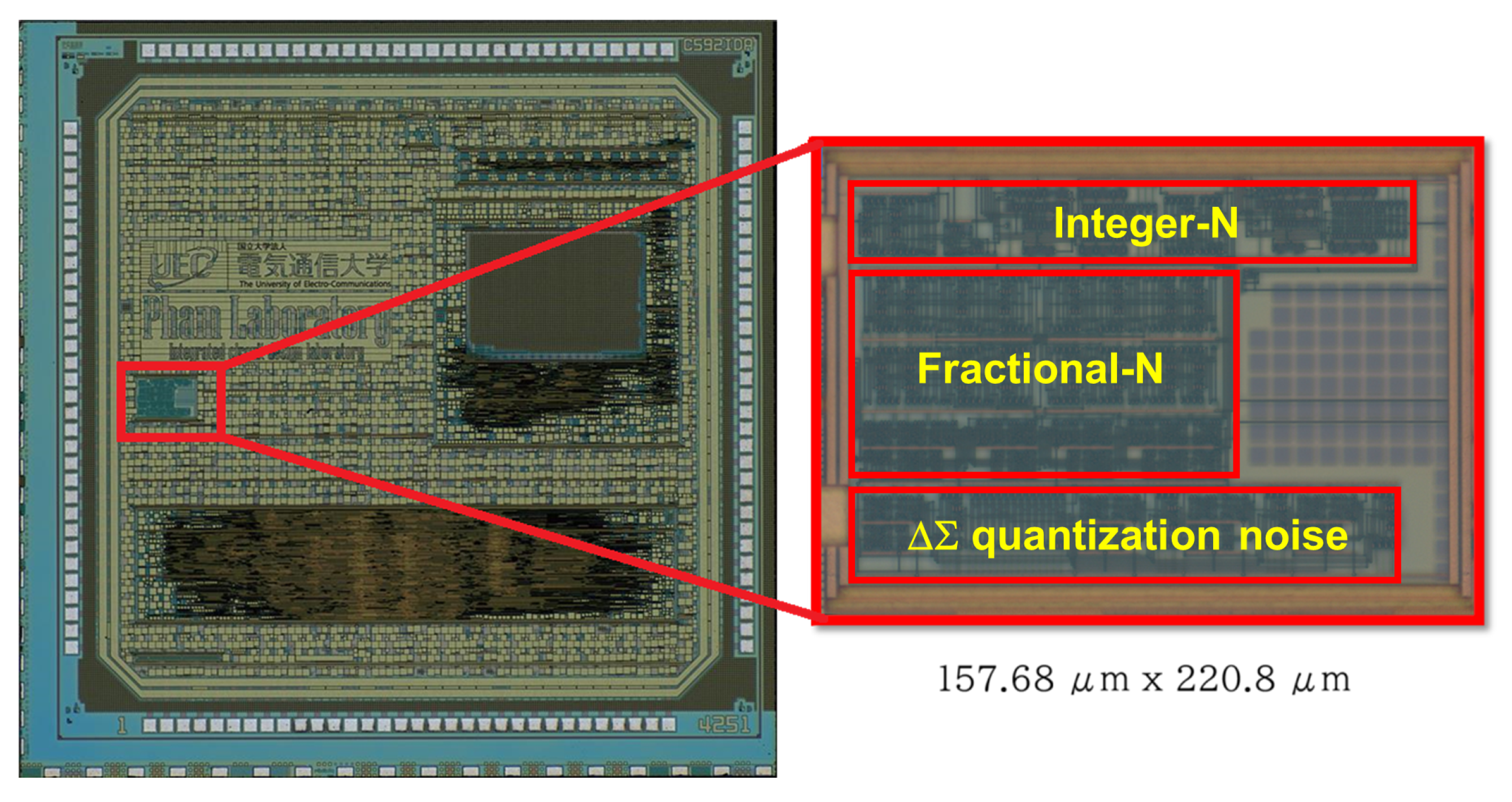

4. Experimental Results

The proposed dual-mode hybrid PLL with a bandwidth-reconfigurable loop filter and intelligent switching controller has been fabricated in a standard 180 nm CMOS process. The die micrograph is shown in

Figure 15, occupying an active area of 0.035 mm

2. The prototype employs a 25.5 MHz crystal oscillator as the reference and covers an output frequency range from 2.9 GHz to 3.2 GHz. Operating from a 1.8 V supply, the PLL consumes a total of 8.6 mW in fractional-N steady-state mode and 4.6 mW in integer-N acquisition mode. Within the total power, the VCO accounts for 2.3 mW, the divider and

modulator consume 3.13 mW, the charge pump and loop filter driver dissipate 1.0 mW, while the digital ISC and auxiliary noise-filtering circuits draw 0.2 mW and 0.5 mW, respectively.

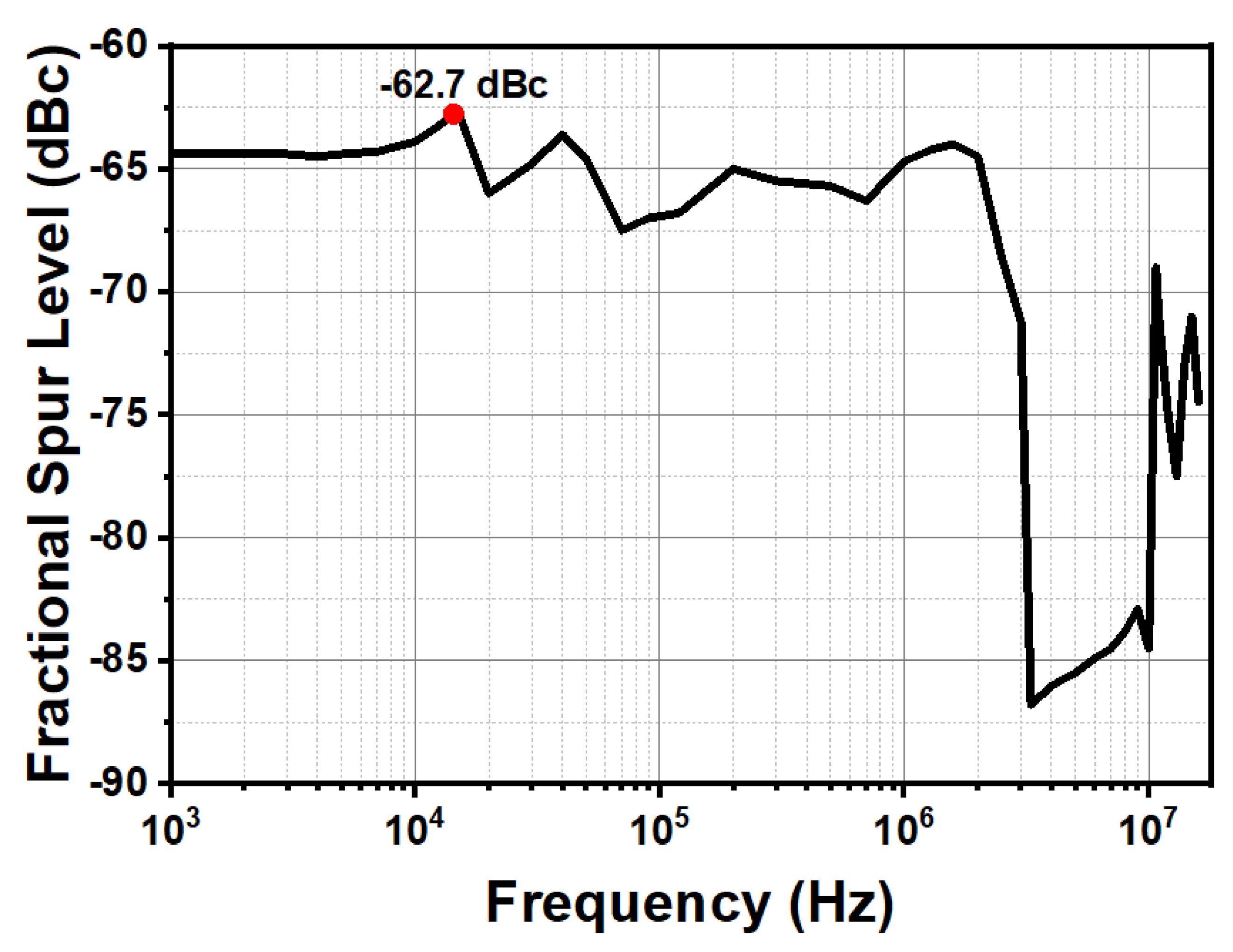

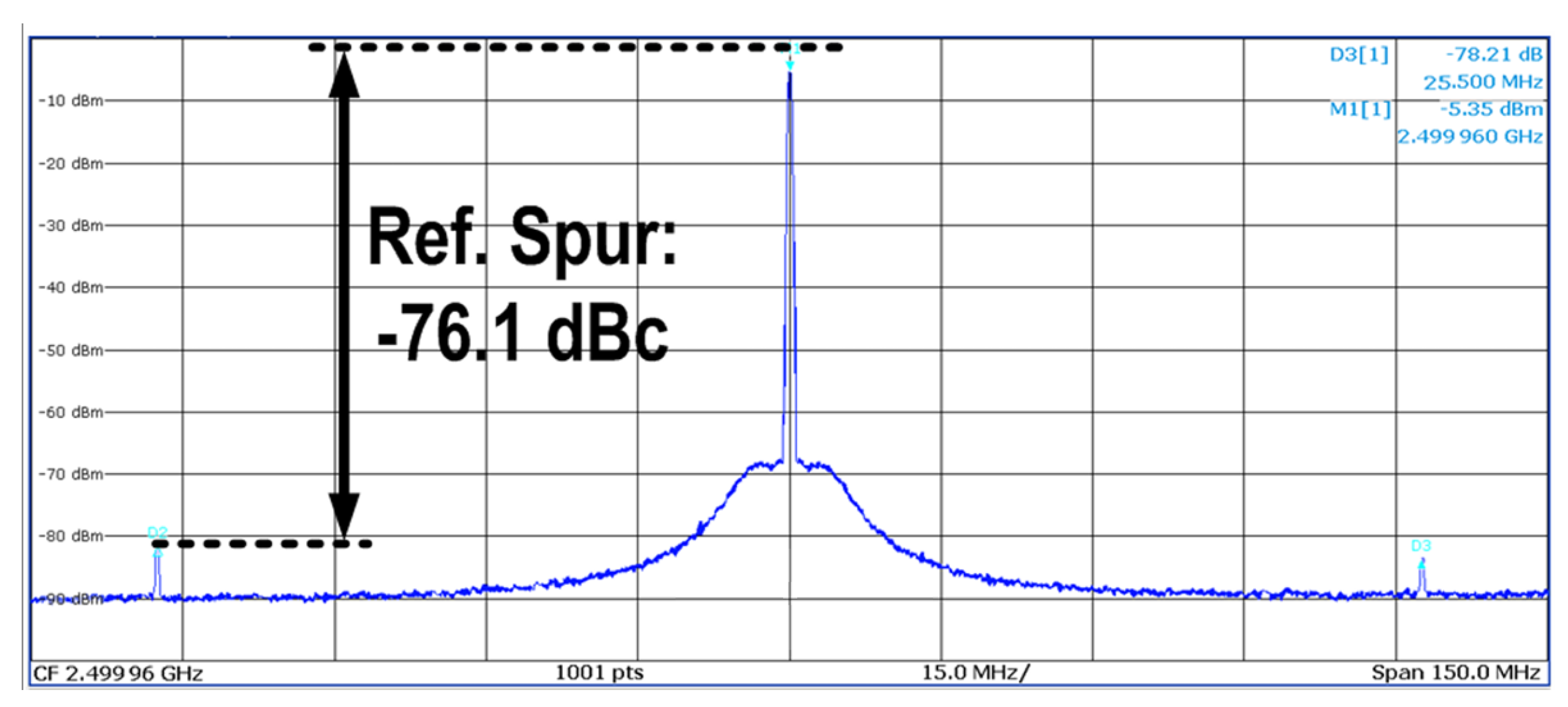

The measured output spectra are depicted in

Figure 16. With the adaptive noise filtering enabled, reference spur suppression improves by 15 dB at a 40 MHz offset, with the largest spur maintained below

dBc. The measured reference spur of PLL achieved

dBc, as shown in

Figure 17, and −119 dBc/Hz phase noise at 100 KHz, as shown in

Figure 18. These results confirm that the ISC enables seamless mode transition without introducing significant jitter peaking.

Table 1 summarizes the measured performance of the proposed architecture and compares it with representative state-of-the-art fractional-N synthesizers, after being scaled to a 28 nm process, following [

33]. The normalization of results from the 180 nm process to the 28 nm process aims to create a fair, technology-independent basis for comparison with current state-of-the-art works. This method helps to de-embed and emphasize the architectural innovations, thereby objectively evaluating the design’s potential without being affected by the limitations of the older process. Owing to its dual-mode operation, the prototype achieves both a fast-lock time of less than 5 μs (benefiting from the wide-band acquisition mode) and low in-band noise comparable to LC-VCO-based designs. The overall figure of merit (FoM) of −232.22 dB is competitive with state-of-the-art synthesizers, while the elimination of large on-chip inductors enables a compact and energy-efficient solution for mobile and IoT RF applications.

5. Conclusions

This paper introduced a novel dual-mode hybrid phase-locked loop architecture that marries the best features of both integer-N and fractional-N synthesis. It achieves this using a reconfigurable loop filter and a smart intelligent switching controller. The reconfigurable loop filter dynamically changes the loop bandwidth. This allows the PLL to operate in two distinct modes. (1) Wide-band integer-N mode: this mode provides rapid signal acquisition, meaning it locks onto the desired frequency very quickly. (2) Narrow-band fractional-N mode: this mode minimizes in-band noise, resulting in a cleaner output signal.

The intelligent switching controller is a key innovation. It monitors both the phase error and the noise from the modulator to manage the transition between these two modes. This adaptive control ensures the switch is seamless, preventing unwanted jitter peaking and minimizing spurious tones that can degrade signal quality. A prototype of the proposed PLL was built using a 180 nm CMOS process. It operates in the 2.9–3.2 GHz frequency range and delivers impressive performance of the following: (1) lock time: less than 5 microseconds; (2) in-band phase noise: −119 dBc/Hz in fractional-N mode; and (3) spur levels: below −62.7 dBc. The overall FoM is an impressive −228.8 dB, which is highly competitive with other advanced designs. Unlike many other high-performance synthesizers, this design avoids the need for large and power-hungry LC-based inductors, making it compact and energy-efficient.

These results confirm that the proposed architecture is a viable solution for modern RF systems, such as IoT and mobile communication devices, where a small footprint and low-power consumption are crucial. Future research will explore scaling the design to more advanced manufacturing processes (sub-10 nm) and using machine learning to further optimize its performance.