Research Trends and Challenges of Integrated Constant On-Time (COT) Buck Converters

Abstract

1. Introduction

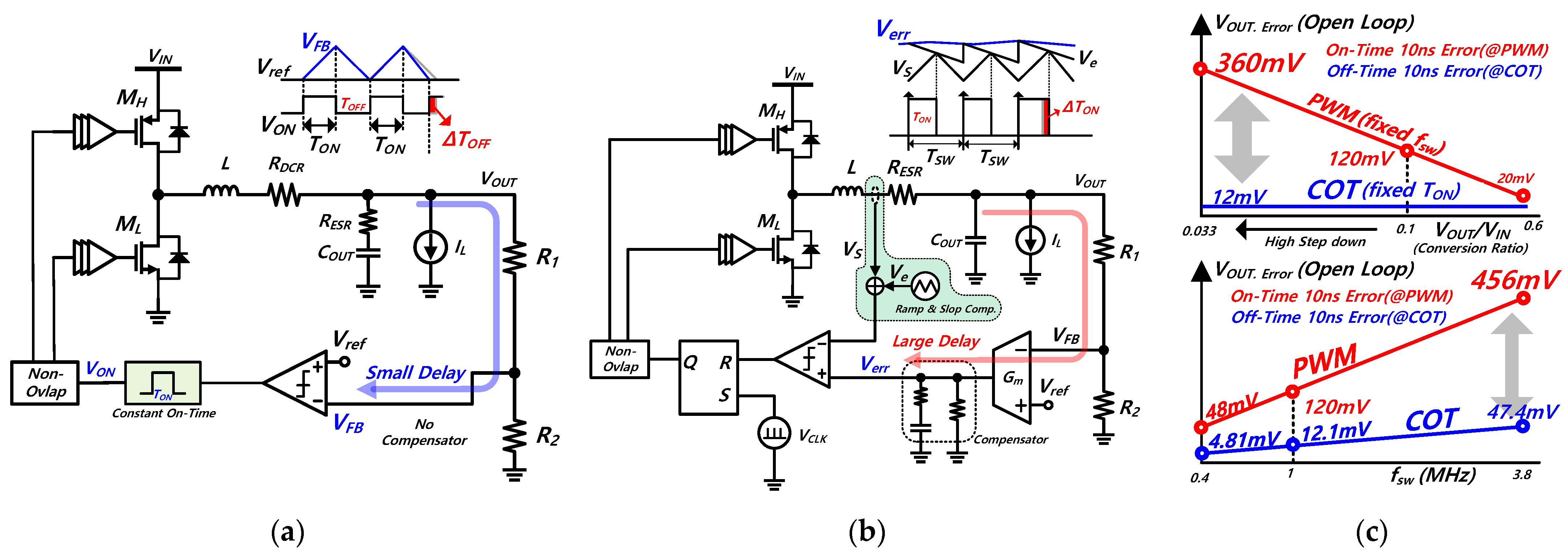

2. Conventional Constant On-Time Control

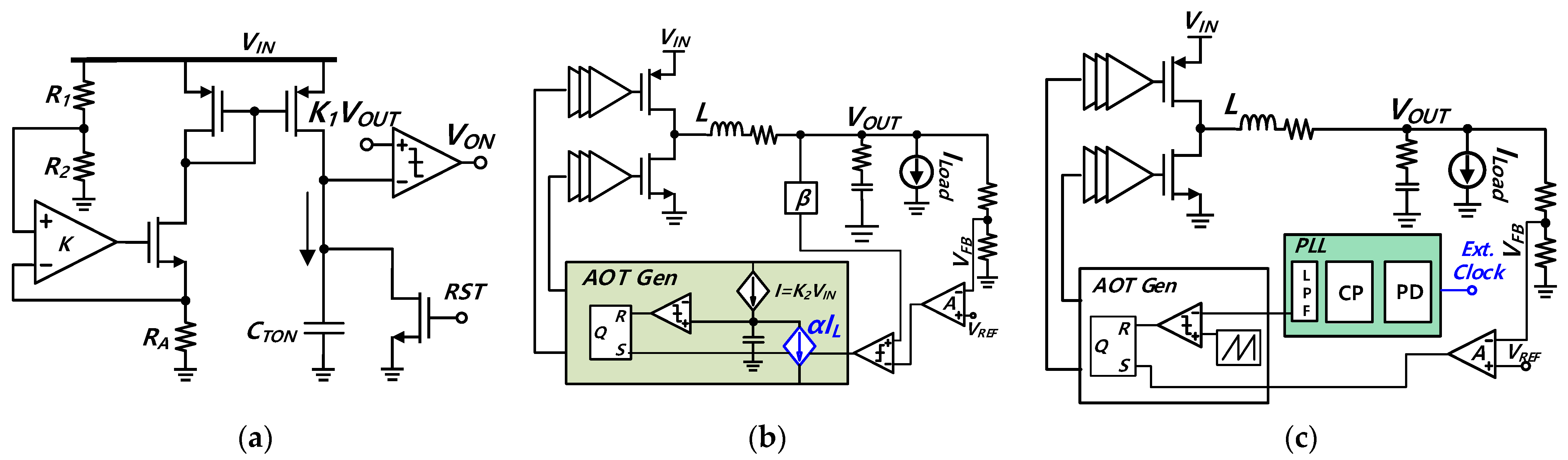

2.1. A Comparative Analysis of COT and PWM Control

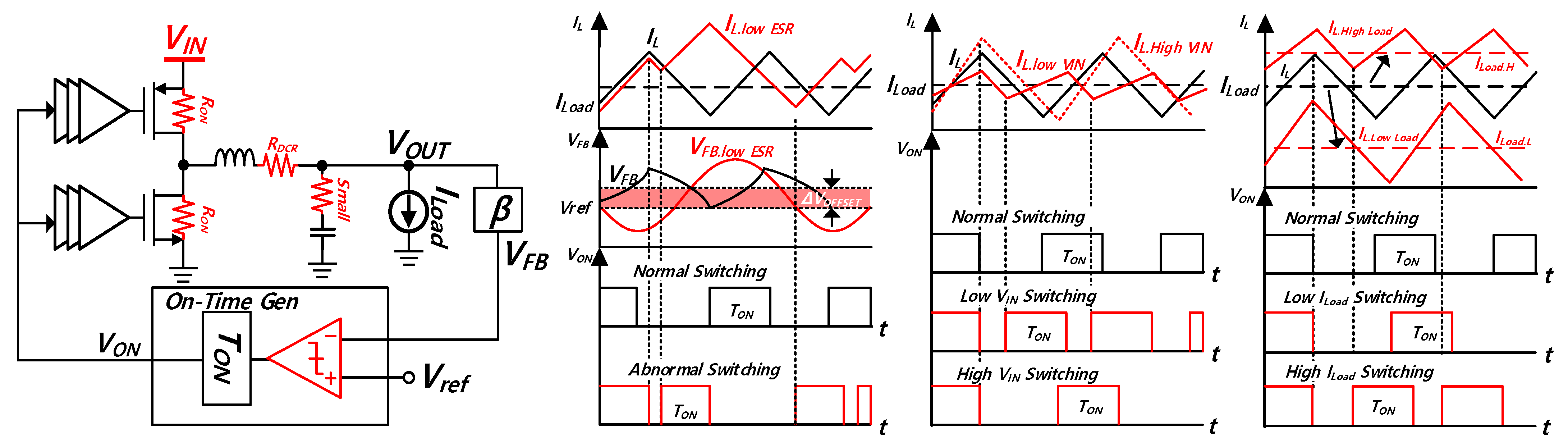

2.2. Low ESR Unstability and Frequency Deviation Issues of Conventional Constant On-Time (COT) Control

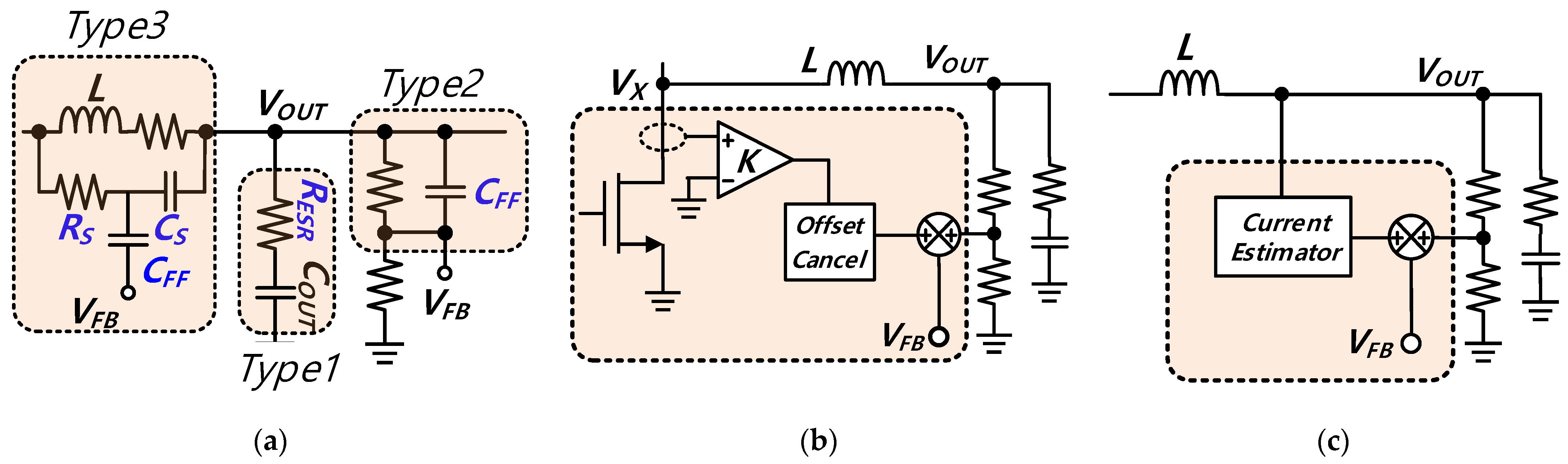

3. Ripple Injection and DC Offset Cancellation Techniques

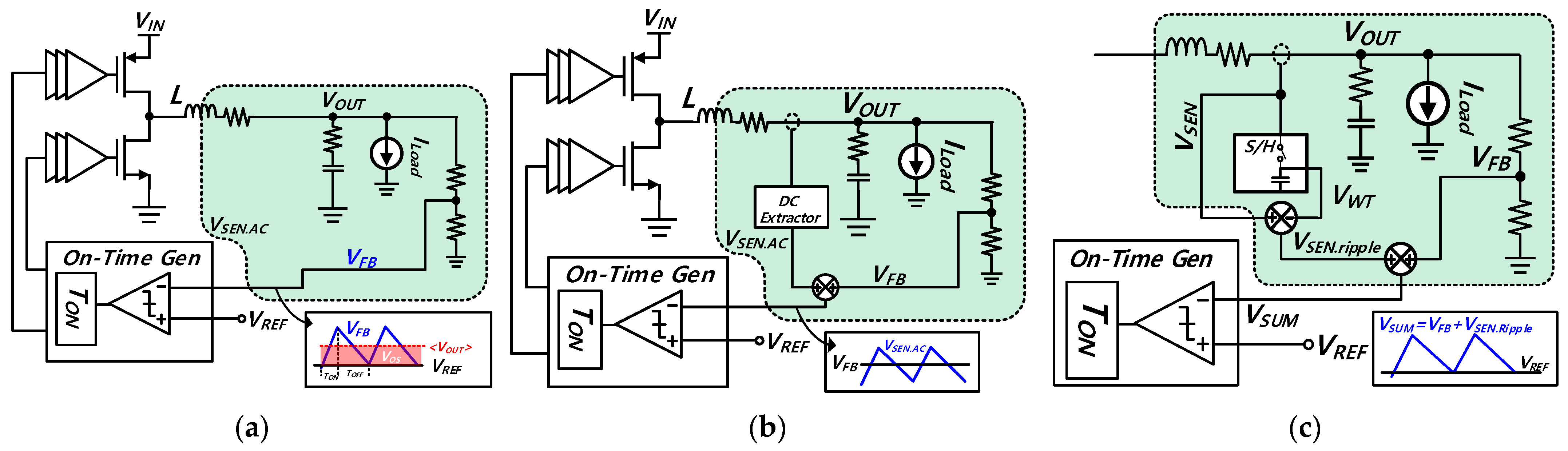

3.1. Ripple Injection Techniques

3.2. Offset Cancellation Techniques

4. Frequency Stabilization Techniques

4.1. Principle of Adaptive On-Time Control

4.2. Adaptive On-Time Techniques

5. Research Challenges of Constant On-Time (COT) Control in Integrated Circuits

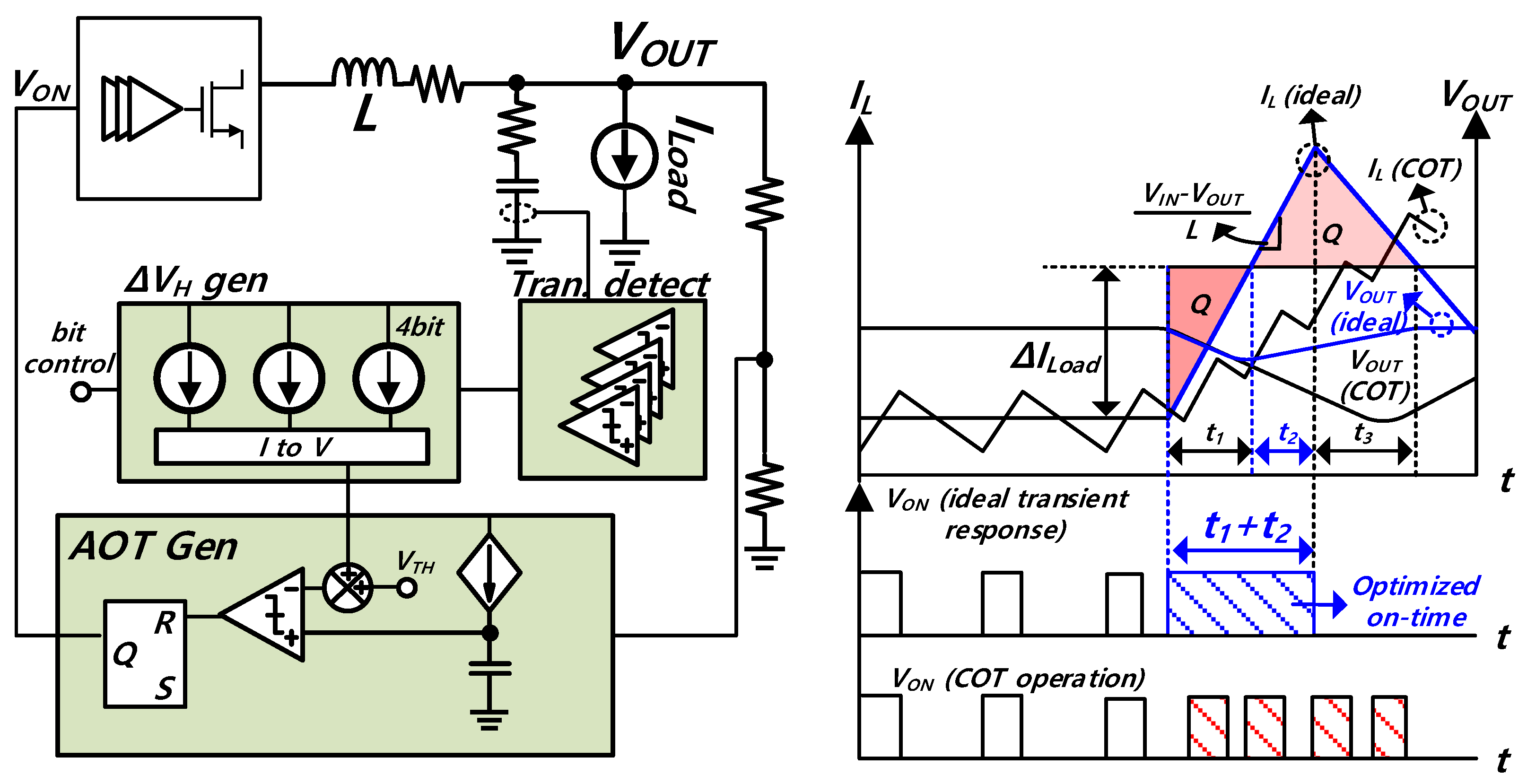

5.1. Load Transient Enhancement and Optimization Techniques

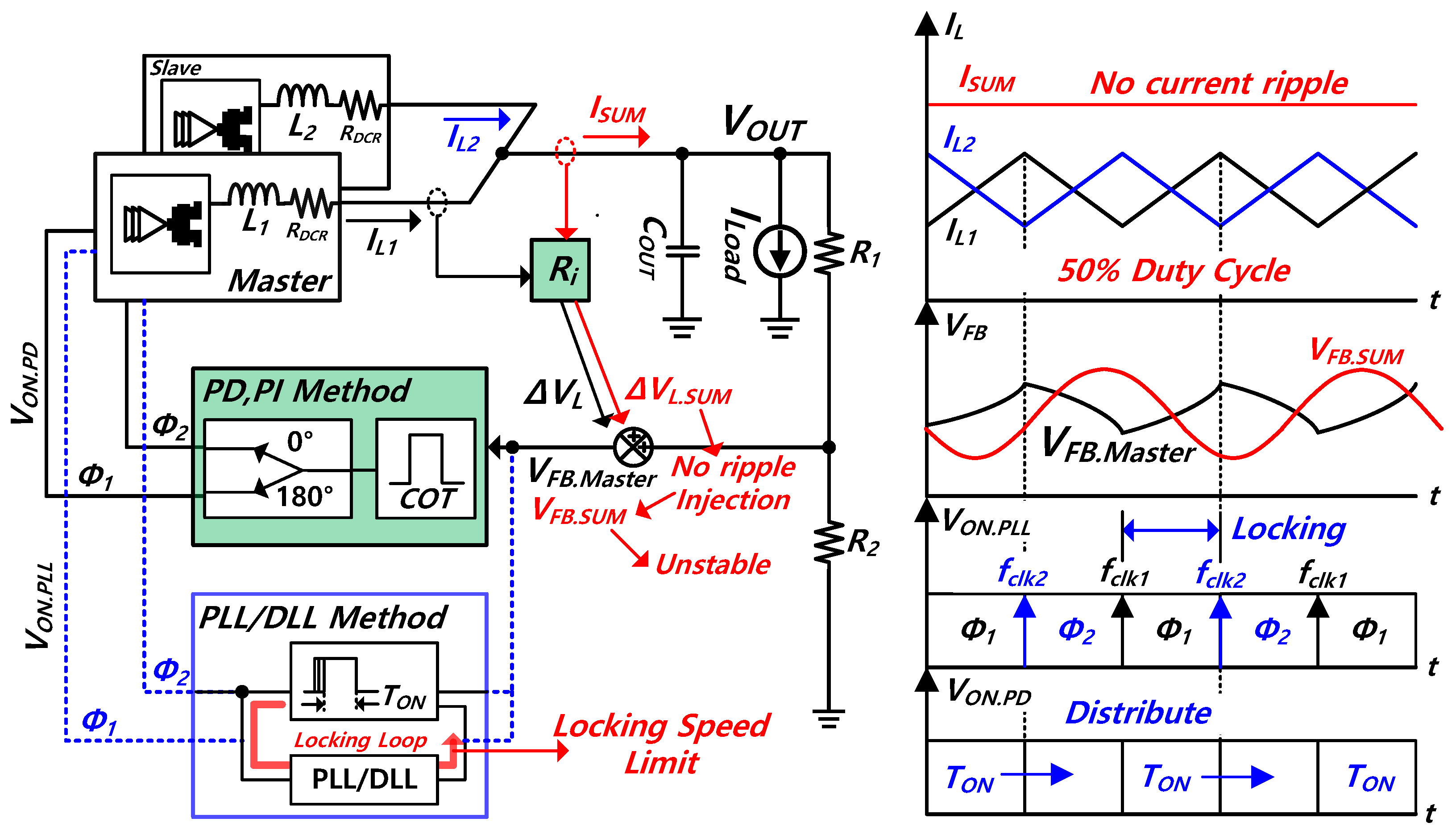

5.2. Multiphase Techniques

6. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Chung, T.; Kim, S.; Yoon, J.; Han, H.; Park, K.S.; Lee, H.; Yoon, H.-Y.; Lee, S.-K.; Lim, J.; Kwon, Y.; et al. A 10A/ls fast transient AOT voltage regulator on DDR5 DIMM with dithered pseudo-constant switching frequency achieving -6dB harmonic suppression. In Proceedings of the 2021 Symposium on VLSI Circuits, Kyoto, Japan, 13–19 June 2021. [Google Scholar]

- Texas Instruments. AN-1487 Current Mode Hysteretic Buck Regulators; Application Report SNVA170B; Texas Instruments Incorporated: Dallas, TX, USA, 2013. [Google Scholar]

- Zeng, Z.-Y.; Cheng, C.-H.; Lin, F.-T. Comprehensive Analysis and Design of Current-Balance Loop in Constant On-Time Controlled Multi-Phase Buck Converter. IEEE Access 2020, 8, 184752–184764. [Google Scholar]

- Wei, K.; Ma, D.B. A 10-MHz DAB Hysteretic Control Switching Power Converter for 5G IoT Power Delivery. IEEE J. Solid-State Circuits 2021, 56, 2113–2122. [Google Scholar] [CrossRef]

- Chien, S.-H.; Hung, T.-H.; Huang, S.-Y.; Kuo, T.-H. A Monolithic Capacitor-Current-Controlled Hysteretic Buck Converter With Transient-Optimized Feedback Circuit. IEEE J. Solid-State Circuits 2015, 50, 2524–2532. [Google Scholar] [CrossRef]

- Nashed, M.; Fayed, A.A. Current-Mode Hysteretic Buck Converter With Spur-Free Control for Variable Switching Noise Mitigation. IEEE Trans. Power Electron. 2018, 33, 650–664. [Google Scholar] [CrossRef]

- Lee, B.; Song, M.K.; Maity, A.; Ma, D.B. A 25MHz 4-Phase SAW Hysteretic DC-DC Converter with 1-Cycle APC Achieving 190ns tsettle to 4A Load Transient and Above 80% Efficiency in 96.7% of the Power Range. In Proceedings of the 2017 IEEE International Solid-State Circuits Conference—(ISSCC), San Francisco, CA, USA, 5–9 February 2017; pp. 190–191. [Google Scholar]

- Lee, S.-H.; Bang, J.-S.; Yoon, K.-S.; Hong, S.-W.; Shin, C.-S.; Jung, M.-Y.; Cho, G.-H. A 0.518mm2 Quasi-Current-Mode Hysteretic Buck DC-DC Converter with 3µs Load Transient Response in 0.35µm BCDMOS. In Proceedings of the 2015 IEEE International Solid-State Circuits Conference-(ISSCC) Digest of Technical Papers, San Francisco, CA, USA, 22–26 February 2015. [Google Scholar]

- Zhao, L.; Tang, J.; Wei, K.; Huang, C. A 4-Phase DAB Current-Mode Hysteretic Controlled Buck Converter With Relaxed Inductor Requirements and Enhanced DC and Dynamic Performance. IEEE J. Solid-State Circuits 2024, 59, 1556–1566. [Google Scholar] [CrossRef]

- Microchip. Adaptive Constant On-Time Control and Ripple Injection Circuit Design; Application Note AN5629; Microchip Technology Inc.: Chandler, AZ, USA, 2017. [Google Scholar]

- MPS. COT Buck Loop BW and Load Step Resp. Comparison; Application Note AN136 Rev. 1.2; Monolithic Power Systems: San Jose, CA, USA, 2019. [Google Scholar]

- Huang, W.; Liu, L.; Liao, X.; Xu, C.; Li, Y. A 240-nA Quiescent Current, 95.8% Efficiency AOT-Controlled Buck Converter With A2-Comparator and Sleep-Time Detector for IoT Application. IEEE Trans. Power Electron. 2021, 36, 12898–12909. [Google Scholar] [CrossRef]

- Chen, K.; Garrett, J.; Peng, K.; Hulfachor, R.; Onabajo, M. Buck Circuit Design With Pseudo-Constant Frequency and Constant On-Time for High Current Point-of-Load Regulation. IEEE Trans. Circuits Syst. I Regul. Pap. 2021, 68, 4062–4075. [Google Scholar] [CrossRef]

- Ming, X.; Xin, Y.-L.; Li, T.-S.; Liang, H.; Li, Z.-J.; Zhang, B. A Constant On-Time Control With Internal Active Ripple Compensation Strategy for Buck Converter with Ceramic Capacitors. IEEE Trans. Power Electron. 2019, 34, 9263–9278. [Google Scholar] [CrossRef]

- Lin, Y.-C.; Chen, C.-J.; Chen, D.; Wang, B. A Ripple-Based Constant On-Time Control With Virtual Inductor Current and Offset Cancellation for DC Power Converters. IEEE Trans. Power Electron. 2012, 27, 4301–4310. [Google Scholar] [CrossRef]

- Tsai, C.-H.; Lin, S.-M.; Huang, C.-S. A Fast-Transient Quasi-V2 Switching Buck Regulator Using AOT Control With a Load Current Correction (LCC) Technique. IEEE Trans. Power Electron. 2013, 28, 3949–3957. [Google Scholar] [CrossRef]

- Chen, W.-W.; Chen, J.-F.; Liang, T.-J.; Wei, L.-C.; Huang, J.-R.; Ting, W.-Y. A Novel Quick Response of RBCOT With VIC Ripple for Buck Converter. IEEE Trans. Power Electron. 2013, 28, 4299–4307. [Google Scholar] [CrossRef]

- Yang, W.-H.; Huang, C.-J.; Huang, H.-H.; Lin, W.-T.; Chen, K.-H.; Lin, Y.-H.; Lin, S.-R.; Tsai, T.-Y. A Constant-on-Time Control DC–DC Buck Converter With the Pseudowave Tracking Technique for Regulation Accuracy and Load Transient Enhancement. IEEE Trans. Power Electron. 2018, 33, 6187–6198. [Google Scholar] [CrossRef]

- Ain, Q.U.; Khan, D.; Jang, B.G.; Basim, M.; Shehzad, K.; Asif, M.; Verma, D.; Ali, I.; Pu, Y.G.; Hwang, K.C.; et al. A High-Efficiency Fast Transient COT Control DC–DC Buck Converter With Current Reused Current Sensor. IEEE Trans. Power Electron. 2021, 36, 9521–9535. [Google Scholar] [CrossRef]

- Sun, Q.; Ma, Y.; Ye, Z.; Wang, X.; Zhang, H. A Pseudo-Constant Frequency Constant On-Time Buck Converter With Internal Current Ripple Injection and Output DC Offset Cancellation. IEEE Access 2019, 7, 175443–175453. [Google Scholar] [CrossRef]

- Hu, K.-Y.; Yeh, W.-T.; Tsai, C.-H.; Tsai, C.-W. Fully Digital Current Mode Constant On-Time Controlled Buck Converter With Output Voltage Offset Cancellation. IEEE Access 2021, 9, 162572–162580. [Google Scholar] [CrossRef]

- He, J.-P.; Liu, X.-R.; Xia, Y.-K.; Chen, Y.-Q.; Wu, C.-D. A Voltage Ripple Compensation Method for Constant On-Time Buck Converter. IEEE Access 2023, 11, 139628–139642. [Google Scholar] [CrossRef]

- Chen, J.-J.; Hwang, Y.-S.; Chang, C.-H.; Ku, Y.-T.; Yu, C.-C. A Sub-1 μs Fast-Response Buck Converter With Adaptive and Frequency-Locked Controlled Techniques. IEEE Trans. Ind. Electron. 2019, 66, 2198–2203. [Google Scholar] [CrossRef]

- Oh, Y.-J.; Lee, C.-H.; Nam, S.-Y.; Oh, J.-S.; Lee, S.-J.; Yang, J.-H.; Lee, J.; Hong, S.-W. A Robust High On-Duty Buck Converter Achieving a Peak Effective On-Duty of 0.976 With EMI Suppression. IEEE Trans. Ind. Electron. 2025, 72, 3223–3227. [Google Scholar] [CrossRef]

- Chen, W.-C.; Chen, H.-C.; Chien, M.-W.; Chou, Y.-W.; Chen, K.-H.; Lin, Y.-H.; Tsai, T.-Y.; Lin, S.-R.; Lee, C.-C. Pseudo-Constant Switching Frequency in On-Time Controlled Buck Converter with Predicting Correction Techniques. IEEE Trans. Power Electron. 2016, 31, 3650–3662. [Google Scholar] [CrossRef]

- Tsai, C.-H.; Chen, B.-M.; Li, H.-L. Switching Frequency Stabilization Techniques for Adaptive On-Time Controlled Buck Converter With Adaptive Voltage Positioning Mechanism. IEEE Trans. Power Electron. 2016, 31, 443–451. [Google Scholar] [CrossRef]

- Ke, X.; Wei, K.; Ma, D.B. A 10MHz, 40V-to-5V Clock-Synchronized AOT Hysteretic Converter With Programmable Soft Start Technique for Automotive USB Chargers. In Proceedings of the 2017 IEEE Applied Power Electronics Conference and Exposition (APEC), Tampa, FL, USA, 26–30 March 2017. [Google Scholar]

- Zhao, J.; Ye, Q.; Lai, X. A Frequency Stable On-Time Control Buck Converter With Reference and Frequency Compensation Technique Using Low ESR Output Capacitor. IEEE Trans. Ind. Electron. 2022, 69, 3536–3545. [Google Scholar] [CrossRef]

- Huang, Y.-R.; Chen, C.-J. A Novel Describing Function Small-Signal Modeling Approach for Passive Ripple Constant On-Time Controlled Converter With Exponentially Varying Slope. IEEE Trans. Power Electron. 2024, 39, 8425–8435. [Google Scholar] [CrossRef]

- Texas Instrument. Controlling Output Ripple and Achieving ESR Independence in Constant On-Time (COT) Regulator; Application Note AN-1481; Texas Instruments Incorporated: Dallas, TX, USA, 2013. [Google Scholar]

- Texas Instrument. Selecting an Ideal Ripple Generation Network for Your COT Buck Converter; Application Report SNVA776A; Texas Instruments Incorporated: Dallas, TX, USA, 2017. [Google Scholar]

- Texas Instrument. Stability Analysis and Design of COT Type-3 Ripple Circuit; Application Note SNVA874; Texas Instruments Incorporated: Dallas, TX, USA, 2019. [Google Scholar]

- Redl, R.; Sun, J. Ripple-Based Control of Switching Regulators—An Overview. IEEE Trans. Power Electron. 2009, 24, 2669–2680. [Google Scholar] [CrossRef]

- Choi, M.; Kye, C.-H.; Oh, J.; Choo, M.-S.; Jeong, D.-K. A Current-Mode Digital AOT 4-Phase Buck Voltage Regulator. IEEE Solid-State Circuits Lett. 2019, 2, 244–247. [Google Scholar] [CrossRef]

- Cheng, K.-Y.; Yu, F.; Lee, F.C.; Mattavelli, P. Digital Enhanced V2-Type Constant On-Time Control Using Inductor Current Ramp Estimation for a Buck Converter with Low-ESR Capacitors. IEEE Trans. Power Electron. 2013, 28, 1241–1252. [Google Scholar] [CrossRef]

- Yang, P.-J.; Wu, C.-H.; Yeh, C.-Y.; Chang-Chien, L.-R. Digital Adaptive On-Time and Transient-Optimized Ripple Con-trolled Buck Converter. IEEE Access 2023, 11, 129482–129492. [Google Scholar] [CrossRef]

- Tsai, C.-J.; Chen, H.-H.; Chen, C.-J. A Phase Interpolated Dual-Phase Adaptive On-Time Controlled Buck Converter. IEEE Trans. Circuits Syst. I Regul. Pap. 2024, 71, 5155–5165. [Google Scholar] [CrossRef]

- Huang, S.-Y.; Fang, K.-Y.; Huang, Y.-W.; Chien, S.-H.; Kuo, T.-H. Capacitor-Current-Sensor Calibration Technique and Application in a 4-Phase Buck Converter with Load-Transient Optimization. In Proceedings of the 2016 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 31 January–4 February 2016; pp. 228–229. [Google Scholar]

- Kim, S.J.; Nandwana, R.K.; Khan, Q.; Pilawa-Podgurski, R.C.N.; Hanumolu, P.K. A 4-Phase 30–70 MHz Switching Frequency Buck Converter Using a Time-Based Compensator. IEEE J. Solid-State Circuits 2015, 50, 2814–2824. [Google Scholar] [CrossRef]

- Gordillo, J.; Aguilar, C. A Simple Sensorless Current Sharing Technique for Multiphase DC–DC Buck Converters. IEEE Trans. Power Electron. 2016, 32, 3480–3489. [Google Scholar] [CrossRef]

- Li, P.; Xue, L.; Hazucha, P.; Karnik, T.; Bashirullah, R. A Delay-Locked Loop Synchronization Scheme for High-Frequency Multiphase Hysteretic DC-DC Converters. IEEE J. Solid-State Circuits 2009, 44, 3131–3145. [Google Scholar] [CrossRef]

- Liu, P.-H.; Lee, F.C.; Li, Q. Hybrid interleaving with adaptive PLL loop for adaptive on-time controlled switching converters. In Proceedings of the 2014 IEEE Energy Conversion Congress and Exposition (ECCE), Pittsburgh, PA, USA, 14–18 September 2014; pp. 4110–4117. [Google Scholar]

- Sun, M.; Yang, Z.; Joshi, K.; Mandal, D.; Adell, P.; Bakkaloglu, B. A 6 A, 93% Peak Efficiency, 4-Phase Digitally Synchronized Hysteretic Buck Converter With ±1.5% Frequency and ±3.6% Current-Sharing Error. IEEE J. Solid-State Circuits 2017, 52, 3081–3094. [Google Scholar] [CrossRef]

- Nien, C.-F.; Chen, D.; Hsiao, S.-F.; Kong, L.; Chen, C.-J.; Chan, W.-H.; Lin, Y.-L. A Novel Adaptive Quasi-Constant On-Time Current-Mode Buck Converter. IEEE Trans. Power Electron. 2017, 32, 8124–8133. [Google Scholar] [CrossRef]

- Abu-Qahouq, J.; Mao, H.; Batarseh, I. Multiphase voltage-mode hysteretic controlled DC-DC converter with novel current sharing. IEEE Trans. Power Electron. 2004, 19, 1397–1407. [Google Scholar] [CrossRef]

- Garcia, O.; Zumel, P.; de Castro, A.; Cobos, J. Current Self-Balance Mechanism in Multiphase Buck Converter. IEEE Trans. Power Electron. 2009, 24, 1600–1606. [Google Scholar] [CrossRef]

- Tang, J.; Zhao, L.; Wei, K.; Huang, C. An 8A 100-MHz 4-Phase Buck Converter with Fast Dynamic Response and Enhanced Light-Load Efficiency. In Proceedings of the 2018 IEEE 61st International Midwest Symposium on Circuits and Systems (MWSCAS), Windsor, ON, Canada, 5–8 August 2018. [Google Scholar]

- Huang, Y.-W.; Kuo, T.-H.; Huang, S.-Y.; Fang, K.-Y. A Four-Phase Buck Converter With Capacitor-Current-Sensor Calibration for Load-Transient-Response Optimization That Reduces Undershoot/Overshoot and Shortens Settling Time to Near Their Theoretical Limits. IEEE J. Solid-State Circuits 2018, 53, 552–568. [Google Scholar] [CrossRef]

- Li, S.-Y.; Chen, B.-R.; Chen, K.-H.; Lin, Y.-H.; Lin, S.-R.; Tsai, T.-Y. 48-to-1 V Direct Conversion Using High-Voltage Storage and Low-Voltage Boost Bootstrap Technique and Early Comparison On-Time Generator for Precise Nanosecond Pulses and 90.3% Efficiency in Automotive Applications. IEEE J. Solid-State Circuits 2022, 57, 3396–3406. [Google Scholar] [CrossRef]

- Lee, Y.-H.; Wang, S.-J.; Chen, K.-H. Quadratic Differential and Integration Technique in V2 Control Buck Converter With Small ESR Capacitor. IEEE Trans. Power Electron. 2010, 25, 829–838. [Google Scholar]

- Texas Instruments Incorporated. TPS51518. December 2011. Available online: https://www.ti.com/lit/gpn/tps51518 (accessed on 12 December 2011).

- Analog Devices. ADP1882/ADP1883. April. 2010. Available online: https://www.analog.com/media/en/technical-documentation/data-sheets/ADP1882_1883.pdf (accessed on 18 May 2010).

- Monolithic Power Systems, MP2316. May 2019. Available online: https://www.monolithicpower.com/en/documentview/productdocument/index/version/2/document_type/Datasheet/lang/en/sku/MP2316/document_id/789/ (accessed on 31 May 2019).

- Richtek Technology Corporation, RT6242A/B. March 2016. Available online: https://www.richtek.com/assets/product_file/RT6242A=RT6242B/DS6242AB-05.pdf (accessed on 5 May 2016).

- Hariharan, K.; Kapat, S.; Mukhopadhyay, S. Constant on/off-Time Hybrid Modulation in Digital Current-Mode Control Using Event-Based Sampling. IEEE Trans. Power Electron. 2019, 34, 3789–3803. [Google Scholar] [CrossRef]

- Zadeh, H.A.; Kooshkaki, H.R.; Lee, K.-Y.; Mercier, P.P. An Adaptive Constant-on-Time-Controlled Hybrid Multilevel DC–DC Converter Operating From Li-Ion Battery Voltages with Low Spurious Output. IEEE Trans. Power Electron. 2023, 38, 5763–5776. [Google Scholar] [CrossRef]

- Li, Y.-C.; Chen, C.-J.; Tsai, C.-J. A Constant On-Time Buck Converter With Analog Time-Optimized On-Time Control. IEEE Trans. Power Electron. 2020, 35, 3754–3765. [Google Scholar] [CrossRef]

- Meyer, E.; Zhang, Z.; Liu, Y.-F. An Optimal Control Method for Buck ConvertersUsing a Practical Capacitor ChargeBalance Technique. IEEE Trans. Power Electron. 2008, 23, 1802–1812. [Google Scholar] [CrossRef]

| Unit | [5] | [8] | [12] | [13] | [14] | [16] | [18] | [19] | [20] | |

|---|---|---|---|---|---|---|---|---|---|---|

| Tech. | μm | 0.18 | 0.35 | 0.18 | 0.13 | 0.5 | 0.35 | 0.028 | 0.13 | 0.18 |

| VIN | V | 1.8 | 3.3 | 2.1–5.5 | 4–19 | 4.5–30 | 3.3–4.2 | 2.6–3.63 | 7–15 | 5–12 |

| VOUT | V | 0.9–1.2 | 2 | 1.8 | 0.25–2.5 | 1 | 1.2 | 1.05 | 5–7 | 1.05–3.3 |

| L | μH | 0.24 | 4.7 | 2.2 | 0.15 | 2.2 | 4.7 | 1 | 2.2 | 1.5 |

| COUT | μF | 16 | 4.7 | 10 | 470 | 88 | 8.9 | 4.7 | N/A | 22 |

| fSW | MHz | 3 | 0.8 | N/A | 0.8 | 0.4 | 0.75 | 2.5 | 2 | 0.7 |

| ILoad | A | 3 | 0.5 | 0.3 | 40 | 1.2–4 | 0.745 | 0.3–1.7 | 0–2 | 1–5 |

| Peak Eff. | % | 95.58 | 93 | 90.04 | 92 | 95 | 86.6 | 94 | 95.56 | 92 |

| Settling time | μs | 2 | 10 | N/A | 40 | 28 | 3.6 | 4 | 3 | 15.4 |

| VUS/OS | mV | 80 | 50 | 50 | 28/18 | 24 | 75 | 90/75 | 72/85 | 30/58 |

| ΔfSW/fSW | % | N/A | N/A | N/A | 0.16 | N/A | N/A | N/A | N/A | N/A |

| Area | mm2 | 1.41 | 2.89 | 1.1 | N/A | N/A | 1.9 | N/A | 3 | 3.01 |

| Multiphase | - | 2Φ, PD | ||||||||

| Unit | [21] | [22] | [23] | [24] | [25] | [26] | [27] | [34] | ||

| Tech. | μm | 0.18 | 0.13 | 0.35 | 0.13 | 0.028 | 0.18 | 0.35 | 0.028 | |

| VIN | V | 12 | 19 | 3–3.7 | 1.8 | 3.3 | 2.7–3.6 | 40 | 4.2 | |

| VOUT | V | 1 | 5.1 | 1.2–1.8 | 0.5–1.7 | 1.05 | 1–1.2 | 5 | 0.6–1.0 | |

| L | μH | 2.2 | 1.5 | 4.7 | 0.47 | 1 | N/A | 0.47 | 0.015 | |

| COUT | μF | 66 | 22 × 4 | 10 | 22 | 4.7 | N/A | 22 | 3.2 | |

| fSW | MHz | 0.5 | 0.57 | 1 | <1 | 2.5 | 1 | 10 | 75 | |

| ILoad | A | 0–5 | 0–8 | 0.7 | 0.5 | 0.3–1.7 | 1.1 | 0–2 | 1.2 | |

| Peak Eff. | % | N/A | 94 | 90 | 97.6 | 89 | 88.2 | 90.5 | 89 | |

| Settling time | μs | 10 | 40 | 0.96 | 0.4 | 10 | 10 | 0.48 | 0.08 | |

| V*US/OS | mV | 80/100 | 120/180 | N/A | 66/92 | 95/400 | 76 | 9/12 | 80 | |

| ΔfSW/fSW | % | N/A | N/A | N/A | N/A | 0.32 | 5.2 | N/A | N/A | |

| Area | mm2 | 1.2 | N/A | 1.971 | 1.955 | 2.4 | 1.1 | 5.75 | 0.39 | |

| Multiphase | - | 4Φ, PD | ||||||||

| Unit | [36] | [57] | [56] | [41] | [43] | [47] | [48] | [50] | ||

| Tech. | μm | N/A | 0.18 | 0.065 | 0.5 | 0.18 | 0.13 | 0.18 | 0.13 | |

| VIN | V | 2.7–4.2 | 3.3 | 2.7–4.5 | 4.8 | 2~3.3 | 1.35–1.65 | 3.3 | 4.25–15 | |

| VOUT | V | 1.2 | 0.6–1.2 | 0.6–1.3 | 3.3 | 0.8~1.6 | 0.75–1 | 0.7–3.0 | 0.8–1.43 | |

| L | μH | 4.7 | 1 | 0.47 | 0.11~0.22 | 0.33 | 0.005 | 0.22 | 0.68 | |

| COUT | μF | 4.7 | 4.7 | 10 | 0.008–0.19 | 10 | 0.22 | 0.62 | 47 × 3 | |

| fSW | MHz | 1 | 1.5 | 2.5 | ~30 | 3~9.5 | 100 | 30 | 0.5–1.25 | |

| ILoad | A | 0.1–0.5 | 1.25 | 1.6 | 1 | 6 | 8 | 2.5 | 10 | |

| Peak Eff. | % | 81.6 | 90.2 | 86 | 83 | 93 | 88 | 88.1 | 92.5 | |

| Settling time | μs | 2.5 | 3 | 13.7 | N/A | 6 | 0.15 | 0.0225 | 60 | |

| V*US/OS | mV | 50/68 | 10/20 | 113/91 | 0.4/0.35 | 0.25/0.25 | 0.06/0.14 | 40 | ||

| ΔfSW/fSW | % | 2.8 | N/A | 0.13 | N/A | 1.5 | N/A | N/A | N/A | |

| Area | mm2 | N/A | 1.423 | 13.3 | 3.3 | 12.5 | N/A | 1.93 | 6.5 | |

| Multiphase | - | 4Φ, DLL | 4Φ, DLL | 4Φ, PD | 4Φ, DLL | 2Φ, PD |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Koh, S.-T.; Bae, S. Research Trends and Challenges of Integrated Constant On-Time (COT) Buck Converters. Electronics 2025, 14, 3721. https://doi.org/10.3390/electronics14183721

Koh S-T, Bae S. Research Trends and Challenges of Integrated Constant On-Time (COT) Buck Converters. Electronics. 2025; 14(18):3721. https://doi.org/10.3390/electronics14183721

Chicago/Turabian StyleKoh, Seok-Tae, and Sunghyun Bae. 2025. "Research Trends and Challenges of Integrated Constant On-Time (COT) Buck Converters" Electronics 14, no. 18: 3721. https://doi.org/10.3390/electronics14183721

APA StyleKoh, S.-T., & Bae, S. (2025). Research Trends and Challenges of Integrated Constant On-Time (COT) Buck Converters. Electronics, 14(18), 3721. https://doi.org/10.3390/electronics14183721