The Effect of Diluted N2O Annealing Time on Gate Dielectric Reliability of SiC Metal-Oxide Semiconductor Capacitors and Characterization of Performance on SiC Metal-Oxide Semiconductor Field Effect Transistor

Abstract

1. Introduction

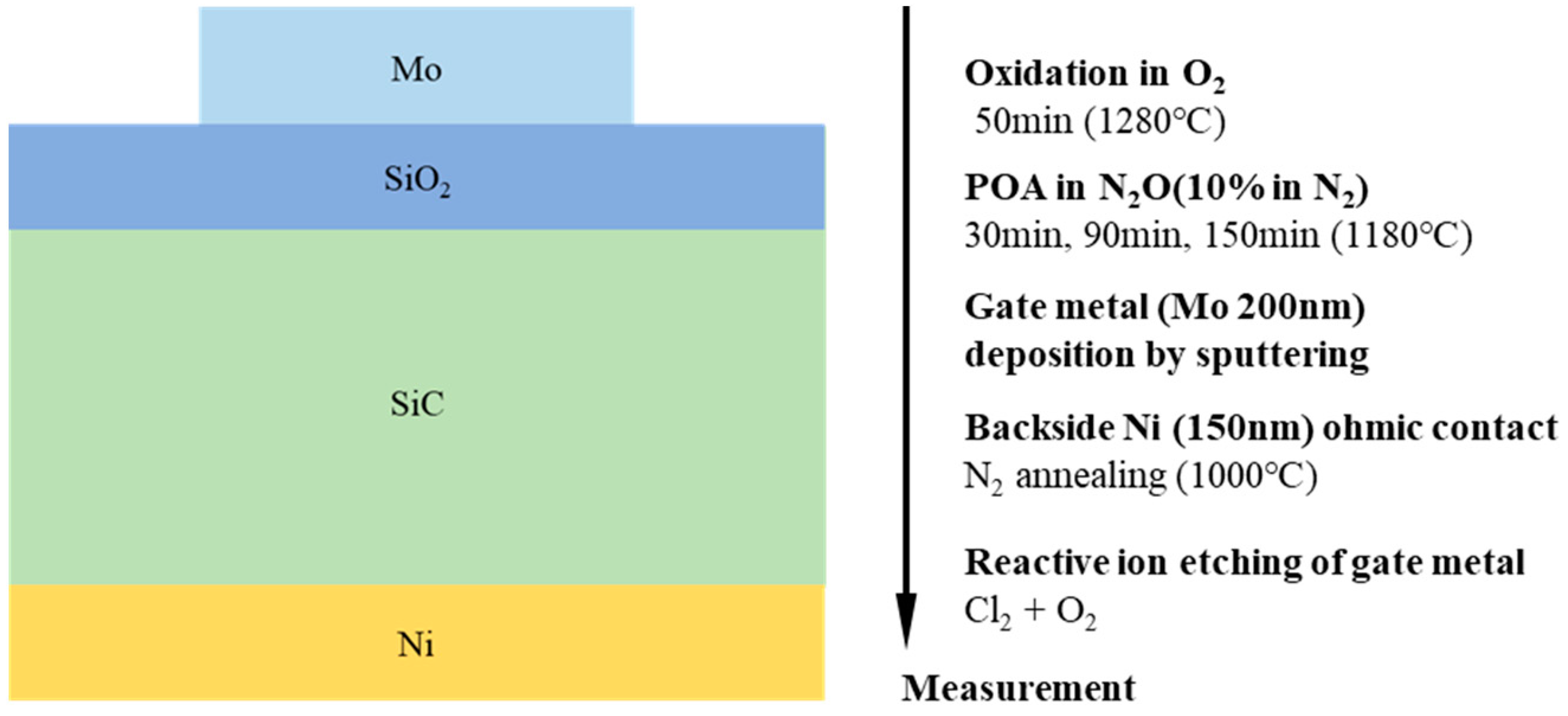

2. Experiment of MOS Capacitors

3. Results and Discussion

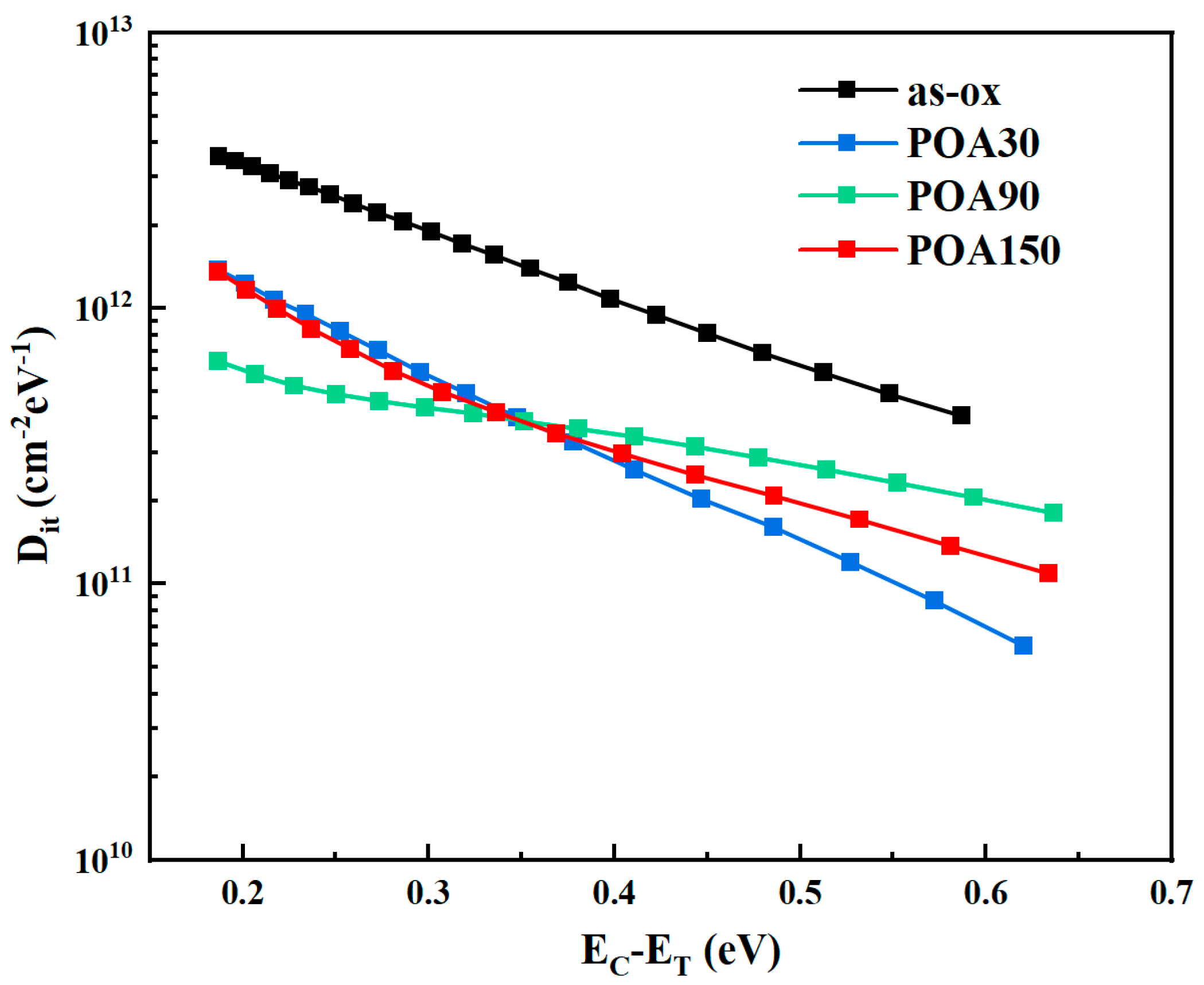

3.1. The Results of C-V Test

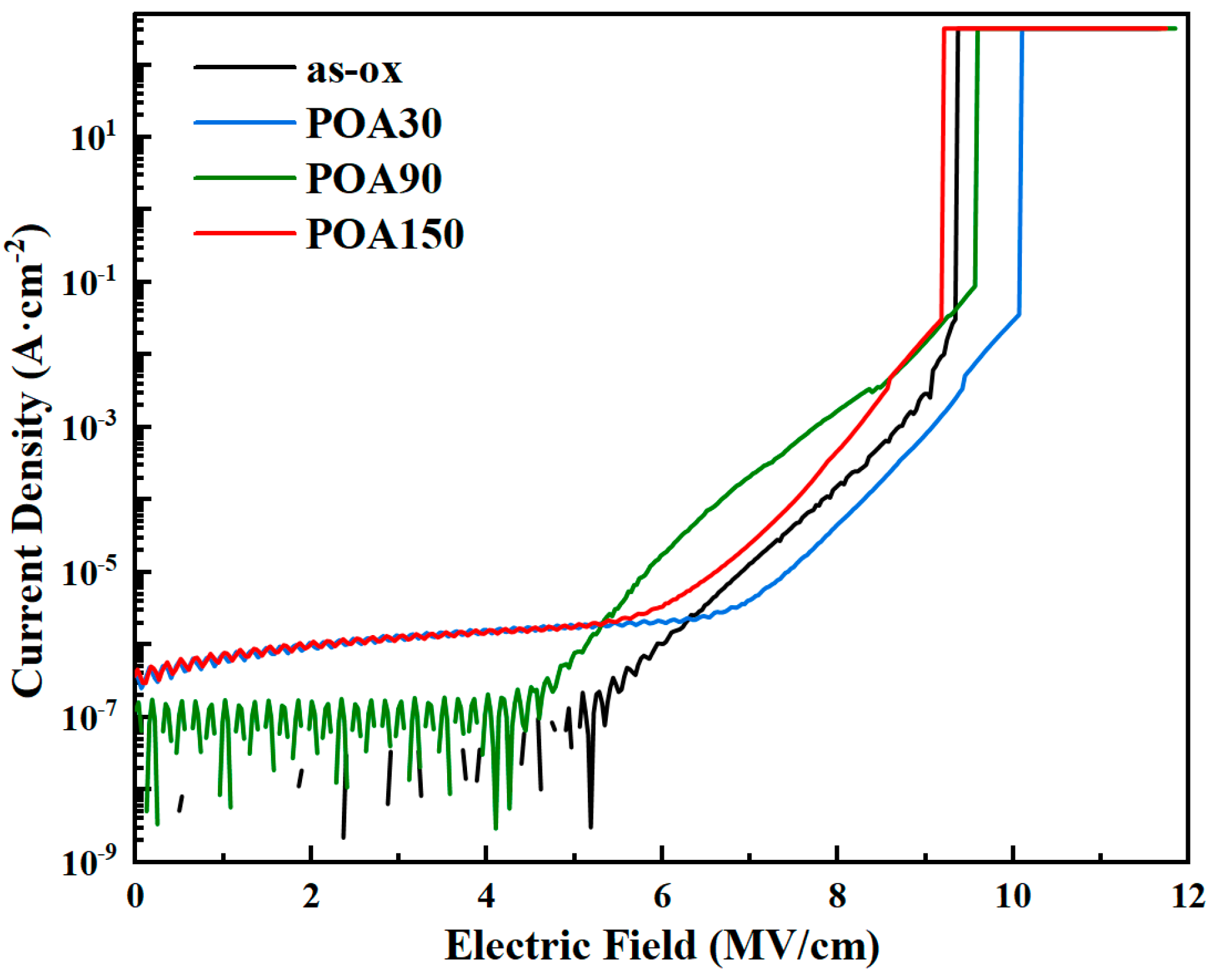

3.2. The Results of IV Test

4. Experiment of LDMOSFETs

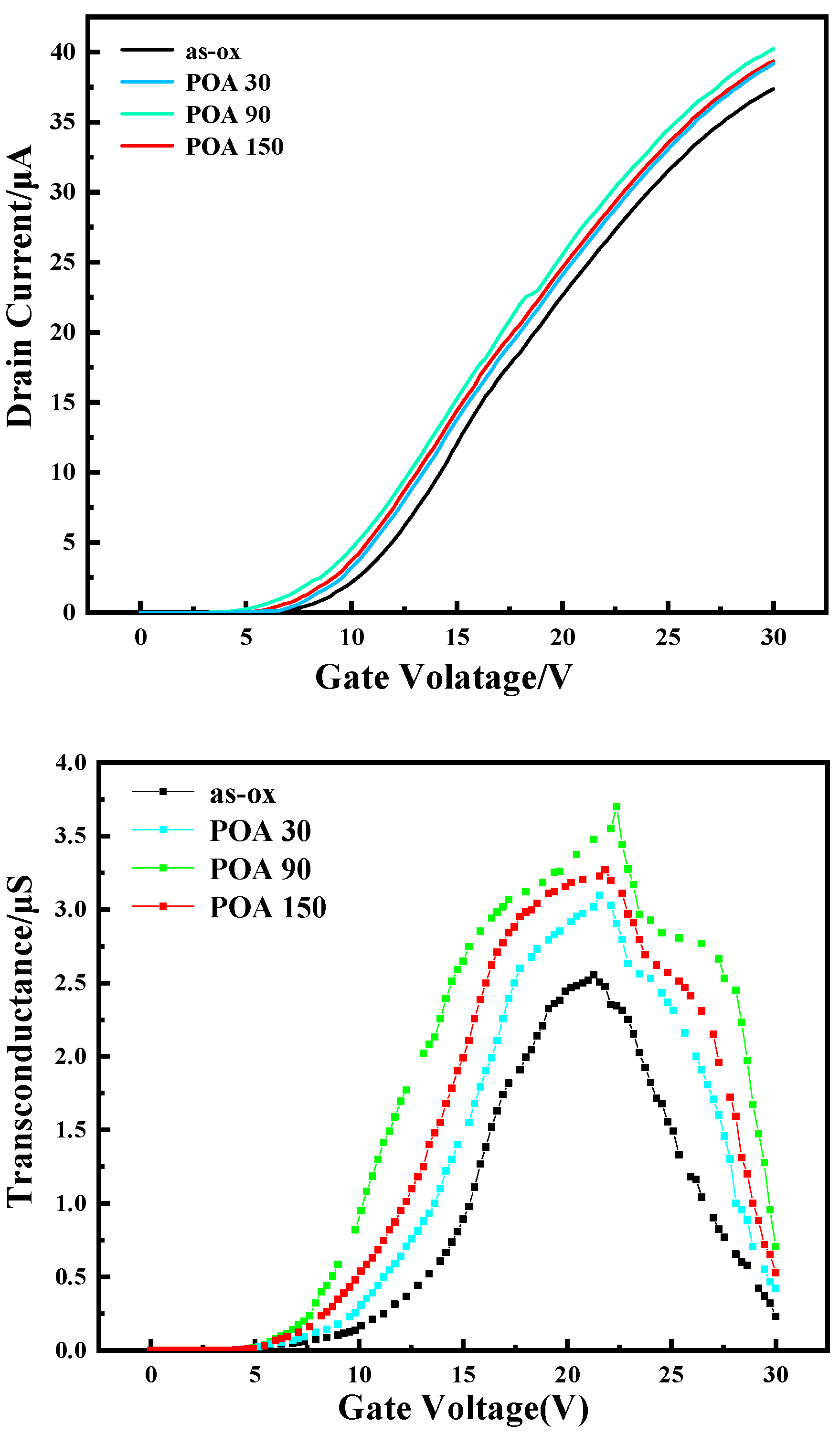

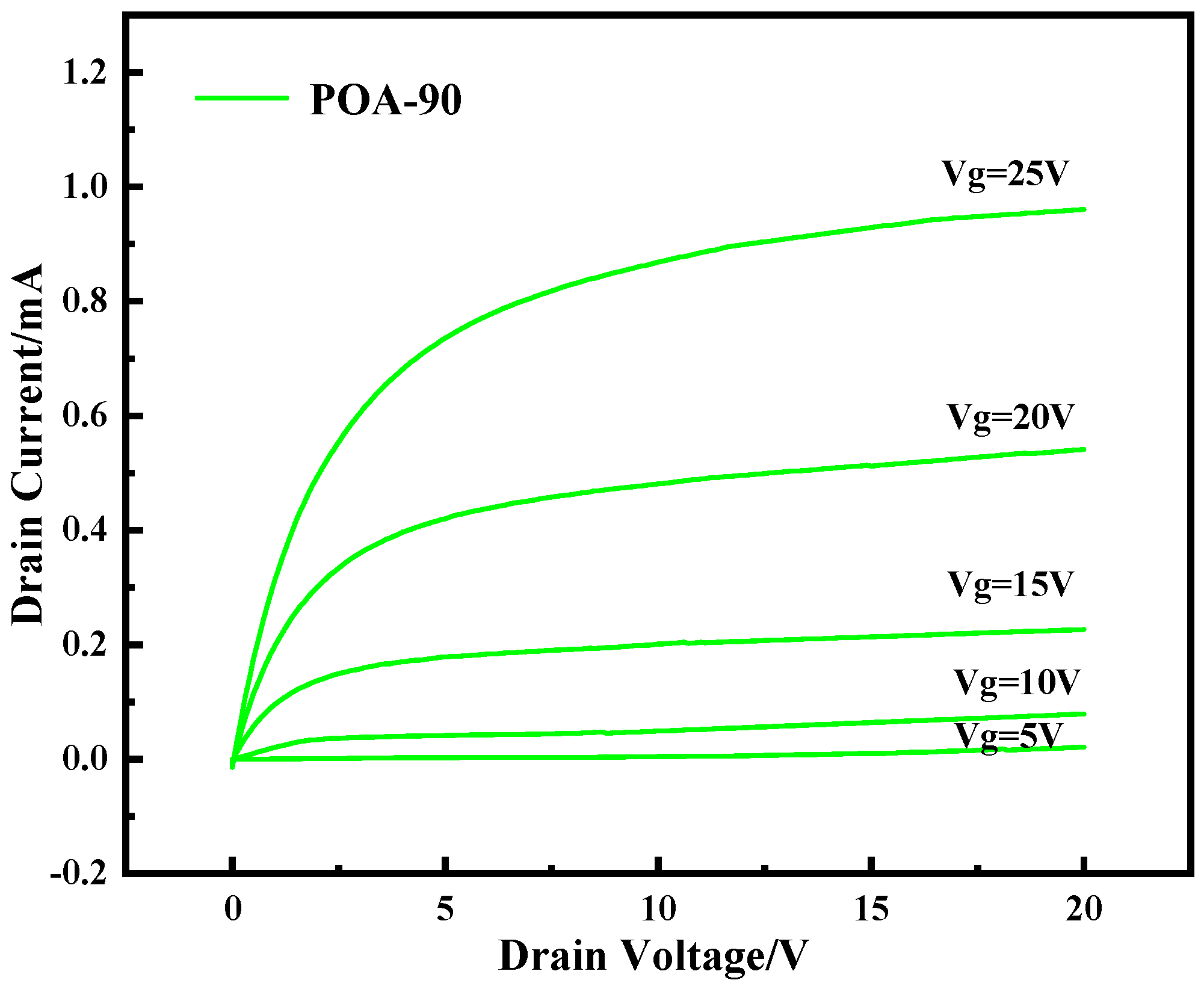

The Results of I-V Test

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Kimoto, T.; Cooper, J.A. Fundamentals of Silicon Carbide Technology: Growth, Characterization, Devices and Applications; John Wiley & Sons: Singapore, 2014. [Google Scholar]

- Dhar, S. Nitrogen and hydrogen induced trap passivation at the SiO2/4H-SiC interface. In Materials Science Forum; Trans Tech Publications Ltd.: Stafa-Zurich, Switzerland, 2006; pp. 949–954. [Google Scholar]

- Li, X.; Lee, S.S.; Li, M.; Ermakov, A.; Medina-Ramos, J.; Fister, T.T.; Amarasinghe, V.; Gustafsson, T.; Garfunkel, E.; Fenter, P.; et al. Effect of nitrogen passivation on interface composition and physical stress in SiO2/SiC (4H) structures. Appl. Phys. Lett. 2018, 113, 131601. [Google Scholar] [CrossRef]

- Kobayashi, T.; Harada, K.; Kumagai, Y.; Oba, F.; Matsushita, Y.I. Native point defects and carbon clusters in 4H-SiC: A hybrid functional study. J. Appl. Phys. 2019, 125, 125701. [Google Scholar] [CrossRef]

- Anders, M.A.; Lenahan, P.M.; Lelis, A.J. Are dangling bond centers important interface traps in 4H-SiC metal oxide semiconductor field effect transistors. Appl. Phys. Lett. 2016, 109, 142106. [Google Scholar] [CrossRef]

- Devynck, F.; Alkauskas, A.; Broqvist, P.; Pasquarello, A. Charge transition levels of carbon-, oxygen-, and hydrogen-related defects at the SiC/SiO2 interface through hybrid functionals. Phys. Rev. B 2011, 84, 235320. [Google Scholar] [CrossRef]

- Tseng, Y.H.; Wu, T.H.; Tsui, B.Y.; Yen, C.T.; Hung, C.C.; Lee, C.Y. A comprehensive study on the oxidation of 4H-SiC in diluted N2O ambient. Jpn. J. Appl. Phys. 2017, 56, 04CR02. [Google Scholar] [CrossRef]

- Zhai, D.; Gao, D.; Xiao, J.; Gong, X.; Yang, J.; Zhao, Y.; Wang, J.; Lu, J. Electrical characterization of near-interface traps in thermally oxidized and NO-annealed SiO2/4H-SiC metal-oxide-semiconductor capacitors. J. Phys. D Appl. Phys. 2020, 53, 445102. [Google Scholar] [CrossRef]

- Jamet, P.; Dimitrijev, S.; Tanner, P. Effects of nitridation in gate oxides grown on 4H-SiC. J. Appl. Phys. 2001, 90, 5058–5063. [Google Scholar] [CrossRef]

- Nanen, Y.; Kato, M.; Suda, J.; Kimoto, T. Effects of nitridation on 4H-SiC MOSFETs fabricated on various crystal faces. IEEE Trans. Electron Devices 2013, 60, 1260–1262. [Google Scholar] [CrossRef]

- Yoshioka, H.; Nakamura, T.; Kimoto, T. Generation of very fast states by nitridation of the SiO2/SiC interface. J. Appl. Phys. 2012, 112, 024520. [Google Scholar] [CrossRef]

- Meyer, D.J.; Bohna, N.A.; Lenahan, P.M.; Lelis, A.J. Spin dependent recombination at deep-level centers in 6H silicon carbide/silicon metal oxide semiconductor field effect transistors. In Materials Science Forum; Trans Tech Publications Ltd.: Bäch, Switzerland, 2004; Volume 457, pp. 477–480. [Google Scholar] [CrossRef]

- Deak, P.; Knaup, J.M.; Hornos, T.; Thill, C.; Gali, A.; Frauenheim, T. The mechanism of defect creation and passivation at the SiC/SiO2 interface. J. Phys. D Appl. Phys. 2007, 40, 6242. [Google Scholar] [CrossRef]

- Agarwal, A.K.; Burk, A.A.; Callanan, R.; Capell, C.; Das, M.K.; Haney, S.K.; Hull, B.A.; Jonas, C.; O’Loughlin, M.J. Critical technical issues in high voltage SiC power devices. In Materials Science Forum; Trans Tech Publications Ltd.: Bäch, Switzerland, 2009; Volume 600, pp. 895–900. [Google Scholar] [CrossRef]

- Siddiqui, A.; Elgabra, H.; Singh, S. The current status and the future prospects of surface passivation in 4H-SiC transistors. IEEE Trans. Device Mater. Reliab. 2016, 16, 419–428. [Google Scholar] [CrossRef]

- Zhao, P.; Liu, Y.; Tin, C.C.; Zhu, W.G.; Ahn, J. Investigation of 4H-SiC MOS capacitors annealed in diluted N2O at different temperatures. Microelectron. Eng. 2006, 83, 61–64. [Google Scholar] [CrossRef]

- Noborio, M.; Suda, J.; Kimoto, T. P-Channel MOSFETs on 4H-SiC {0001} and Nonbasal Faces Fabricated by Oxide Deposition and N2O Annealing. IEEE Trans. Electron Devices 2009, 56, 1953–1958. [Google Scholar] [CrossRef]

- Jia, Y.; Lv, H.; Song, Q.; Tang, X.; Xiao, L.; Wang, L.; Tang, G.; Zhang, Y.; Zhang, Y. Influence of oxidation temperature on the interfacial properties of n-type 4H-SiC MOS capacitors. Appl. Surf. Sci. 2017, 397, 175–182. [Google Scholar] [CrossRef]

- Luo, Z.; Wan, C.; Jin, Z.; Xu, H. Effects of sequential annealing in low oxygen partial-pressure and NO on 4H-SiC MOS devices. Semicond. Sci. Technol. 2021, 36, 045021. [Google Scholar] [CrossRef]

- Greulich-Weber, S. The microscopic and electronic structure of shallow donors in SiC. Phys. Status Solidi (b) 1998, 210, 415–427. [Google Scholar] [CrossRef]

- Fujihira, K.; Tarui, Y.; Imaizumi, M.; Ohtsuka, K.I.; Takami, T.; Shiramizu, T.; Kawase, K.; Tanimura, J.; Ozeki, T. Characteristics of 4H–SiC MOS interface annealed in N2O. Solid-State Electron. 2005, 49, 896–901. [Google Scholar] [CrossRef]

- Umeda, T.; Esaki, K.; Kosugi, R.; Fukuda, K.; Ohshima, T.; Morishita, N.; Isoya, J. Behavior of nitrogen atoms in SiC-SiO2 interfaces studied by electrically detected magnetic resonance. Appl. Phys. Lett. 2011, 99, 142105. [Google Scholar] [CrossRef]

- Yoshioka, H.; Senzaki, J.; Shimozato, A.; Tanaka, Y.; Okumura, H. N-channel field-effect mobility inversely proportional to the interface state density at the conduction band edges of SiO2/4H-SiC interfaces. AIP Adv. 2015, 5, 017109. [Google Scholar] [CrossRef]

- Friedrichs, P.; Burte, E.P.; Schörner, R. Interface properties of metal-oxide-semiconductor structures on n-type 6H and 4H-SiC. J. Appl. Phys. 1996, 79, 7814–7819. [Google Scholar] [CrossRef]

- Hazra, S.; Chakraborty, S.; Lai, P.T. Density profiles and electrical properties of thermally grown oxide nanofilms on p-type 6H–SiC (0001). Appl. Phys. Lett. 2004, 85, 5580–5582. [Google Scholar] [CrossRef]

- Chang, K.C.; Porter, L.M.; Bentley, J.; Lu, C.Y.; Cooper, J., Jr. Electrical, structural, and chemical analysis of silicon carbide-based metal-oxide-semiconductor field-effect-transistors. J. Appl. Phys. 2004, 95, 8252–8257. [Google Scholar] [CrossRef]

- Li, H.F.; Dimitrijev, S.; Sweatman, D.; Harrison, H.B.; Tanner, P.; Feil, B. Investigation of nitric oxide and Ar annealed SiO2/SiC interfaces by X-ray photoelectron spectroscopy. J. Appl. Phys. 1999, 86, 4316–4321. [Google Scholar] [CrossRef]

- Jamet, P.; Dimitrijev, S. Physical properties of N2O and NO-nitrided gate oxides grown on 4H SiC. Appl. Phys. Lett. 2001, 79, 323–325. [Google Scholar] [CrossRef]

- Kimoto, T.; Watanabe, H. Defect engineering in SiC technology for high-voltage power devices. Appl. Phys. Express 2020, 13, 120101. [Google Scholar] [CrossRef]

- Baliga, B.J. Silicon carbide power devices. In Springer Handbook of Semiconductor Devices; Springer International Publishing: Cham, Switzerland, 2022; pp. 491–523. [Google Scholar]

- Song, Q.W.; Tang, X.Y.; He, Y.J.; Tang, G.N.; Wang, Y.H.; Zhang, Y.M.; Guo, H.; Jia, R.X.; Lv, H.L.; Zhang, Y.M. Fabrication and characterization of the normally-off N-channel lateral 4H–SiC metal–oxide–semiconductor field-effect transistors. Chin. Phys. B 2016, 25, 037306. [Google Scholar] [CrossRef]

| Sample | Oxidation Time at 1280 °C (min) | POA Time at 1180 °C (min) | VFB (V) | Hysteresis in C-V (V) | NNITs (cm−2) |

|---|---|---|---|---|---|

| as-ox | 50 | / | 4.71 | 0.21 | 6.78 × 1011 |

| POA-30 | 50 | 30 | 3.60 | 0.02 | 5.27 × 1010 |

| POA-90 | 50 | 90 | 2.40 | 0.08 | 2.11 × 1011 |

| POA-150 | 50 | 150 | 2.91 | 0.16 | 5.02 × 1011 |

| Sample | Oxidation Time at 1280 °C (min) | POA Time at 1180 °C (min) | VTH (V) | Peak Field Effect Mobility (cm²/V·s) |

|---|---|---|---|---|

| as-ox | 50 | / | 10.5 | 5.0 |

| POA-30 | 50 | 30 | 9.3 | 6.0 |

| POA-90 | 50 | 90 | 7.8 | 7.1 |

| POA-150 | 50 | 150 | 8.5 | 6.3 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Dong, Z.; Jiang, L.; Su, M.; Zeng, C.; Liu, H.; Li, B.; Sun, Y.; Cui, Q.; Zeng, Z.; Zhang, B. The Effect of Diluted N2O Annealing Time on Gate Dielectric Reliability of SiC Metal-Oxide Semiconductor Capacitors and Characterization of Performance on SiC Metal-Oxide Semiconductor Field Effect Transistor. Electronics 2024, 13, 596. https://doi.org/10.3390/electronics13030596

Dong Z, Jiang L, Su M, Zeng C, Liu H, Li B, Sun Y, Cui Q, Zeng Z, Zhang B. The Effect of Diluted N2O Annealing Time on Gate Dielectric Reliability of SiC Metal-Oxide Semiconductor Capacitors and Characterization of Performance on SiC Metal-Oxide Semiconductor Field Effect Transistor. Electronics. 2024; 13(3):596. https://doi.org/10.3390/electronics13030596

Chicago/Turabian StyleDong, Zhihua, Leifeng Jiang, Manqi Su, Chunhong Zeng, Hui Liu, Botong Li, Yuhua Sun, Qi Cui, Zhongming Zeng, and Baoshun Zhang. 2024. "The Effect of Diluted N2O Annealing Time on Gate Dielectric Reliability of SiC Metal-Oxide Semiconductor Capacitors and Characterization of Performance on SiC Metal-Oxide Semiconductor Field Effect Transistor" Electronics 13, no. 3: 596. https://doi.org/10.3390/electronics13030596

APA StyleDong, Z., Jiang, L., Su, M., Zeng, C., Liu, H., Li, B., Sun, Y., Cui, Q., Zeng, Z., & Zhang, B. (2024). The Effect of Diluted N2O Annealing Time on Gate Dielectric Reliability of SiC Metal-Oxide Semiconductor Capacitors and Characterization of Performance on SiC Metal-Oxide Semiconductor Field Effect Transistor. Electronics, 13(3), 596. https://doi.org/10.3390/electronics13030596