Motor Dynamic Loading and Comprehensive Test System Based on FPGA and MCU

Abstract

:1. Introduction

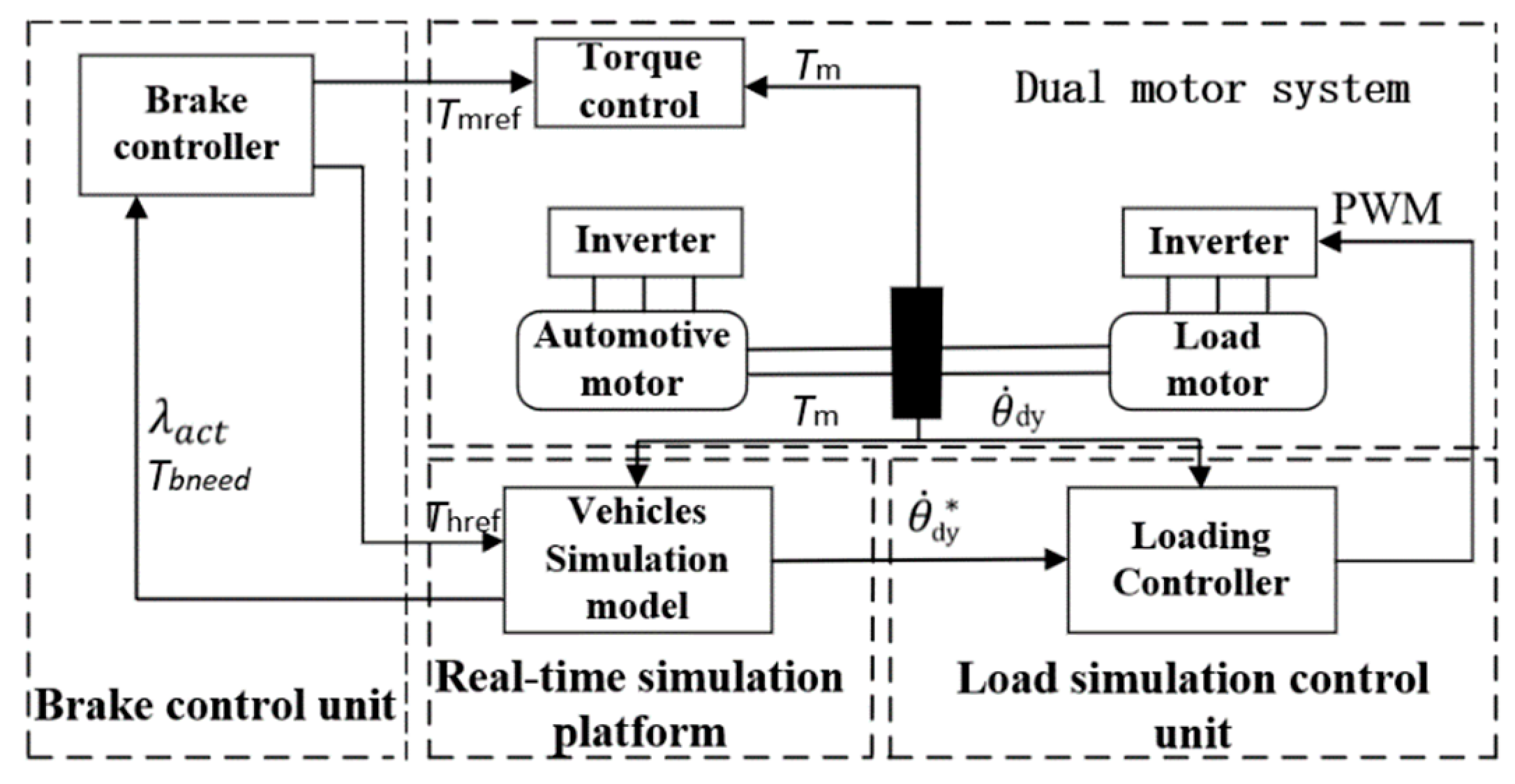

2. Composition Principle of the Motor Test System

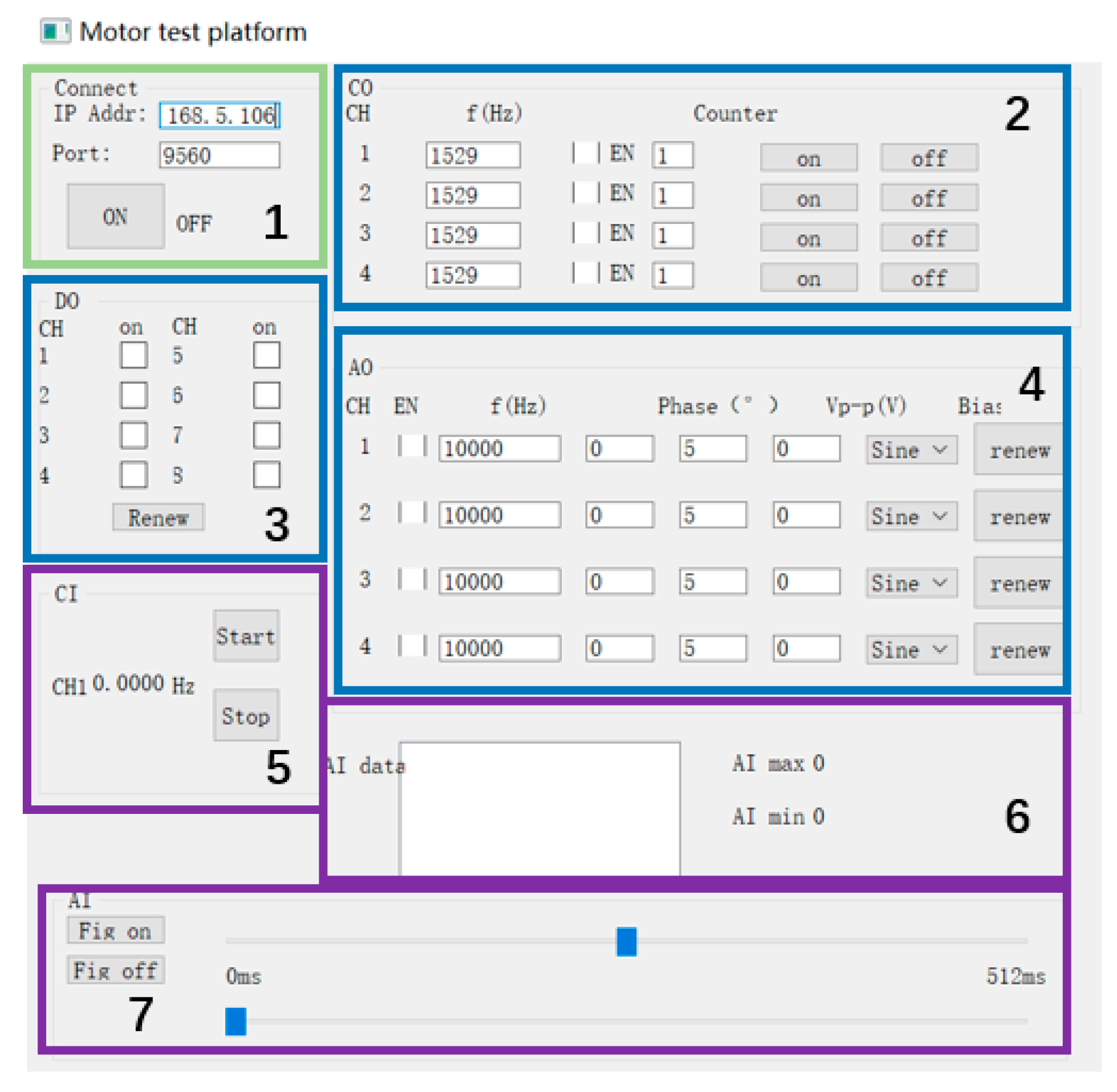

3. System Hardware Design

3.1. Overall Structure

3.2. Circuit Design of STM32 Module

3.3. FPGA Module Circuit Design

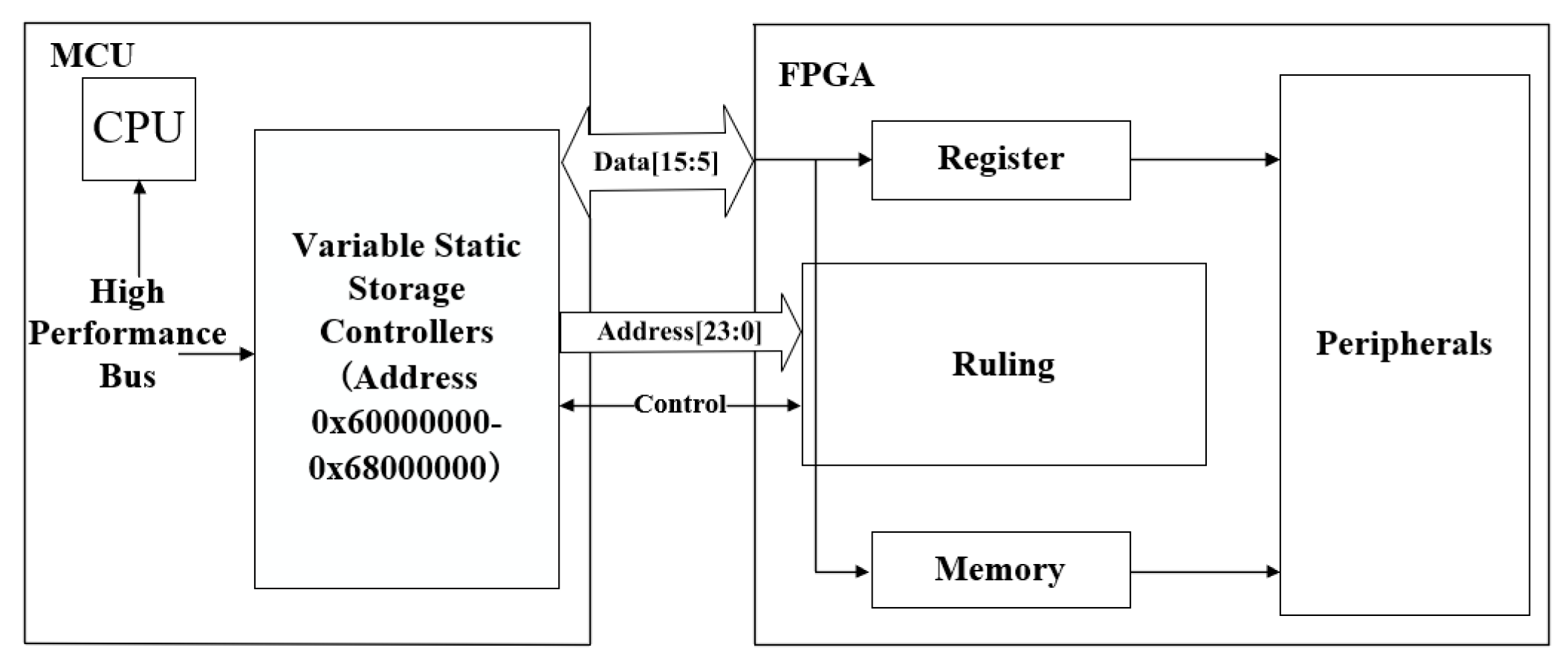

3.4. FSMC Communication Design between STM32 and FPGA

4. System Software Architecture

4.1. Overall Software Structure

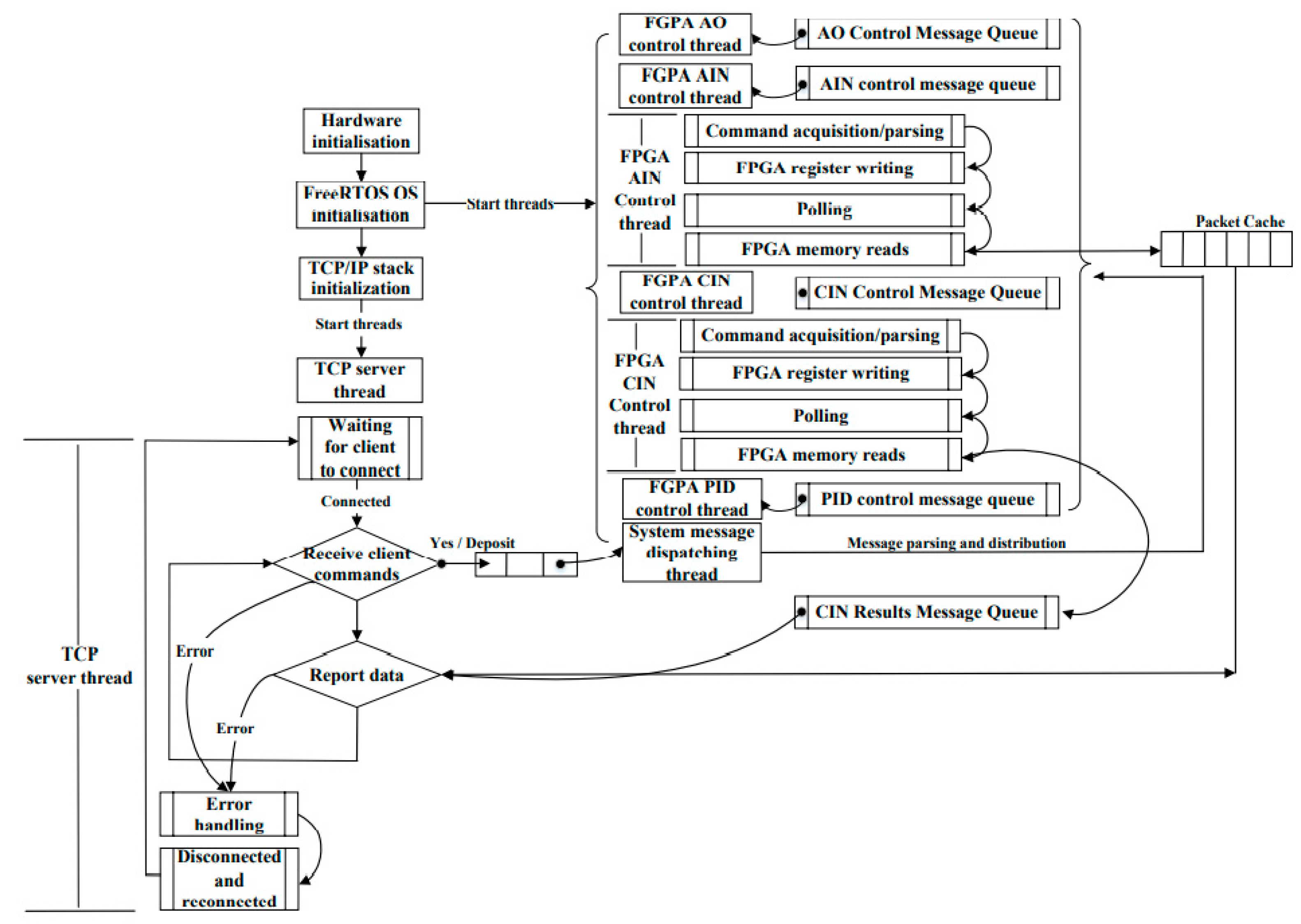

4.2. STM32 Software Design

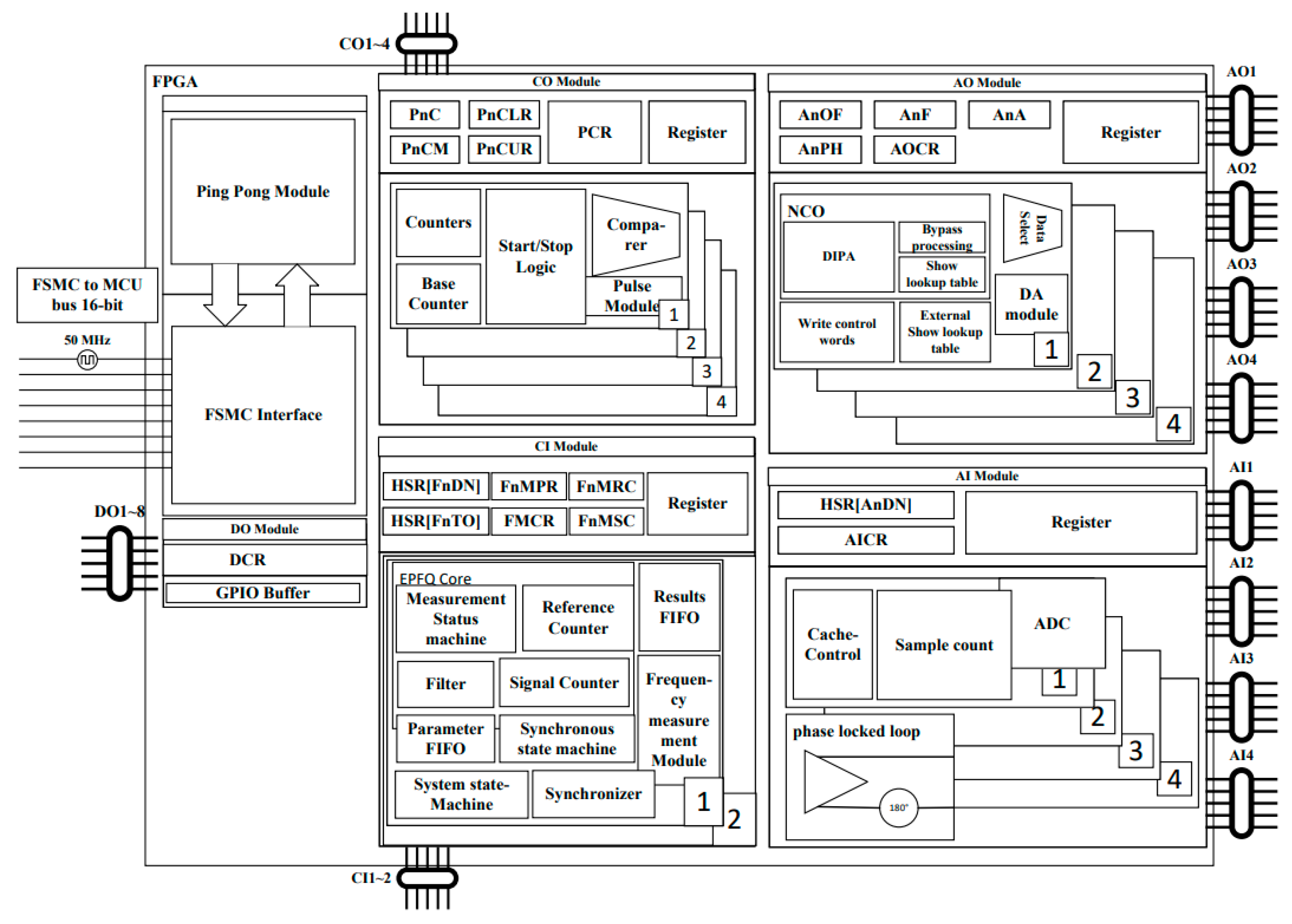

4.3. FPGA Software Design

4.4. Ping-Pong Algorithm for Data

| Algorithom 1 ping-pong operation |

| Input: DATA_Ti(i = 1,2,3,…n) |

| if(buffer_1 ! = Full ) |

| buffer_1 = DATA_Ti |

| else if (buffer_1 = Full) |

| buffer_2 = DATA_Ti |

| End if |

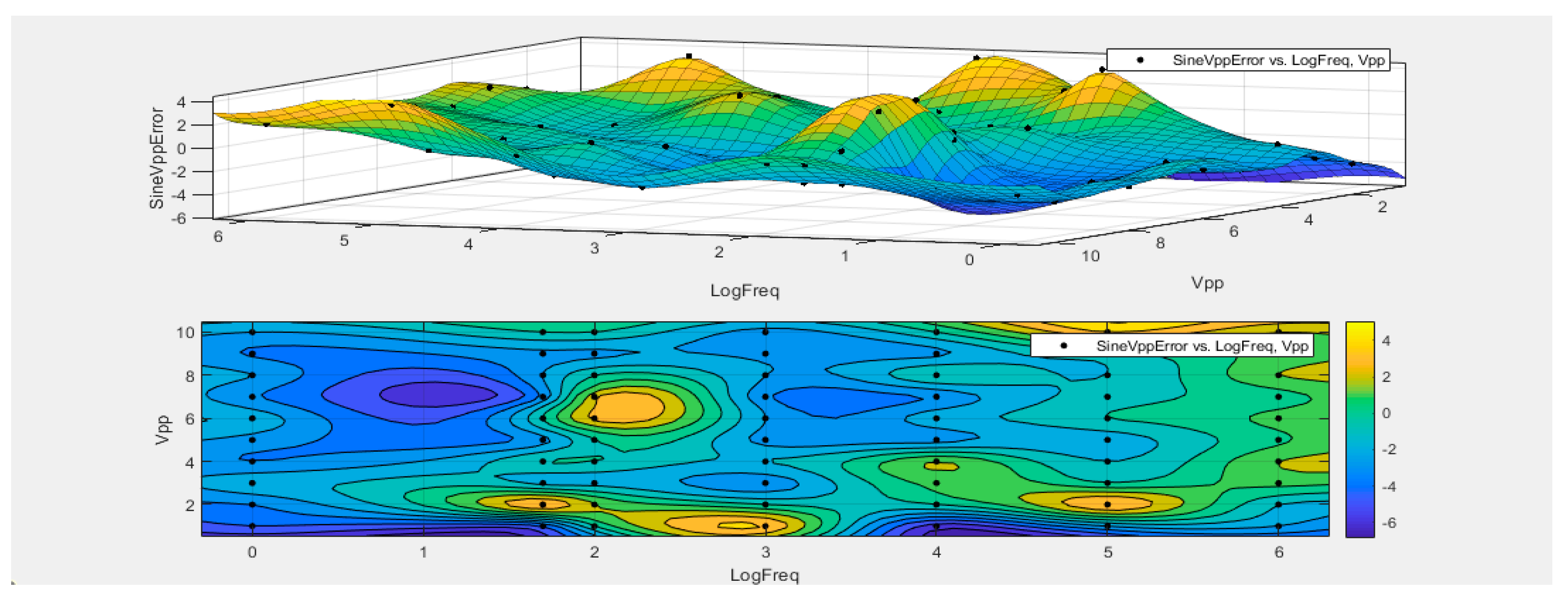

5. Experimental Verification and Result Analysis

5.1. Motor Load Test

5.2. Motor Transient Parameter Test

6. Conclusions

- It can be embedded into the traditional dynamometer system to upgrade the motor transient test and dynamic loading performance of the original equipment;

- The overall function of the system can be tailored, and the dynamometer control core based on modular design can independently realize multi-channel or single channel transient test and dynamic loading functions;

- The uninterrupted transmission of the MS level data stream is realized, and the uninterrupted transmission of the data stream based on the data ping-pong operation algorithm ensures the real-time upload and dynamic refreshing of data.

Author Contributions

Funding

Conflicts of Interest

References

- Bunker, B.; Franchek, M.A.; Thomason, B.E. Robust multivariable control of an engine-dynamometer system. IEEE Trans. Control. Syst. Technol. 1997, 5, 189–199. [Google Scholar] [CrossRef]

- Flieh, H.M.; Totoki, E.; Lorenz, R.D. Dynamic Shaft Torque Observer Structure Enabling Accurate Dynamometer Transient Loss Measurements. IEEE Trans. Ind. Appl. 2018, 54, 6121–6132. [Google Scholar] [CrossRef]

- Sun, X.; Shi, Z.; Cai, Y.; Lei, G.; Guo, Y.; Zhu, J. Driving-Cycle-Oriented Design Optimization of a Permanent Magnet Hub Motor Drive System for a Four-Wheel-Drive Electric Vehicle. IEEE Trans. Transp. Electrif. 2020, 6, 1115–1125. [Google Scholar] [CrossRef]

- Ghahderijani, M.M.; Dehkordi, B.M. Comprehensive Robust and Fast Control of $Z$-Source-Inverter-Based Interior Permanent Magnet Synchronous Motor Drive System. IEEE Trans. Ind. Electron. 2021, 68, 11783–11793. [Google Scholar] [CrossRef]

- Langbauer, C.; Diengsleder-Lambauer, K.; Lieschnegg, M. Downhole Dynamometer Sensors for Sucker Rod Pumps. IEEE Sens. J. 2021, 21, 8543–8552. [Google Scholar] [CrossRef]

- Udovichenko, A.V.; Kaluzhskij, D.; Uvarov, N.; Mekhtiyev, A. Electric Motors for Variable-Speed Drive of Lock Valves. Electronics 2021, 10, 2727. [Google Scholar] [CrossRef]

- Hong, D.K.; Choi, J.H.; Kim, D.J.; Chun, Y.D.; Woo, B.C.; Koo, D.H. Development of a High Speed Induction Motor for Spindle Systems. IEEE Trans. Magn. 2013, 49, 4088–4091. [Google Scholar] [CrossRef]

- Zhao, J.; Zhao, J.; Wang, H.; Song, J.; Dong, F. Precision Position Measurement of Linear Motors Mover Based on Temporal Image Correlation. IEEE Trans. Instrum. Meas. 2019, 68, 3268–3277. [Google Scholar] [CrossRef]

- Xu, J.; Zhang, B.; Fang, H.; Guo, H. Guaranteeing the fault transient performance of aerospace multiphase permanent magnet motor system: An adaptive robust speed control approach. CES Trans. Electr. Mach. Syst. 2020, 4, 114–122. [Google Scholar] [CrossRef]

- Sarani, E.; Vaez-Zadeh, S. Design Procedure and Optimal Guidelines for Overall Enhancement of Steady-State and Transient Performances of Line Start Permanent Magnet Motors. IEEE Trans. Energy Convers. 2017, 32, 885–894. [Google Scholar] [CrossRef]

- Zhang, Z.; Wang, L.; Zhang, J.; Ma, R. Study on Requirements for Load Emulation of the Vehicle With an Electric Braking System. IEEE Trans. Veh. Technol. 2017, 66, 9638–9653. [Google Scholar] [CrossRef]

- Song-Manguelle, J.; Ekemb, G.; Mon-Nzongo, D.L.; Jin, T.; Doumbia, M.L. A Theoretical Analysis of Pulsating Torque Components in AC Machines With Variable Frequency Drives and Dynamic Mechanical Loads. IEEE Trans. Ind. Electron. 2018, 65, 9311–9324. [Google Scholar] [CrossRef]

- Kim, N.; Rousseau, A.; Rask, E. Parameter Estimation for a Lithium-Ion Battery From Chassis Dynamometer Tests. IEEE Trans. Veh. Technol. 2016, 65, 4393–4400. [Google Scholar] [CrossRef]

- Al-Badri, M.; Pillay, P.; Angers, P. A Novel Algorithm for Estimating Refurbished Three-Phase Induction Motors Efficiency Using Only No-Load Tests. IEEE Trans. Energy Convers. 2015, 30, 615–625. [Google Scholar] [CrossRef]

- Korkmaz, E.; Bediz, B.; Gozen, B.A.; Ozdoganlar, O.B. Dynamic characterization of multi-axis dynamometers. Precis. Eng. 2014, 38, 148–161. [Google Scholar] [CrossRef]

- Kang, T.J.; Kim, J.; Lee, S.B.; Yung, C. Experimental Evaluation of Low-Voltage Offline Testing for Induction Motor Rotor Fault Diagnostics. IEEE Trans. Ind. Appl. 2015, 51, 1375–1384. [Google Scholar] [CrossRef]

- Durantay, L.; Velly, N.; Pradurat, J.F.; Chisholm, M. New Testing Method for Large High-Speed Induction Motors. IEEE Trans. Ind. Appl. 2017, 53, 660–666. [Google Scholar] [CrossRef]

- Lee, S.B.; Naeini, A.; Jayaram, S.; Stone, G.C.; Šašić, M. Surge Test-Based Identification of Stator Insulation Component With Partial Discharge Activity for Low Voltage AC Motors. IEEE Trans. Ind. Appl. 2020, 56, 2541–2549. [Google Scholar] [CrossRef]

- de Sousa, L.B.; Sass, F.; Fortes, M.Z. Comparison of Three-Phase Induction Motors Testing Methods using ABNT 17094-3:2018 and IEC 60034-2-1:2014. IEEE Lat. Am. Trans. 2021, 19, 746–754. [Google Scholar] [CrossRef]

- Reddy, P.B.; El-Refaie, A.M.; Zou, M.; Pan, D.; Alexander, J.P.; Tapadia, N.; Grace, K.; Huh, K.-K.; Johnson, F. Performance Testing and Analysis of Synchronous Reluctance Motor Utilizing Dual-Phase Magnetic Material. IEEE Trans. Ind. Appl. 2018, 54, 2193–2201. [Google Scholar] [CrossRef] [Green Version]

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Zhu, C.; Bao, L.; Zheng, B.; Qian, J.; Cai, Y.; Wang, B. Motor Dynamic Loading and Comprehensive Test System Based on FPGA and MCU. Electronics 2022, 11, 1317. https://doi.org/10.3390/electronics11091317

Zhu C, Bao L, Zheng B, Qian J, Cai Y, Wang B. Motor Dynamic Loading and Comprehensive Test System Based on FPGA and MCU. Electronics. 2022; 11(9):1317. https://doi.org/10.3390/electronics11091317

Chicago/Turabian StyleZhu, Chunxiang, Linxin Bao, Bowen Zheng, Jiacheng Qian, Yongdong Cai, and Binrui Wang. 2022. "Motor Dynamic Loading and Comprehensive Test System Based on FPGA and MCU" Electronics 11, no. 9: 1317. https://doi.org/10.3390/electronics11091317

APA StyleZhu, C., Bao, L., Zheng, B., Qian, J., Cai, Y., & Wang, B. (2022). Motor Dynamic Loading and Comprehensive Test System Based on FPGA and MCU. Electronics, 11(9), 1317. https://doi.org/10.3390/electronics11091317