Performance Benchmarking of TFET and FinFET Digital Circuits from a Synthesis-Based Perspective

Abstract

:1. Introduction

2. Methodology

2.1. Device Specification

2.2. Sizing Methodology

3. Results and Discussion

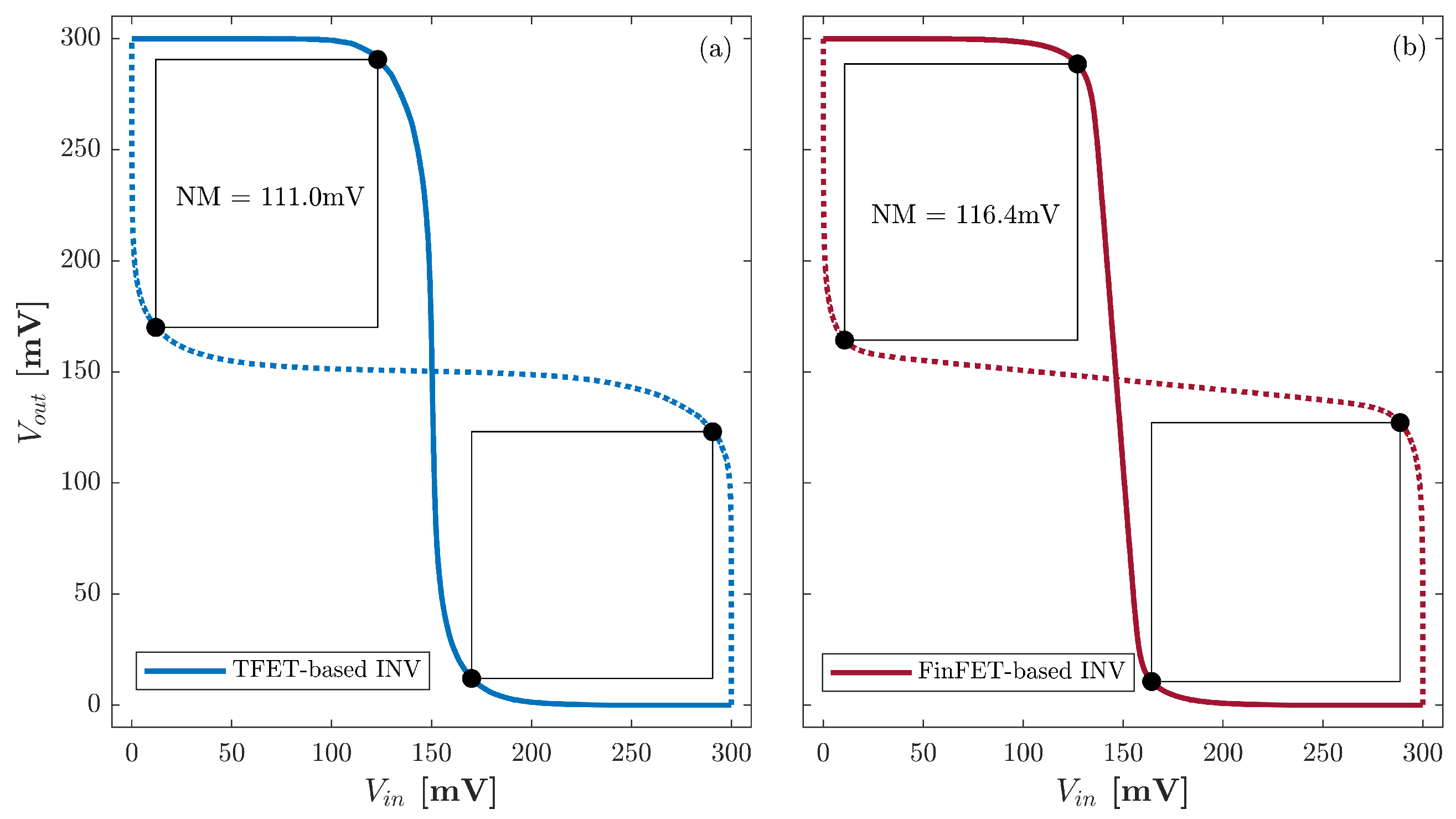

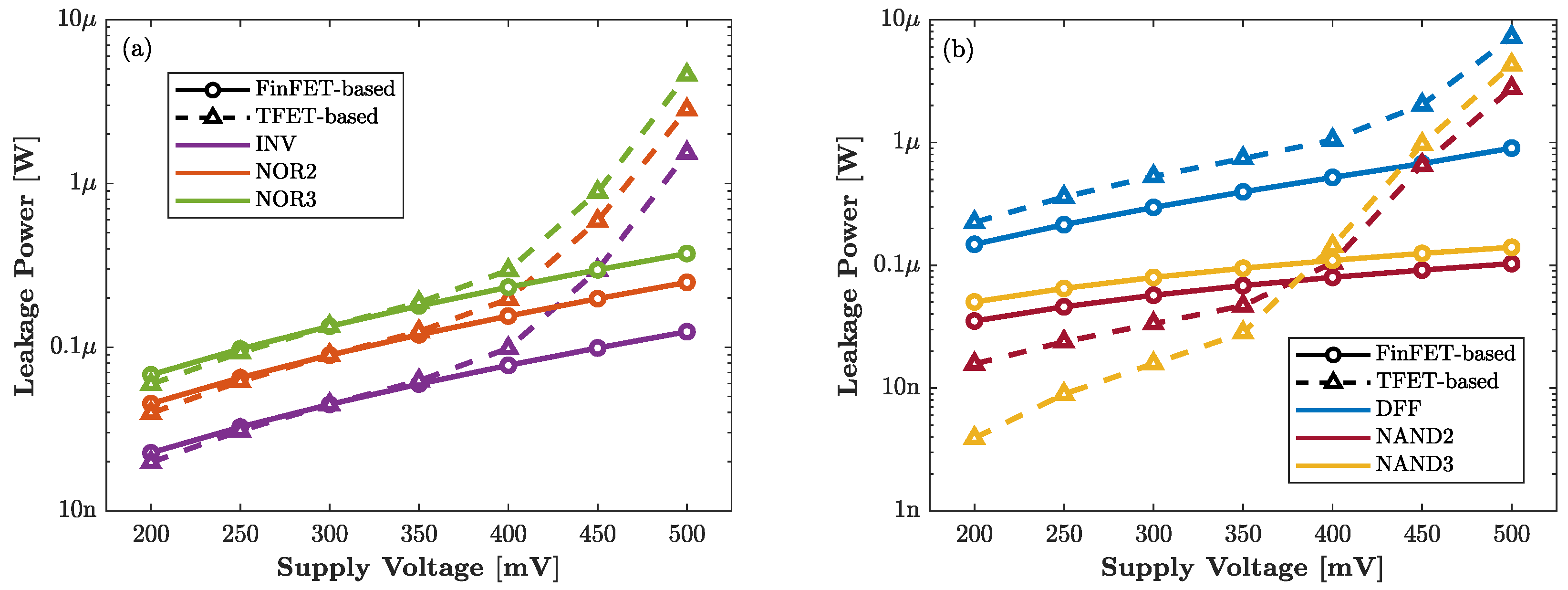

3.1. Characterization Results

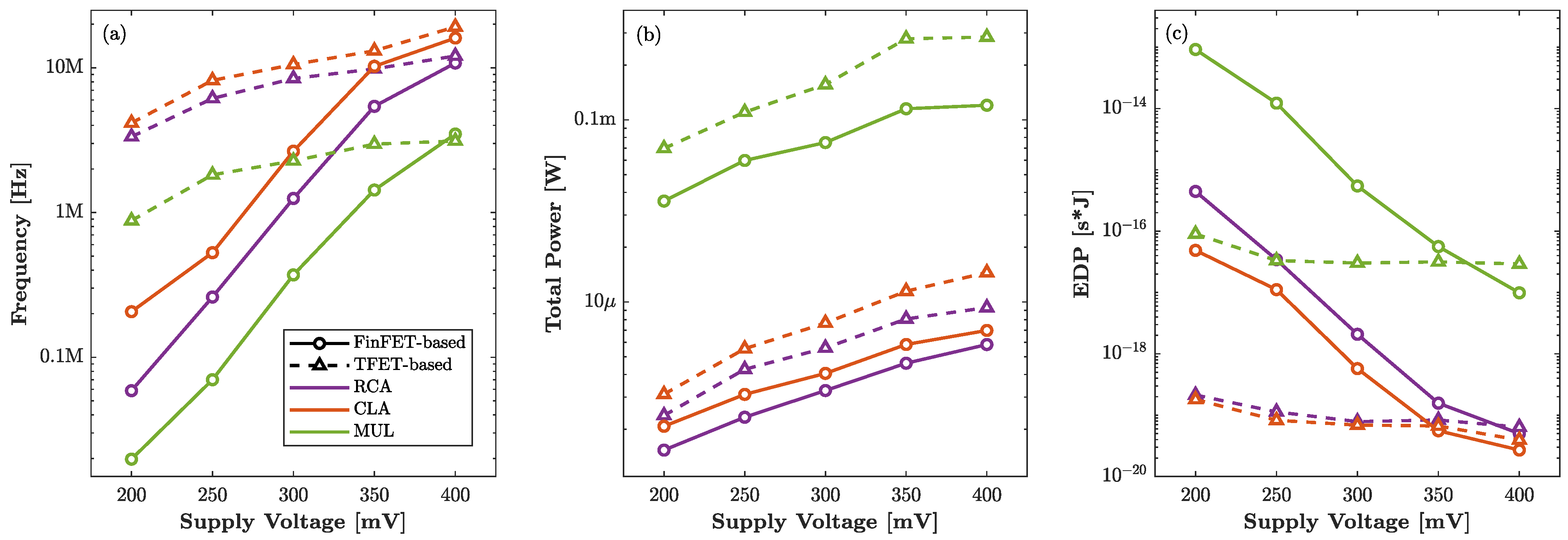

3.2. Synthesis Results

4. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Wang, A.; Chandrakasan, A. A 180 mV FFT processor using subthreshold circuit techniques. In Proceedings of the 2004 IEEE International Solid-State Circuits Conference (IEEE Cat. No.04CH37519), San Francisco, CA, USA, 15–19 February 2004; Volume 1, pp. 292–529. [Google Scholar] [CrossRef]

- Calhoun, B.; Chandrakasan, A. Characterizing and modeling minimum energy operation for subthreshold circuits. In Proceedings of the 2004 International Symposium on Low Power Electronics and Design (IEEE Cat. No.04TH8758), Newport Beach, CA, USA, 11 August 2004; pp. 90–95. [Google Scholar] [CrossRef]

- Zambrano, B.; Garzón, E.; Strangio, S.; Crupi, F.; Lanuzza, M. A 0.05 mm2, 350 mV, 14 nW Fully-Integrated Temperature Sensor in 180-nm CMOS. IEEE Trans. Circuits Syst. II Express Briefs 2021. [Google Scholar] [CrossRef]

- Lin, Z.; Li, L.; Wu, X.; Peng, C.; Lu, W.; Zhao, Q. Half-Select Disturb-Free 10T Tunnel FET SRAM Cell With Improved Noise Margin and Low Power Consumption. IEEE Trans. Circuits Syst. II Express Briefs 2021, 68, 2628–2632. [Google Scholar] [CrossRef]

- Frustaci, F.; Lanuzza, M.; Zicari, P.; Perri, S.; Corsonello, P. Designing high-speed adders in power-constrained environments. IEEE Trans. Circuits Syst. II Express Briefs 2009, 56, 172–176. [Google Scholar] [CrossRef]

- Alioto, M. Ultra-Low Power VLSI Circuit Design Demystified and Explained: A Tutorial. IEEE Trans. Circuits Syst. I Regul. Pap. 2012, 59, 3–29. [Google Scholar] [CrossRef]

- Taco, R.; Levi, I.; Lanuzza, M.; Fish, A. An 88-fJ/40-MHz [0.4 V]–0.61-pJ/1-GHz [0.9 V] Dual-Mode Logic 8 × 8 bit Multiplier Accumulator With a Self-Adjustment Mechanism in 28-nm FD-SOI. IEEE J.-Solid-State Circuits 2018, 54, 560–568. [Google Scholar] [CrossRef]

- Shavit, N.; Stanger, I.; Taco, R.; Lanuzza, M.; Fish, A. A 0.8-V, 1.54-pJ/940-MHz Dual-Mode Logic-Based 16 × 16-b Booth Multiplier in 16-nm FinFET. IEEE Solid-State Circuits Lett. 2020, 3, 314–317. [Google Scholar] [CrossRef]

- Vicuña, K.; Mosquera, C.; Musello, A.; Benedictis, S.; Rendón, M.; Garzón, E.; Prócel, L.M.; Trojman, L.; Taco, R. Energy Efficient Self-Adaptive Dual Mode Logic Address Decoder. Electronics 2021, 10, 1052. [Google Scholar] [CrossRef]

- Stanger, I.; Shavit, N.; Taco, R.; Lanuzza, M.; Fish, A. Silicon Evaluation of Multimode Dual Mode Logic for PVT-Aware Datapaths. IEEE Trans. Circuits Syst. II Express Briefs 2020, 67, 1639–1643. [Google Scholar] [CrossRef]

- Taco, R.; Levi, I.; Lanuzza, M.; Fish, A. Low voltage logic circuits exploiting gate level dynamic body biasing in 28 nm UTBB FD-SOI. Solid-State Electron. 2016, 117, 185–192. [Google Scholar] [CrossRef]

- Saripalli, V.; Datta, S.; Narayanan, V.; Kulkarni, J.P. Variation-tolerant ultra low-power heterojunction tunnel FET SRAM design. In Proceedings of the 2011 IEEE/ACM International Symposium on Nanoscale Architectures, San Diego, CA, USA, 8–9 June 2011; pp. 45–52. [Google Scholar] [CrossRef] [Green Version]

- Guo, L.; Ye, L.; Chen, C.; Huang, Q.; Yang, L.; Lv, Z.; An, X.; Huang, R. Benchmarking TFET from a circuit level perspective: Applications and guideline. In Proceedings of the 2017 IEEE International Symposium on Circuits and Systems (ISCAS), Baltimore, MD, USA, 28–31 May 2017; pp. 1–4. [Google Scholar] [CrossRef]

- Taco, R.; Levi, I.; Lanuzza, M.; Fish, A. Extended exploration of low granularity back biasing control in 28nm UTBB FD-SOI technology. In Proceedings of the 2016 IEEE International Symposium on Circuits and Systems (ISCAS), Montreal, QC, Canada, 22–25 May 2016; pp. 41–44. [Google Scholar] [CrossRef]

- Strangio, S.; Palestri, P.; Lanuzza, M.; Crupi, F.; Esseni, D.; Selmi, L. Assessment of InAs/AlGaSb Tunnel-FET Virtual Technology Platform for Low-Power Digital Circuits. IEEE Trans. Electron. Devices 2016, 63, 2749–2756. [Google Scholar] [CrossRef]

- Xie, Q.; Lin, X.; Wang, Y.; Chen, S.; Dousti, M.J.; Pedram, M. Performance Comparisons Between 7-nm FinFET and Conventional Bulk CMOS Standard Cell Libraries. IEEE Trans. Circuits Syst. II Express Briefs 2015, 62, 761–765. [Google Scholar] [CrossRef]

- Chen, S.; Wang, Y.; Lin, X.; Xie, Q.; Pedram, M. Performance prediction for multiple-threshold 7nm-FinFET-based circuits operating in multiple voltage regimes using a cross-layer simulation framework. In Proceedings of the 2014 SOI-3D-Subthreshold Microelectronics Technology Unified Conference (S3S), Millbrae, CA, USA, 6–9 October 2014; pp. 1–2. [Google Scholar] [CrossRef]

- Garzón, E.; Lanuzza, M.; Taco, R.; Strangio, S. Ultralow Voltage FinFET- Versus TFET-Based STT-MRAM Cells for IoT Applications. Electronics 2021, 10, 1756. [Google Scholar] [CrossRef]

- Zhang, Q.; Zhao, W.; Seabaugh, A. Low-subthreshold-swing tunnel transistors. IEEE Electron. Device Lett. 2006, 27, 297–300. [Google Scholar] [CrossRef]

- Arevalo, A.; Liautard, R.; Romero, D.; Trojman, L.; Procel, L.M. New Insight for next Generation SRAM: Tunnel FET versus FinFET for Different Topologies. In Proceedings of the 2019 32nd Symposium on Integrated Circuits and Systems Design (SBCCI), Sao Paulo, Brazil, 26–30 August 2019; pp. 1–6. [Google Scholar] [CrossRef]

- Strangio, S.; Palestri, P.; Lanuzza, M.; Esseni, D.; Crupi, F.; Selmi, L. Benchmarks of a III-V TFET technology platform against the 10-nm CMOS FinFET technology node considering basic arithmetic circuits. Solid-State Electron. 2017, 128, 37–42. [Google Scholar] [CrossRef]

- Heo, U.; Li, X.; Liu, H.; Gupta, S.; Datta, S.; Narayanan, V. A High-Efficiency Switched-Capacitance HTFET Charge Pump for Low-Input-Voltage Applications. In Proceedings of the 2015 28th International Conference on VLSI Design, Bangalore, India, 3–7 January 2015; pp. 304–309. [Google Scholar] [CrossRef]

- Strangio, S.; Settino, F.; Palestri, P.; Lanuzza, M.; Crupi, F.; Esseni, D.; Selmi, L. Digital and analog TFET circuits: Design and benchmark. Solid-State Electron. 2018, 146, 50–65. [Google Scholar] [CrossRef] [Green Version]

- Esseni, D.; Pala, M.G.; Rollo, T. Essential Physics of the OFF-State Current in Nanoscale MOSFETs and Tunnel FETs. IEEE Trans. Electron. Devices 2015, 62, 3084–3091. [Google Scholar] [CrossRef]

- Settino, F.; Lanuzza, M.; Strangio, S.; Crupi, F.; Palestri, P.; Esseni, D.; Selmi, L. Understanding the Potential and Limitations of Tunnel FETs for Low-Voltage Analog/Mixed-Signal Circuits. IEEE Trans. Electron. Devices 2017, 64, 2736–2743. [Google Scholar] [CrossRef]

- Wu, T.C.; Chen, C.J.; Chen, Y.N.; Hu, V.P.H.; Su, P.; Chuang, C.T. Evaluation of energy-efficient latch circuits with hybrid tunneling FET and FinFET devices for ultra-low-voltage applications. In Proceedings of the 2015 28th IEEE International System-on-Chip Conference (SOCC), Beijing, China, 8–11 September 2015; pp. 339–344. [Google Scholar] [CrossRef]

- Lanuzza, M.; Strangio, S.; Crupi, F.; Palestri, P.; Esseni, D. Mixed Tunnel-FET/MOSFET Level Shifters: A New Proposal to Extend the Tunnel-FET Application Domain. IEEE Trans. Electron. Devices 2015, 62, 3973–3979. [Google Scholar] [CrossRef] [Green Version]

- Morris, D.H.; Vaidyanathan, K.; Avci, U.E.; Liu, H.; Karnik, T.; Young, I.A. Enabling high-performance heterogeneous TFET/CMOS logic with novel circuits using TFET unidirectionality and low-VDD operation. In Proceedings of the 2016 IEEE Symposium on VLSI Technology, Honolulu, HI, USA, 14–16 June 2016; pp. 1–2. [Google Scholar] [CrossRef]

- ASU. Predictive Technology Model (PTM). Available online: http://ptm.asu.edu (accessed on 21 January 2021).

- Lin, L.; Jain, S.; Alioto, M. Sub-nW Microcontroller With Dual-Mode Logic and Self-Startup for Battery-Indifferent Sensor Nodes. IEEE J.-Solid-State Circuits 2021, 56, 1618–1629. [Google Scholar] [CrossRef]

| Gate | INV | NOR2 | NOR3 | NAND2 | NAND3 |

|---|---|---|---|---|---|

| TFET | 3/1 | 4/1 | 5/1 | 3/6 | 3/17 |

| FinFET | 1/1 | 1/1 | 1/1 | 1/3 | 1/6 |

| [mV] | FinFET-Based | TFET-Based | ||||||||

|---|---|---|---|---|---|---|---|---|---|---|

| INV | NOR2 | NOR3 | NAND2 | NAND3 | INV | NOR2 | NOR3 | NAND2 | NAND3 | |

| 200 | 70.8% | 69.2% | 67.7% | 72.3% | 72.5% | 66.0% | 65.0% | 65.0% | 68.0% | 69.0% |

| 300 | 77.6% | 77.6% | 77.5% | 80.5% | 80.9% | 74.0% | 75.5% | 75.0% | 77.4% | 78.1% |

| 400 | 81.2% | 81.2% | 81.2% | 84.5% | 84.0% | 67.0% | 62.3% | 60.0% | 65.4% | 66.7% |

| Parameter | Value |

|---|---|

| Voltage (mV) | 200–500 |

| Temperature (°C) | 25 |

| Process | Typical–Typical |

| Logic Gates | DFF, INV, NAND2, NAND3*, NOR2, NOR3* |

| Technology | 10 nm |

| Devices | FinFET and TFET |

| Load Capacitance Range (fF) | 60–1000 |

| Input Slope Range (ns) | 0.895–1288 |

| Gate | FinFET-Based | TFET-Based |

|---|---|---|

| DFF-CLK | 267 | 675 |

| DFF-D | 94 | 231 |

| INV | 94 | 231 |

| NAND2 | 189 | 489 |

| NAND3 | 331 | 1060 |

| NOR2 | 94 | 290 |

| NOR3 | 94 | 350 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Rendón, M.; Cao, C.; Landázuri, K.; Garzón, E.; Prócel, L.M.; Taco, R. Performance Benchmarking of TFET and FinFET Digital Circuits from a Synthesis-Based Perspective. Electronics 2022, 11, 632. https://doi.org/10.3390/electronics11040632

Rendón M, Cao C, Landázuri K, Garzón E, Prócel LM, Taco R. Performance Benchmarking of TFET and FinFET Digital Circuits from a Synthesis-Based Perspective. Electronics. 2022; 11(4):632. https://doi.org/10.3390/electronics11040632

Chicago/Turabian StyleRendón, Mateo, Christian Cao, Kevin Landázuri, Esteban Garzón, Luis Miguel Prócel, and Ramiro Taco. 2022. "Performance Benchmarking of TFET and FinFET Digital Circuits from a Synthesis-Based Perspective" Electronics 11, no. 4: 632. https://doi.org/10.3390/electronics11040632

APA StyleRendón, M., Cao, C., Landázuri, K., Garzón, E., Prócel, L. M., & Taco, R. (2022). Performance Benchmarking of TFET and FinFET Digital Circuits from a Synthesis-Based Perspective. Electronics, 11(4), 632. https://doi.org/10.3390/electronics11040632