An 11-Bit 10 MS/s SAR ADC with C–R DAC Calibration and Comparator Offset Calibration

Abstract

1. Introduction

2. Design of 11-Bit 10 MS/s SAR ADC Using C–R DAC

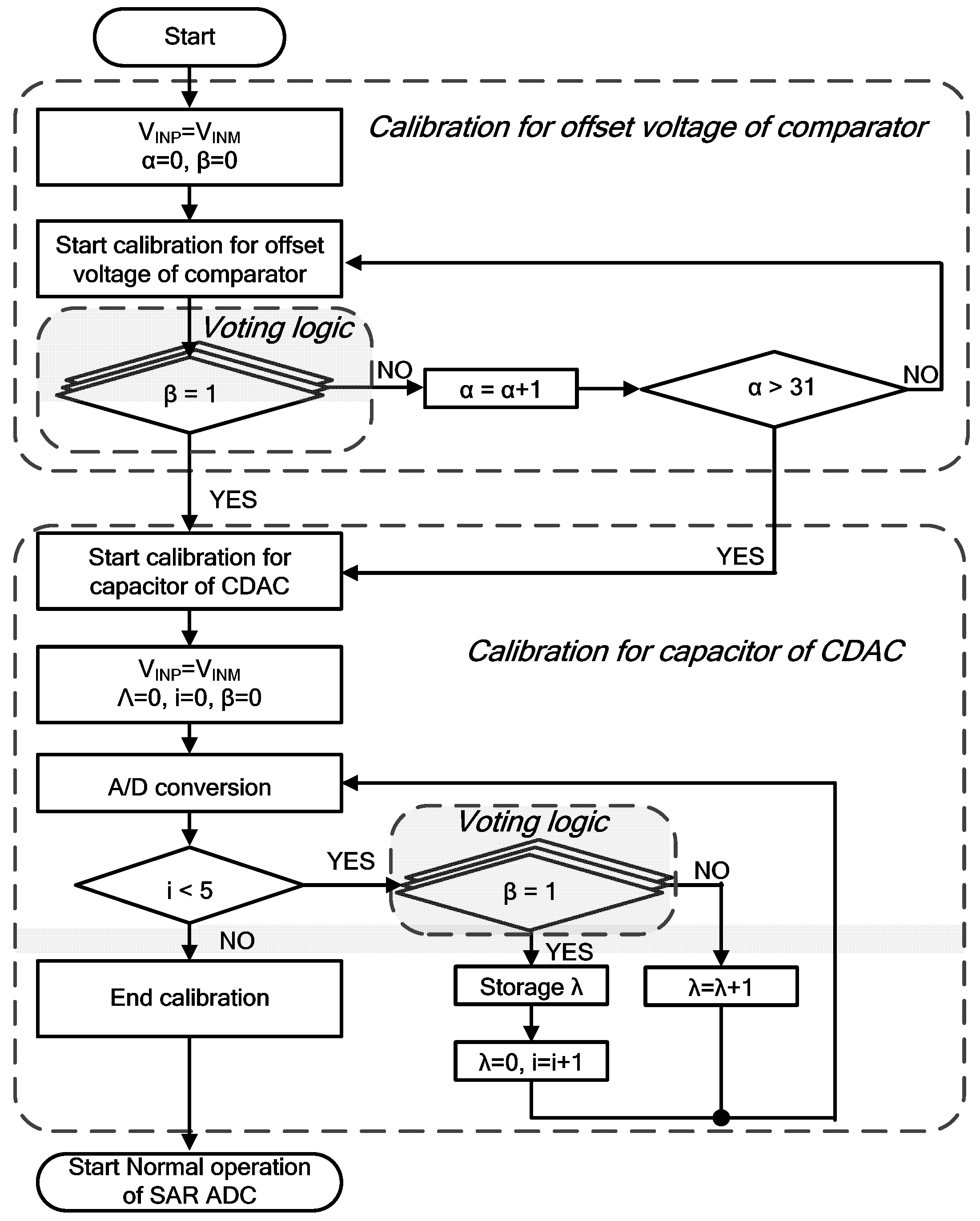

3. Proposed C–R DAC Calibration and Comparator Offset Calibration

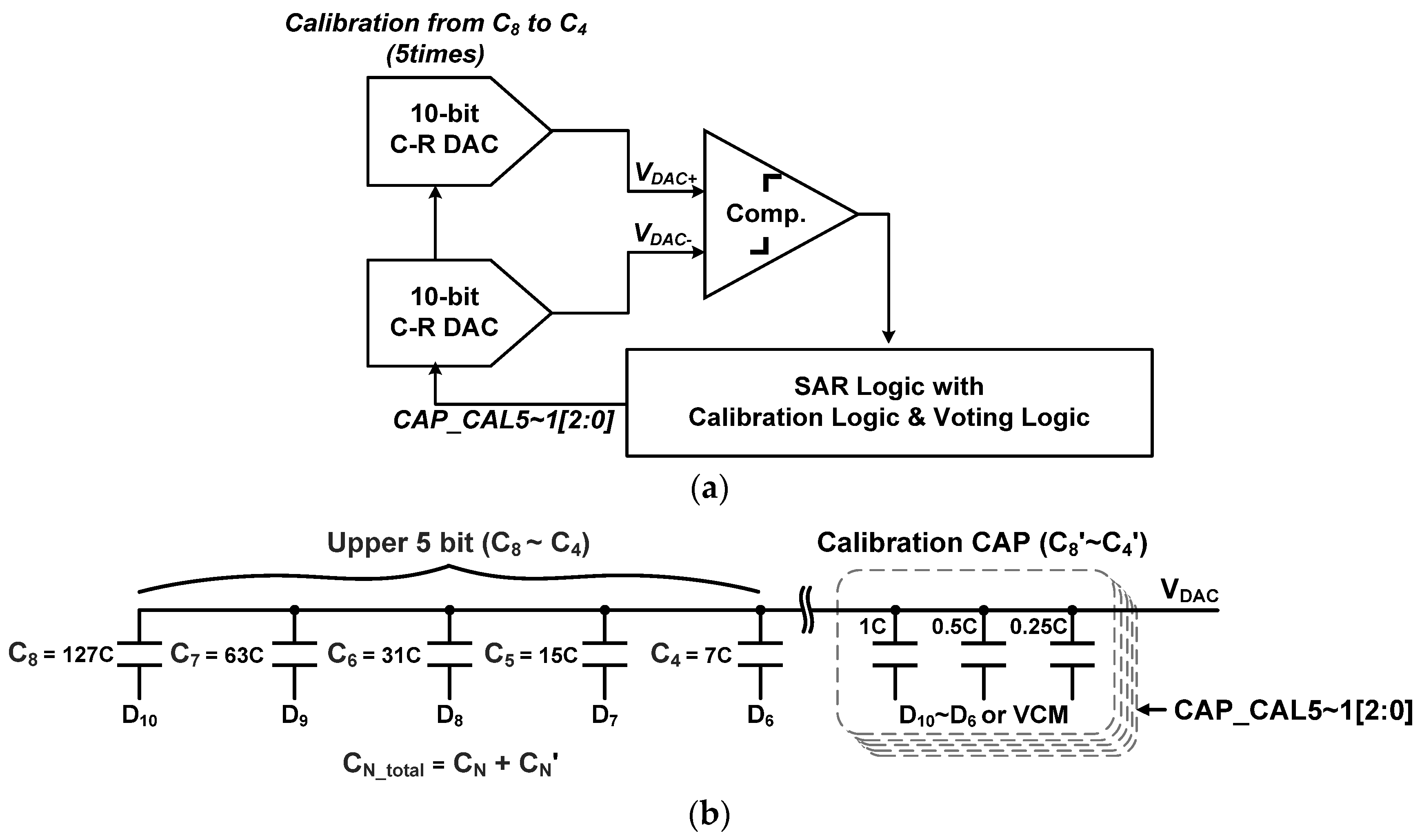

3.1. C–R DAC Calibration

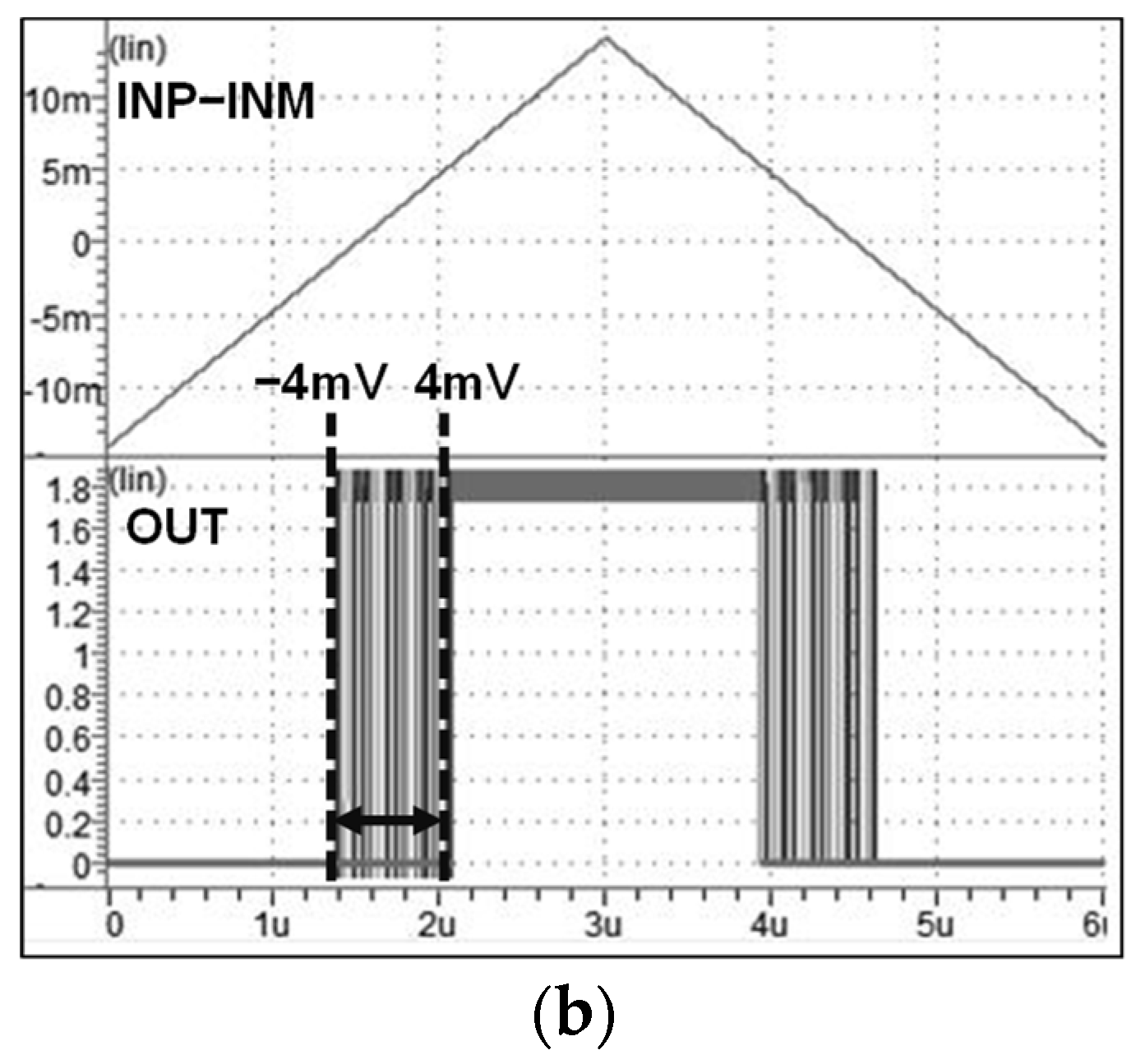

3.2. Comparator Offset Calibration

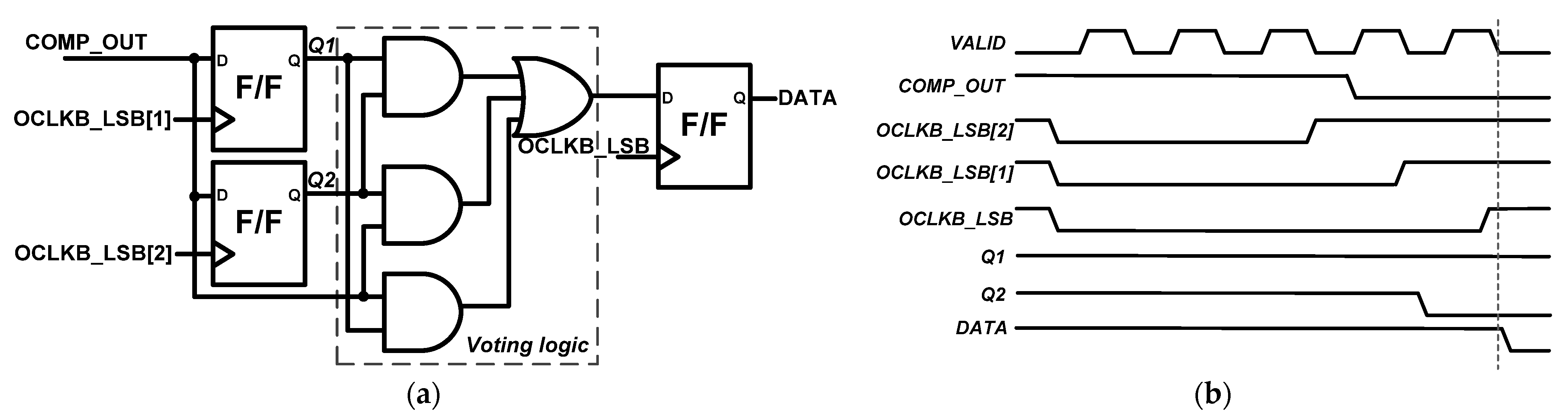

3.3. Voting Logic

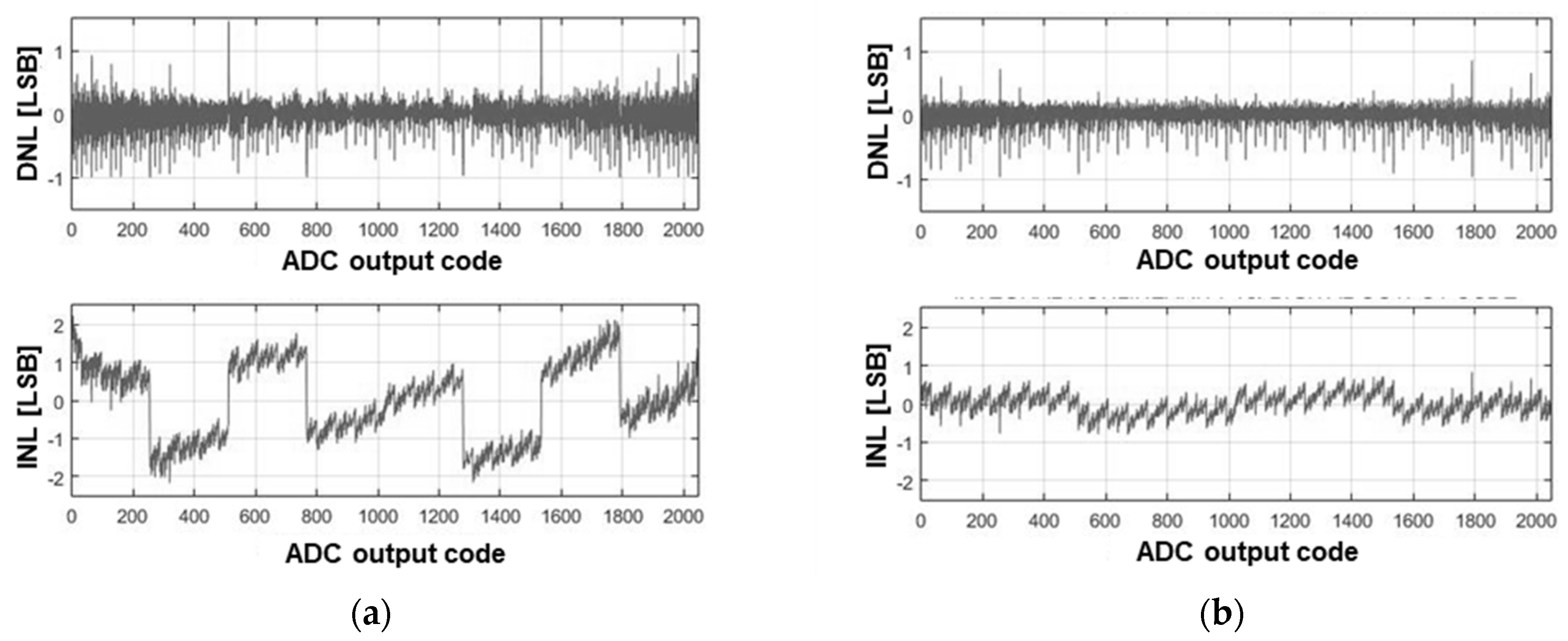

4. Chip Implement and Measurement Results

5. Conclusions

Author Contributions

Funding

Informed Consent Statement

Acknowledgments

Conflicts of Interest

References

- Choi, S.; Ku, H.-S.; Son, H.; Kim, B.; Park, H.-J.; Sim, J.-Y. An 84.6-dB-SNDR and 98.2-dB-SFDR Residue-Integrated SAR ADC for Low-Power Sensor Applications. IEEE J. Solid-State Circuits 2018, 53, 404–417. [Google Scholar] [CrossRef]

- Zhang, D.; Bhide, A.; Alvandpour, A. A 53-nW 9.1-ENOB 1-kS/s SAR ADC in 0.13-μm CMOS for Medical Implant Devices. IEEE J. Solid-State Circuits 2012, 47, 1585–1593. [Google Scholar] [CrossRef]

- Harpe, P.J.A.; Zhou, C.; Bi, Y.; van der Meijs, N.P.; Wang, X.; Philips, K.; Dolmans, G.; de Groot, H. A 26 μW 8 bit 10 MS/s Asynchronous SAR ADC for Low Energy Radios. IEEE J. Solid-State Circuits 2011, 46, 1585–1595. [Google Scholar] [CrossRef]

- Liu, C.; Kuo, C.; Lin, Y. A 10 bit 320 MS/s Low-Cost SAR ADC for IEEE 802.11ac Applications in 20 nm CMOS. IEEE J. Solid-State Circuits 2015, 50, 2645–2654. [Google Scholar] [CrossRef]

- Guo, W.; Kim, Y.; Tewfik, A.H.; Sun, N. A Fully Passive Compressive Sensing SAR ADC for Low-Power Wireless Sensors. IEEE J. Solid-State Circuits 2017, 52, 2154–2167. [Google Scholar] [CrossRef]

- Liu, S.; Rabuske, T.; Paramesh, J.; Pileggi, L.; Fernandes, J. Analysis and Background Self-Calibration of Comparator Offset in Loop-Unrolled SAR ADCs. IEEE Trans. Circuits Syst. I Regul. Pap. 2017, 65, 458–470. [Google Scholar] [CrossRef]

- Zhou, H.; Gui, X.; Gao, P. Design of a 12-bit 0.83 MS/s SAR ADC for an IPMI SoC. In Proceedings of the 2015 28th IEEE International System-on-Chip Conference, Beijing, China, 8–11 September 2015; pp. 175–179. [Google Scholar]

- Zhang, C.; Wang, H. Reduction of Parasitic Capacitance Impact in Low-Power SAR ADC. IEEE Trans. Instrum. Meas. 2011, 61, 587–594. [Google Scholar] [CrossRef]

- Um, J.; Kim, Y.; Song, E.; Sim, J.; Park, H. A Digital-Domain Calibration of Split-Capacitor DAC for a Differential SAR ADC Without Additional Analog Circuits. IEEE Trans. Circuits Syst. I Regul. Pap. 2013, 60, 2845–2856. [Google Scholar] [CrossRef]

- Zhang, M.; Noh, K.; Fan, X.; Sánchez-Sinencio, E. A 0.8–1.2 V 10–50 MS/s 13-bit Subranging Pipelined-SAR ADC Using a Temperature-Insensitive Time-Based Amplifier. IEEE J. Solid-State Circuits 2017, 52, 2991–3005. [Google Scholar] [CrossRef]

- Zhu, Y.; Chan, C.; Wong, S.; Seng-Pan, U.; Martins, R.P. Histogram-Based Ratio Mismatch Calibration for Bridge-DAC in 12-bit 120 MS/s SAR ADC. IEEE Trans. Very Large Scale Integr. VLSI Syst. 2015, 24, 1203–1207. [Google Scholar] [CrossRef]

- Wang, X.; Li, F.; Wang, Z. A Simple Histogram-Based Capacitor Mismatch Calibration in SAR ADCs. IEEE Trans. Circuits Syst. II Express Briefs 2020, 67, 2838–2842. [Google Scholar] [CrossRef]

- Yoshioka, M.; Ishikawa, K.; Takayama, T.; Tsukamoto, S. A 10-b 50-MS/s 820-uW SAR ADC With On-Chip Digital Calibration. IEEE Trans. Biomed. Circuits Syst. 2010, 2010, 410–416. [Google Scholar] [CrossRef] [PubMed]

- Youn, E.; Jang, Y.-C. 12-bit 20M-S/s SAR ADC using C-R DAC and Capacitor Calibration. In Proceedings of the 2018 International SoC Design Conference (ISOCC), Deagu, Korea, 12–15 November 2018; pp. 2163–9612. [Google Scholar]

- Lee, S.-Y.; Tsou, C.; Li, Y.-C. Single-Bin DFT-Based Digital Calibration Technique for CDAC in SAR ADCs. IEEE Trans. Circuits Syst. I Regul. Pap. 2019, 66, 4582–4591. [Google Scholar] [CrossRef]

- Peng, X.; Gao, A.; Chen, Z.; Zhang, H.; Li, Y.; Cao, W.; Liu, X.; Tang, H. A Novel Comparator Offset Calibration Technique for SAR ADCs. In Proceedings of the 2018 IEEE International Conference on Electron Devices and Solid State Circuits (EDSSC), Shenzhen, China, 6–8 June 2018. [Google Scholar]

- Park, S.-M.; Jeong, Y.-H.; Hwang, Y.-J.; Lee, P.-H.; Kim, Y.-W.; Son, J.; Lee, H.-Y.; Jang, Y.-C. A 10-bbit 20-MS/s Asynchronous SAR ADC with Meta-Stability Detector Using Replica Comparators. IEICE Trans. Electron. 2016, 99, 651–654. [Google Scholar] [CrossRef]

- Harpe, P.; Cantatore, E.; Roermund, A.V. An oversampled 12/14b SAR ADC with noise reduction and linearity enhancements achieving up to 79.1 dB SNDR. In Proceedings of the 2014 IEEE International Solid-State Circuits Conference Digest of Technical Papers, San Francisco, CA, USA, 9–13 February 2014. [Google Scholar]

- Harpe, P.; Cantatore, E.; Roermund, A.V. A 10b/12b 40kS/s SAR ADC With Data-Driven Noise Reduction Achieving up to 10.1b ENOB at 2.2 fJ/Conversion-Step. IEEE J. Solid-State Circuits 2013, 48, 3011–3018. [Google Scholar] [CrossRef]

- Zhou, Y.; Xu, B.; Chiu, Y. A 12 bit 160 MS/s Two-Step SAR ADC With Background Bit-Weight Calibration Using a Time-Domain Proximity Detector. IEEE J. Solid-State Circuits 2015, 50, 920–931. [Google Scholar] [CrossRef]

- Liu, W.; Huang, P.; Chiu, Y. A 12-bit 50-MS/s 3.3-mW SAR ADC with background digital calibration. In Proceedings of the IEEE 2012 Custom Integrated Circuits Conference, San Jose, CA, USA, 9–12 September 2012. [Google Scholar]

- Chan, C.; Zhu, Y.; Li, C.; Zhang, W.; Ho, I.; Wei, L.; Seng-Pan, U.; Martins, R.P. 60-dB SNDR 100-MS/s SAR ADCs With Threshold Reconfigurable Reference Error Calibration. IEEE J. Solid-State Circuits 2017, 52, 2576–2588. [Google Scholar] [CrossRef]

- Bindra, H.S.; Annema, A.; Simon, M.L.; Nauta, B. A 0.2–8 MS/s 10b flexible SAR ADC achieving 0.35–2.5 fJ/conv-step and using self-quenched dynamic bias comparator. In Proceedings of the 2019 Symposium on VLSI Circuits, Kyoto, Japan, 9–14 July 2019. [Google Scholar]

| Item | CDAC | C–R DAC |

|---|---|---|

| CDAC | 2048·C | 512·C |

| Item | [20] | [21] | [22] | [23] | This Work |

|---|---|---|---|---|---|

| Architecture | Pipelined SAR | SAR | SAR | SAR | SAR |

| Calibration | Yes | Yes | Yes | No | Yes |

| Resolution [bit] | 12 | 12 | 11 | 10 | 11 |

| Technology [nm] | 40 | 90 | 65 | 65 | 180 |

| Supply [V] | 1.1 | 1.2 | 1.2 | 1.3 | 1.8 |

| FS [MHz] | 160 | 50 | 100 | 8 | 10 |

| Power [μW] | 4960 | 4700 | 2440 | 12.8 | 583 |

| Area [mm2] | 0.042 | 0.118 | 0.012 | 0.04 | 0.29 |

| SFDR [dB] | 86.9 | 82.7 | 68.35 | 66 | 78.57 |

| SNDR [dB] | 65.3 | 65.1 | 57.93 | 57.74 | 63.77 |

| ENOB [bits] | 10.5 | 10.5 | 9.33 | 9.3 | 10.3 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Jung, H.; Youn, E.; Jang, Y.-C. An 11-Bit 10 MS/s SAR ADC with C–R DAC Calibration and Comparator Offset Calibration. Electronics 2022, 11, 3654. https://doi.org/10.3390/electronics11223654

Jung H, Youn E, Jang Y-C. An 11-Bit 10 MS/s SAR ADC with C–R DAC Calibration and Comparator Offset Calibration. Electronics. 2022; 11(22):3654. https://doi.org/10.3390/electronics11223654

Chicago/Turabian StyleJung, Hoyong, Eunji Youn, and Young-Chan Jang. 2022. "An 11-Bit 10 MS/s SAR ADC with C–R DAC Calibration and Comparator Offset Calibration" Electronics 11, no. 22: 3654. https://doi.org/10.3390/electronics11223654

APA StyleJung, H., Youn, E., & Jang, Y.-C. (2022). An 11-Bit 10 MS/s SAR ADC with C–R DAC Calibration and Comparator Offset Calibration. Electronics, 11(22), 3654. https://doi.org/10.3390/electronics11223654