Research on an Improved Three-Level SVPWM Modulation Algorithm Based on ID-NPC Topology

Abstract

1. Introduction

2. Improved D-NPC Topology

3. Improved Three-Level SVPWM Control Strategy

3.1. Three-Level SVPWM Sequential Synthesis Algorithm

3.2. Vector Synthesis Algorithm of 2 × Amplitude Substitution

3.3. Vector Synthesis Algorithm of 1/2 × Amplitude Substitution

3.4. Time Effect Optimization

4. Simulation and Analysis of Modulation Algorithm Based on ID-NPC

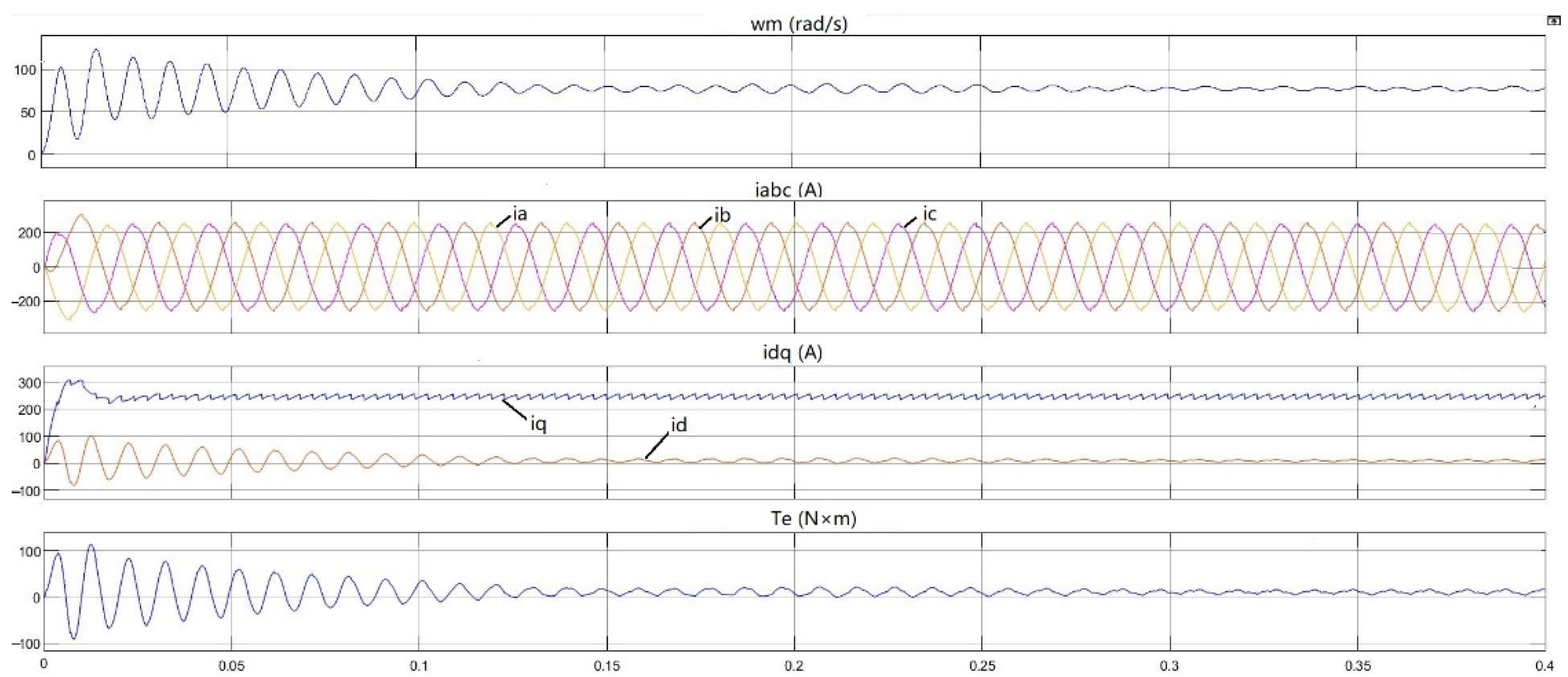

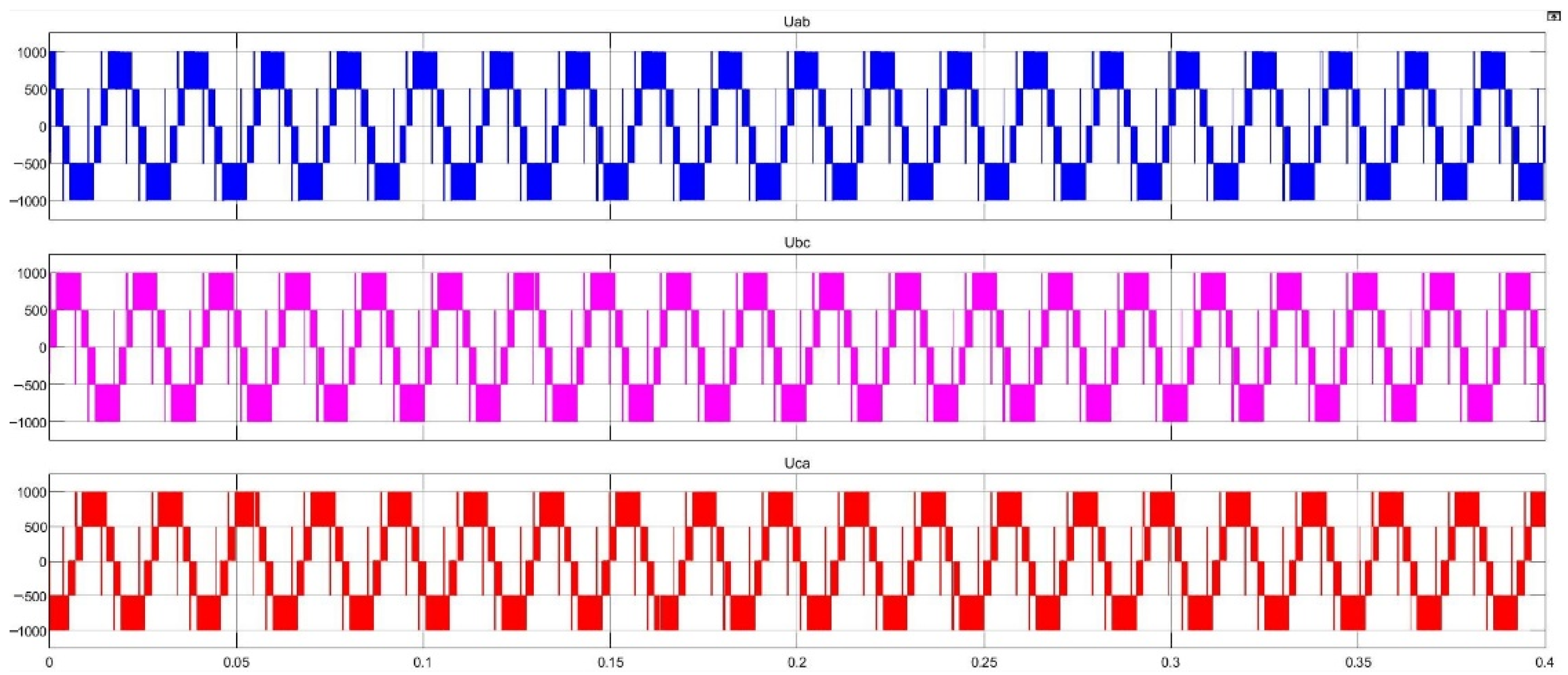

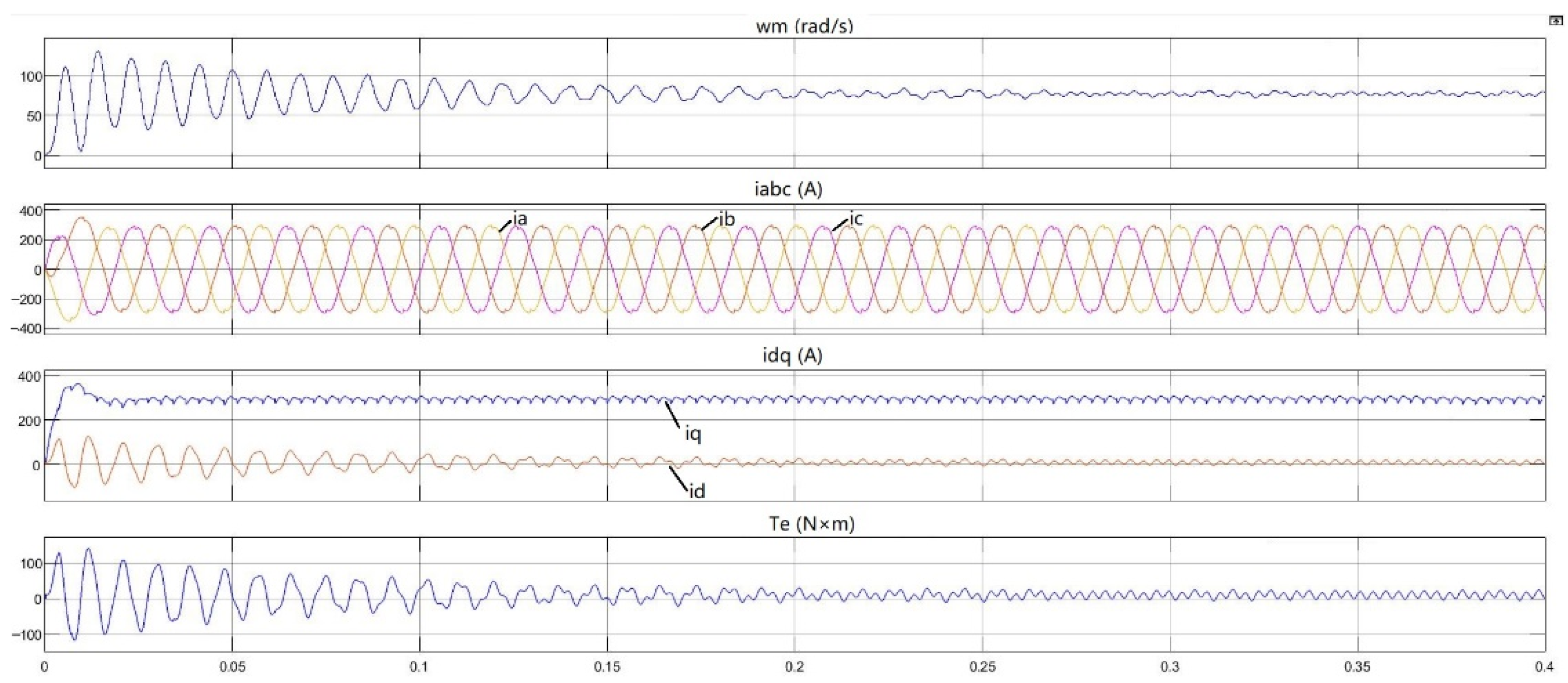

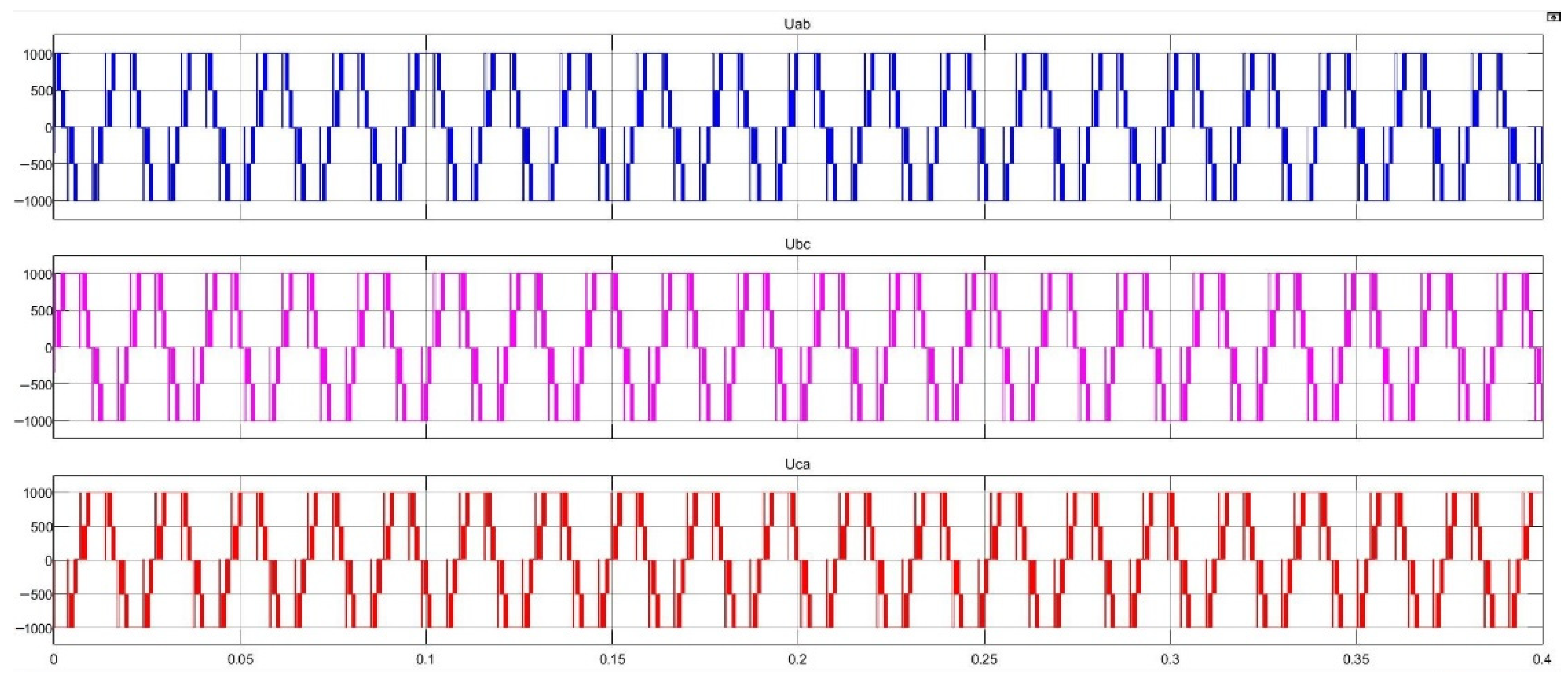

4.1. Waveform of Vector Synthesis Algorithm of 2 × Amplitude Substitution

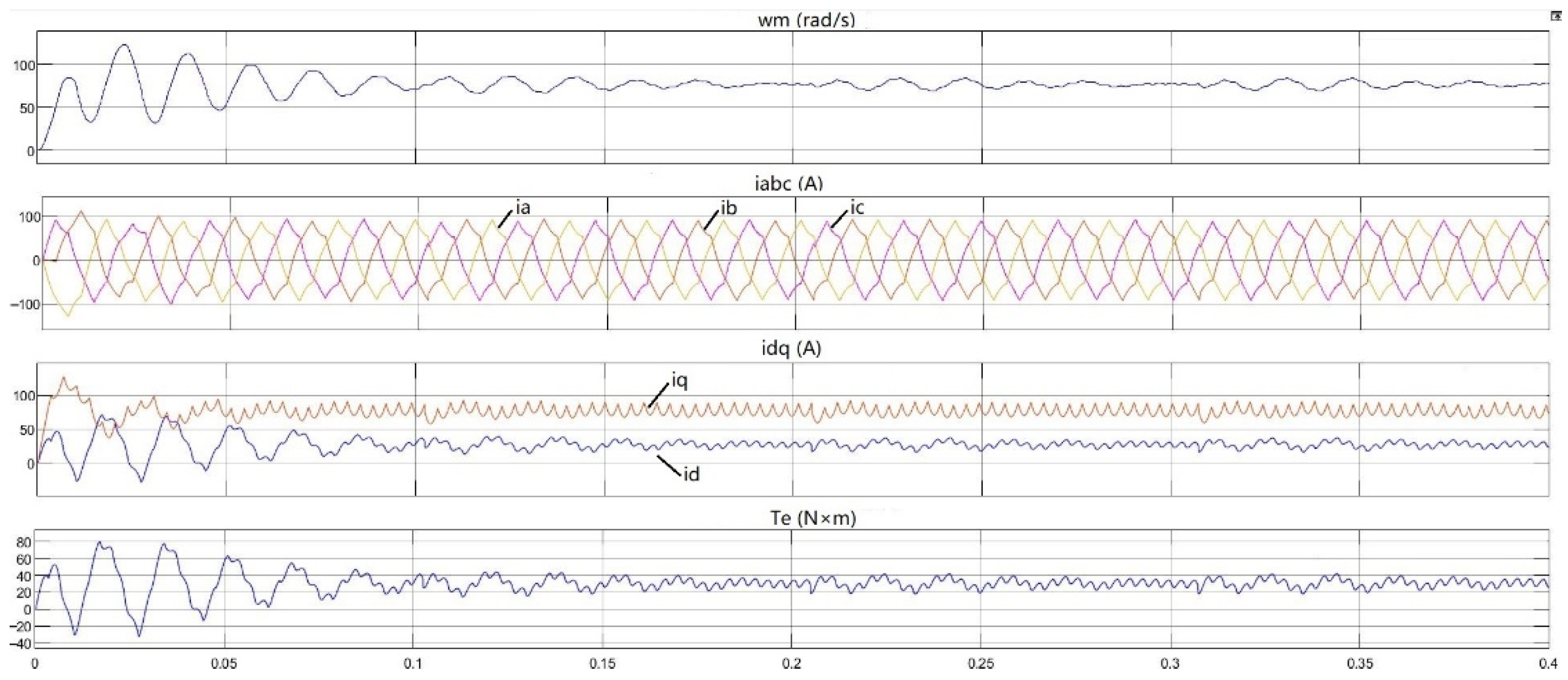

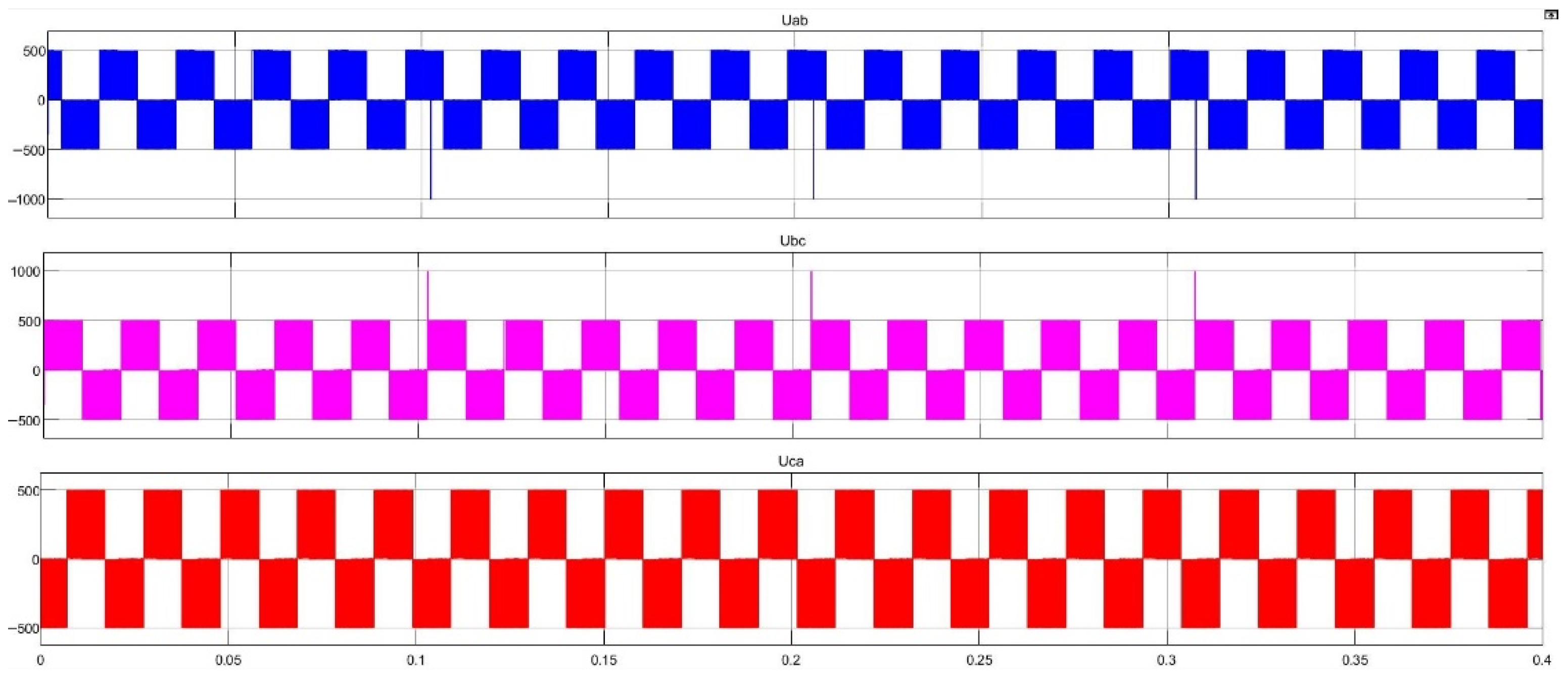

4.2. Waveform of Vector Synthesis Algorithm of 1/2 × Amplitude Substitution

5. Discussion

6. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Franquelo, L.G.; Rodriguez, J.; Leon, J.I.; Kouro, S.; Portillo, R.; Prats, M.A. The age of multilevel converters arrives. IEEE Ind. Electron. Mag. 2008, 2, 28–39. [Google Scholar] [CrossRef]

- Rodriguez, J.; Bernet, S.; Wu, B. Multilevel Voltage-Source-Converter Topologies for Industrial Medium-Voltage Drives. IEEE Trans. Ind. Electron. 2007, 2930–2945. [Google Scholar] [CrossRef]

- Holtz, J.; Oikonomou, N. Neutral Point Potential Balancing Algorithm at Low Modulation Index for Three-Level Inverter Medium-Voltage Drives. IEEE Trans. Ind. Appl. 2007, 43, 761–768. [Google Scholar] [CrossRef]

- Zhang, Y.; Li, Y.W.; Zargari, N.R.; Cheng, Z. Improved selective harmonics elimination (SHE) scheme with online harmonic compensation for high-power PWM converters. In Proceedings of the 2014 IEEE Energy Conversion Congress and Exposition (ECCE), Pittsburgh, PA, USA, 14–18 September 2014; pp. 5510–5517. [Google Scholar] [CrossRef]

- Celanovic, N.; Boroyevich, D. A comprehensive study of neutral-point voltage balancing problem in three-level neutral-point-clamped voltage source PWM inverters. IEEE Trans. Power Electron. 2000, 15, 242–249. [Google Scholar] [CrossRef]

- Gui, S.W.; Wang, L.; Huang, S.H. An Improved VSVPWM Strategy of Considering Neutral-Point Potential Balancing in Three-Level NPC Converter. Appl. Mech. Mater. 2014, 496–500, 1079–1083. [Google Scholar] [CrossRef]

- Xia, C.L.; Xu, Z.; Zhao, J.X. A New Direct Power Control Strategy for NPC Three-Level Voltage Source Rectifiers Using a Novel Vector Influence Table Method. J. Power Electron. 2015, 15, 106–115. [Google Scholar] [CrossRef][Green Version]

- Zhang, M.S.; Cui, Y.; Wang, Q.J. A Study on Neutral-Point Potential in Three-Level NPC Converters. Energies 2019, 12, 3367. [Google Scholar] [CrossRef]

- Seo, J.H.; Choi, C.H.; Hyun, D.-S. A new simplified space-vector PWM method for three-level inverters. IEEE Trans. Power Electron. 2001, 16, 545–550. [Google Scholar] [CrossRef]

- Jiang, W.D.; Wang, Q.J.; Chen, Q.; Shi, X.F. SVPWM Strategy for Three-Level Inverter Based on SVPWM Strategy for Two-Level Inverter. Acta Electrotech. Sin. 2009, 24, 108–114. [Google Scholar] [CrossRef]

- Cao, Y.l.; Zhang, X.d.; Liu, X. Research on Improved D-NPC Three Phase Three Level Converter and Its Control Strategy. Des. Eng. 2020, 11, 815–823. [Google Scholar] [CrossRef]

- Fang, H.; Wu, X.J.; Song, W.S.; Feng, X.Y. Unity Studies Between Three-level SVPWM and CBPWM in the Over-modulation Region. Chin. J. Electr. Eng. 2015, 35, 1994–1996. [Google Scholar] [CrossRef]

- Yuan, D.K.; Xu, Y.D.; Li, X.T. Permanent Magnet Synchronous Motor Variable Frequency Speed Regulation System and Its Control; China Machine Press: Beijing, China, 2018; pp. 189–194. [Google Scholar]

- Gupta, A.K.; Khambadkone, A.M. A Simple Space Vector PWM Scheme to Operate a Three-Level NPC Inverter at High Modulation Index Including Overmodulation Region, With Neutral Point Balancing. IEEE Trans. Ind. Appl. 2007, 43, 751–760. [Google Scholar] [CrossRef]

- Wang, W.; Zhang, B.; Xie, F. A Novel SVPWM for Three-Level NPC Inverter Based on m-Mode Controllability. IEEE Trans. Ind. Electron. 2018, 65, 6055–6065. [Google Scholar] [CrossRef]

- Yao, Y.; Kang, L.Y.; Zhang, Z. A Novel Modulation Method for Three-Level Inverter Neutral Point Potential Oscillation Elimination. J. Power Electron. 2018, 18, 445–455. [Google Scholar] [CrossRef]

| Level States | G11 | G15 | G13 |

|---|---|---|---|

| “+” (H) | 1 | 0 | 0 |

| “0” (Z) | 0 | 1 | 0 |

| “−” (L) | 0 | 0 | 1 |

| First Area | S112 | ||

|---|---|---|---|

| Adjacent vector | (HHH, ZZZ, LLL) | (HZZ, ZLL) | (HHZ, ZZL) |

| Action time | |||

| Space Vector | Switch State | Voltage Vector | |

|---|---|---|---|

| S11 | 0 | ||

| S12 | 0 | ||

| S13 | 0 | ||

| S14 | 0 | ||

| S15 | 0 | ||

| S16 | 0 | ||

| Areas | A | B | C |

|---|---|---|---|

| S11 | |||

| S12 | |||

| S13 | |||

| S14 | |||

| S15 | |||

| S16 |

| Name | DC Voltage | Sampling Frequency | Simulation Time | Modulation Frequency |

|---|---|---|---|---|

| Value | 1000 V | 10 kHz | 0.4 s | 48.8 Hz |

| Name | Stator Resistance | Terminal Inductance | Flux Linkage | Rotational Inertia | Rotational Inertia | Pole Pairs |

|---|---|---|---|---|---|---|

| Value | 0.958 Ω | 0.00525 H | 0.187 Wb | 0.189 | 0.008 | 4 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Cao, Y.; Zhang, X. Research on an Improved Three-Level SVPWM Modulation Algorithm Based on ID-NPC Topology. Electronics 2021, 10, 1129. https://doi.org/10.3390/electronics10091129

Cao Y, Zhang X. Research on an Improved Three-Level SVPWM Modulation Algorithm Based on ID-NPC Topology. Electronics. 2021; 10(9):1129. https://doi.org/10.3390/electronics10091129

Chicago/Turabian StyleCao, Yonglei, and Xiaodong Zhang. 2021. "Research on an Improved Three-Level SVPWM Modulation Algorithm Based on ID-NPC Topology" Electronics 10, no. 9: 1129. https://doi.org/10.3390/electronics10091129

APA StyleCao, Y., & Zhang, X. (2021). Research on an Improved Three-Level SVPWM Modulation Algorithm Based on ID-NPC Topology. Electronics, 10(9), 1129. https://doi.org/10.3390/electronics10091129