Reconfiguration Strategy for Fault Tolerance in a Cascaded Multilevel Inverter Using a Z-Source Converter

Abstract

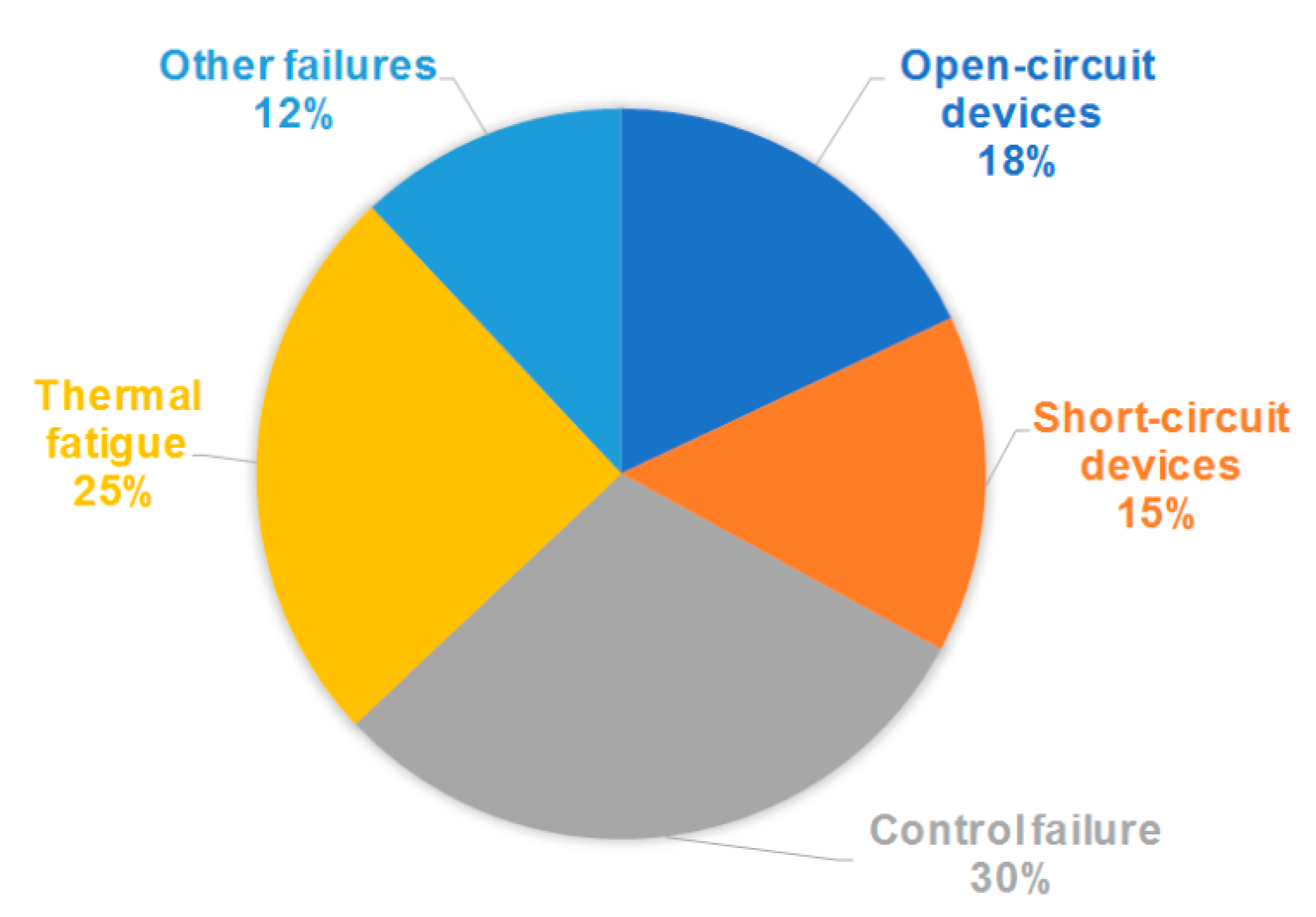

1. Introduction

1.1. Material Redundancy

1.2. Analytical Redundancy

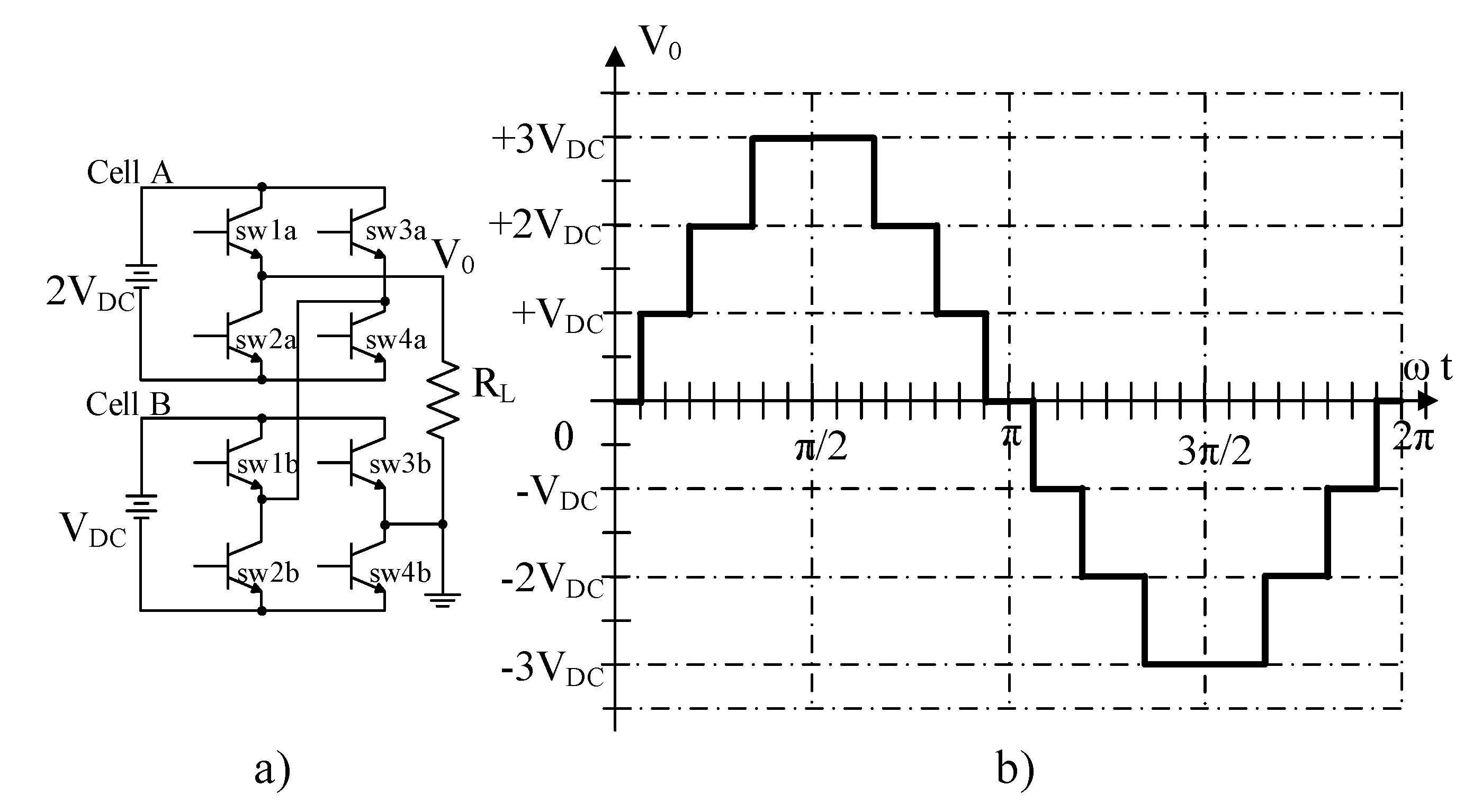

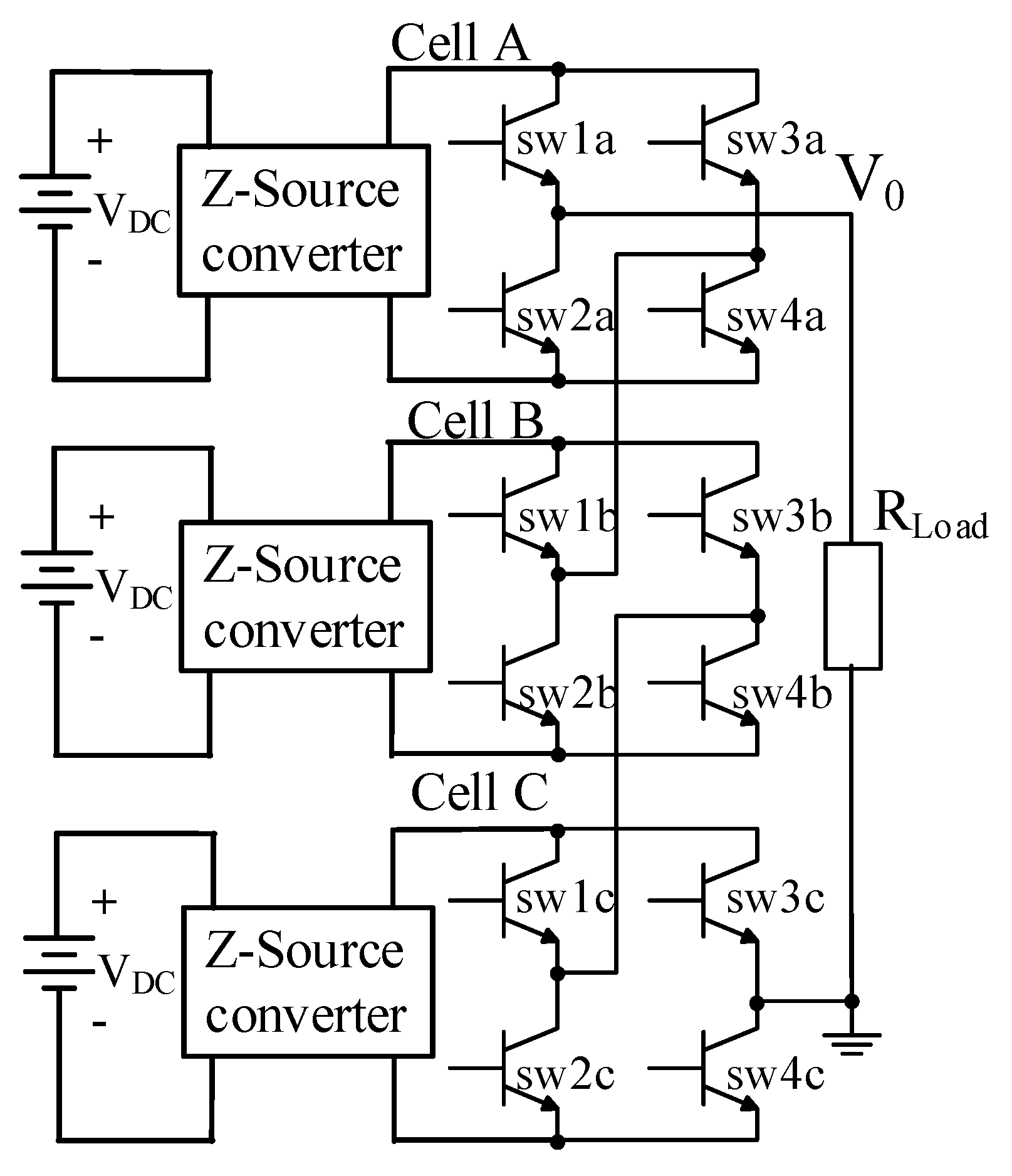

2. Multilevel Inverter

2.1. Symmetrical Cascaded Multilevel Inverter (S-CMLI)

2.2. Asymmetrical Cascaded Multilevel Inverter (A-CMLI)

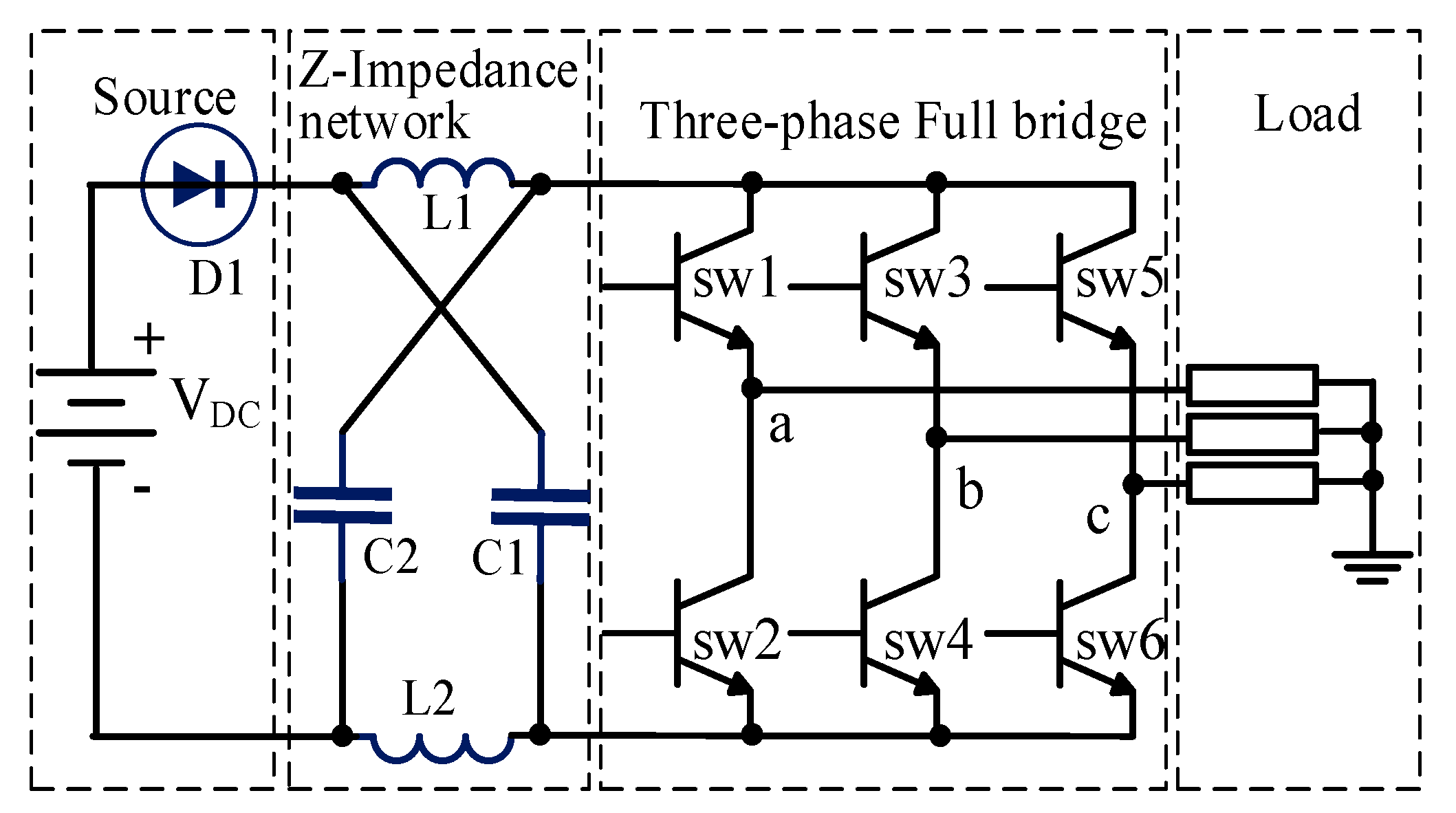

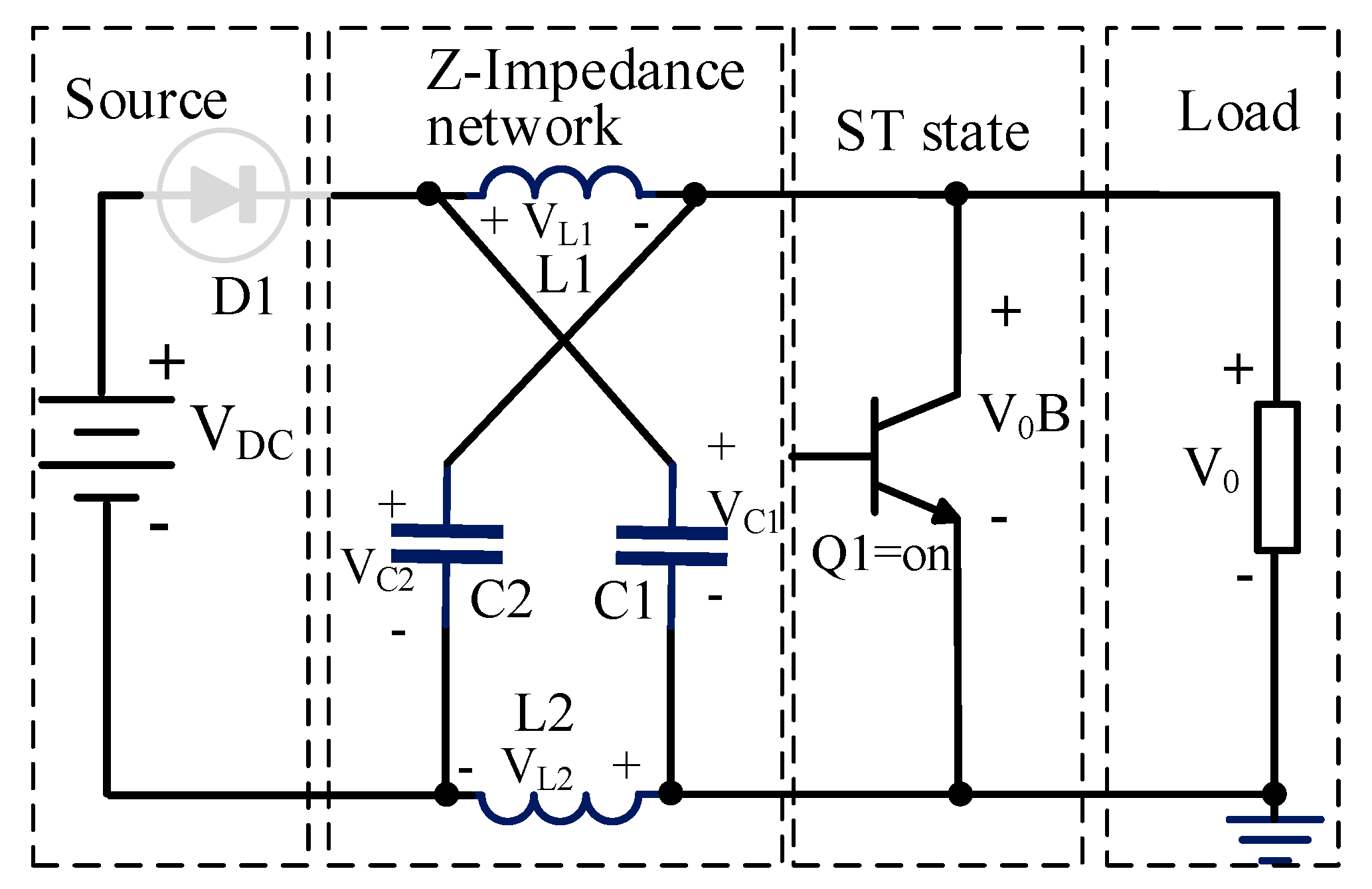

3. Z-source Inverter

3.1. Z-Source Converter

3.2. NST State in Z-Source Converter

3.3. ST State in Z-Source Converter

4. Fault Reconfiguration Technique

5. Experimental Results

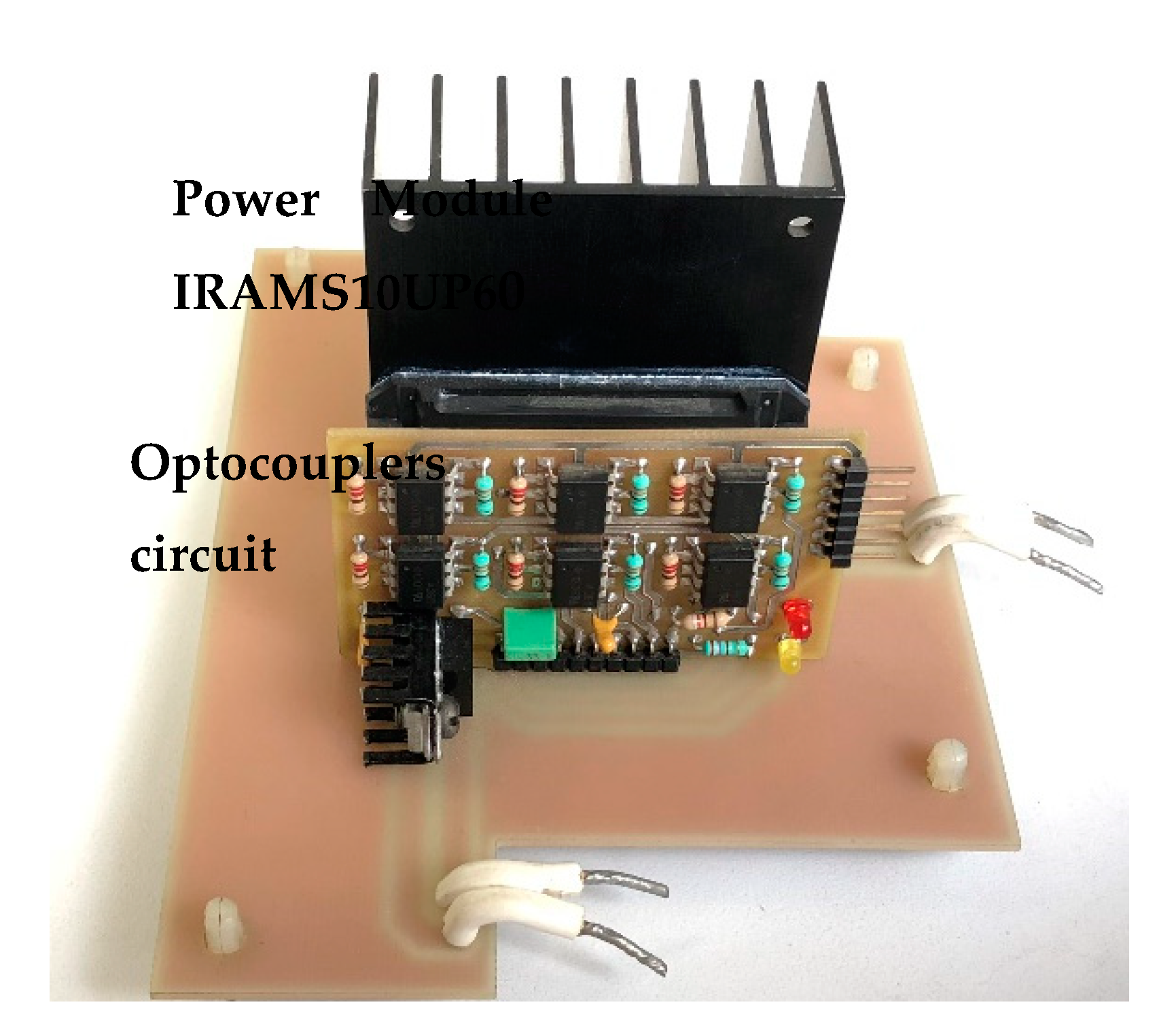

5.1. Experimental Prototype of the Z-Source Converter

- Diode D1: HFA15TB60 (Ultrafast Diode), rated at 15 A, 600 V (International Rectifier, El Segundo, CA, USA)

- MOSFET Q1: IRFP350, rated at 10 A, 400 V (Vishay Siliconix, Santa Clara, CA, USA)

- Inductors L1 and L2: model 1140-102K-RC, 1 mH/5.5 A (Bourns, Jalisco, Mexico)

5.2. Z-source Converter Behavior in Transient Mode

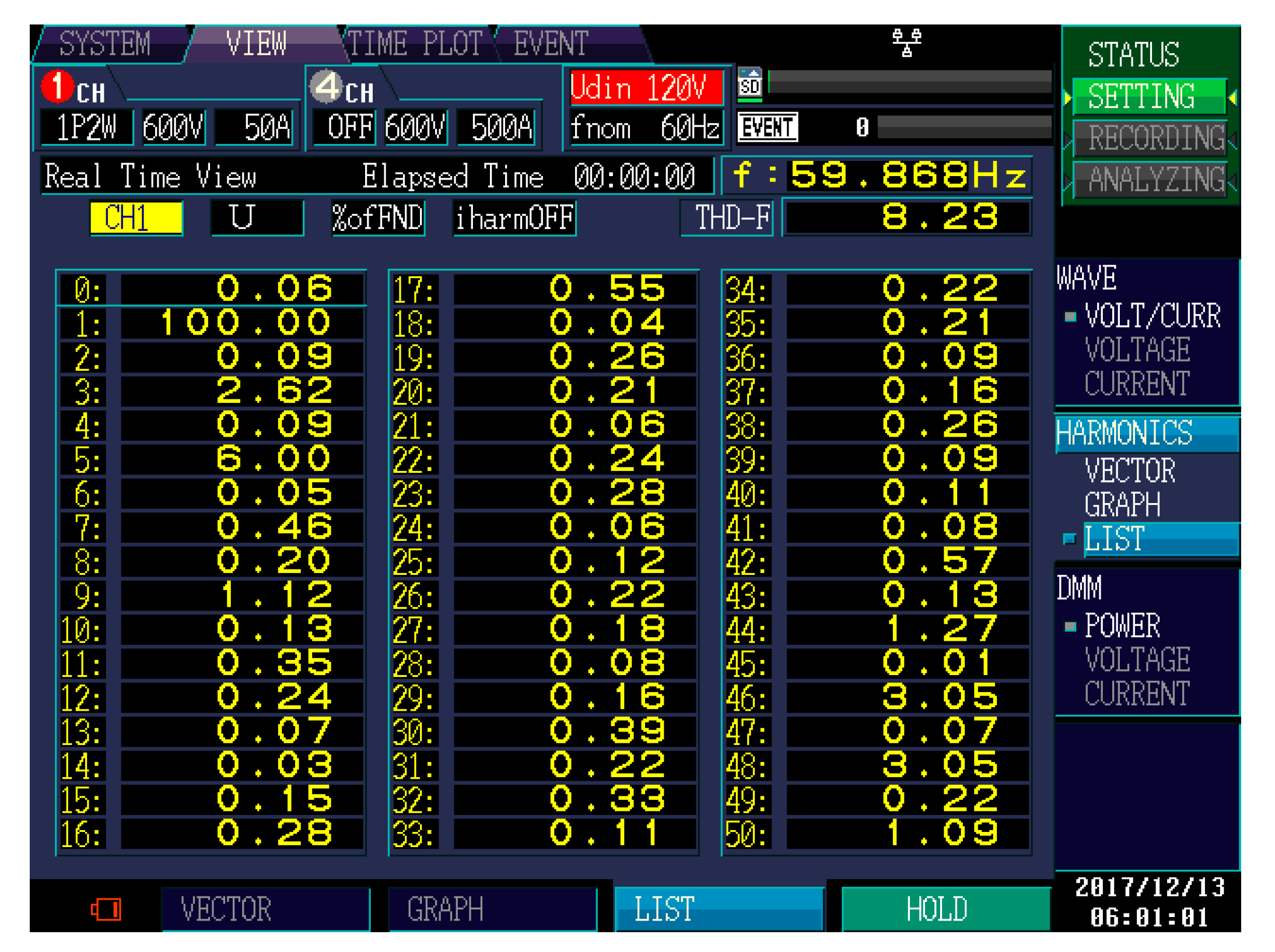

5.3. Multilevel Inverter Behavior in the Fault-Free Condition

- Cells A, B, and C: Experimentally built with power modules IRAMS10UP60 (International Rectifier, El Segundo, CA, USA) (These power modules produce a short circuit in the output terminals when any fault occurs in the semiconductor power switches that compose it [21]), rated at 10 A, 600 V (Integrated gate drivers and bootstrap diodes).

- Optocouplers circuit: A2611 (Fairchild Semiconductor, CA, USA) (The internal shield provides a guaranteed common mode transient immunity specification up to 15,000 V/μs at 1000V).

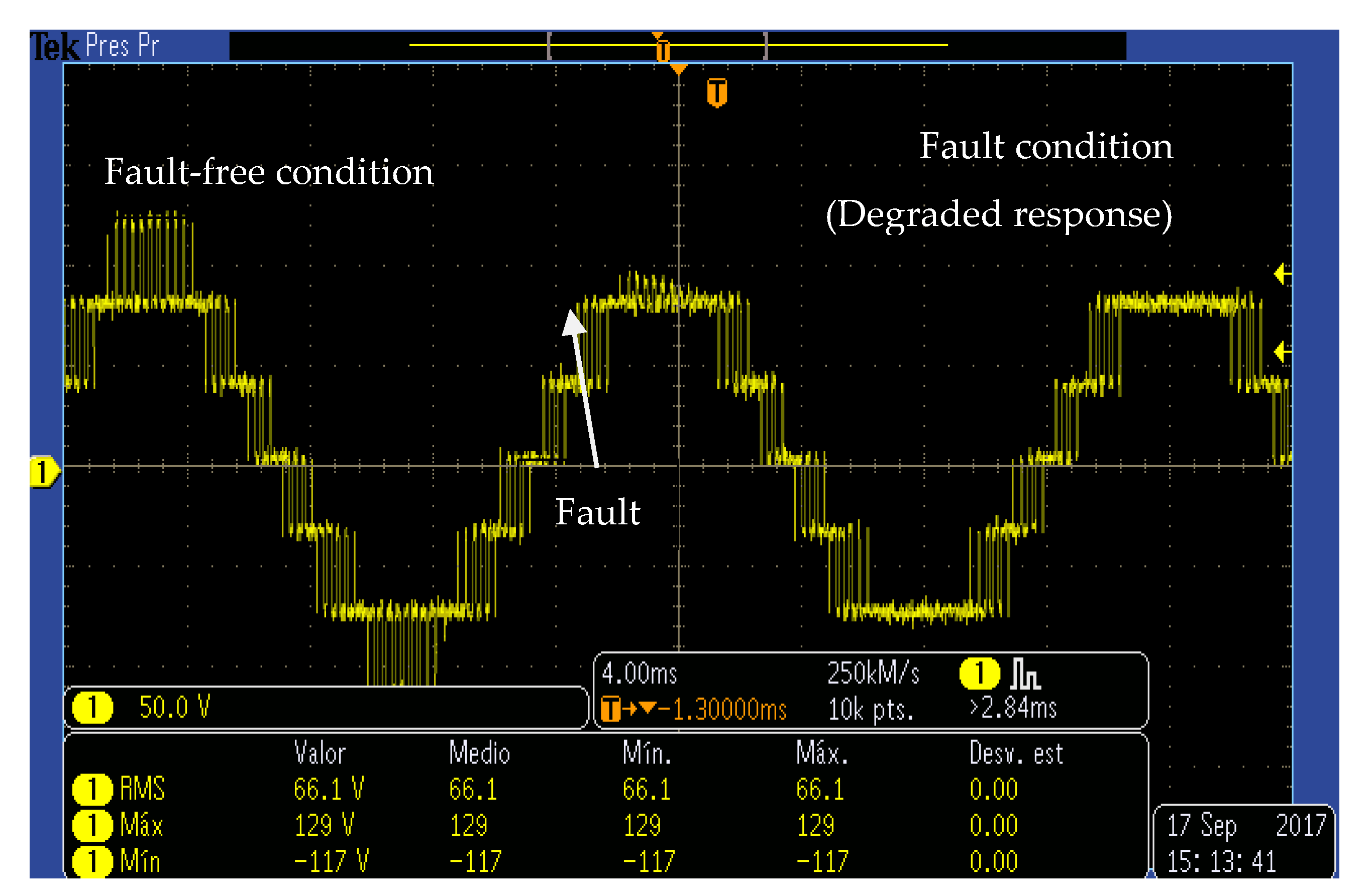

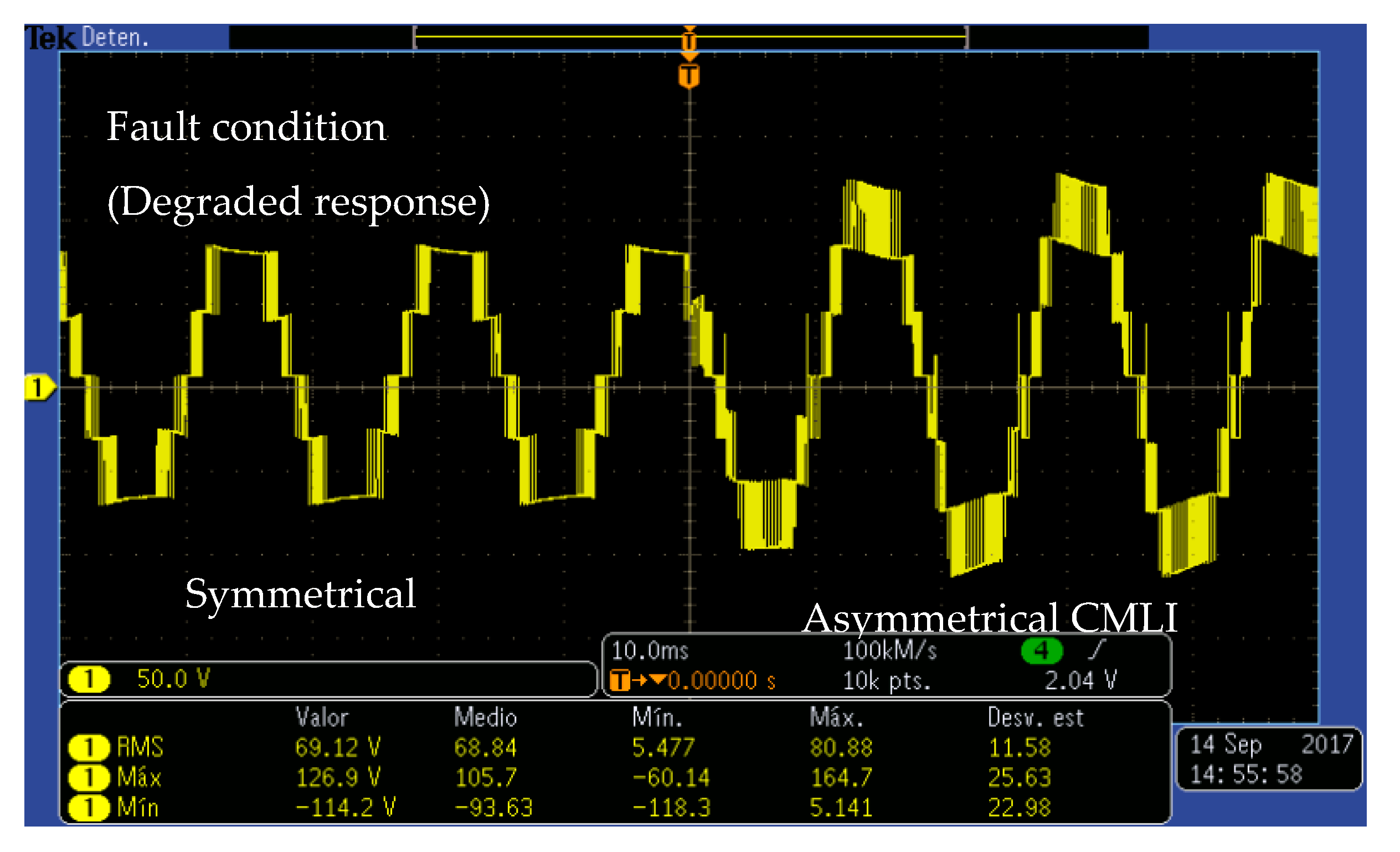

5.4. Multilevel Inverter Behavior from the Fault-Free Condition to the Fault Condition (Degraded Response)

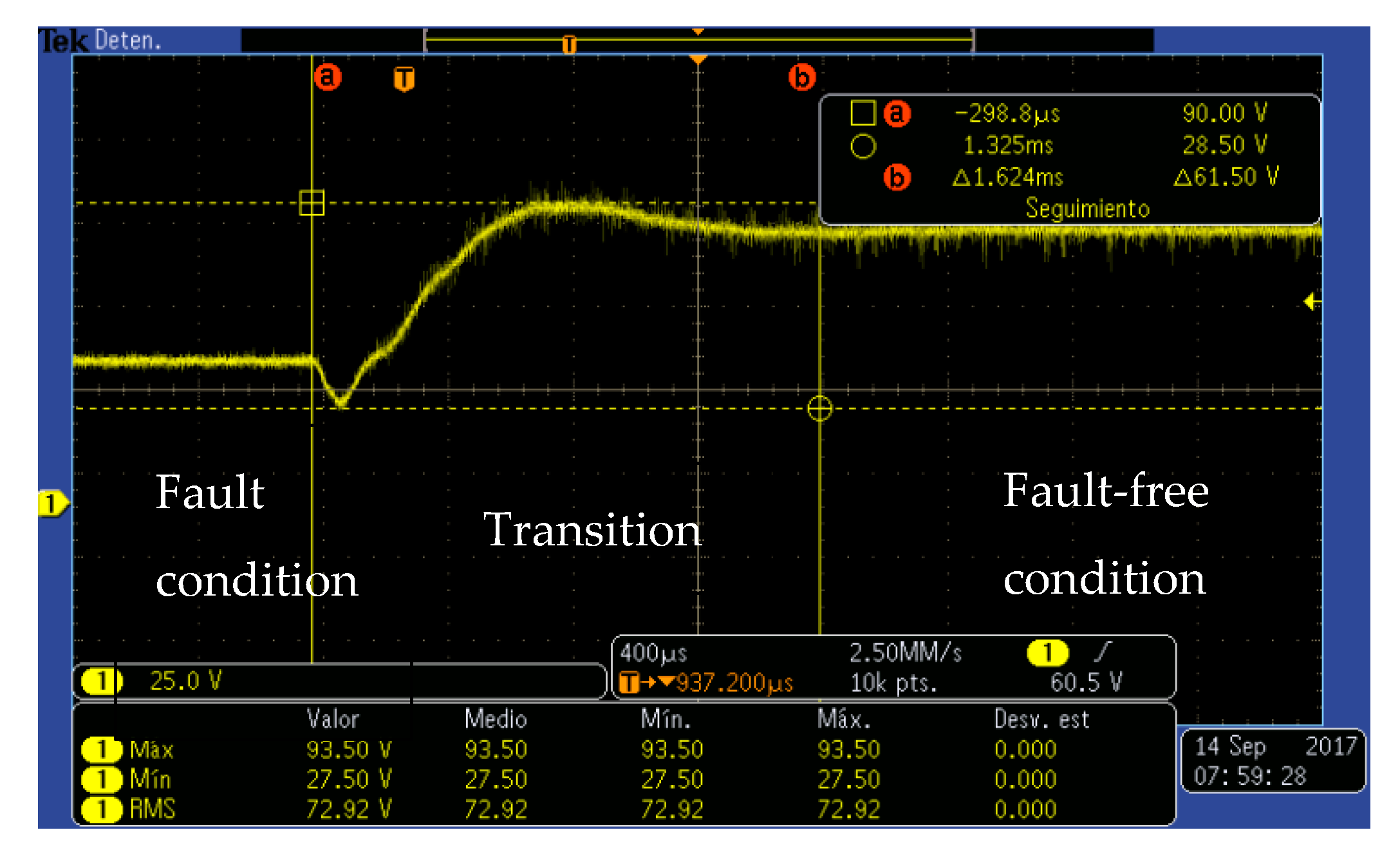

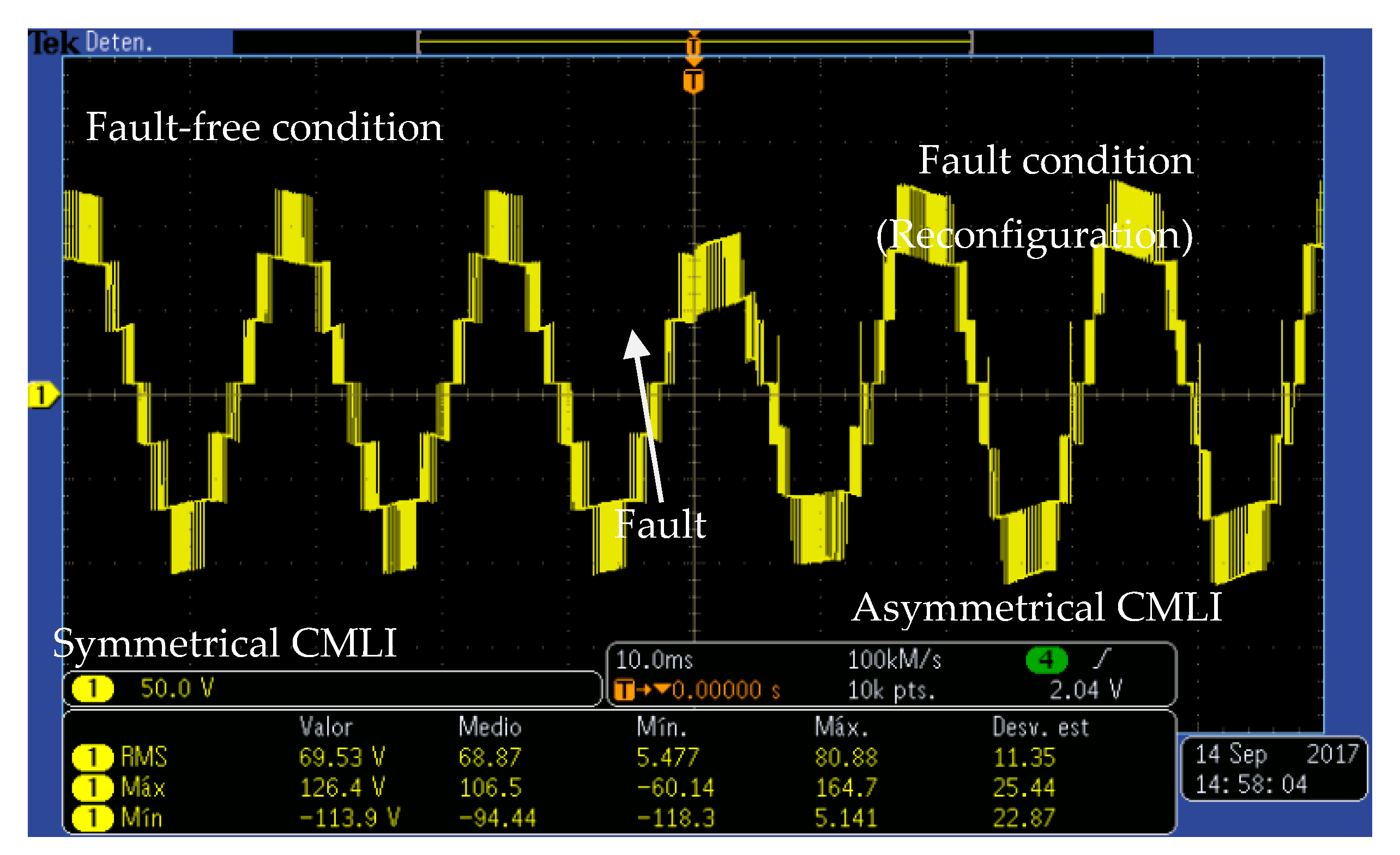

5.5. Multilevel Inverter Behavior during Fault Condition: Degraded Response Change to Reconfiguration

5.6. Multilevel Inverter Behavior from the Fault-Free Condition to the Fault Condition (Reconfiguration)

6. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Aldaco, S.E.D.L.; Calleja, H.; Alquicira, J.A. Reliability and Mission Profiles of Photovoltaic Systems: A FIDES Approach. IEEE Trans. Power Electron. 2015, 30, 2578–2586. [Google Scholar] [CrossRef]

- Aldaco, S.E.D.L.; Calleja, H.; Alquicira, J.A. Metaheuristic Optimization Methods Applied to Power Converters: A Review. IEEE Trans. Power Electron. 2015, 30, 6791–6803. [Google Scholar] [CrossRef]

- Kumar, P.V.; Fernandes, B.G. A Fault-Tolerant Single-Phase Grid-Connected Inverter Topology with Enhanced Reliability for Solar PV Applications. IEEE J. Emerg. Sel. Top Power Electron. 2017, 5, 1254–1262. [Google Scholar] [CrossRef]

- Rodríguez-Blanco, M.; Vzquez-Prez, A.; Hernndez-Gonzlez, L.; Golikov, V.; Aguayo-Alquicira, J.; May-Alarcn, M. Fault Detection for IGBT Using Adaptive Thresholds During the Turn-on Transient. IEEE Trans. Ind. Electron. 2015, 62, 1975–1983. [Google Scholar] [CrossRef]

- JALHOTRA, M.; Kumar, L.; GAUTAM, S.; Gupta, S. Development of fault tolerant multilevel inverter topology. IET Power Electron. 2018, 11, 1416–1424. [Google Scholar] [CrossRef]

- Kumar, M.S.; Borghate, V.B.; Karasani, R.R.; Sabyasachi, S.; Suryawanshi, H.M. A fault-tolerant modular multilevel inverter topology. Int. J. Circuit Theory Appl. 2018, 46, 1028–1043. [Google Scholar] [CrossRef]

- Chatzakis, J.; Antonidakis, E. A novel N+k fault-tolerant hot-swap DC/AC inverter design. In Proceedings of the 2008 IEEE Power Electronics Specialists Conference, Rhodes, Greece, 15–19 June 2008; pp. 3291–3294. [Google Scholar]

- Rodriguez-Blanco, M.A.; Claudio-Sanchez, A.; Theilliol, D.; Vela-Valdes, L.G.; Sibaja-Teran, P.; Hernandez-Gonzalez, L.; Aguayo-Alquicira, J. A Failure-Detection Strategy for IGBT Based on Gate-Voltage Behavior Applied to a Motor Drive System. IEEE Trans. Ind. Electron. 2011, 58, 1625–1633. [Google Scholar] [CrossRef]

- Kwak, Y.-G.; Heo, D.-H.; Kim, S.-P.; Song, S.-G.; Park, S.-J.; Kang, F.-S. Reliability and Economic Efficiency Analysis of 4-Leg Inverter Compared with 3-Leg Inverters. Electronics 2021, 10, 87. [Google Scholar] [CrossRef]

- Dixon, J.; Barriuso, P.; Ortuzar, M.; Moran, L.; Pontt, J.; Rodriguez, J. Fault Tolerant Reconfiguration System for Asymmetric Multilevel Converters Using Bi-Directional Power Switches. In Proceedings of the IECON 2007-33rd Annual Conference of the IEEE Industrial Electronics Society, Taipei, Taiwan, 5–8 November 2007; pp. 2124–2129. [Google Scholar]

- Abbasi, S.; Ghadimi, A.A.; Abolmasoumi, A.H.; Miveh, M.R.; Jurado, F. Enhanced Control Scheme for a Three-Phase Grid-Connected PV Inverter under Unbalanced Fault Conditions. Electronics 2020, 9, 1247. [Google Scholar] [CrossRef]

- Ma, M.; Hu, L.; Chen, A.; He, X. Reconfiguration of Carrier-Based Modulation Strategy for Fault Tolerant Multilevel Inverters. IEEE Trans. Power Electr. 2007, 22, 2050–2060. [Google Scholar] [CrossRef]

- Kim, S.-M.; Lee, J.-S.; Lee, K.-B. A Novel Modulation Strategy Based on Level-Shifted PWM for Fault Tolerant Control of Cascaded Multilevel Inverters. Trans. Korean Inst. Electr. Eng. 2015, 64, 718–725. [Google Scholar] [CrossRef][Green Version]

- Turpin, C.; Baudesson, P.; Richardeau, F.; Forest, F.; Meynard, T. Fault management of multicell converters. IEEE Trans. Ind. Electron. 2002, 49, 988–997. [Google Scholar] [CrossRef]

- Vargas, R.A.; Figueroa, A.; Aldaco, S.E.D.L.-; Aguayo, J.; Hernández, L.; Rodriguez, M.A. Analysis of Minimum Modulation for the 9-Level Multilevel Inverter in Asymmetric Structure. IEEE Lat. Am. Trans. 2015, 13, 2851–2858. [Google Scholar] [CrossRef]

- Malinowski, M.; Gopakumar, K.; Rodriguez, J.; Perez, M.A. A Survey on Cascaded Multilevel Inverters. IEEE Trans. Ind. Electron. 2009, 57, 2197–2206. [Google Scholar] [CrossRef]

- Ye, M.; Ren, W.; Wei, Q.; Song, G.; Miao, Z. Research on Modified Hybrid Frequency Modulation Technology of Type-III Asymmetric CHB Multilevel Inverters. Electronics 2020, 9, 263. [Google Scholar] [CrossRef]

- Peng, F.Z. Z-source inverter. IEEE Trans. Ind. Appl. 2003, 39, 504–510. [Google Scholar] [CrossRef]

- Grgić, I.; Vukadinović, D.; Bašić, M.; Bubalo, M. Calculation of Semiconductor Power Losses of a Three-Phase Quasi-Z-Source Inverter. Electronics 2020, 9, 1642. [Google Scholar] [CrossRef]

- Chitra, K.; Jeevanandham, A. Design and implementation of maximum constant boost switched inductor z-source inverter for three-phase on-line uninterrupted power supply. COMPEL Int. J. Comput. Math. Electr. Electron. Eng. 2015, 34, 1101–1121. [Google Scholar] [CrossRef]

- Datasheet IRAMS10UP60. Available online: https://www.alldatasheet.com/view_datasheet.jsp?Searchword=IRAMS10UP60 (accessed on 1 February 2021).

| Condition | Cell A | Cell B | Cell C |

|---|---|---|---|

| Fault-free | CMLI in symmetric mode. Z-Source in fault-free condition. | CMLI in symmetric mode. Z-Source in fault-free condition. | CMLI in symmetric mode. Z-Source in fault-free condition. |

| Fault in Cell A | CMLI in short-circuit mode. Z-Source in OFF mode. | CMLI in asymmetric mode. Z-Source in fault-free condition. | CMLI in asymmetric mode. Z-Source in fault mode. |

| Fault in Cell B | CMLI in asymmetric mode. Z-Source in fault mode. | CMLI in short-circuit mode. Z-Source in OFF mode. | CMLI in asymmetric mode. Z-Source in fault-free condition. |

| Fault in Cell C | CMLI in asymmetric mode. Z-Source in fault-free condition. | CMLI in asymmetric mode. Z-Source in fault mode. | CMLI in short-circuit mode. Z-Source in OFF mode. |

| Figure Parameter | Value | |

|---|---|---|

| VDC | ||

| C1 & C2 | ||

| L1 & L2 | ||

| RLOAD | ||

| LX | ||

| CX | ||

| fs | ||

| Variable Parameter | Fault-Free Condition (Nominal) | Fault Condition |

| V0 | ||

| P0 | ||

| D | ||

| ΔiL | ||

| ΔVC | 0.15 V | |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Aguayo-Alquicira, J.; Vásquez-Libreros, I.; De Léon-Aldaco, S.E.; Ponce-Silva, M.; Lozoya-Ponce, R.E.; Flores-Rodríguez, E.; García-Morales, J.; Reyes-Severiano, Y.; Carrillo-Santos, L.M.; Marín-Reyes, M.; et al. Reconfiguration Strategy for Fault Tolerance in a Cascaded Multilevel Inverter Using a Z-Source Converter. Electronics 2021, 10, 574. https://doi.org/10.3390/electronics10050574

Aguayo-Alquicira J, Vásquez-Libreros I, De Léon-Aldaco SE, Ponce-Silva M, Lozoya-Ponce RE, Flores-Rodríguez E, García-Morales J, Reyes-Severiano Y, Carrillo-Santos LM, Marín-Reyes M, et al. Reconfiguration Strategy for Fault Tolerance in a Cascaded Multilevel Inverter Using a Z-Source Converter. Electronics. 2021; 10(5):574. https://doi.org/10.3390/electronics10050574

Chicago/Turabian StyleAguayo-Alquicira, Jesus, Iván Vásquez-Libreros, Susana Estefany De Léon-Aldaco, Mario Ponce-Silva, Ricardo Eliu Lozoya-Ponce, Eligio Flores-Rodríguez, Jarniel García-Morales, Yesenia Reyes-Severiano, Luis Mauricio Carrillo-Santos, Manuel Marín-Reyes, and et al. 2021. "Reconfiguration Strategy for Fault Tolerance in a Cascaded Multilevel Inverter Using a Z-Source Converter" Electronics 10, no. 5: 574. https://doi.org/10.3390/electronics10050574

APA StyleAguayo-Alquicira, J., Vásquez-Libreros, I., De Léon-Aldaco, S. E., Ponce-Silva, M., Lozoya-Ponce, R. E., Flores-Rodríguez, E., García-Morales, J., Reyes-Severiano, Y., Carrillo-Santos, L. M., Marín-Reyes, M., & Amores-Campos, E. M. (2021). Reconfiguration Strategy for Fault Tolerance in a Cascaded Multilevel Inverter Using a Z-Source Converter. Electronics, 10(5), 574. https://doi.org/10.3390/electronics10050574