A Dynamic Current Pulsing Technique to Improve the Noise Efficiency Factor of Neural Recording Amplifiers

Abstract

1. Introduction

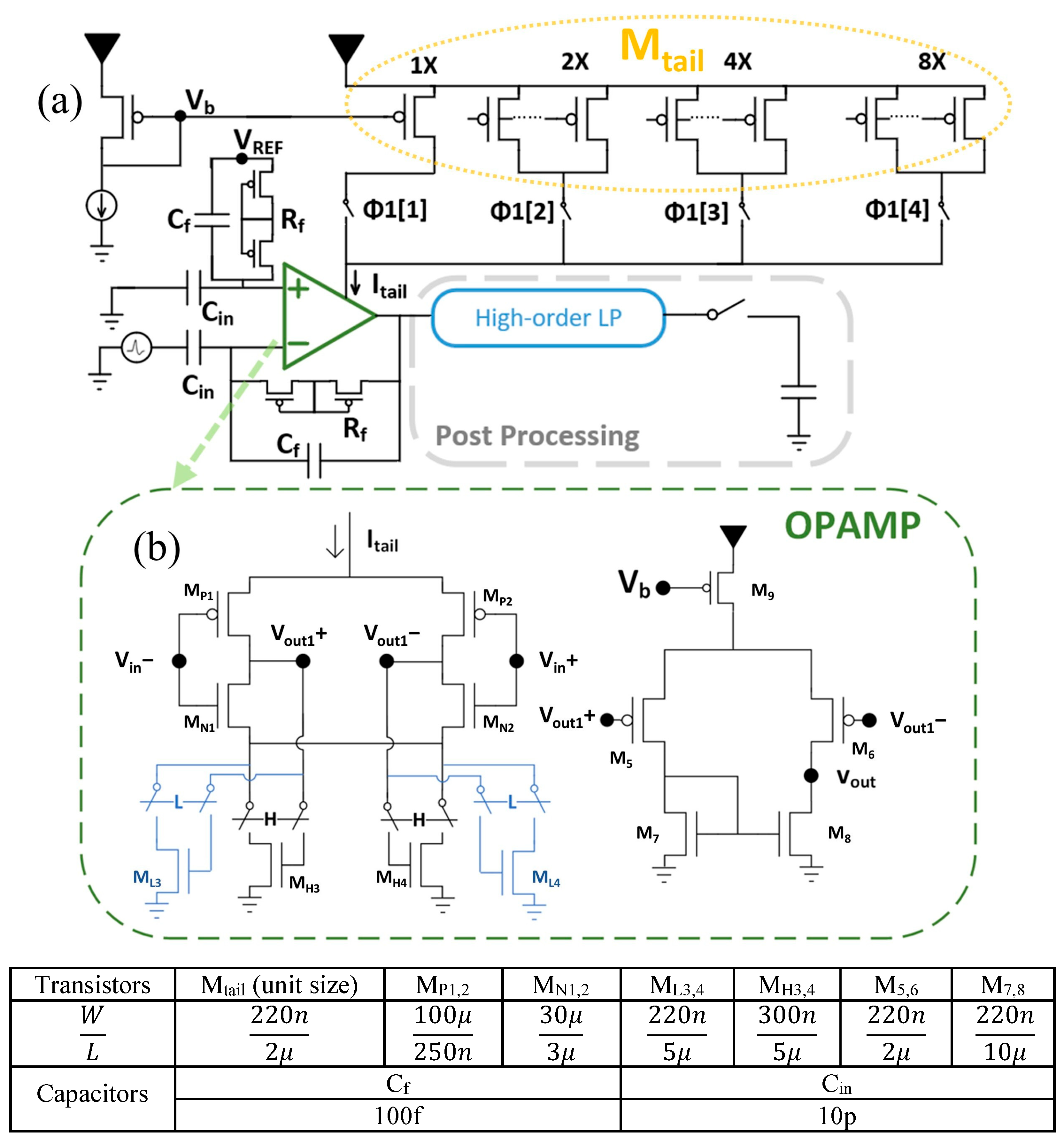

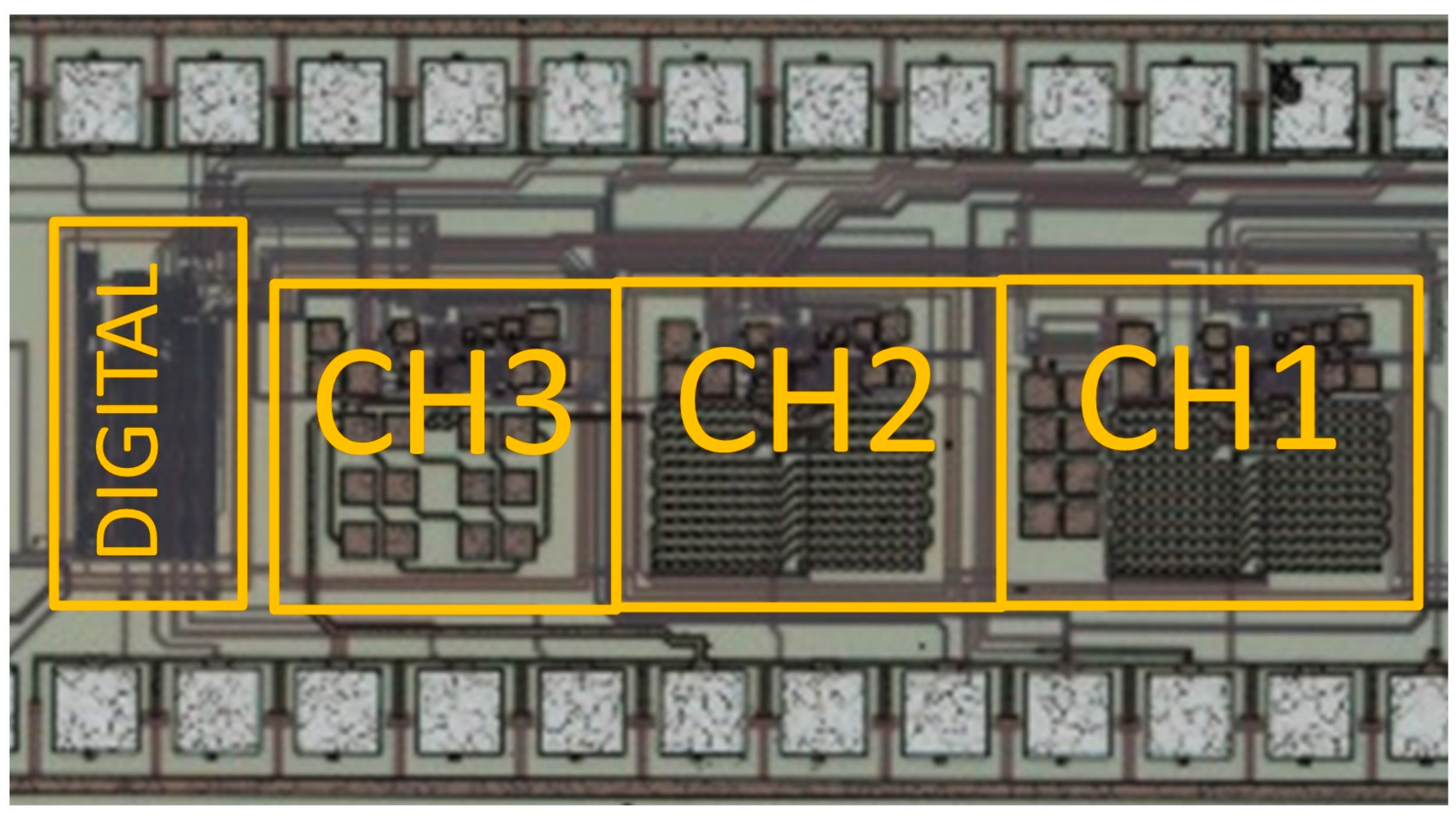

2. Circuit Design

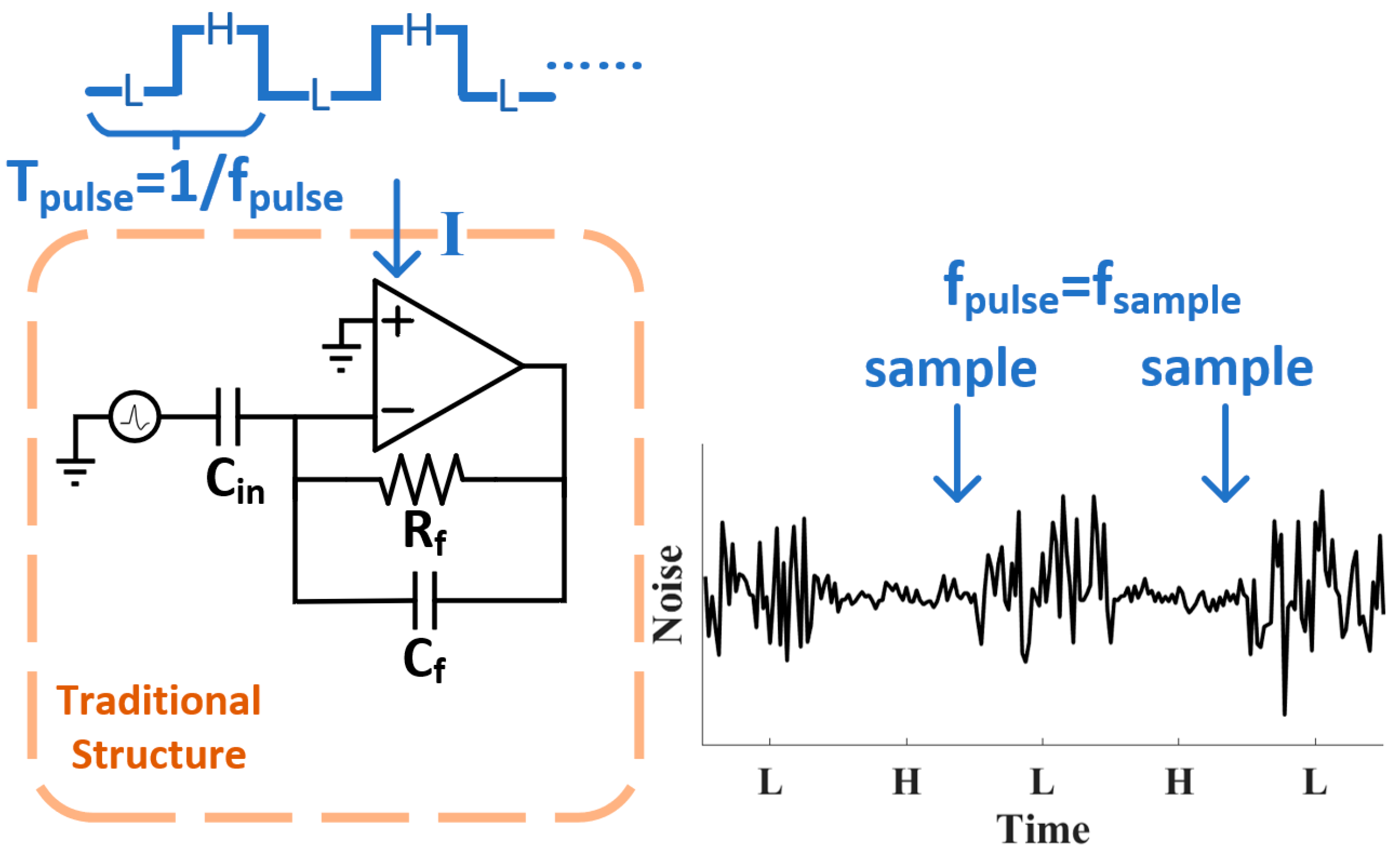

2.1. Current Pulsing Technique

2.2. Settling Time and Noise Folding

3. ASIC Measurement

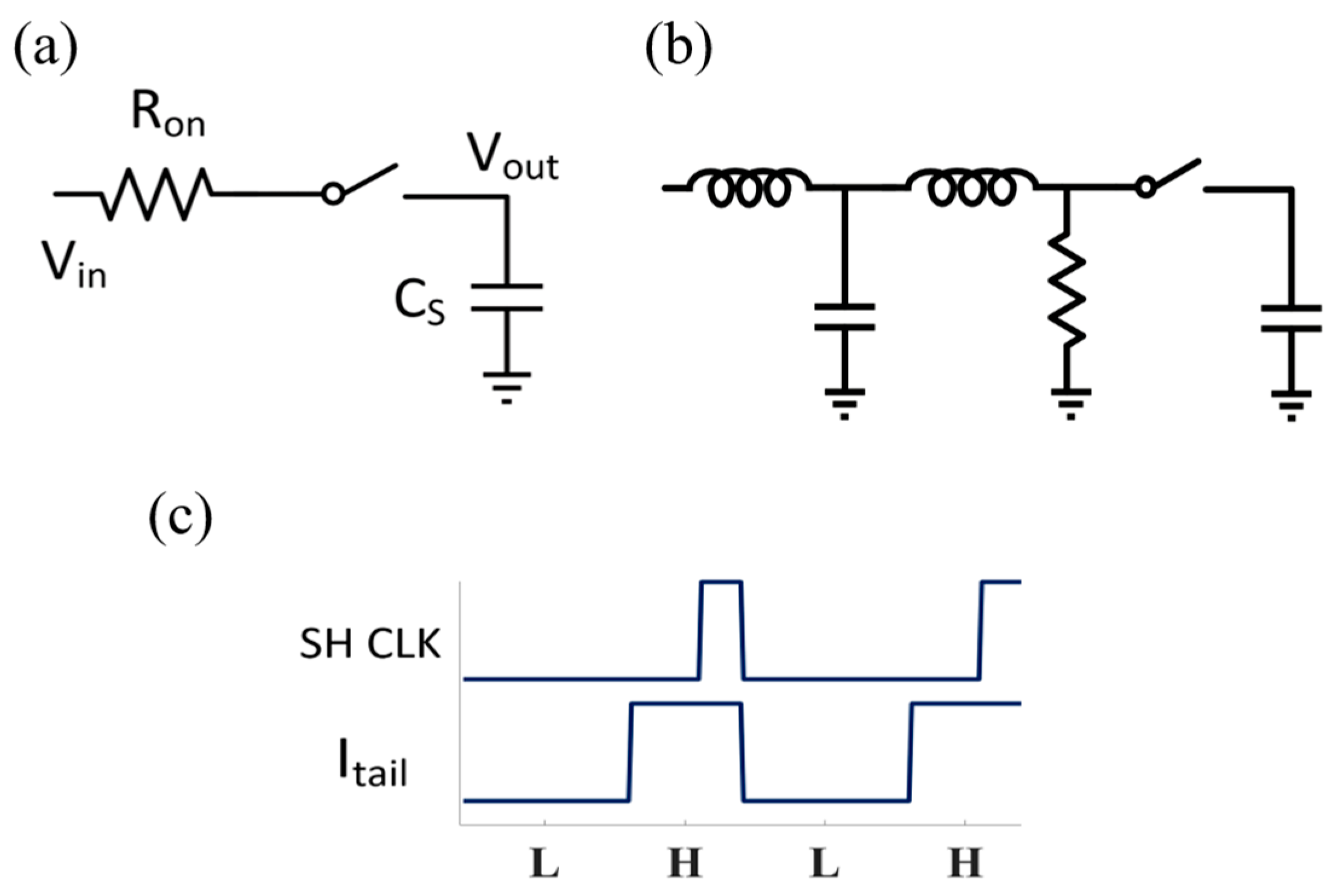

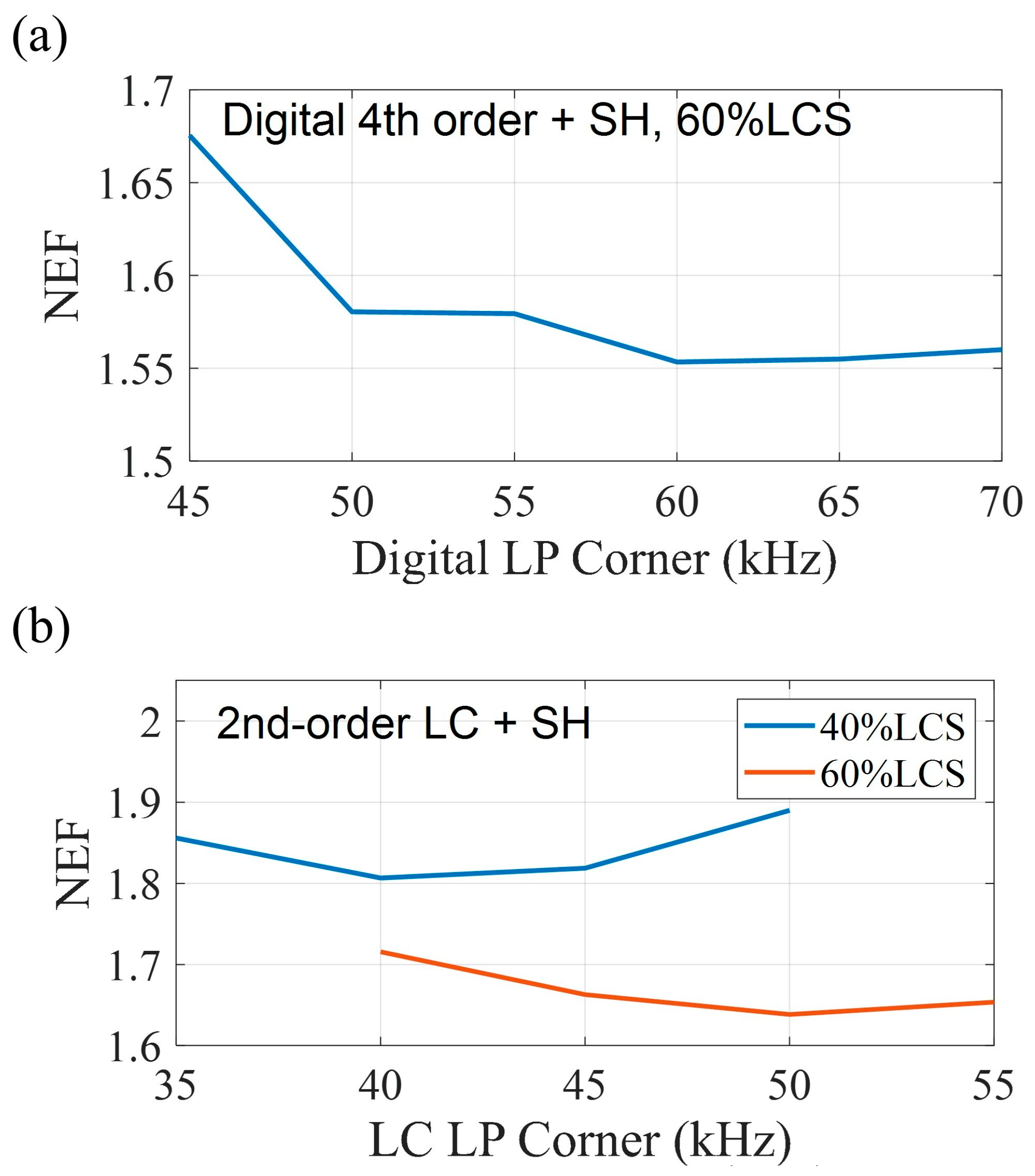

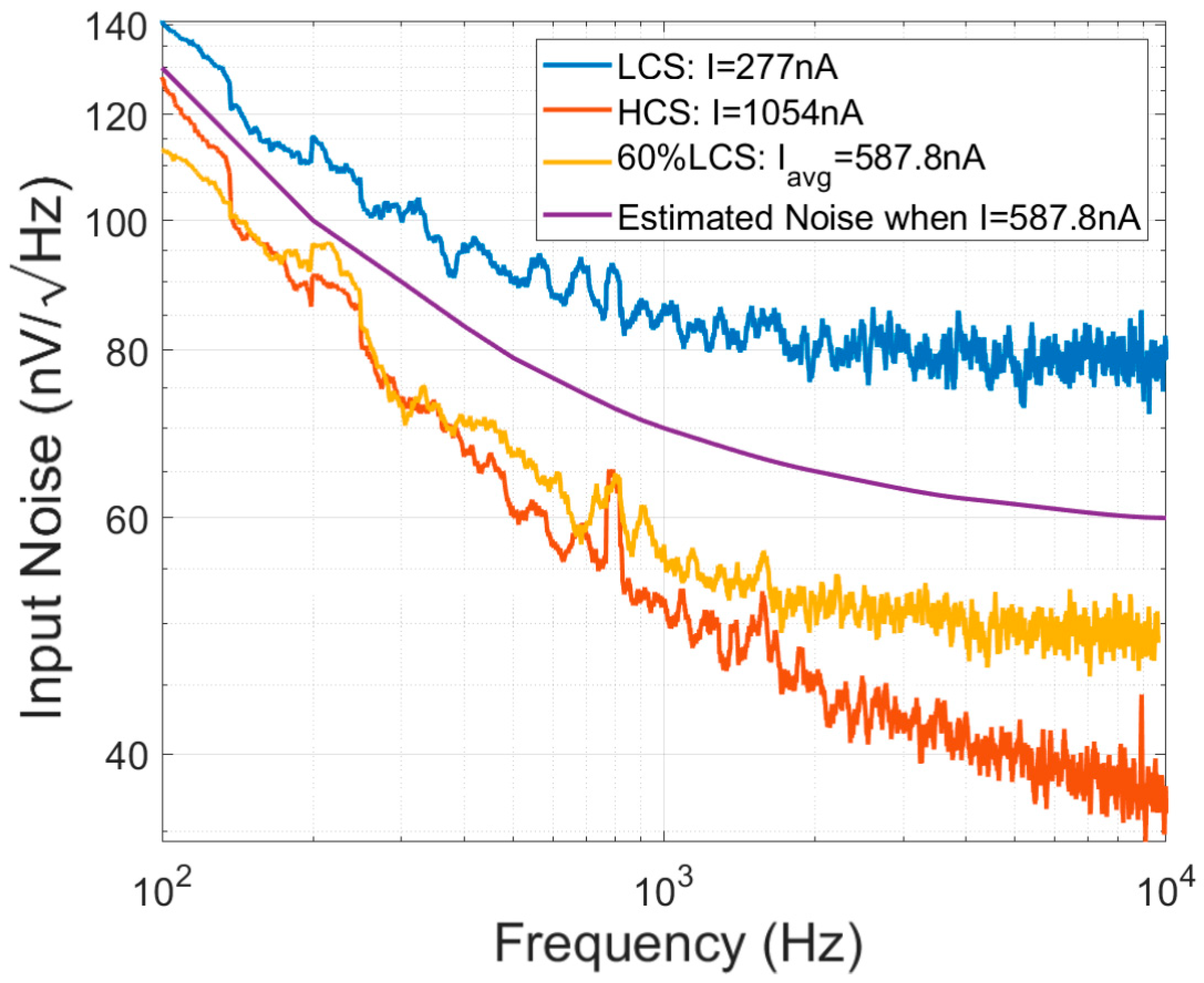

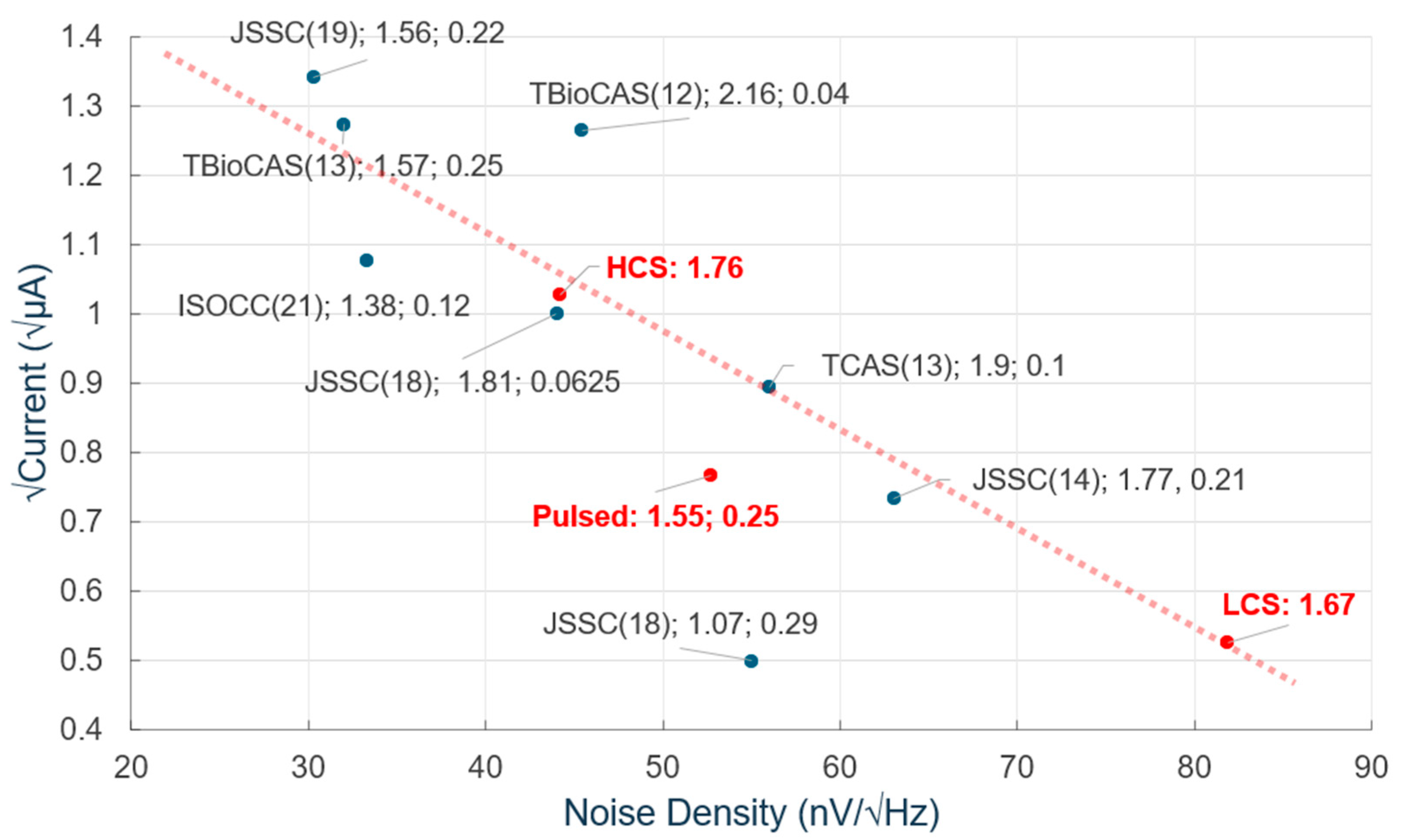

4. Post Processing

4.1. Sample-and-Hold Filter

4.2. Noise Performance

5. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Dey, N.; Ashour, A.S.; Mohamed, W.S.; Nguyen, N.G. Biomedical Signals. In Acoustic Sensors for Biomedical Applications; Springer International Publishing: Cham, Switzerland, 2019; pp. 7–20. [Google Scholar]

- Qian, C.; Parramon, J.; Sanchez-Sinencio, E. A Micropower Low-Noise Neural Recording Front-End Circuit for Epileptic Seizure Detection. IEEE J. Solid-State Circuits 2011, 46, 1392–1405. [Google Scholar] [CrossRef]

- Thakor, N.V. Translating the Brain-Machine Interface. Sci. Transl. Med. 2013, 5, 210ps17. [Google Scholar] [CrossRef]

- Das, R.; Moradi, F.; Heidari, H. Biointegrated and Wirelessly Powered Implantable Brain Devices: A Review. IEEE Trans. Biomed. Circuits Syst. 2020, 14, 343–358. [Google Scholar] [CrossRef] [PubMed]

- Chen, K.-H.S.; Chen, R. Principles of Electrophysiological Assessments for Movement Disorders. J. Mov. Disord. 2020, 13, 27–38. [Google Scholar] [CrossRef] [PubMed]

- Dvey-Aharon, Z.; Fogelson, N.; Peled, A.; Intrator, N. Schizophrenia detection and classification by advanced analysis of EEG recordings using a single electrode approach. PLoS ONE 2015, 10, e0123033. [Google Scholar] [CrossRef]

- Ieracitano, C.; Mammone, N.; Hussain, A.; Morabito, F.C. A Convolutional Neural Network based self-learning approach for classifying neurodegenerative states from EEG signals in dementia. In Proceedings of the 2020 International Joint Conference on Neural Networks (IJCNN), Glasgow, UK, 19–24 July 2020; pp. 1–8. [Google Scholar]

- Curot, J.; Busigny, T.; Valton, L.; Denuelle, M.; Vignal, J.-P.; Maillard, L.; Chauvel, P.; Pariente, J.; Trebuchon, A.; Bartolomei, F.; et al. Memory scrutinized through electrical brain stimulation: A review of 80 years of experiential phenomena. Neurosci. Biobehav. Rev. 2017, 78, 161–177. [Google Scholar] [CrossRef]

- Bârzan, H.; Ichim, A.-M.; Mureşan, R.C. Machine Learning-Assisted Detection of Action Potentials in Extracellular Multi-Unit Recordings. In Proceedings of the 2020 IEEE International Conference on Automation, Quality and Testing, Robotics (AQTR), Cluj-Napoca, Romania, 21–23 May 2020; pp. 1–5. [Google Scholar]

- Xu, H.; Han, Y.; Han, X.; Xu, J.; Lin, S.; Cheung, R.C.C. Unsupervised and real-time spike sorting chip for neural signal processing in hippocampal prosthesis. J. Neurosci. Methods 2019, 311, 111–121. [Google Scholar] [CrossRef]

- Chen, Y.; Yang, X.; Gielen, G.; Mora Lopez, C. Optimizing Neural Recording Front-Ends Toward Enhanced Spike Sorting Accuracy in High-Channel-Count Systems. IEEE Trans. Neural Syst. Rehabil. Eng. 2025, 33, 2180–2191. [Google Scholar] [CrossRef]

- Saeed, M.; Khan, A.A.; Kamboh, A.M. Comparison of Classifier Architectures for Online Neural Spike Sorting. IEEE Trans. Neural Syst. Rehabil. Eng. 2017, 25, 334–344. [Google Scholar] [CrossRef]

- Hao, H.; Chen, J.; Richardson, A.; Van der Spiegel, J.; Aflatouni, F. A 10.8 µW Neural Signal Recorder and Processor With Unsupervised Analog Classifier for Spike Sorting. IEEE Trans. Biomed. Circuits Syst. 2021, 15, 351–364. [Google Scholar] [CrossRef]

- Marblestone, A.H.; Zamft, B.M.; Maguire, Y.G.; Shapiro, M.G.; Cybulski, T.R.; Glaser, J.I.; Amodei, D.; Benjamin Stranges, P.; Kalhor, R.; Dalrymple, D.A.; et al. Physical principles for scalable neural recording. Front. Comput. Neurosci. 2013, 7, 137. [Google Scholar] [CrossRef] [PubMed]

- Olsson, R.H.; Buhl, D.L.; Sirota, A.M.; Buzsaki, G.; Wise, K.D. Band-tunable and multiplexed integrated circuits for simultaneous recording and stimulation with microelectrode arrays. IEEE Trans. Biomed. Eng. 2005, 52, 1303–1311. [Google Scholar] [CrossRef] [PubMed]

- Zou, X.; Liu, L.; Cheong, J.H.; Yao, L.; Li, P.; Cheng, M.-Y.; Goh, W.L.; Rajkumar, R.; Dawe, G.S.; Cheng, K.-W.; et al. A 100-Channel 1-mW Implantable Neural Recording IC. IEEE Trans. Circuits Syst. I Regul. Pap. 2013, 60, 2584–2596. [Google Scholar] [CrossRef]

- Han, D.; Zheng, Y.; Rajkumar, R.; Dawe, G.S.; Je, M. A 0.45 V 100-Channel Neural-Recording IC With Sub-μW/Channel Consumption in 0.18 μm CMOS. IEEE Trans. Biomed. Circuits Syst. 2013, 7, 735–746. [Google Scholar] [CrossRef]

- Steyaert, M.S.J.; Sansen, W.M.C. A micropower low-noise monolithic instrumentation amplifier for medical purposes. IEEE J. Solid-State Circuits 1987, 22, 1163–1168. [Google Scholar] [CrossRef]

- Luo, D.; Zhang, M.; Wang, Z. A Low-Noise Chopper Amplifier Designed for Multi-Channel Neural Signal Acquisition. IEEE J. Solid-State Circuits 2019, 54, 2255–2265. [Google Scholar] [CrossRef]

- Shen, L.; Lu, N.; Sun, N. A 1-V 0.25-μW Inverter Stacking Amplifier With 1.07 Noise Efficiency Factor. IEEE J. Solid-State Circuits 2018, 53, 896–905. [Google Scholar] [CrossRef]

- Mondal, S.; Hall, D.A. An ECG chopper amplifier achieving 0.92 NEF and 0.85 PEF with AC-coupled inverter-stacking for noise efficiency enhancement. In Proceedings of the 2017 IEEE International Symposium on Circuits and Systems (ISCAS), Baltimore, MD, USA, 28–31 May 2017; pp. 1–4. [Google Scholar]

- Harrison, R.R.; Charles, C. A low-power low-noise cmos for amplifier neural recording applications. IEEE J. Solid-State Circuits 2003, 38, 958–965. [Google Scholar] [CrossRef]

- Olsson, R.H.; Gulari, N.; Wise, K.D. Silicon neural recording arrays with on-chip electronics for in-vivo data acquisition. In Proceedings of the 2nd Annual International IEEE-EMBS Special Topic Conference on Microtechnologies in Medicine and Biology, Madison, WI, USA, 2–4 May 2002; pp. 237–240. [Google Scholar]

- Bai, Q.; Wise, K.D. Single-unit neural recording with active microelectrode arrays. IEEE Trans. Biomed. Eng. 2001, 48, 911–920. [Google Scholar] [CrossRef]

- Mondal, S.; Hsu, C.-L.; Jafari, R.; Hall, D.A. A Dynamically Reconfigurable ECG Analog Front-End With a 2.5× Data-Dependent Power Reduction. IEEE Trans. Biomed. Circuits Syst. 2021, 15, 1066–1078. [Google Scholar] [CrossRef]

- Xiao, Z.; Tang, C.-M.; Dougherty, C.M.; Bashirullah, R. A 20µW neural recording tag with supply-current-modulated AFE in 0.13 µm CMOS. In Proceedings of the 2010 IEEE International Solid-State Circuits Conference—(ISSCC), San Francisco, CA, USA, 7–11 February 2010; pp. 122–123. [Google Scholar]

- Olsson, R.H.; Wise, K.D. A three-dimensional neural recording microsystem with implantable data compression circuitry. IEEE J. Solid-State Circuits 2005, 40, 2796–2804. [Google Scholar] [CrossRef]

- Kim, S.-J.; Han, S.-H.; Cha, J.-H.; Liu, L.; Yao, L.; Gao, Y.; Je, M. A Sub-μW/Ch Analog Front-End for Δ-Neural Recording With Spike-Driven Data Compression. IEEE Trans. Biomed. Circuits Syst. 2019, 13, 1–14. [Google Scholar] [CrossRef]

- Pérez-Bailón, J.; Márquez, A.; Calvo, B.; Medrano, N.; Sanz-Pascual, M.T. A 1 V–1.75 μW Gm-C low pass filter for bio-sensing applications. In Proceedings of the 2018 IEEE 9th Latin American Symposium on Circuits & Systems (LASCAS), Puerto Vallarta, Mexico, 25–28 February 2018; pp. 1–4. [Google Scholar]

- Câmpeanu, A.; Gal, J. Design of active filters simulating mesh current equation of LC ladder filters. In Proceedings of the International Symposium on Signals, Circuits and Systems, ISSCS 2005, Iasi, Romania, 14–15 July 2005. [Google Scholar]

- Iizuka, T.; Abidi, A.A. FET-R-C Circuits: A Unified Treatment—Part I: Signal Transfer Characteristics of a Single-Path. IEEE Trans. Circuits Syst. I Regul. Pap. 2016, 63, 1325–1336. [Google Scholar] [CrossRef]

- Rodriguez-Perez, A.; Ruiz-Amaya, J.; Delgado-Restituto, M.; Rodriguez-Vazquez, Á. A Low-Power Programmable Neural Spike Detection Channel With Embedded Calibration and Data Compression. IEEE Trans. Biomed. Circuits Syst. 2012, 6, 87–100. [Google Scholar] [CrossRef]

- Choi, D.; Cha, H.-K. A Low-Power Low-Noise Neural Signal Acquisition Amplifier with Tolerance to Large Stimulation Artifacts. In Proceedings of the 2021 18th International SoC Design Conference (ISOCC), Jeju Island, Republic of Korea, 6–9 October 2021; pp. 325–326. [Google Scholar]

- Kim, C.; Joshi, S.; Courellis, H.; Wang, J.; Miller, C.; Cauwenberghs, G. Sub-μVrms-Noise Sub-μW/Channel ADC-Direct Neural Recording With 200-mV/ms Transient Recovery Through Predictive Digital Autoranging. IEEE J. Solid-State Circuits 2018, 53, 3101–3110. [Google Scholar] [CrossRef]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Huo, Y.; Olsson, R.H., III. A Dynamic Current Pulsing Technique to Improve the Noise Efficiency Factor of Neural Recording Amplifiers. J. Low Power Electron. Appl. 2025, 15, 67. https://doi.org/10.3390/jlpea15040067

Huo Y, Olsson RH III. A Dynamic Current Pulsing Technique to Improve the Noise Efficiency Factor of Neural Recording Amplifiers. Journal of Low Power Electronics and Applications. 2025; 15(4):67. https://doi.org/10.3390/jlpea15040067

Chicago/Turabian StyleHuo, Yujia, and Roy H. Olsson, III. 2025. "A Dynamic Current Pulsing Technique to Improve the Noise Efficiency Factor of Neural Recording Amplifiers" Journal of Low Power Electronics and Applications 15, no. 4: 67. https://doi.org/10.3390/jlpea15040067

APA StyleHuo, Y., & Olsson, R. H., III. (2025). A Dynamic Current Pulsing Technique to Improve the Noise Efficiency Factor of Neural Recording Amplifiers. Journal of Low Power Electronics and Applications, 15(4), 67. https://doi.org/10.3390/jlpea15040067