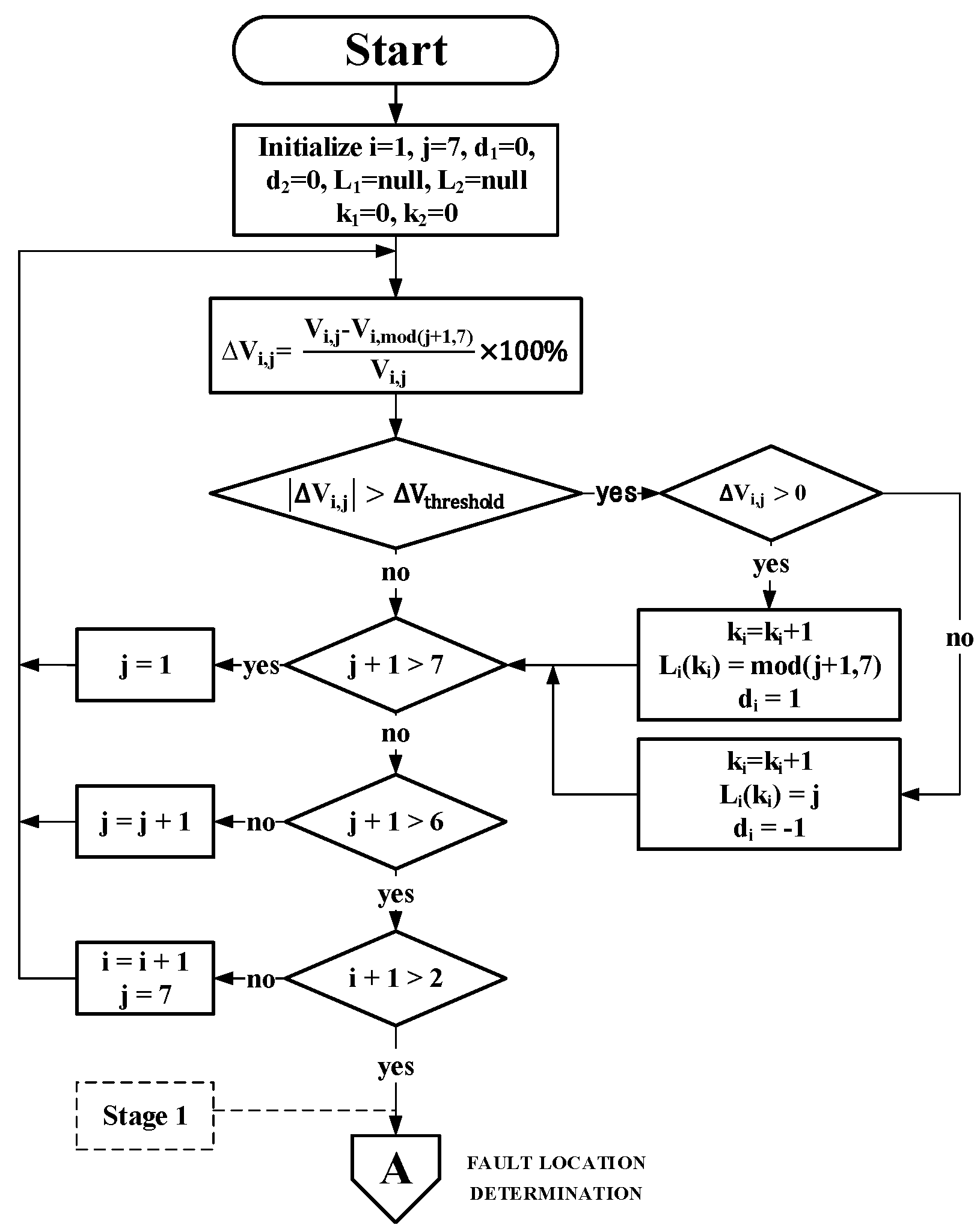

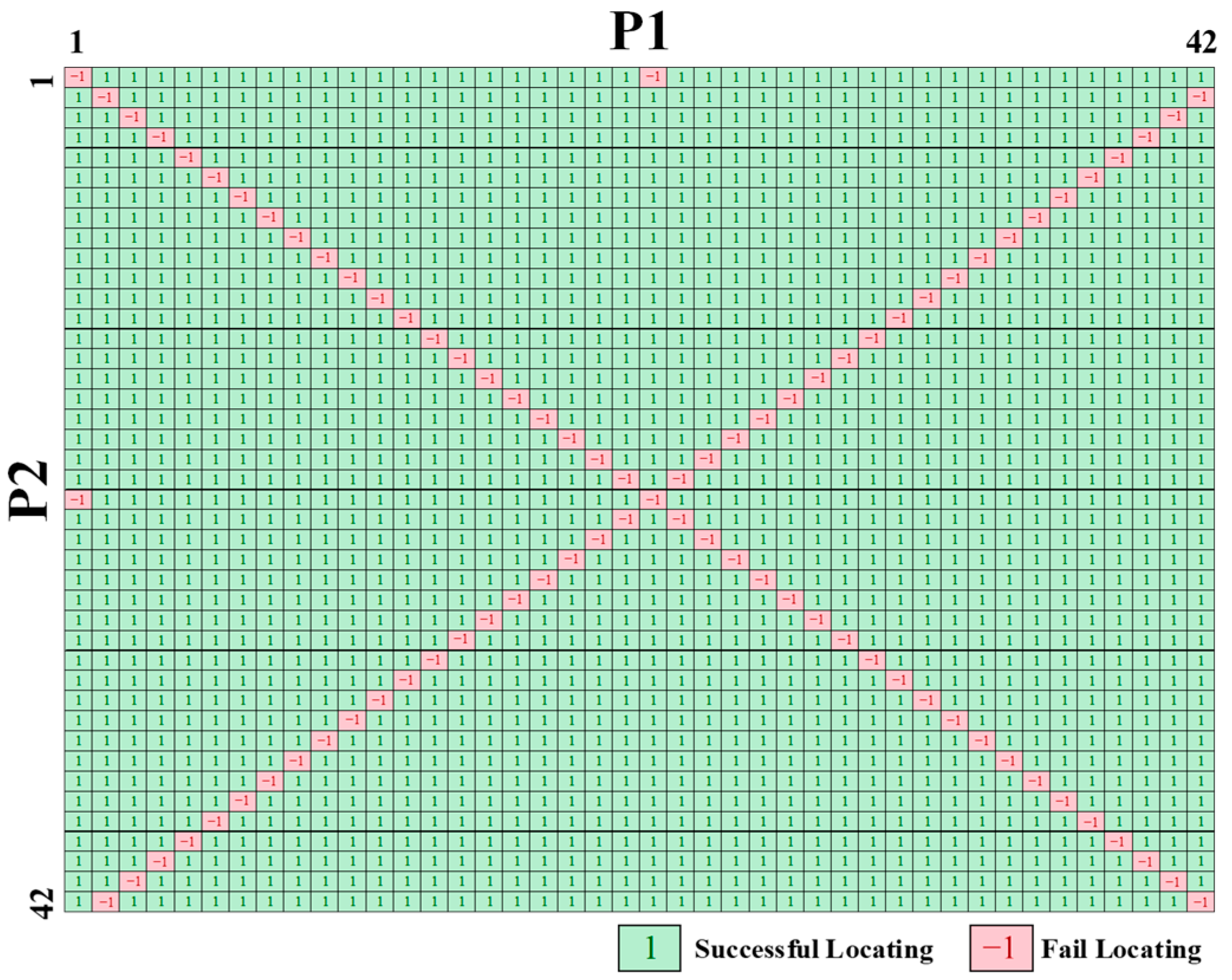

The heuristic algorithm for line-to-line fault location can be divided into two main phases: the fault candidate location marking process, and the fault location determination process. The following sections provide a detailed introduction and case analysis of these two parts.

3.2.1. Fault Candidate Location Marking

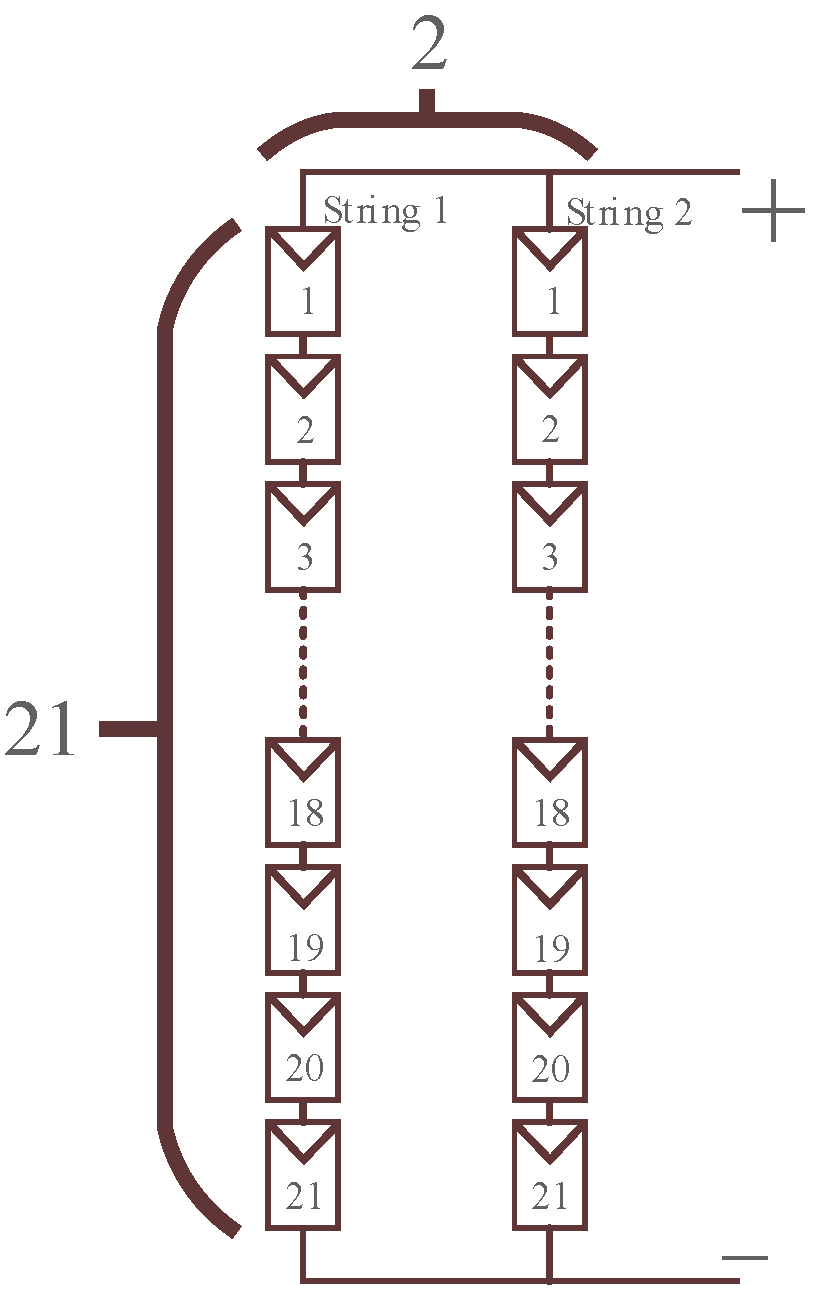

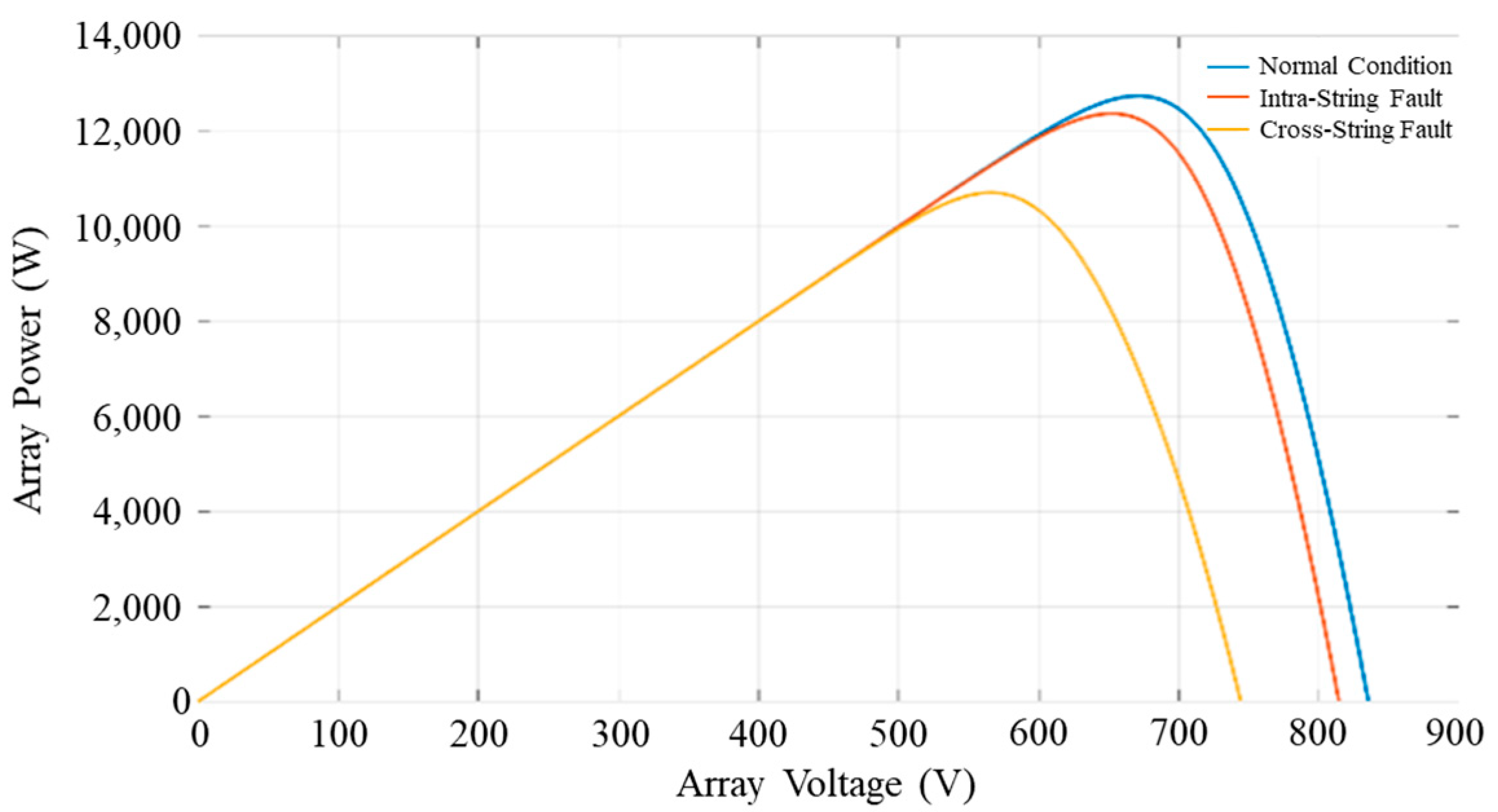

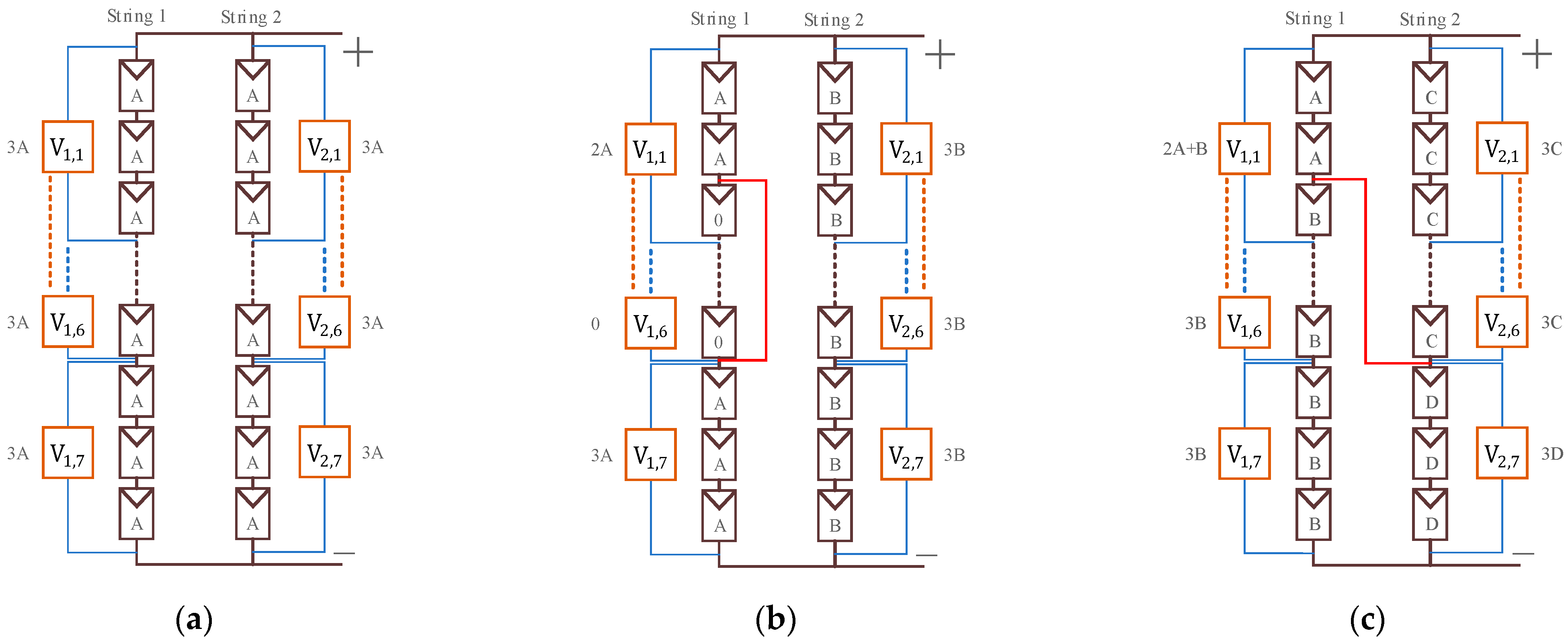

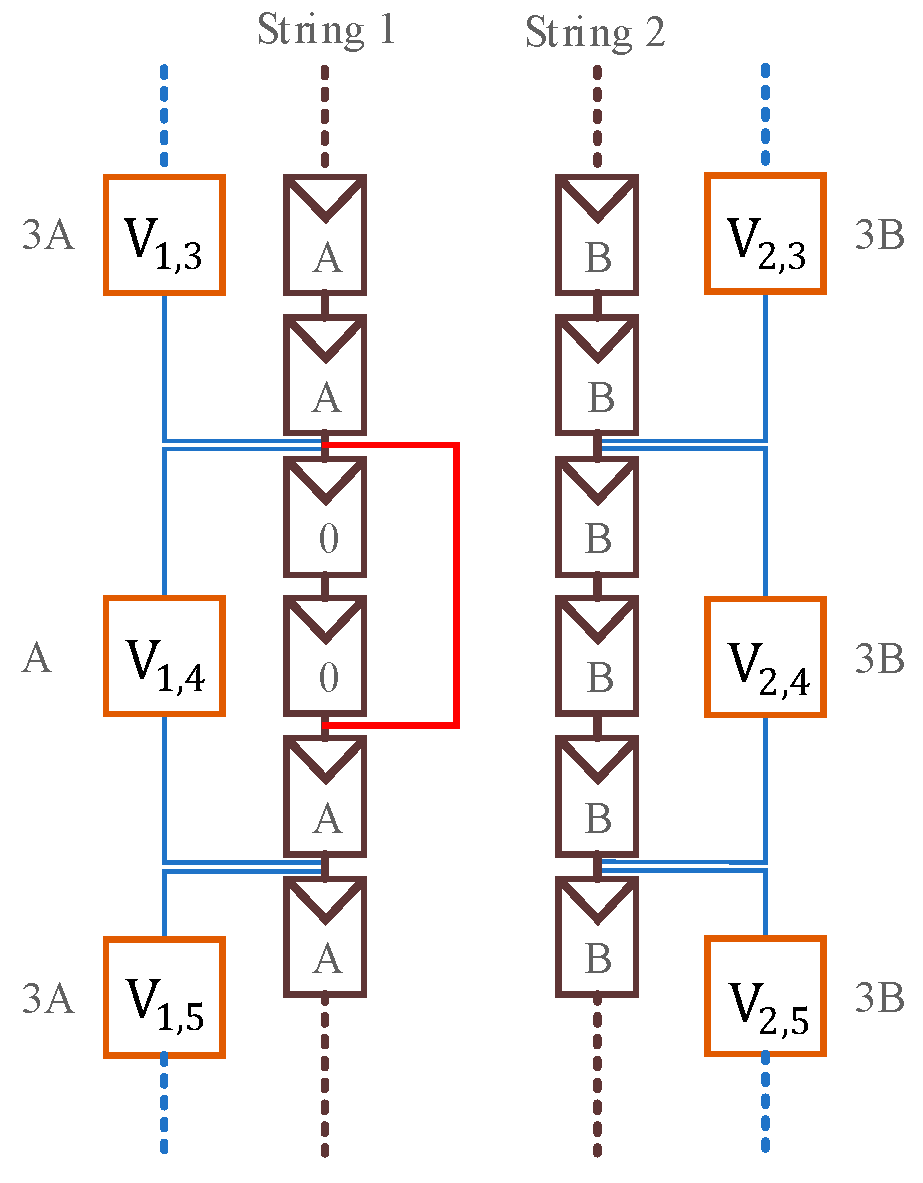

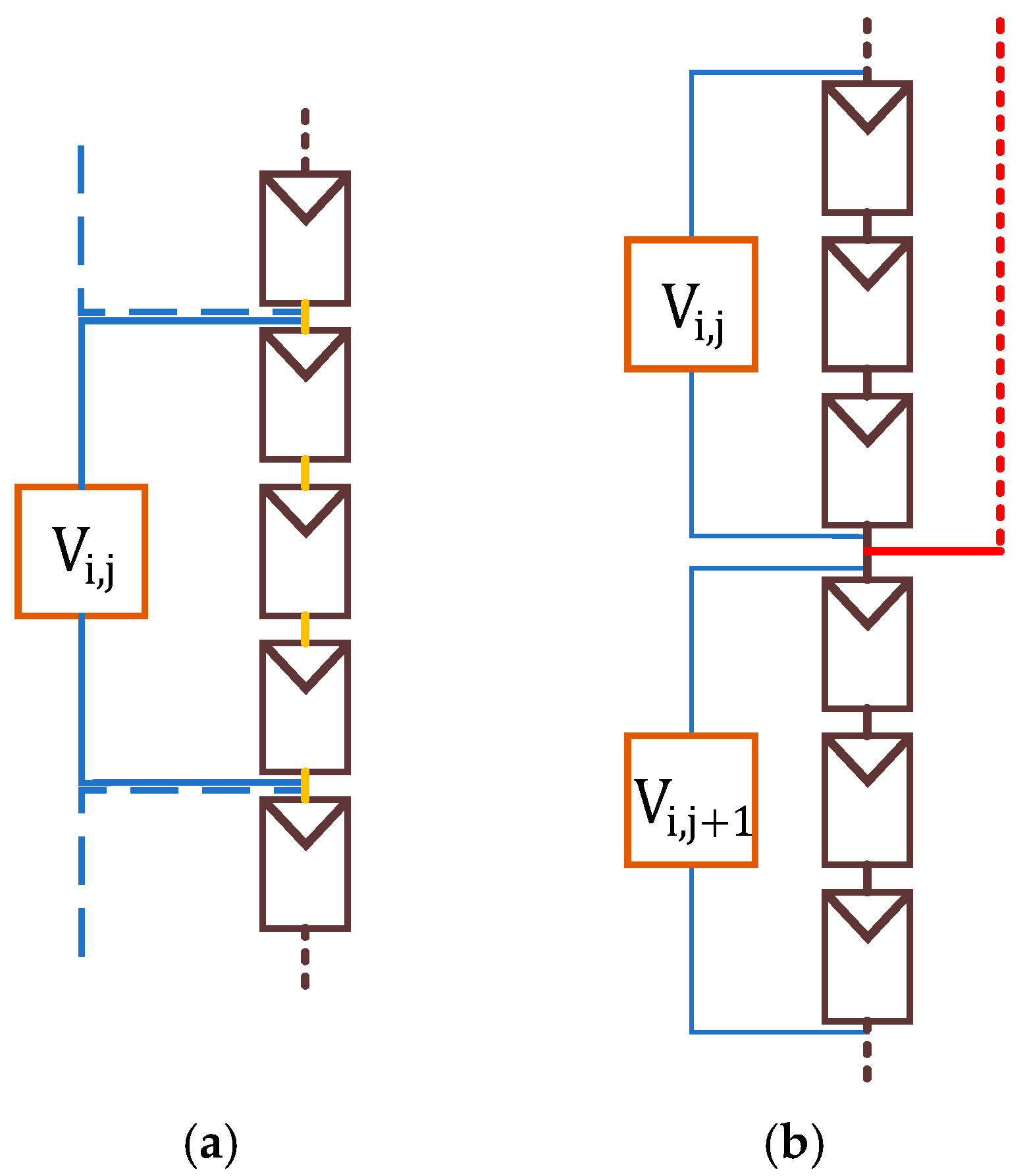

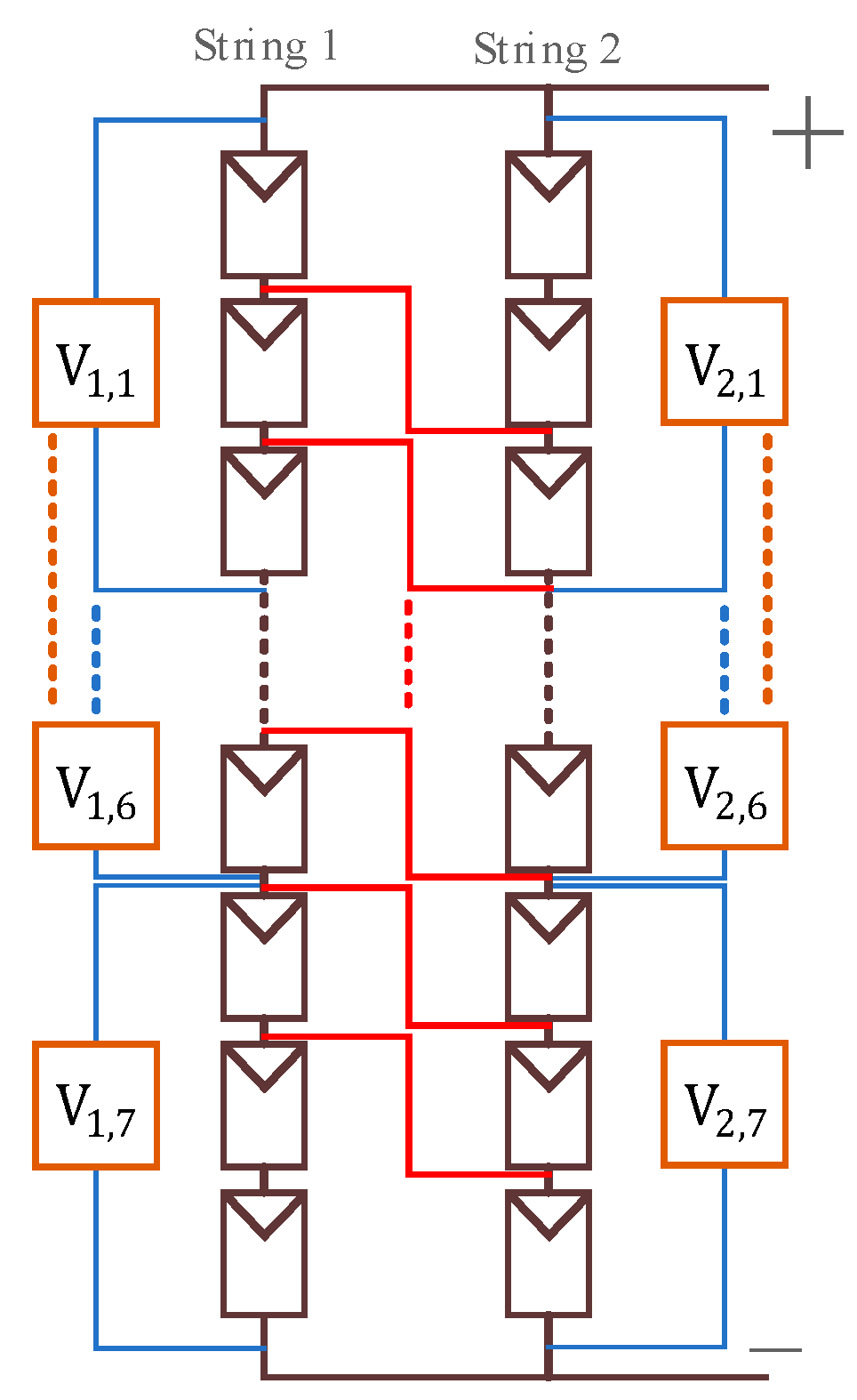

Assuming each module voltage is evenly distributed, each module group voltage will be identical during normal operation. This is shown in

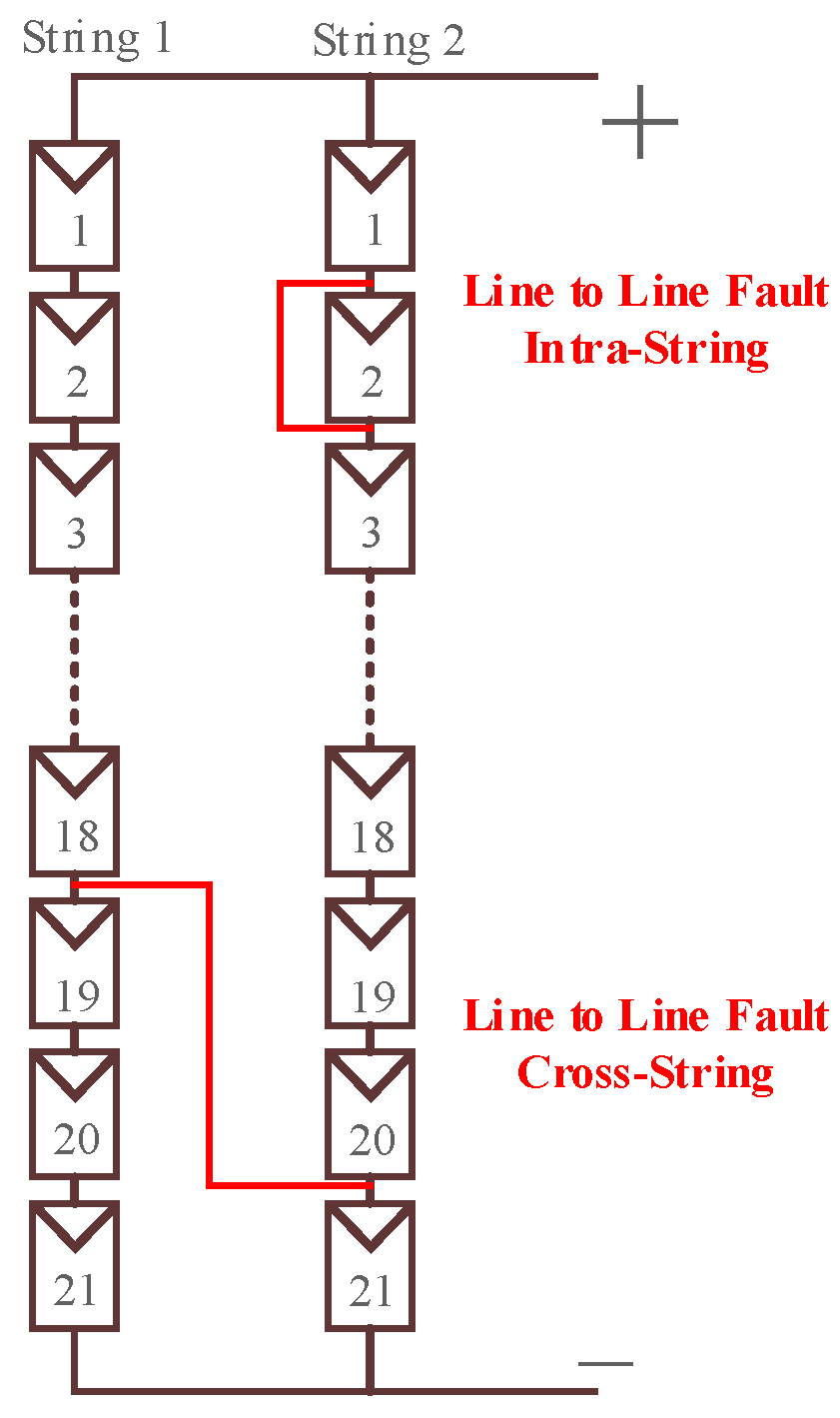

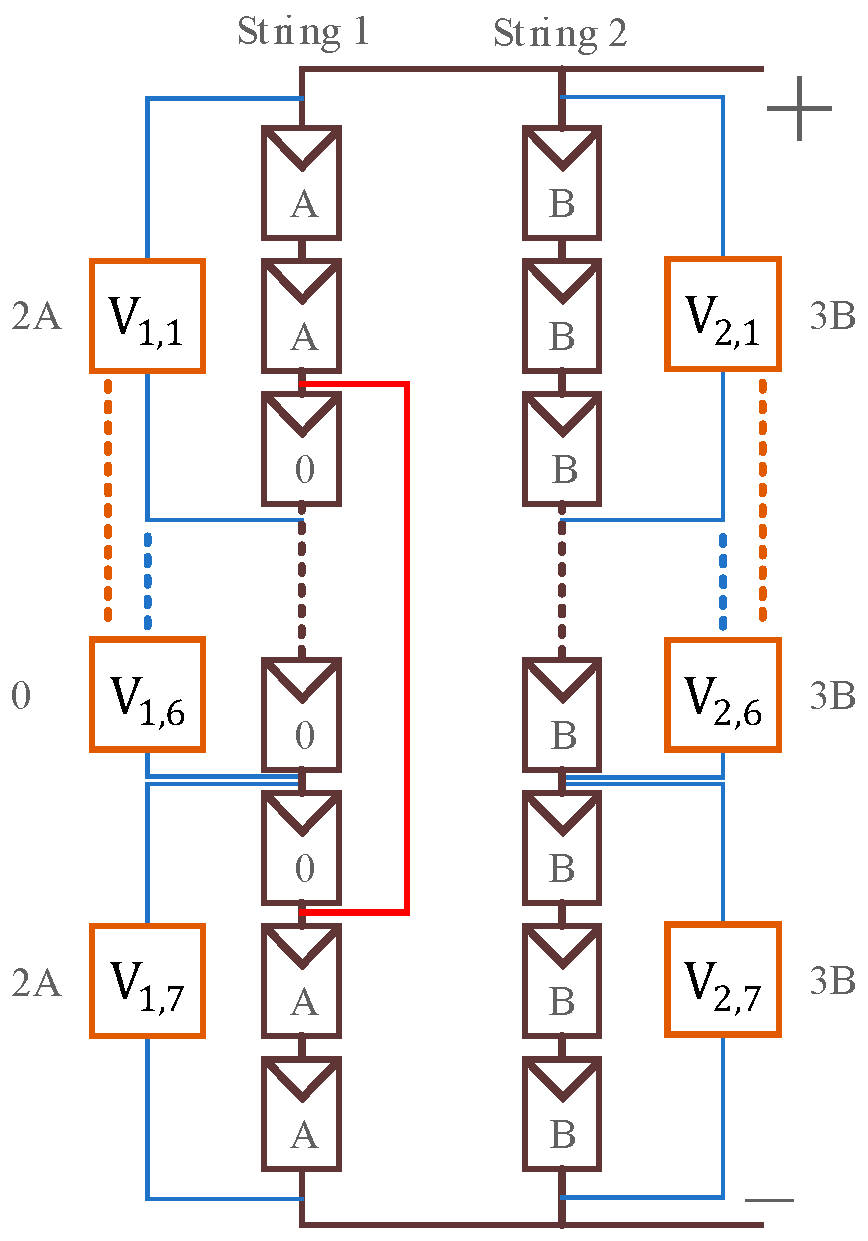

Figure 5a, with each group voltage at 3A. When a line-to-line short-circuit fault occurs, the voltages of each module group change differently. In

Figure 5b, for an intra-string fault, the voltage of the affected module is 0 V. Therefore, in String 1,

V1,1 = 2A,

V1,2 −

V1,6 = 0,

V1,7 = 3A, while all module group voltages in String 2 remain at 3B. In

Figure 5c, for a cross-string fault, the array module voltages split into values A, B, C, and D, resulting in

V1,1 = 2A + B,

V1,2 −

V1,7 = 3B,

V2,1 −

V1,6 = 3C, and

V2,7 = 3D.

To identify all possible fault locations, a scanning method is used to compare the voltage of each module group with the voltage of the subsequent module group, calculating the rate of voltage change ∆

Vi,j between them. This is shown in Equation (2).

When |∆

Vi,j| exceeds the set threshold ∆

Vthreshold, this indicates that a line-to-line fault has occurred in one of the two module groups. Typically, the module voltage in the faulted group is lower than in normal modules, so the sign of

∆Vi,j must be determined. If ∆

Vi,j is positive, this indicates that

Vi,j+1 has a lower voltage, so the module with index

j + 1 should be marked. Conversely, if ∆

Vi,j is negative, this indicates that ∆

Vi,j has a lower voltage, so the module with index

j should be marked. This relationship is represented in Equation (3):

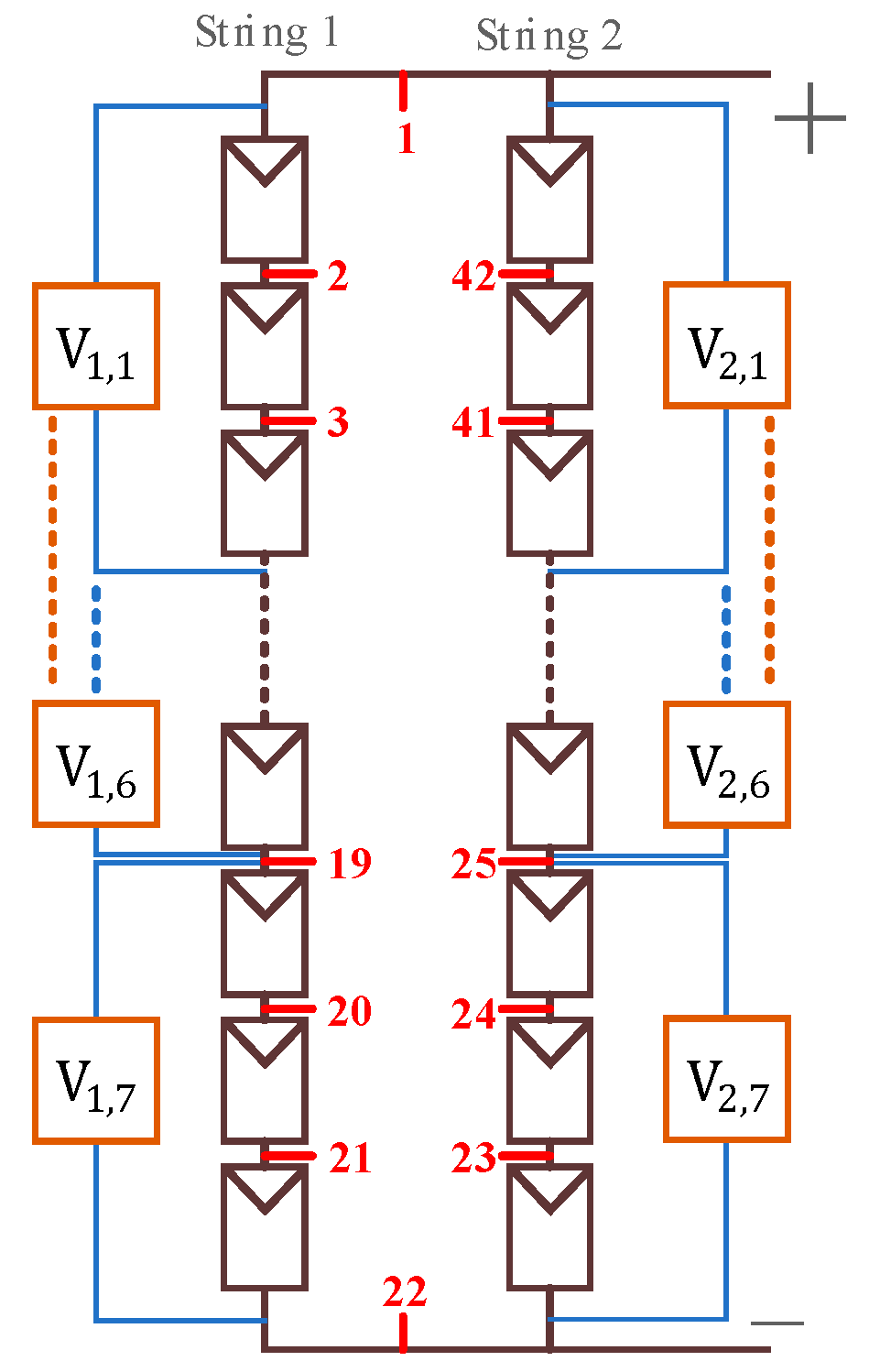

Using the 21 × 2 array configuration as an example, this study establishes a candidate location marking process for line-to-line short-circuit faults. This is shown in

Figure 6. The scanning sequence starts from 7, followed by 7, 1, 2, …, 6. After calculating ∆

Vi,j for the 6th module group, the process moves to the next row. The purpose of this sequence is to ensure that each module group undergoes calculation. To simplify the process,

j + 1 is replaced with mod(

j + 1).

In the candidate location marking process for line-to-line short-circuit faults shown in

Figure 6, six additional variables are introduced:

d1,

d2,

L1,

L2,

k1, and

k2. Here,

d1 and

d2 represent the direction of module group voltages in the two strings. When a cross-string line-to-line short-circuit fault occurs, the module group voltages in the higher-potential string are ordered from high to low, whereas in the lower-potential string, the voltages are ordered from low to high. Thus, a direction value d of 1 for a string indicates that the fault point is the first recorded fault point in that string. Conversely, if

d = −1, this indicates that the fault point is the last recorded fault point in that string, while a value of 0 indicates that no fault has occurred. Furthermore,

L1 and

L2 are sequences that record the fault candidate locations for each string. The remaining variables,

k1 and

k2, represent the number of fault candidate locations within each string.

3.2.2. Fault Location Determination

Through the previously described candidate location marking process for line-to-line short-circuit faults, this study obtains several pieces of information useful for determining the fault location:

d1,

d2,

L1,

L2,

k1, and

k2. Next, using the 21 × 2 array configuration as an example, this study presents the proposed fault location determination process for line-to-line short-circuit faults, as shown in

Figure 7.

This process is derived from empirical observation and results in six cases, labeled Case 1 to Case 6. Cases 1 to 3 involve intra-string short-circuit faults, while Cases 4 to 6 involve cross-string short-circuit faults. Each of these six cases is explained in detail below.

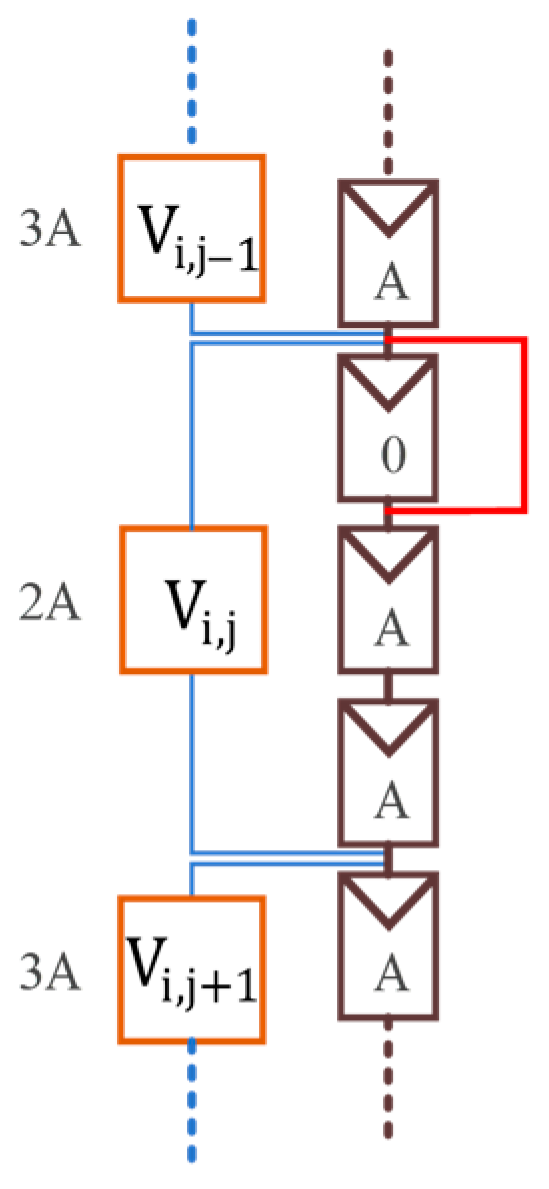

Case 1: An intra-string short-circuit fault occurs within a single module group, as shown in

Figure 8, with the fault occurring in module group

V1,4; two modules are short-circuited, resulting in a module group voltage of A. In the fault marking process, when

i = 1,

j = 3, a comparison between the third and fourth module groups reveals that |∆

V1,3| is greater than the threshold ∆

Vthreshold and is positive. Therefore, the fault position count

k1 is incremented by 1, the fault candidate array

L1 adds the index 4, and the voltage direction

d1 is set to 1. When

j = 4, |∆

V1,4| also exceeds the threshold but is negative, so

k1 is incremented to 2,

L1 adds the index 4, and

d1 is set to −1. For

i = 2, no anomalies are detected; therefore, the initial state is maintained. The results of the fault marking process are shown in

Table 2, Stage 1.

Next, the process proceeds to the fault location determination step. Initially, duplicate fault points in the fault candidate array

Li are removed, and the remaining points are sorted. The fault point count

ki is then recalculated, with the results shown in

Table 2, Stage 2. At this point, it has been determined that a fault point exists in the first string, so s is set at 1, with only one fault point present. Therefore, it is concluded that the fault is located in the fourth module group of the first string.

Case 2: An intra-string short-circuit fault occurs at the beginning and end module groups of the string, as shown in

Figure 9. The fault is located between module groups

V1,1 and

V1,7. This type of fault is a more severe line-to-line short-circuit fault, as nearly the entire string is short-circuited, impacting the entire array’s power generation.

In the fault marking process, String 1 initially compares

V1,7 with

V1,1 and finds that both have the same voltage; therefore, no record is made. However, in the comparisons between

V1,1 and

V1,2, and between

V1,6 and

V1,7, it is observed that

V1,2 and

V1,6 have lower voltages, and these are recorded. Thus, a total of two module groups are marked as faulted, with the final recorded voltage direction as −1. No abnormalities are detected in String 2; therefore, it remains in its initial state. The marking results are shown in

Table 3, Stage 1.

In the fault determination process, duplicate fault points in the fault candidate array

Li are first removed and sorted, and the fault point count

ki is recalculated, with the results shown in

Table 3, Stage 2. At this stage, it has been found that there are two fault points in String 1, so s is set at 1. Directly identifying the fault in module groups 2 and 6 of String 1 would lead to an error. Therefore, whether the first marked point in

Ls is less than or equal to 2 and the last marked point in

Ls is greater than or equal to 6 will be checked first. If this condition is true, it is checked whether

V1,2 and

V1,6 are 0. If the condition is false, no further modifications are necessary. If the condition is true, this indicates that the fault is not in module groups 2 and 6, and the location results need to be adjusted by setting

Ls(1) to 1 and

Ls(

ks) to 7. This is shown in the “Modified” section of

Table 3. Finally, it is determined that the fault location is in module groups 1 and 7 of String 1.

Case 3: Multiple module groups experience intra-string short-circuit faults, as shown in

Figure 10. The fault occurs between module groups

V1,6 and

V1,7. In accordance with the fault marking process, in String 1, the initial comparison between

V1,7 and

V1,1 reveals that

V1,7 has a lower voltage; therefore, it is marked. The subsequently marked fault points are 6 and 7, resulting in a total of three fault points, with the final recorded voltage direction as 1. No abnormalities are detected in String 2. The results are shown in

Table 4, Stage 1.

Next, in the fault determination process, duplicate fault points in the fault candidate array

Li are removed and sorted, and the fault point count

ki is recalculated. The results are shown in

Table 4, Stage 2. At this stage, it is determined that there are two fault points in String 1, setting s to 1. However, the conditions

Ls(1) <= 2 &

Ls(

ks) >= 6 &

Vs,2 = 0 &

Vs,6 = 0 are not satisfied. Therefore, no modifications are needed, and the fault points are directly identified as being in module groups 6 and 7 of String 1.

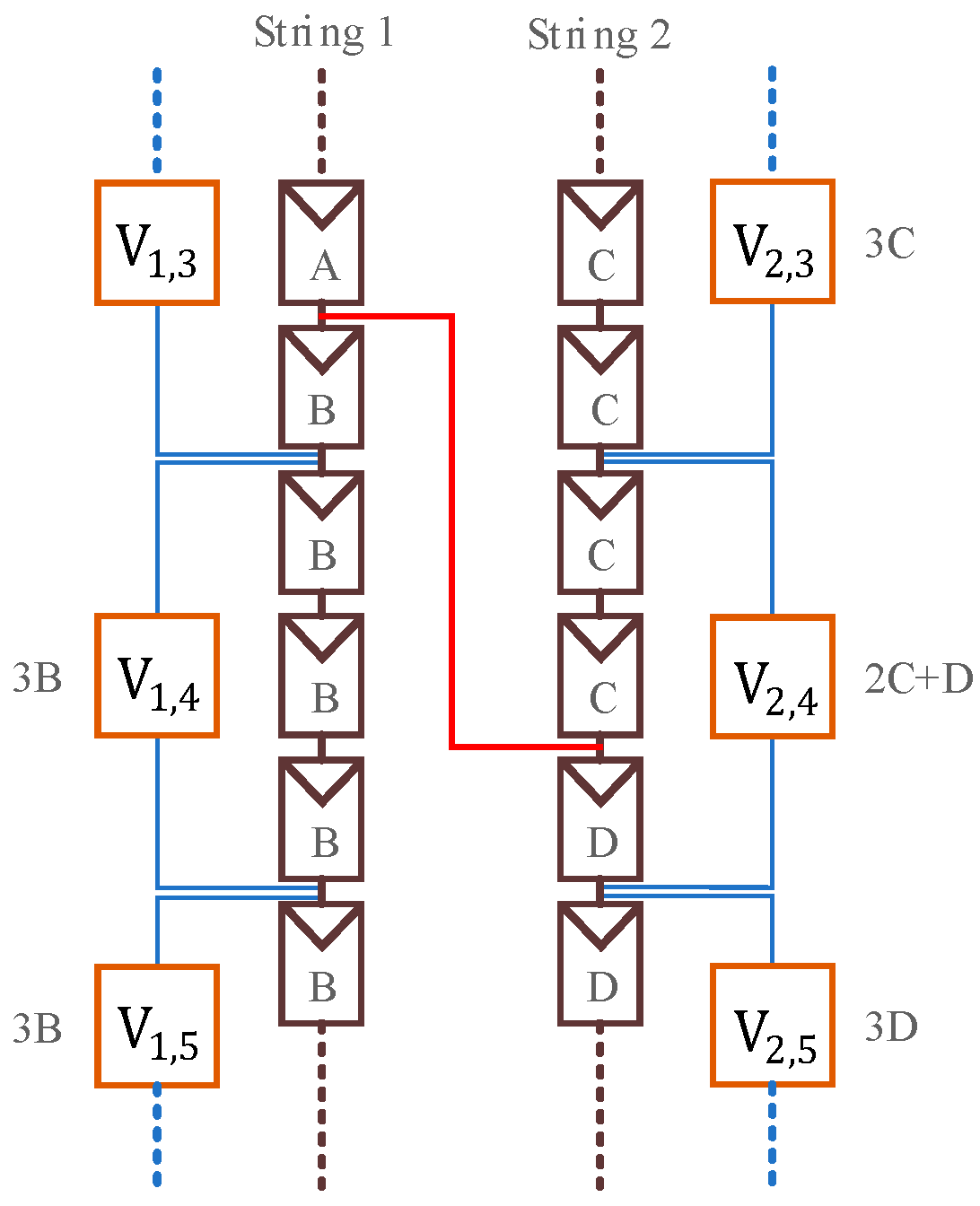

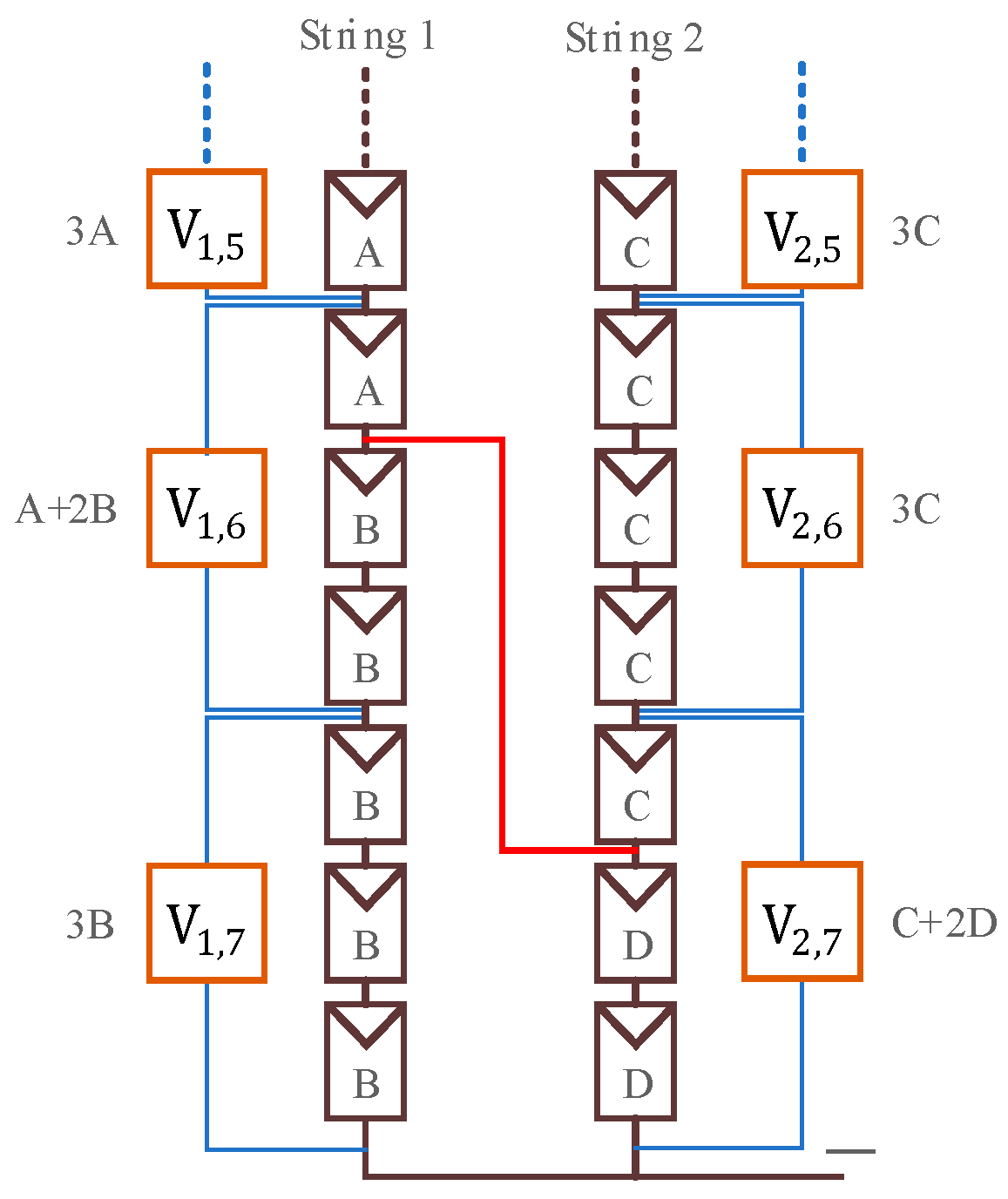

Case 4: A cross-string short-circuit fault occurs between two strings, with neither endpoint located in the first or last two module groups of each string, as shown in

Figure 11. The fault occurs between module groups

V1,3 and

V2,4, so the voltages of all modules are divided into four values: A, B, C, and D.

In accordance with the fault marking process proposed in this paper, correctly marking the fault location requires knowledge of the relative magnitudes between A and B, as well as between C and D. This relationship can be determined through comparison. Using the fault structure in

Figure 11 as an example, the array currents are labeled as shown in

Figure 12.

In accordance with Kirchhoff’s Voltage Law, the sum of voltages in any closed loop is zero, resulting in the following equations:

In accordance with the principle of proportionality, the following relationships are established:

Based on the I–V characteristic curve of the PV module, it is understood that higher voltage corresponds to lower current, so:

In accordance with Kirchhoff’s Current Law, the current flowing into any node is always equal to the current flowing out, implying that

IFault must be greater than 0. Therefore:

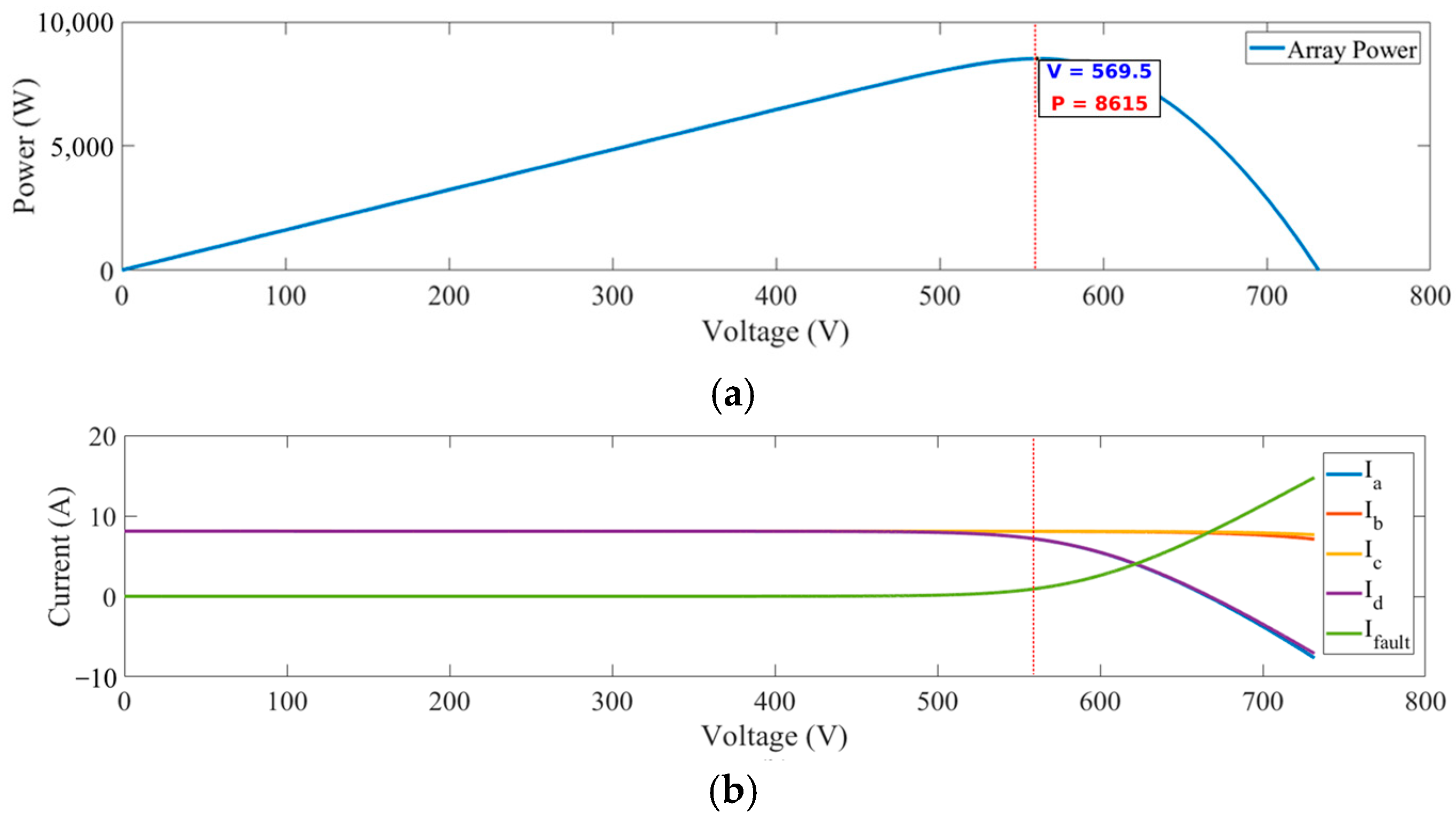

This inference is also confirmed by simulation, as shown in

Figure 13. In

Figure 13a, the simulation conditions are set to normal operating cell temperature (NOCT), with irradiance G at 800 W/m

2 and module temperature T at 45 °C. When the array reaches maximum power, the currents in

Figure 13b exhibit the relationships described in Equations (6) and (7). Although

IFault approaches 0 A at lower voltages, a closer inspection reveals that it remains greater than 0 A at all times.

Then, based on the I–V characteristic curve of the PV module, it can be concluded that:

With the known voltage relationships between A and B, and C and D, the fault marking process is applied to the fault structure in

Figure 11. In String 1, the fault points 7, 3, and 4 are sequentially marked, with the final recorded voltage direction as 1. In String 2, the fault points 1, 3, and 4 are marked in sequence, with the final recorded voltage direction as −1. The results are shown in

Table 5, Stage 1.

At the beginning of the fault determination process, the marked results are organized and sorted, as shown in

Table 5, Stage 2. At this point,

d1 = 1 and

d2 = −1, so s is set to 1. Upon inspection, the last marked point in the low-potential string

L2 is not 6, and the first marked point in the high-potential string

L1 is not 2, indicating that the fault is located in the middle of both strings. Therefore, the fault location is identified as the first fault point in the high-potential string and the last fault point in the low-potential string. In this case, the fault is determined to be a short circuit between module group 3 in String 1 and module group 4 in String 2.

Case 5: A cross-string short-circuit fault occurs between two strings, with the low-potential end located in the last module group of the string, as shown in

Figure 14. The fault occurs between module groups

V1,6 and

V2,7. The voltages of all modules are divided into four values, A, B, C, and D, with the same relative magnitudes as in Case 4.

Following the fault marking process, the results are shown in

Table 6, Stage 1. In String 1, fault points 7, 6, and 7 are marked sequentially, with the final recorded voltage direction as 1. In String 2, fault points 1 and 6 are marked sequentially, with the final recorded voltage direction as −1.

The process then proceeds to fault marking, where duplicate fault points in the fault sequence

Li are removed and sorted, and the fault point count

ki is recalculated. The results are shown in

Table 6, Stage 2, with

d1 = 1 and

d2 = −1, so s is set to 1. If the fault location is determined directly using the approach in Case 4, it will result in an error because the low-potential end fault point is located at the last fault point of that string. To accurately locate the fault, if the low-potential end is found in the second-to-last module group, it is necessary to first confirm whether the voltages of the second-to-last and third-to-last module groups are equal. In accordance with the premise of even voltage distribution, if the fault indeed occurs in the last module group, the voltages of the second-to-last and third-to-last module groups will be equal. Thus, when this condition is observed, the last fault point in the low-potential string should be adjusted to the last module group index to achieve an accurate fault location.

In Case 5, this condition is indeed confirmed, so the sequence

L2 is modified accordingly, as shown in

Table 6, Modified. The fault location is then determined using the approach in Case 4, resulting in a short-circuit fault identified between module group 6 in String 1 and module group 7 in String 2.

Case 6: A cross-string short-circuit fault occurs between two strings, with the high-potential end located in the first module group of the string, as shown in

Figure 15. The fault occurs between module groups

V1,1 and

V2,2. The voltages of all modules are divided into four values, A, B, C, and D, with the same relative magnitudes as in Case 4.

Following the fault marking process, the results are shown in

Table 7, Stage 1. In String 1, fault points 7 and 2 are marked sequentially, with the final recorded voltage direction as 1. In String 2, fault points 1, 2, and 3 are marked sequentially, with the final recorded voltage direction as –1.

After entering the fault marking process, the marked results are organized as shown in

Table 7, Stage 2;

d1 = 1 and

d2 = −1, so s is set to 1. When the high-potential end is located in the first module group of the string, the same issue as in Case 5 arises. However, in this case, the comparison is between the voltages of the second and third module groups in the high-potential string. If these two voltages are equal, this indicates that the fault is not in the first module group. Therefore, the first fault point in the high-potential string should be adjusted to the index of the first module group for accurate location. The modified results are shown in

Table 7, Modified. The final fault location is determined to be a short circuit between module group 1 in String 1 and module group 2 in String 2.

In addition to the six PV array line-to-line short-circuit fault cases described above,

Figure 7 (“Fault location determination process”) shows two situations in which fault location cannot be determined. The first case is when no fault location information is obtained during the fault marking process, making location impossible. This typically occurs when a short-circuit fault likely happens at both positive and negative endpoints of the array, causing all array voltages to read 0 V. The second case occurs when both

d1 and

d2 are either 1 or −1. This situation is unlikely under ideal conditions, as the relative magnitudes between the four voltage values (A, B, C, and D) in a cross-string fault are clearly defined, so this should not happen. Such a situation is more likely caused by multiple simultaneous faults; the heuristic fault location algorithm proposed in this paper cannot determine the fault location under these conditions.

3.2.4. Threshold Determination

In the heuristic algorithm for line-to-line fault location, a critical component is appropriately setting the ∆Vthreshold in the fault marking process. If ∆Vthreshold is set too high, it may prevent milder faults from being accurately marked. Conversely, if ∆Vthreshold is set too low, it could lead to unnecessary misjudgments. Therefore, determining the optimal ∆Vthreshold is essential.

This section primarily explores how to set ∆Vthreshold based on the array structure and the module group voltage measurement range. Typically, an intuitive approach is to set ∆Vthreshold to be able to detect the mildest fault condition as a primary requirement. Therefore, using a 21 × 2 array configuration with three modules per module group as an example, this paper discusses the settings for both intra-string and cross-string line-to-line short-circuit faults.

In the intra-string fault type, the mildest fault condition occurs when a single PV module experiences a short circuit, as shown in

Figure 17. If a short-circuit fault occurs in module group

Vi,j, the voltage change rates related to

Vi,j are ∆

Vi,j+1 and ∆

Vi,j. Based on the voltage distribution, |∆

Vi,j+1| can be calculated as 33.33%, and |∆

Vi,j| as 50%. Therefore, in the intra-string fault type, the minimum ∆

Vthreshold should be set below 33.33%.

In the intra-string fault type, the mildest fault condition is also analyzed. As shown in

Figure 18, a line-to-line short-circuit fault occurs between two strings with only one PV module difference. However, due to different positions, there are 19 possible fault scenarios from the top to the bottom of the array. The following section will simulate these 19 scenarios and calculate the minimum |∆

Vi,j| for each case. In addition to the NOCT, the simulation environment parameters also explore four more extreme combinations of irradiance and module temperature: G = 100 W/m

2, T = 10 °C; G = 100 W/m

2, T = 85 °C; G = 1000 W/m

2, T = 10 °C; and G = 1000 W/m

2, T = 85 °C.

The simulation results are shown in

Table 8, which indicate that |∆

Vi,j| is lower at lower temperatures. The minimum |∆

Vi,j| across all conditions occurs under the environment parameters G = 100 W/m

2, T = 10 °C, with a value of 2.1304%. Therefore, in the cross-string fault type, the minimum ∆

Vthreshold should be set below 2.1304% to ensure accurate fault location.

Finally, combining the minimum ∆Vthreshold settings for both intra-string and cross-string fault types, this paper ultimately selects 2% as the ∆Vthreshold for the 21 × 2 array configuration. This ensures that the heuristic line-to-line fault location algorithm can identify all possible fault locations.

The ∆Vthreshold is primarily determined based on the array configuration and environmental conditions, as demonstrated for the 21 × 2 array in this study. For different array sizes or module groupings, the threshold should be recalibrated accordingly. Similarly, environmental factors such as irradiance and temperature affect the voltage differences and thus the threshold value. Developing adaptive thresholding techniques that automatically adjust to varying array configurations and operational conditions is an important direction for future research to improve the robustness and applicability of the proposed algorithm.

It is acknowledged that the proposed heuristic algorithm assumes relatively stable module voltage distributions under fault conditions. While minor environmental variations and measurement noise are mitigated through the use of module group voltage averages, significant fluctuations may affect accuracy. Robustness testing under various non-ideal conditions and incorporation of filtering or adaptive thresholding techniques are important future research directions to enhance practical applicability.