Research on a Secure and Reliable Runtime Patching Method for Cyber–Physical Systems and Internet of Things Devices

Abstract

1. Introduction

- We have proposed a customized remediation framework to meet the asymmetric or heterogeneous needs of embedded systems. We have designed a four-step remediation process (vulnerability identification, vulnerability localization, patch preparation, and patch switching) tailored to the characteristics of embedded devices, which enhances the detection-based hotfixing approach to avoid relying on binary detection and other software layers and improves the accuracy and adaptability of the patches.

- To address service interruptions caused by static patching, we have proposed a lightweight runtime hot-patching method tailored for embedded devices. Although hot patching is a known concept, its application in resource-constrained environments, like industrial embedded systems, remains challenging. Our approach has avoided system downtime by leveraging built-in hardware debug features, ensuring low overhead and strict real-time performance. This has enabled safe and efficient patching in mission-critical scenarios where service continuity is essential.

- In order to overcome the high overhead of dynamic patching, the framework uses on-board debugging units to dynamically replace instructions at runtime, which has reduced resource consumption during the repair process majorly while maintaining the real-time nature of the system. This method assumes the availability of on-chip debug components, like FPB and DWT, which are widely supported by Cortex-M microcontrollers; thus, its applicability is focused on embedded platforms with such hardware features.

- The experimental results have shown that the hot-patch-based vulnerability repair method proposed here has performed well in embedded device vulnerability repair, has effectively reduced system downtime and service interruption, and has provided strong support for the stability and availability of these kinds of symmetric systems. Through in-depth analysis and optimization, we have provided an innovative and efficient solution for the security maintenance of embedded devices, which has important theoretical significance and practical value.

2. Related Works

3. Methodology

3.1. Vulnerability Identification

3.2. Vulnerability Localization

3.3. Patch Preparation

3.4. Patch Switching

3.4.1. Debugging Unit FPB Configuration

- The fpb_Init function is responsible for initializing the FPB unit, ensuring that the FPB unit has been loaded correctly, and preparing for subsequent task scheduling and priority management.

- The fpb_enable function is used to set the FPB unit to be enabled and disabled; if not set, the device will ignore any breakpoints that have been configured and enabled.

- Let the patch code be denoted as , and let represent the address where the jump instruction will be injected. We define a mapping function:

- We define a patch loading function:

3.4.2. Add Patch Tasks to the Scheduler and Configure Jump Instructions

3.4.3. The Update Program Notifies the Hardware to Activate the Patch Through Atomic Instructions

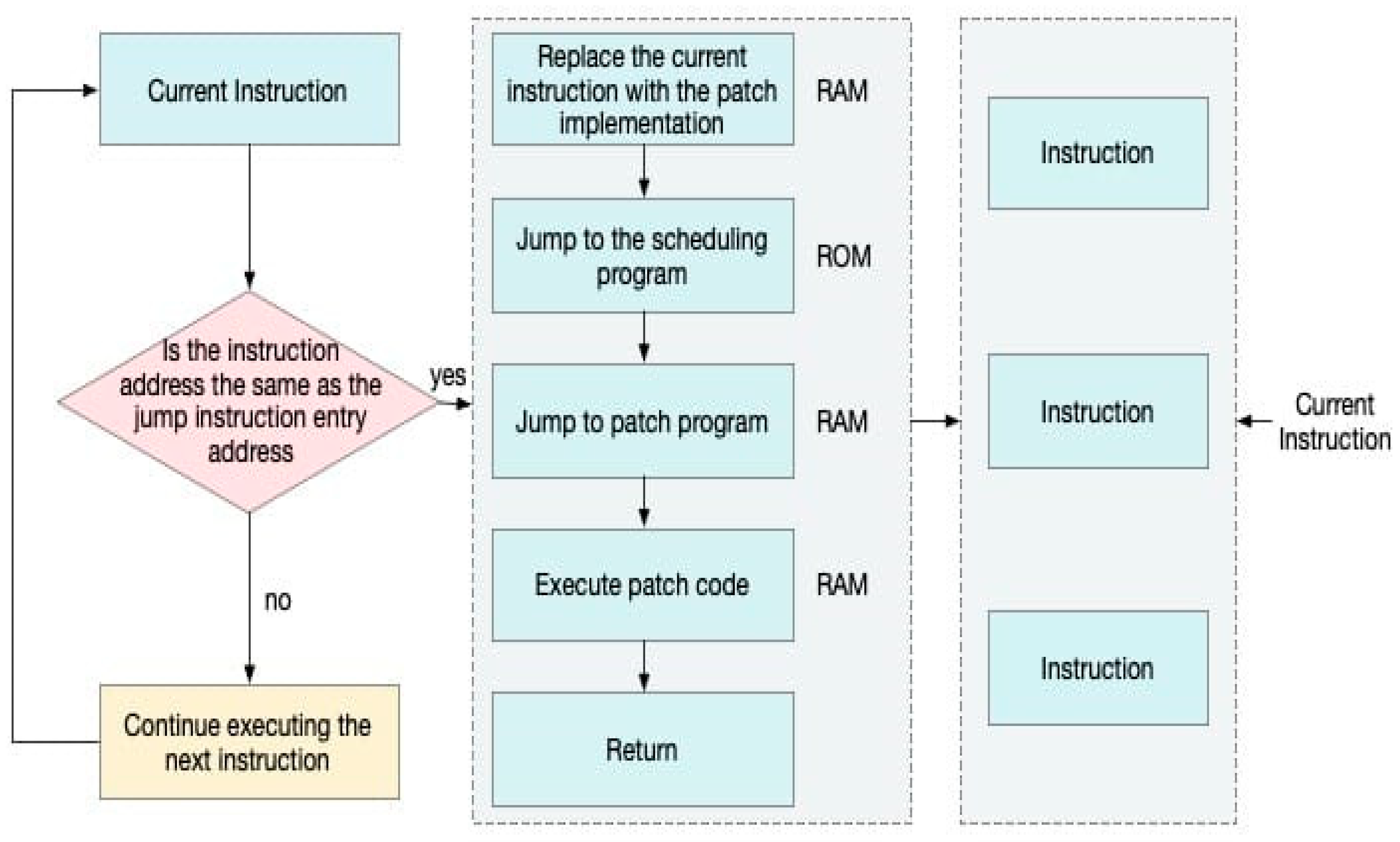

3.4.4. Monitor the Instructions Executed by the CPU

3.4.5. Jump to Patch Code by Jump Instruction

3.4.6. Execute Patch Code

4. Experiments

4.1. Experimental Environment

4.2. Datasets

4.3. Experiment and Result Analysis

4.3.1. Vulnerability Fixing Time Comparison Experiment and Result Analysis

4.3.2. Vulnerability Repair Success Rate Comparison Experiment and Result Analysis

4.3.3. System Stability Comparison Experiment and Result Analysis

4.3.4. System Usability Comparison Experiment and Result Analysis

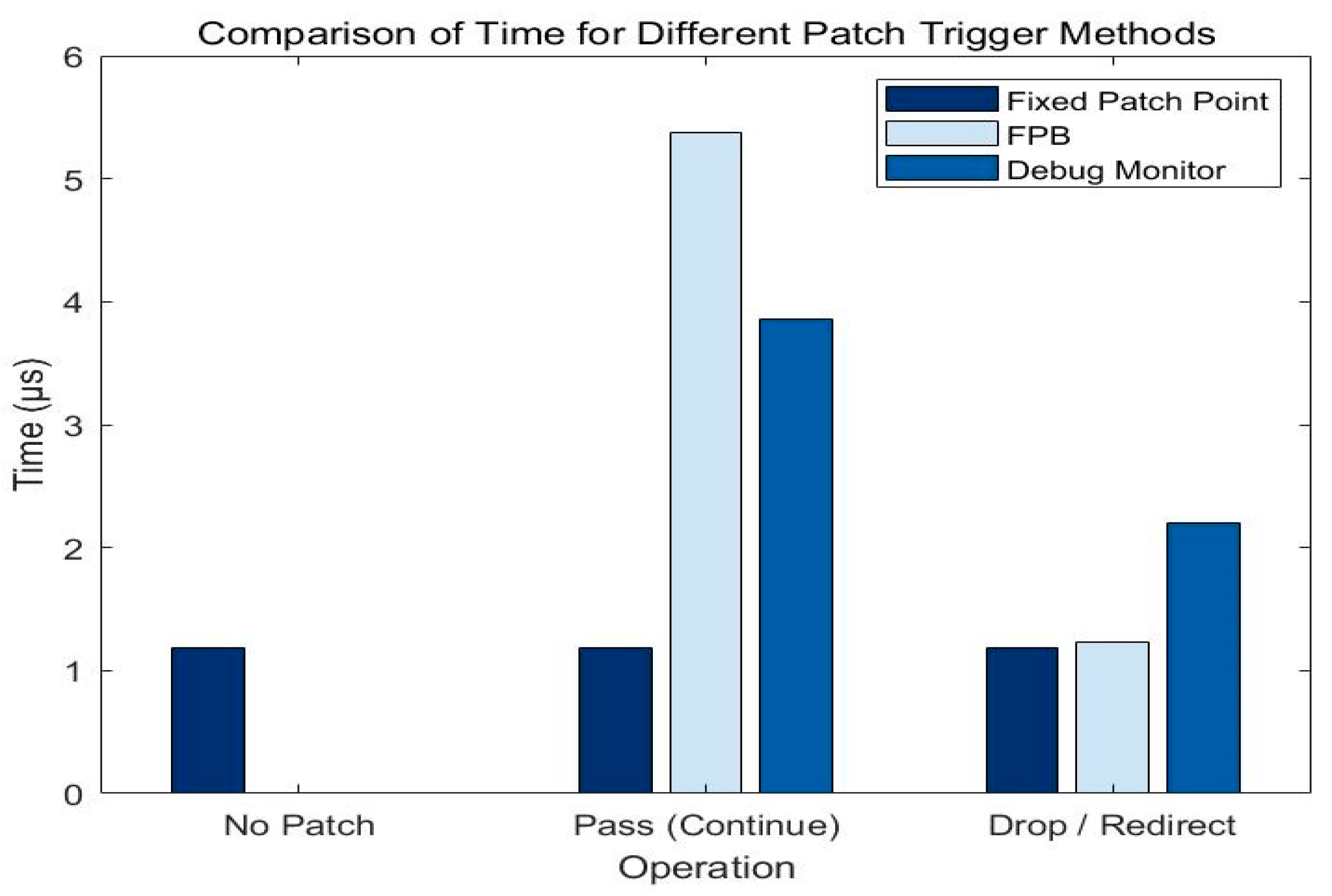

4.3.5. Experiment and Result Analysis of Time and CPU Cycle Required for Different Patch-Triggering Methods

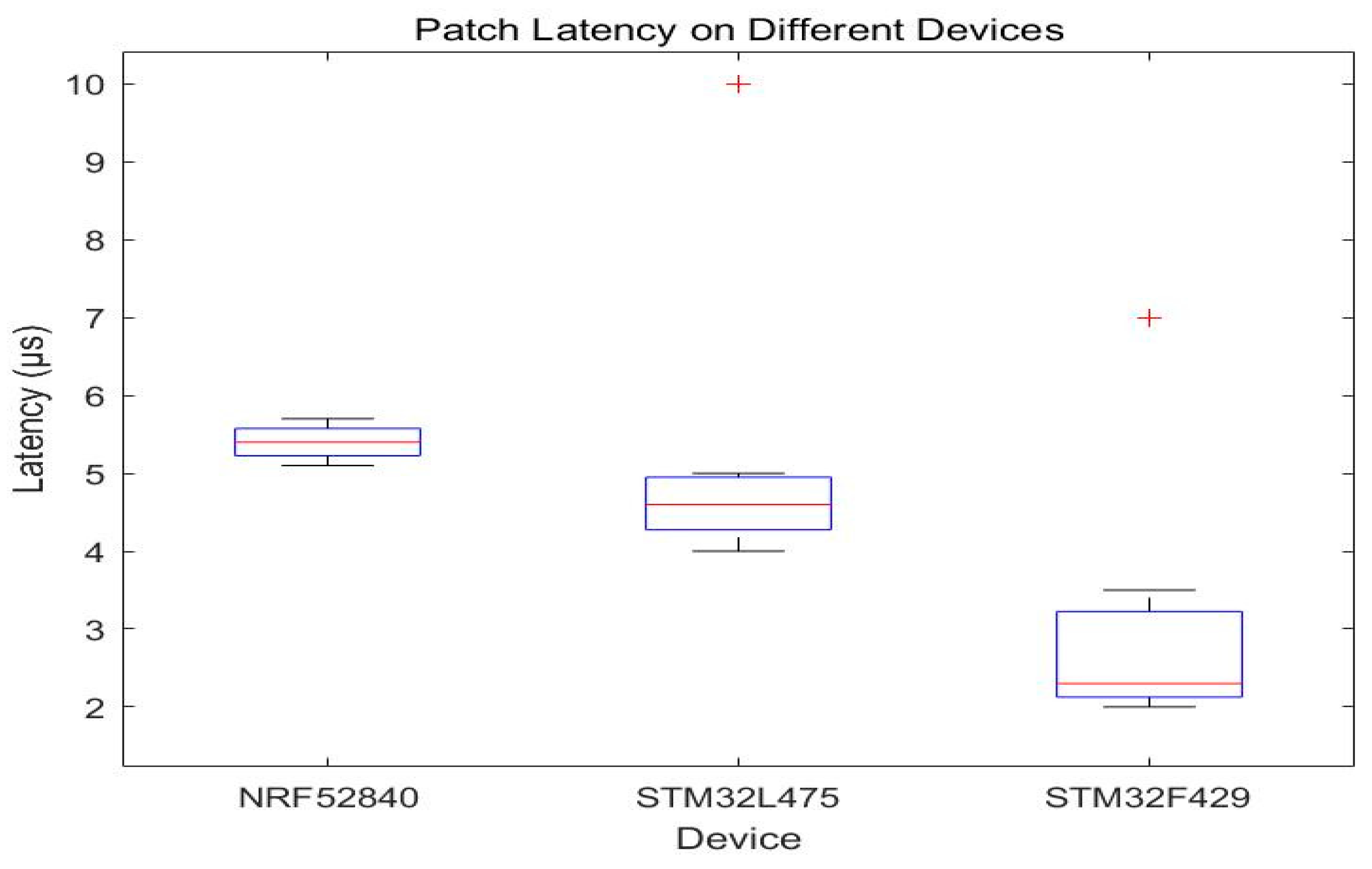

4.3.6. Patch Delay Experiments with Different Devices and Analysis of Results

4.3.7. Comparison with State-of-the-Art Methods

- HERA, which targets embedded real-time systems via hardware-assisted patching;

- RapidPatch, a high-speed eBPF-based hot patch generator for firmware.

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Bhattacharjya, A.; Kozdroj, K.; Bazydlo, G.; Wisniewski, R. Trusted and Secure Blockchain-Based Architecture for Internet-of-Medical-Things. Electronics 2022, 11, 2560. [Google Scholar] [CrossRef]

- Jeong, H.; Baik, J.; Kang, K. Functional level hot-patching platform for executable and linkable format binaries. In Proceedings of the 2017 IEEE International Conference on Systems, Man, and Cybernetics (SMC), Banff, AB, Canada, 5–8 October 2017; pp. 489–494. [Google Scholar]

- Bhattacharjya, A.; Zhong, X.; Xing, L. Secure Hybrid RSA (SHRSA) based multilayered authenticated, efficient and End to End secure 6-layered personal messaging communication protocol. In Digital Twin Technologies and Smart Cities, Internet of Things (IoT); Springer Nature: Cham, Switzerland, 2020; Available online: https://www.springer.com/gb/book/9783030187316#aboutBook (accessed on 20 April 2025).

- Ziems, N.; Wu, S. Security vulnerability detection using deep learning natural language processing. In Proceedings of the IEEE INFOCOM 2021—IEEE Conference on Computer Communications Workshops (INFOCOM WKSHPS), Vancouver, BC, Canada, 10–13 May 2021; pp. 1–6. [Google Scholar]

- Nweke, L.O. A survey of specification-based intrusion detection techniques for cyber-physical systems. Int. J. Adv. Comput. Sci. Appl. 2021, 5. [Google Scholar] [CrossRef]

- Cai, W.; Chen, J.; Yu, J.; Gao, L. A software vulnerability detection method based on deep learning with complex network analysis and subgraph partition. Inf. Softw. Technol. 2023, 164, 107328. [Google Scholar] [CrossRef]

- Gu, H.; Shang, J.; Wang, P.; Mi, J.; Bhattacharjya, A. A Secure Protocol Authentication Method Based on the Strand Space Model for Blockchain-Based Industrial Internet of Things. Symmetry 2024, 16, 851. [Google Scholar] [CrossRef]

- Kumar, J.R.H.; Bhargavramu, N.; Durga, L.S.N.; Nimmagadda, D.; Bhattacharjya, A. Blockchain Based Traceability in Computer Peripherals in Universities Scenarios. In Proceedings of the 2023 3rd International Conference on Electronic and Electrical Engineering and Intelligent System (ICE3IS), Yogyakarta, Indonesia, 9–10 August 2023. [Google Scholar]

- Bhattacharjya, A.; Xiaofeng, Z.; Jing, W. An end-to-end user two-way authenticated double encrypted messaging scheme based on hybrid RSA for the future internet architectures. Int. J. Inf. Comput. Secur. 2018, 10, 63–79. [Google Scholar] [CrossRef]

- Bhattacharjya, A.; Xiaofeng, Z.; Jing, W.; Xing, L. Hybrid RSA-based highly efficient, reliable and strong personal full mesh networked messaging scheme. Int. J. Inf. Comput. Secur. 2018, 10, 418–436. [Google Scholar] [CrossRef]

- Bhattacharjya, A.; Xiaofeng, Z.; Jing, W.; Xing, L. On mapping of address and port using translation. Int. J. Inf. Comput. Secur. 2019, 11, 214–232. [Google Scholar] [CrossRef]

- Zhang, Z.; Wang, X.; Hao, Q.; Xu, D.; Wang, J.; Liu, J.; Ma, J.; Zhang, J. Hardware-Implemented Security Processing Unit for Program Execution Monitoring and Instruction Fault Self-Repairing on Embedded Systems. Appl. Sci. 2022, 12, 3584. [Google Scholar] [CrossRef]

- Li, Z.; Wang, P.; Wang, Z. FlowGANAnomaly: Flow-based anomaly network intrusion detection with adversarial learning. Chin. J. Electron. 2024, 33, 58–71. [Google Scholar] [CrossRef]

- Wang, Z.; Li, Z.; Fu, M.; Ye, Y.; Wang, P. Network traffic classification based on federated semi-supervised learning. J. Syst. Archit. 2024, 149, 103091. [Google Scholar] [CrossRef]

- Li, Z.; Zhang, Z.; Fu, M.; Wang, P. A novel network flow feature scaling method based on cloud-edge collaboration. In Proceedings of the 2023 IEEE 22nd International Conference on Trust, Security and Privacy in Computing and Communications (TrustCom), Exeter, UK, 1–3 November 2023; pp. 1947–1953. [Google Scholar]

- Niesler, C.; Surminski, S.; Davi, L. HERA: Hotpatching of Embedded Real-time Applications. In Proceedings of the Network and Distributed Systems Security (NDSS) Symposium 2021, Virtual, 21–25 February 2021; pp. 21–25. [Google Scholar]

- Li, Z.; Liu, M.; Wang, P.; Su, W.; Chang, T.; Chen, X.; Zhou, X. Multi-ARCL: Multimodal Adaptive Relay-Based Distributed Continual Learning for Encrypted Traffic Classification. J. Parallel Distrib. Comput. 2025, 201, 105083. [Google Scholar] [CrossRef]

- Payer, M.; Bluntschli, B.; Gross, T.R. DynSec: On-the-fly Code Rewriting and Repair. In Proceedings of the 5th Workshop on Hot Topics in Software Upgrades (HotSWUp 13), San Jose, CA, USA, 24–28 June 2013. [Google Scholar]

- Holmbacka, S.; Lund, W.; Lafond, S.; Lilius, J. Lightweight Framework for Runtime Updating of C-Based Software in Embedded Systems. In Proceedings of the 5th Workshop on Hot Topics in Software Upgrades (HotSWUp 13), San Jose, CA, USA, 24–28 June 2013. [Google Scholar]

- Jiang, W.; Liu, L. Research on hot-patching technology based on VXWORKS system. Comput. Technol. Dev. 2017, 27, 18–22+28. [Google Scholar]

- Zhou, M.; Wang, H.; Li, K.; Zhu, H.; Sun, L. Save the Bruised Striver: A Reliable Live Patching Framework for Protecting Real-World PLCs. In Proceedings of the EuroSys’24: The Nineteenth European Conference on Computer Systems, Athens, Greece, 22–25 April 2024; pp. 1192–1207. [Google Scholar]

- Ye, H.; Gu, J.; Martinez, M.; Durieux, T.; Monperrus, M. Automated classification of overfitting patches with statically extracted code features. IEEE Trans. Softw. Eng. 2021, 48, 2920–2938. [Google Scholar] [CrossRef]

- Wang, M. Exploration and application of remote hot deployment based on SpringBoot. Inf. Comput. 2023, 35, 1–4. [Google Scholar]

- Xiong, Y.; Liu, X.; Zeng, M.; Zhang, L.; Huang, G. Identifying patch correctness in test-based program repair. In Proceedings of the 40th International Conference on Software Engineering, Gothenburg, Sweden, 27 May–3 June 2018; pp. 789–799. [Google Scholar]

- He, Y.; Zou, Z.; Sun, K.; Liu, Z.; Xu, K.; Wang, Q.; Shen, C.; Wang, Z.; Li, Q. RapidPatch: Firmware Hotpatching for Real-Time Embedded Devices. In Proceedings of the 31st USENIX Security Symposium, Boston, MA, USA, 10–12 August 2022; pp. 10–12. [Google Scholar]

- Ramaswamy, A.; Bratus, S.; Smith, S.W.; Locasto, M.E. Katana: A Hot Patching Framework for ELF Executables. In Proceedings of the 2010 International Conference on Availability, Reliability and Security, Krakow, Poland, 15–18 February 2010; pp. 507–512. [Google Scholar]

- Naeem, H.; Alsirhani, A.; Alserhani, F.M.; Ullah, F.; Krejcar, O. Augmenting Internet of Medical Things Security: Deep ensemble integration and methodological fusion. Comput. Model. Eng. Sci. 2024, 141, 2185–2223. [Google Scholar] [CrossRef]

- Chen, H.; Chen, R.; Zhang, F.; Zang, B.; Yew, P.-C. Live updating operating systems using virtualization. In Proceedings of the VEE06: Second International Conference on Virtual Execution Environments, Ottawa, ON, Canada, 14–16 June 2006. [Google Scholar]

- Altekar, G.; Bagrak, I.; Burstein, P.; Schultz, A. OPUS: Online Patches and Updates for Security. In Proceedings of the 14th USENIX Security Symposium, Baltimore, MD, USA, 31 July–5 August 2005. [Google Scholar]

- Zhu, Z.; Chen, H.; Zhang, J.; Wang, X.; Jin, Z.; Xue, M.; Zhu, D.; Choo, K.K.R. MFABA: A More Faithful and Accelerated Boundary-Based Attribution Method for Deep Neural Networks. In Proceedings of the Thirty-Eighth AAAI Conference on Artificial Intelligence, Vancouver, BC, Canada, 20–27 February 2024; Volume 38, pp. 17228–17236. [Google Scholar]

- Zhang, J.; Ling, X.; Wang, Y. Design of a generic framework for assembly engineering for ARM Cortex-M series cores. Small Microcomput. Syst. 2021, 42, 2440–2445. [Google Scholar]

- Mao, Y.; Migliore, V.; Nicomette, V. MATANA: A Reconfigurable Framework for Runtime Attack Detection Based on the Analysis of Microarchitectural Signals. Appl. Sci. 2022, 12, 1452. [Google Scholar] [CrossRef]

- Zhu, Z.; Jin, Z.; Wang, X.; Zhang, J.; Chen, H.; Choo, K.-K.R. Rethinking Transferable Adversarial Attacks with Double Adversarial Neuron Attribution. IEEE Trans. Artif. Intell. 2024, 6, 354–364. [Google Scholar] [CrossRef]

- Dong, Y.; Guo, W.; Chen, Y.; Zhang, Y.; Wang, G. Towards the Detection of Inconsistencies in Public Security Vulnerability Reports. In Proceedings of the 28th USENIX Security Symposium, Santa Clara, CA, USA, 14–16 August 2019. [Google Scholar]

- Shi, J.; Wang, Y.; Su, Y.; Chen, S. Analysis of MQX interrupt mechanism and interrupt program framework design based on ARM Cortex-M4. Comput. Sci. 2013, 40, 41–44. [Google Scholar]

- Zhou, C. Design and Implementation of Server/Client Based Patch Management System. Microcomput. Appl. 2009, 30, 53–57. [Google Scholar]

- Correa, R.; Bermejo Higuera, J.R.; Higuera, J.B.; Sicilia Montalvo, J.A.; Rubio, M.S.; Magreñán, Á.A. Hybrid security assessment methodology for web applications. Comput. Model. Eng. Sci. 2021, 126, 89–124. [Google Scholar]

| Categories | Name | Description |

|---|---|---|

| Hardware | Multiprocessor | Intel Core i7-10870H |

| GPUs | NVIDIA GeForce RTX 3060 | |

| Random access memory (RAM) | 16 GB DDR4 | |

| Software | Development and operating environments | Ubuntu 20.04 LTS |

| Integrated development environment (IDE) | Eclipse IDE 2021-09 | |

| Programming language | C, C++ | |

| Debugging Tools version | GDB 10.1 Git 2.25.1 | |

| Control network tool | Wireshark 3.4.8 | |

| Traffic Tools | Scapy 2.4.5 | |

| Virtualized environment | VMware Workstation Pro |

| Vulnerability ID | Subassemblies | Description | (Machine) Filter |

|---|---|---|---|

| 2020-17441 | PicoTCP | Validate lPv6 payload length field against actual size for function pico ipv6 processp!Validate | Filter Patch |

| 2020-17442 | PicoTCP | Hop-by-hop lPv6 extension header length field for function | Filter Patch |

| 2020-17443 | PicoTCP | pico ipv6 process restricts that echo->transport len is no less than 8 inpico_icmp6_send.echoreply | Filter Patch |

| 2020-17444 | PicoTCP | Check possible overflow of header extension length field forpico_ipv6_check headers._.sequence | Filter Patch |

| 2020-17445 | PicoTCP | Validate optlen using a loop prior to function pico ipv6_process_destopt | Filter Patch |

| Method | Fixing Time (ms) | Success Rate (%) | Memory Overhead (KB) | Platform Dependency |

|---|---|---|---|---|

| HERA | 21.4 | 95.2 | 5.6 | Cortex-M only |

| RapidPatch | 42.7 | 97.4 | 8.1 | x86/eBPF Required |

| Proposed method | 15.2 | 98.7 | 3.1 | Generic (ARMv7-M) |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Xi, Z.; Zhang, B.; Bhattacharjya, A.; Wang, Y.; He, C. Research on a Secure and Reliable Runtime Patching Method for Cyber–Physical Systems and Internet of Things Devices. Symmetry 2025, 17, 983. https://doi.org/10.3390/sym17070983

Xi Z, Zhang B, Bhattacharjya A, Wang Y, He C. Research on a Secure and Reliable Runtime Patching Method for Cyber–Physical Systems and Internet of Things Devices. Symmetry. 2025; 17(7):983. https://doi.org/10.3390/sym17070983

Chicago/Turabian StyleXi, Zesheng, Bo Zhang, Aniruddha Bhattacharjya, Yunfan Wang, and Chuan He. 2025. "Research on a Secure and Reliable Runtime Patching Method for Cyber–Physical Systems and Internet of Things Devices" Symmetry 17, no. 7: 983. https://doi.org/10.3390/sym17070983

APA StyleXi, Z., Zhang, B., Bhattacharjya, A., Wang, Y., & He, C. (2025). Research on a Secure and Reliable Runtime Patching Method for Cyber–Physical Systems and Internet of Things Devices. Symmetry, 17(7), 983. https://doi.org/10.3390/sym17070983