Abstract

The continued downscaling of transistors has exacerbated aging mechanisms such as bias temperature instability (BTI) and hot-carrier injection (HCI), posing significant reliability challenges for nanoscale integrated circuits. These effects are particularly critical to flip-flops operating at low supply voltages, which are essential for ultra-low-power applications including the Internet of Things (IoT) and biomedical implants. In this work, we address the aging issue in low-voltage Split-Controlled Flip-Flops (SCFFs) by proposing a novel transistor-level mitigation technique specifically tailored to this architecture within a domestic 14 nm process library. Through a detailed analysis of aging-critical transistors, three targeted enhancement strategies are introduced. Simulation results demonstrate that the improved SCFF achieves more than a 60% reduction in PMOS threshold voltage degradation and a 40% reduction in timing delay, while maintaining robust operation at a supply voltage as low as 0.4 V. These results highlight the effectiveness of the proposed approach in mitigating aging effects and enhancing reliability under low-voltage operation.

1. Introduction

With the continuous advancement of semiconductor process technology, transistor feature sizes have progressively scaled down toward physical limits. This miniaturization offers significant advantages, including enhanced switching speed, improved data processing capability, and reduced power consumption. However, as technology nodes shrink, aging effects such as bias temperature instability (BTI) and hot-carrier injection (HCI) have become critical reliability concerns [1]. These mechanisms cause threshold voltage (Vth) shifts, mobility degradation, and timing failures, particularly in ultra-low-voltage circuits where timing margins are inherently limited [2,3].

Driven by stringent power constraints and long-term reliability requirements, low-voltage flip-flops are increasingly adopted in a wide range of applications, including IoT sensor nodes, smart labels, environmental monitoring chips for edge intelligence, and implantable medical devices in biomedical electronics. Among various designs, the split-controlled flip-flop (SCFF) is particularly attractive for ultra-low-power scenarios due to its ultra-low power consumption, wide voltage adaptability, and non-redundant switching characteristics [4]. However, aging effects in flip-flops are significantly aggravated under low-voltage conditions. In low-voltage design, circuit speed decreases and initial timing margins become extremely limited. The additional delay introduced by aging mechanisms can therefore easily cause timing violations during data sampling and latching, leading to functional failures. Meanwhile, the reduced signal swing at low voltages increases susceptibility to noise, and aging-induced performance degradation further amplifies this sensitivity, substantially raising the risk of erroneous operation. Moreover, PMOS transistors in SCFFs in the feedback loop are subject to prolonged stress during normal operation and thus face severe aging risks dominated by negative bias temperature instability (NBTI) [5,6,7,8]. Consequently, reliability enhancement through transistor sizing optimization, structural modification, or process-level improvements becomes essential.

Previous studies have extensively investigated aging phenomena in conventional flip-flop architectures. For example, a comparative analysis framework was proposed to evaluate aging effects across four representative flip-flop structures implemented in both CMOS and FinFET technologies, revealing critical reliability trade-offs [9]. BTI-induced degradation in nanoscale CMOS flip-flops has also been comprehensively assessed to evaluate the impact on key timing parameters such as setup time, hold time, and clock-to-output delay [10]. Furthermore, a dual-threshold voltage design technique has been introduced to mitigate aging-related performance degradation [11].

To date, most existing anti-aging techniques focus on classical flip-flop architectures, which; however, often fail to meet the demands of modern ultra-low-power applications due to intrinsic performance limitations. As a result, recent research on trigger circuits has increasingly emphasized low power consumption and robustness against performance variations, particularly under low-voltage operation [12,13]. The SCFF has been studied as a promising candidate due to its inherent energy efficiency and wide voltage operating range. Nevertheless, achieving ultra-low-voltage operation typically requires applying reverse body bias to lower the effective Vth, introducing additional design complexity and further exposing the circuit to accelerated aging during long-term operation [14]. To date, effective aging mitigation strategies are still not fully explored, especially designs specifically tailored for SCFFs [15,16].

Here, in this work, we focus on enhancing SCFF reliability through transistor-level optimization and structural improvements. In the proposed approach, the SCFF operates over an ultra-wide dynamic voltage range to minimize power consumption. Aging effects induced by HCI are alleviated by shortening the channel length of transistors on critical paths, while key aging-sensitive devices are identified through a detailed structural analysis of BTI- and HCI-induced degradation. By restructuring the flip-flop topology, the effective stress time of critical transistors is significantly reduced, particularly those in the feedback loop. As a result, aging-induced threats such as Vth drift and increased leakage current are effectively mitigated. Under a domestic 14 nm process, simulation and stress test results demonstrate that the degradation rate of key timing parameters is reduced by more than 50%, with modest and controllable power and area overheads. Moreover, the optimized SCFF maintains stable operation under high-frequency stress conditions, meeting the stringent requirements of long-lifetime ultra-low-power applications.

2. Aging Effect in SCFF

The SCFF, while designed for low-voltage operation, exhibits pronounced sensitivity to aging. The scaling of transistor dimensions raises serious aging concerns for flip-flop stability and long-term reliability. Among various degradation contributors, BTI and HCI are the most significant aging mechanisms [17]. Their effects are so pronounced that they profoundly influence the system-level performance and power. Effects like BTI and HCI cause performance loss that is severely magnified at low voltages, where timing margins are paramount. Such margins are fundamental to reliability, ensuring signals settle within the clock’s required window. Therefore, a detailed analysis of the SCFF key timing parameters and the dominant aging mechanisms (BTI/HCI) is necessary to pinpoint the critical factors for improvement, which is the focus of the following sections.

2.1. Timing Metrics of SCFF

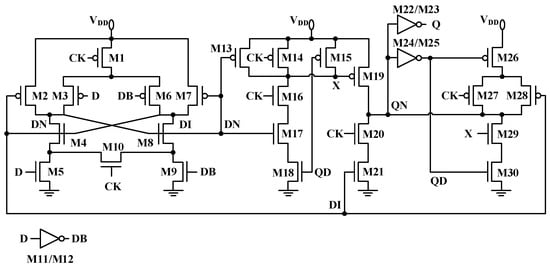

This study enhances the aging mitigation capability of the SCFF [4]. The proposed design enables ultra-wide dynamic voltage scaling while reducing both active and leakage power. As shown in Figure 1, transistors M1–M10 form the master latch with a differential structure, while M13–M30 constitute the slave latch, implementing split control functionality. The differential architecture enhances signal stability under ultra-low-voltage conditions, and the slave latch’s split control mechanism optimizes timing response, ensuring reliable SCFF operation in ultra-low-voltage scenarios.

Figure 1.

Schematic of the SCFF structure.

The optimized SCFF maintains a low-power-delay product across process corners and supply voltages. Regarding the timing operation, when the input D is high and the clock is low, the master latch becomes transparent, allowing the signal to propagate to node DN, while the slave latch is cut-off. Conversely, when D remains high and CLK transitions high, the data are transferred from DN to the output Q. A feedback loop subsequently maintains the low value at DN, thereby preventing signal crosstalk or errors.

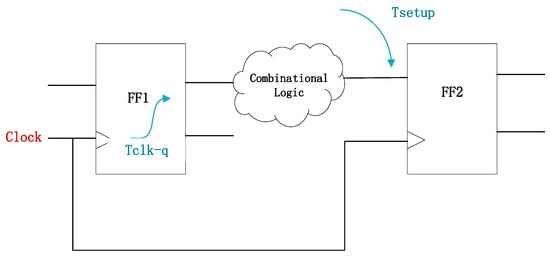

Flip-flops are widely used in pipelined architectures, and their timing characteristics typically determine the maximum operating frequency [18]. Therefore, to evaluate the effectiveness of the SCFF aging optimization, it is essential to measure key timing parameters, including setup time (tsetup), hold time (thold), clock-to-output delay (tcq), input-to-output delay of the master latch, and the overall input-to-output delay of the SCFF. These parameters significantly impact data transmission efficiency and pipeline stability. When the aging duration exceeds a critical threshold, the accumulated delay impairs the circuit ability to accurately sample data, leading to potential functional errors.

Before implementing aging optimization, flip-flop timing metrics must be defined as evaluation criteria. When analyzing flip-flop timing delays, these parameters must be thoroughly considered to ensure long-term reliable operation. To guarantee the correct functionality of digital circuits, flip-flops impose strict timing constraints on input data. The setup time requires data to remain stable before the arrival of the clock edge [19], while the hold time mandates data stability after the clock edge, as shown in Figure 2. These constraints, especially the clock-to-output delay (tcq), require rigorous verification during digital design. If aging causes tsetup to exceed the allowable clock cycle range, data sampling errors may occur. The correction of timing violations in digital circuit design commonly employs techniques such as buffer insertion or an increase in the local supply voltage. However, these measures introduce additional capacitive loads and switching activity, ultimately increasing dynamic power consumption [20]. Therefore, strict timing adherence is essential to prevent violations and data corruption in pipelined processors and high-speed interfaces.

Figure 2.

Illustration of the timing constraints for the flip-flop.

Failure to effectively mitigate transistor aging can lead to aging-induced circuit failures. Common failure modes in digital circuits, such as metastability and timing violations, are critical factors that severely degrade system timing performance. Transistor aging degrades the timing performance of flip-flops and considerably elevates overall power consumption. This increase in power consumption manifests in two ways: on the one hand, static power rises due to elevated leakage currents; on the other hand, switching power is augmented as a result of threshold voltage drift. The dynamic power consumption in flip-flops arises mainly from the switching activity that charges and discharges parasitic capacitance. This power can be modeled by the formula P = C × V2 × f, where C is the load capacitance, V is the supply voltage, and f is the switching frequency.

Specifically, increased Vth reduces drain–source current (Ids), prolonging the capacitance charging and discharging time. To ensure the flip-flop completes state transitions within clock constraints, a higher drive voltage or relaxed timing constraints may be required. Such an operation will directly increase the V2 term in the power formula, leading to higher dynamic power consumption. For high-speed flip-flops, Vth drift reduces switching efficiency, increasing energy consumption per unit time.

Moreover, NBTI and HCI asymmetrically affect PMOS and NMOS transistors: NBTI primarily degrades PMOS, while HCI predominantly impacts NMOS. This disrupts the balance between rising edge and falling edge switching speeds. During state transitions, the charging and discharging transition times, specifically the rise and fall times of internal nodes such as the outputs of the master and slave latches, are prolonged.

Extended transition times contribute to two key power-related issues. One primary effect of prolonged transition times is an increased duration of short-circuit current flowing between the power supply and ground during switching. Although typically a minor component of dynamic power, the cumulative effect of this current under high-frequency operation significantly increases total power consumption. Moreover, slower signal transitions can lead to timing misalignment with adjacent logic blocks. This may induce redundant signal transitions, such as glitches, thereby further elevating dynamic power consumption.

2.2. BTI-Induced Aging Mechanism

Bias Temperature Instability, particularly NBTI in PMOS transistors, poses a critical reliability challenge [21]. This phenomenon significantly contributes to flip-flop aging and fundamentally limits the long-term stability of SCFFs. The emergence of this degradation mechanism can be attributed to two primary technological drivers. On the one hand, it is primarily attributed to the aggressive scaling of MOS device dimensions. On the other hand, it results from sustained operational demands in flip-flop circuits. These factors collectively induce elevated transistor temperatures during operation, which accelerates the dissociation of Si-H bonds at the Si/SiO2 interface. Consequently, the release and subsequent drift of hydrogen species toward the gate dielectric generate interface traps and oxide charges, ultimately resulting in a progressive shift in the threshold voltage of MOS devices.

BTI degradation and temperature rise are mutually reinforcing. High temperatures accelerate the breaking of Si-H bonds and the diffusion of hydrogen species, exacerbating the BTI effect. The higher the temperature, the faster the BTI degradation rate. When the transistor is in the on-state, also known as the stress phase, its threshold voltage experiences a continuous increase. However, this shift is reversible, and recovery begins once the gate voltage is removed. NBTI significantly influences transistor aging by causing performance degradation under negative gate bias. Thus, reducing the stress time of PMOS without affecting performance is crucial.

The reaction–diffusion model explains the physical mechanism of BTI through chemical reaction and diffusion processes [22]. Specifically, it accounts for the generation of interface defects and the consequent threshold voltage drift observed in NBTI. Although the interpretation of the reaction–diffusion model is very accurate, its computational complexity is relatively high. In this paper, the QSA formula is used to analyze the influencing factors of threshold voltage shift caused by the BTI effect. The QSA formula simplifies complex physical formulas by introducing empirical parameters and simplifying assumptions, as shown as Equation (1) [23]:

where A is a process-dependent scale factor reflecting gate dielectric quality, interface properties, and material characteristics; is the gate–source voltage (bias voltage); is the initial threshold voltage; t is the stress time; and describes the temperature acceleration effect. High bias voltage enhances the gate electric field, accelerating interface state defect generation and charge trapping. The acceleration effect of bias voltage on BTI effect is described by these terms. High temperature significantly increases the formation rate of interfacial defects. From this formula, it is evident that under constant technology and temperature conditions, reducing transistor stress time can mitigate BTI-induced threshold voltage increase. Therefore, by modifying the feedback circuit structure in the master–slave latch, the conduction time of transistors that are subjected to prolonged stress can be reduced. By modifying the circuit structure, reducing the value of the stress time t in Equation (1) is an effective way to alleviate aging effects.

2.3. HCI Impact on Critical Transistors

Unlike BTI, HCI poses a more severe long-term reliability challenge due to its irreversible degradation mechanism. The permanent nature of HCI-induced damage leads to cumulative parametric shifts that exceed design margins, ultimately causing premature circuit failure. This phenomenon is particularly critical in advanced nodes.

The HCI mechanism begins when high-energy carriers, such as electrons or holes, are injected into the gate dielectric. This process generates interface state defects and charge trapping. With shrinking transistor channel lengths and increasing operating frequencies, HCI also affects threshold voltage drift. The impact of HCI-induced threshold voltage drift can be analyzed by Equation (2) [24]:

where represents the weighting coefficient of gate current and channel hot-carrier injection in this effect. It means that the degradation in HCI can be caused by gate current when = 1 or by channel hot-carrier injection when = 0. and represent the normalization of the electric field intensities for the gate region and the drain region, respectively; , , and describe the gate current, drain current, and base current, respectively. represents the time index, indicating that the threshold drift increases exponentially with stress time; and m represent the index factors, indicating the current acceleration effect indices of the gate current mechanism and the drain region mechanism, respectively; t is the stress time, and W represents the device width.

As the temperature rises, and will also increase accordingly. In addition, will also experience increased defect formation and migration due to the elevated temperature. The final result is that the threshold drift rate will significantly increase, and the influence of the HCI effect on device lifespan becomes more sensitive under high-temperature conditions.

3. Anti-Aging Strategies

3.1. Critical Transistors Affecting Aging

Before optimization, transistor aging state can be simulated by increasing the gate voltage, primarily for PMOS transistors. Simulations were performed using PMOS transistors with a drawn gate length of 16 nm and a poly finger width of 922 nm, resulting in a transistor width-to-length ratio of 57.625. As shown in Table 1, for flip-flop transistors, voltage values equivalent to ten years of aging are applied to all PMOS transistors to account for threshold voltage shifts. After applying the aging-induced voltage offsets to the gates of all PMOS transistors, each PMOS transistor in the master–slave circuit is analyzed individually by removing the previously applied voltage values. This allows for a precise simulation of the delay effect of a single transistor on the overall performance of the flip-flop.

Table 1.

Measured aging delay distribution across PMOS devices in the SCFF.

To identify which transistors are most critical to circuit aging, a method based on comparative delay analysis is employed. This is achieved by comparing the circuit delay after individually shifting each transistor’s Vth with the baseline delay obtained from the simultaneous aging of all transistors. Transistors whose individual aging-induced delay closely approximates the full-circuit aging delay are identified as significant contributors.

Using this method, three key timing parameters were analyzed following the removal of gate voltage shifts from individual PMOS transistors: the clock-to-output delay, the data-to-complementary-data-node delay, and the data-to-output delay. This analysis identified M3 and M6 as having a significant impact on main latch performance degradation.

3.2. Reducing the BTI Effect Through Structural Modification

Changes in transistor structure mainly affect the BTI effect, and the impact on PMOS transistors is much greater than that on NMOS transistors. Therefore, before structural improvement, aging was simulated by increasing the PMOS gate threshold voltage (ΔVth). After simulated aging, key timing parameters (D-DN delay, CLK-Q delay, and D-Q delay) were compared.

Before improving the circuit structure, it is first necessary to identify the PMOS transistor that has the most significant impact on the circuit, as determined in the previous section. Additionally, during the circuit analysis process, a recovery loop with an excessively long stress time was identified. By modifying the circuit structure, stress time along the critical path can be reduced. According to the QSA formula, reducing PMOS conduction time is the most effective strategy for mitigating BTI-induced aging.

The primary goal of structural modification is to minimize PMOS stress time without compromising flip-flop functionality. In master–slave flip-flops, the feedforward path typically serves as the data transmission route from input to master output, and from flip-flop input to slave output. Thus, structural improvements aimed at reducing PMOS stress time along the critical path have limited effectiveness in such configurations.

3.2.1. Optimization of Sensitive PMOS Transistor Conduction Time

In the conventional SCFF main latch structure, PMOS transistors suffer from non-essential conduction. For example, M3 remains on when CLK = 1 and D = 0, leading to prolonged NBTI stress accumulation. Consequently, Vthp exhibits a forward drift of 23.2764 mV, contributing 64.5% of the total degradation. Due to persistent conduction, the stress duration of M3 accounts for 50% of the operational time, significantly accelerating aging.

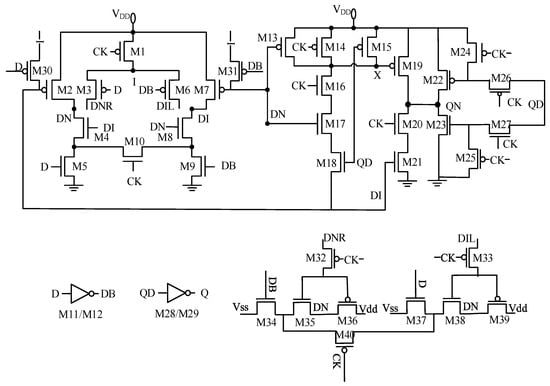

Conditional conduction of M3/M6 is achieved by introducing a bridge transistor network to reconstruct the main latch data path. Adding a clock-controlled bridge transistor between DNR/DN and DIL/DI paths enables logical decoupling, allowing M3 to be on only when CLK = 0 and D = 0, and M6 to be on only when CLK = 0 and D = 1. When CLK = 1, the bridge transistor conducts, maintaining the static pull-down state of DI/DN to prevent data loss. The ΔVthp of M3 decreased from 23.2764 mV to 5.007 mV, with an improvement rate of 78.5%. The conduction time ratio dropped from 50% to 25%, and the D-DN rising edge delay decreased from 21.788 ps to 20.425 ps. Power consumption increased by 8%, while the area increased by only 4%.

Aging was simulated by increasing threshold voltage degradation at each PMOS gate. M3 and M6 were identified as having a significant impact on circuit aging. In the original circuit, M3 and M6 conduct unnecessarily when CLK = 1 (DN = 1, D = 0). Bridge transistors were added between DNR/DN and DIL/DI to ensure that M3/M6 conduct only when CLK = 0 (D = 0 → M3 on, D = 1 → M6 on). Simulation shows that the M3 conduction time decreased from 50% to 25%, and ΔVth degradation decreased from 23.2764 mV to 5.007 mV (a 78% reduction).

3.2.2. Reconstruction of the Data Recovery Loop of the Main Latch

From the SCFF topology, it can be observed that to achieve low power consumption, the holding circuit and forward circuit of the main flip-flop share transistors M4, M5, M8, and M9. If the aforementioned circuit structure is directly modified, there is a potential risk of affecting the circuit functionality to some extent. Therefore, in the proposed modification strategy, the feedback loop containing transistors M2 and M7 was selected for modification.

Transistors M2 and M7 are connected in series in the pull-down network. The gate of M2 is controlled by the DI signal, while M7 is controlled by DN. Consequently, when input data is 0, M2 remains continuously on; similarly, when input data is 1, M7 remains on. For the entire main latch, regardless of the input data value, one PMOS transistor in the recovery loop is always conductive. As shown in Equation (1), when the flip-flop stores data with equal probability, BTI degradation can be mitigated by reducing the conduction probability of M2 and M7 to 0.5.

In the original circuit, delayed signals DI and DN control M2 and M7, resulting in prolonged conduction time. When the clock signal is low, DI and DN are generated by D and DB signals conducting through the pull-up network, introducing additional conduction time due to propagation delay. To minimize unnecessary conduction time, M2 and M7 gate signals can be replaced with direct D and DB inputs, eliminating delay-induced conduction. Additionally, a PMOS transistor controlled by the clock signal must be inserted in series with the pulse clock transistor to ensure turn-off when the clock signal is high.

Separately inserting a PMOS transistor for M2 and M7 would significantly increase power consumption and introduce additional delay. Therefore, the existing PMOS transistor whose gate is controlled by CLK is shared to enable logical control of the CLK signal over the conduction time of M2 and M7.

Thus, the structural improvement for the main flip-flop is as follows: the gates of M2 and M7 are directly controlled by the input signals D and DB, respectively, while sharing the original PMOS transistor controlled by CLK. This configuration allows M2 to be off when CLK = 0 and D = 0, and M7 to be off when CLK = 0 and D = 1. After optimization, redundant switching of PMOS transistors is reduced, leading to lower dynamic power consumption and a decreased aging rate.

3.2.3. Stress Dispersion Design of the Slave Latch

The slave latch (M13–M30) achieves low power consumption through split control, with the critical path being D → DN → QN → Q. M24 to M30 are used as feedback loops for data storage. When analyzing the slave latch recovery circuit structure, it was found that the gates of M26 and M30 in the original circuit were driven by QD. M26 and M30 are two transistors in the feedback loop of the slave latch. When CLK is low, the input signal D passes through the main latch to the slave latch section, and M26 and M30 are in the conducting state as part of the feedback loop. When CLK is high, the slave latch transmits the data from the main latch to the output signal Q. During this time, the feedback loop is not conducting. However, transistors M26 and M30 are driven by the signal QD and were originally stressed for 50% of the cycle, equivalent to one half-cycle of the clock. From the QSA formula, the α coefficient is 0.5. This increases the time that the transistors are in the stress state and exacerbates the aging effects. Similarly, to reduce conduction time, operations similar to Improvement 2 are needed. The circuit structure needs to be modified so that when CLK = 1, the time that the feedback loop is in the stress state is reduced. The gates of M26/M30 can be connected in series with a pulse clock-controlled transistor to achieve turn-off when CLK = 1. The improved feedback circuit of the slave latch comprises transistors M22 to M27. When CLK = 1, transistor M23 is in the cut-off state. When QD = 1, since M24 and M26 are not conducting, M22 is also in the cut-off state; the same applies when QD = 0. When CLK = 0, the feedback loop conducts normally, and the output Q remains stable.

The recovery circuit was modified to ensure that M26 and M30 conduct only when CLK is low and QD changes, thereby reducing their stress time to 25% of the cycle. Furthermore, an NMOS pull-down path was added to guarantee a static shutdown during the high phase of the clock. As a result, the threshold voltage degradation of M27 decreased from 22.379 mV to 17.124 mV, and the contribution of hot-carrier injection to this degradation dropped from 62.8% to 10.2%. The circuit diagrams after optimization are shown in Figure 3.

Figure 3.

Circuit diagram after structural optimization.

3.3. Transistor-Level Structure Reconfiguration

Notable differences exist in aging mechanisms between PMOS and NMOS transistors. For PMOS devices, the dominant aging mechanism is NBTI-induced positive threshold voltage shift, occurring under negative gate bias and high temperatures and following a time-dependent power-law model. For NMOS devices, HCI is the primary aging mechanism, becoming significant under high-frequency switching or high drain voltage conditions, with degradation proportional to channel current density.

As discussed previously, circuit-level structural optimizations mitigate BTI-induced aging. In SCFFs, while BTI is a major aging factor, HCI also has a considerable influence. Specifically, HCI in NMOS transistors (e.g., M5 in the clock path) under high drain voltage conditions causes forward Vth shift, increasing the Clk-q delay.

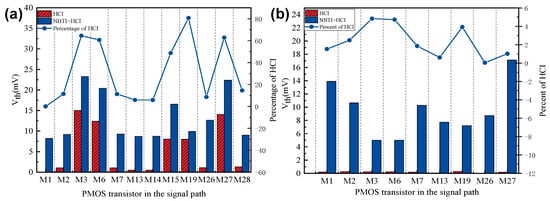

However, the degradation in PMOS transistors is an order of magnitude higher than that in NMOS transistors in the SCFF circuit. Therefore, our research focuses on HCI-sensitive PMOS transistors rather than NMOS transistors. In the simulation, the aging delay of PMOS transistors with the mentioned structure improvement was analyzed, and the proportion of the HCI effect in the overall Vth degradation was calculated. By analyzing the ratio of HCI-induced threshold voltage shift to total variation, as shown in Figure 4a, it is observed that the HCI trap density in M19 and M27 (in the latch feedback path) increases significantly under high-frequency clock stress. HCI-induced degradation exceeds 80%, indicating pronounced aging effects and necessitating targeted optimization.

Figure 4.

Comparison of circuit performance degradation due to HCI and BTI effects in PMOS transistors (a) before and (b) after optimization.

Therefore, process optimizations for HCI-sensitive PMOS transistors are essential. Based on the analysis of the QSA formula, increasing the gate oxide thickness for PMOS transistors in high-frequency critical paths is an effective strategy to reduce HCI sensitivity. A larger transistor width effectively reduces the current density and peak electric field near the drain, thereby mitigating hot-carrier degradation. Consequently, the threshold voltage shift due to HCI exhibits an inverse dependence on device width. Within the SMIC 14 nm process library, increasing the transistor width-to-length ratio can effectively reduce the influence of the HCI effect on threshold voltage offset. The HCI effect of the improved PMOS transistor is significantly enhanced, as shown in Figure 4b.

4. Results and Discussion

To evaluate the effectiveness of the proposed SCFF modification, a comprehensive simulation study was conducted under varying supply voltages and accelerated aging conditions. The results demonstrate that the improved circuit maintains full functional integrity while achieving a significant enhancement in aging resilience, a conclusion further verified through HSPICE simulations and process corner analysis performed under domestic 14 nm process conditions.

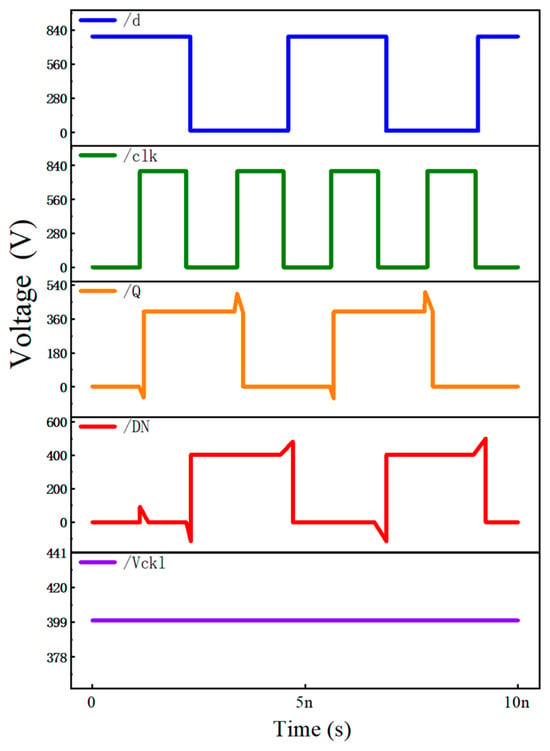

The improved SCFF operates correctly at Vdd = 0.4 V (as shown in the enhanced waveform diagram), with the rising edge delay of DN/DI reduced from 3.378 ns to 0.365 ns, validating the enhancement in timing reliability, as shown in Figure 5.

Figure 5.

Waveform diagram showing voltage versus time.

The proposed structural modifications targeted the reduction in stress duration in critical PMOS transistors (M3 and M6). By decoupling their conduction phases and optimizing the data recovery loop, unnecessary stress time was halved. This resulted in a 31% reduction in aging-induced delay for the 0→1 transition and improved symmetry in delay degradation between the 0→1 and 1→0 transitions. The modified SCFF maintained stable operation at 400 mV, validating suitability for ultra-low-voltage applications. The QSA model was adopted for SCFF aging simulation in this study. The aging conditions were set to a temperature of 125 °C and a duration equivalent to ten years. Performance differences between original and improved structures were compared via HSPICE simulation.

First, significant inhibition of threshold voltage degradation is observed. The NBTI degradation of the key PMOS transistors, namely M3 and M6, was reduced from 23.2764 mV to 5.007 mV, which represents an improvement of 78.5%. Meanwhile, the HCI degradation in the NMOS transistor M27 decreased from 22.379 mV to 17.1243 mV, corresponding to a 23.4% improvement. In addition, comprehensive improvement in timing performance is achieved. The proposed design yielded substantial timing improvements while operating at 0.4 V. The setup time showed a reduction of 61.6%, from 89.63 ps to 34.40 ps, and the clock-to-output delay was decreased by 74.6%, with no compromise in logical functionality.

By comparing the performance of the original SCFF, the gate length-adjusted SCFF (SCFF-GL), and the structurally modified SCFF (SCFF-Mod), it was found that SCFF-Mod achieves the lowest aging delay increment (0.84 ps for 0 → 1 transition) at the cost of a 20% increase in PDP. In contrast, SCFF-GL showed limited improvement due to increased RC delays in the feedforward path.

Aging analysis also identified key transistors contributing most to HCI degradation. Through the QSA model, HCI impact can be mitigated by increasing transistor gate length. Under typical conditions (Vdd = 0.4 V), the degradation increment decreased by approximately 30%. The improved SCFF reduced the aging delay increment by 55% in the worst case, with PDP increased by only 20%.

The SCFF-Mod was evaluated across process corners (tt, ss, ff, fnsp, snfp). The aging delay increment was consistently reduced, with the most notable improvement under the ss corner (55.5% reduction). Structural robustness to process variations underscores its practicality for wide range voltage scaling. At Vdd = 400 mV, the SCFF-Mod demonstrated correct functionality across all test vectors, confirming reliability in sub-threshold operation. The split-controlled design eliminated redundant switching, contributing to PDP efficiency.

Table 2 compares the anti-aging performance of the modified flip-flop with several classic low-voltage flip-flop structures and analyze the optimization effect in terms of performance, power consumption, and area [10,25]. The d2q delay is the average value of the 0-to-1 and 1-to-0 output propagation delays. The propagation delay of the SCFF declines by approximately around 46.02%, showing a significant decline in transmission delay. Among all the evaluated FFs, the SCFF shows the most pronounced decrease in propagation delay, highlighting its superior performance. However, the number of transistors in our work has increased significantly by 33%, and the power consumption has also increased by 26.31% due to the extra transistors when restricting the circuit. Overall, the performance of the improved SCFF is significantly enhanced, accompanied by increases in area and power consumption. The optimized structure has a very obvious improvement in the delay of the trigger with controllable power and area overheads.

Table 2.

Comparison of performance among various structures.

The proposed modifications successfully address aging effects while preserving ultra-low-voltage capabilities. By combining transistor-level tuning and structural optimizations, the design achieves a balanced trade-off between aging resilience and power efficiency. Results validate the SCFF’s suitability for energy-critical applications requiring long-term reliability.

5. Conclusions

In conclusion, this work investigates transistor-level anti-aging strategies for SCFFs under an FinFET process and proposes three effective approaches—conduction time optimization, main latch loop reconstruction, and secondary latch stress dispersion. Using setup time and clock-to-q delay as metrics, the proposed scheme significantly suppresses aging-induced delay, achieving reductions of 61.6% for the 0 → 1 transition and 74.6% for the 1 → 0 transition at the FF corner, while maintaining consistent effectiveness across all process corners, demonstrating strong robustness to process variation and aging. Experimental results confirm that the optimized SCFF effectively mitigates threshold voltage drift and leakage increase, reduces PMOS degradation by over 60%, improves timing delay by more than 40%, and supports stable operation at 0.4 V under high-frequency stress with controllable power and area overheads. Although the introduction of redundant transistors and bias circuits increases layout area by about 30% and adds some dynamic power consumption, the scheme still outperforms conventional redundancy methods, offering a practical solution for long-life, low-power nanoscale IC design. Future work will point toward device-level parallel redundancy for further enhancing aging resilience.

The presented NBTI analysis demonstrates that integrating reliability considerations into circuit design can effectively mitigate aging effects. Although such techniques may introduce power and design overheads, they provide a vital foundation for future robust and long-lifespan circuit architectures. In future analyses and optimization of subsequent flip-flop structures, particular attention should be paid to the aging impact of NBTI on circuit behavior to further enhance semiconductor device performance while providing comprehensive reliability evaluation.

Author Contributions

Conceptualization, Y.Z. and Q.S.; methodology, Y.Z. and J.T.; validation, L.C. and H.Z.; formal analysis, Y.Z.; investigation, Y.Z.; resources, Q.S.; writing—original draft preparation, Y.Z.; writing—review and editing, H.Z. and Q.S. All authors have read and agreed to the published version of the manuscript.

Funding

This work was supported by the National Natural Science Foundation of China (62374036) and the Support Plans for the Youth Top-Notch Talents of China.

Institutional Review Board Statement

Not applicable.

Informed Consent Statement

Not applicable.

Data Availability Statement

The data presented in this study are available on request from the corresponding author.

Conflicts of Interest

The authors declare no conflicts of interest.

References

- Ding, Y.; Yan, C.; Qu, Y.; Zhao, Y. Re-examination of hot carrier degradation mechanism in ultra-scaled nFinFETs. IEEE Electron Device Lett. 2022, 43, 1802–1805. [Google Scholar] [CrossRef]

- Yu, Z.; Sun, Z.; Wang, R.; Zhang, J.; Huang, R. Hot carrier degradation-induced dynamic variability in FinFETs: Experiments and modeling. IEEE Trans. Electron Devices 2020, 67, 1517–1522. [Google Scholar] [CrossRef]

- Parihar, N.; Goel, N.; Mukhopadhyay, S.; Mahapatra, S. BTI analysis tool—Modeling of NBTI DC, AC stress and recovery time kinetics, nitrogen impact, and EOL estimation. IEEE Trans. Electron Devices 2017, 65, 392–403. [Google Scholar] [CrossRef]

- Yan, Z.; Huang, Y.; Jiao, H. A Low-Power Single-Phase Split-Controlled Flip-Flop with No Redundant Switching. In Proceedings of the 2024 IEEE International Symposium on Circuits and Systems (ISCAS), Singapore, Singapore, 19–22 May 2024; pp. 1–5. [Google Scholar] [CrossRef]

- Liu, L.N.; Li, B.; Zhao, M.J.; Xie, J. Design for Improved NBTI Reliability of CMOS Digital IC. In Proceedings of the 2010 IEEE International Conference of Electron Devices and Solid-State Circuits (EDSSC), Hong Kong, 15–17 December 2010; pp. 5–8. [Google Scholar]

- Keane, J.; Wang, X.; Persaud, D.; Kim, C.H. An All-In-One Silicon Odometer for Separately Monitoring HCI, BTI, and TDDB. IEEE J. Solid-State Circuits 2010, 45, 817–829. [Google Scholar] [CrossRef]

- Huard, V.; Denais, M.; Parthasarathy, C. NBTI degradation: From physical mechanisms to modelling. Microelectron. Reliab. 2006, 46, 1–23. [Google Scholar] [CrossRef]

- Schroder, D.K.; Babcock, J.A. Negative bias temperature instability: Road to cross in deep submicron silicon semiconductor manufacturing. J. Appl. Phys. 2003, 94, 1–18. [Google Scholar] [CrossRef]

- Ramakrishnan, K.; Wu, X.; Vijaykrishnan, N.; Xie, Y. Comparative Analysis of NBTI Effects on Low Power and High Performance FlipFlops. In Proceedings of the 2008 IEEE International Conference on Computer Design, Lake Tahoe, CA, USA, 12–15 October 2008; pp. 200–205. [Google Scholar]

- Jafari, A.; Raji, M.; Ghavami, B. Timing Reliability Improvement of Master-Slave Flip-Flops in the Presence of Aging Effects. IEEE Trans. Circuits Syst. I Regul. Pap. 2020, 67, 4761–4773. [Google Scholar] [CrossRef]

- Mintarno, E.; Chandra, V.; Pietromonaco, D.; Aitken, R.; Dutton, R.W. Workload dependent NBTI and PBTI analysis for a sub-45nm commercial microprocessor. In Proceedings of the 2013 IEEE International Reliability Physics Symposium (IRPS), Monterey, CA, USA, 14–18 April 2013; pp. 3A.1.1–3A.1.6. [Google Scholar]

- Kawai, N.; Takayama, S.; Masumi, J.; Kikuchi, N.; Itoh, Y.; Ogawa, K.; Ugawa, A.; Suzuki, H.; Tanaka, Y. A fully static topologically-compressed 21-transistor flip-flop with 75% power saving. IEEE J. Solid-State Circuits 2014, 49, 2526–2533. [Google Scholar] [CrossRef]

- Kim, Y.; Jung, W.; Lee, I.; Dong, Q.; Henry, M.; Sylvester, D.; Blaauw, D. A static contention-free single-phase-clocked 24 T flipflop in 45 nm for low-power applications. In Proceedings of the 2014 IEEE International Solid-State Circuits Conference Digest of Technical Papers (ISSCC), San Francisco, CA, USA, 9–13 February 2014; pp. 466–467. [Google Scholar]

- Cai, Y.; Savanth, A.; Prabhat, P.; Myers, J.; Weddell, A.S.; Kazmierski, T.J. Ultra-Low Power 18-Transistor Fully Static Contention-Free Single-Phase Clocked Flip-Flop in 65-nm CMOS. IEEE J. Solid-State Circuits 2019, 54, 550–559. [Google Scholar] [CrossRef]

- Paul, B.C.; Kunhyuk, K.; Kufluoglu, H.; Alam, M.A.; Roy, K. Temporal performance degradation under nbti: Estimation and design for improved reliability of nanoscale circuits. In Proceedings of the Proceedings of the Design Automation & Test in Europe Conference, Munich, Germany, 6–10 March 2006; Volume 1, pp. 1–6. [Google Scholar]

- Kang, K.; Kufluoglu, H.; Alain, M.A.; Roy, K. Efficient transistor-level sizing technique under temporal performance degradation due to nbti. In Proceedings of the 2006 International Conference on Computer Design, San Jose, CA, USA, 1–4 October 2006; pp. 216–221. [Google Scholar]

- Huang, R.; Jiang, X.B.; Guo, S.F.; Ren, P.P.; Hao, P.; Yu, Z.Q.; Zhang, Z.; Wang, Y.Y.; Wang, R.S. Variability- and reliability-aware design for 16/14 nm and beyond technology. In Proceedings of the 2017 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2–6 December 2017; pp. 12.4.1–12.4.4. [Google Scholar] [CrossRef]

- Chandrakasan, A.P. Analysis of Reliability of Flip-Flops under Transistor Aging Effects in Nano-scale CMOS Technology. In Design of High-Performance Microprocessor Circuits; IEEE Press: Piscataway, NJ, USA, 2001; pp. 57–65. [Google Scholar]

- Alioto, M.; Consoli, E.; Palumbo, G. Variations in nanometer CMOS flip-flops: Part I—Impact of process variations on timing. IEEE Trans. Circuits Syst. I Regul. Pap. 2015, 62, 2035–2043. [Google Scholar] [CrossRef]

- Keane, J.; Kim, C. An odomoeter for CPUs. IEEE Spectr. 2011, 48, 28–33. [Google Scholar] [CrossRef]

- Hicks, J.; Bergstrom, D.; Hattendorf, M.; Jopling, J.; Maiz, J.; Prasad, C.; Wiedemer, J. 45 nm transistor reliability. Intel Technol. J. 2008, 12, 131–144. [Google Scholar]

- Wang, W.; Reddy, V.; Krishnan, A.T.; Vattikonda, R.; Krishnan, S.; Cao, Y. An integrated modeling paradigm ofcircuit reliability for 65 nm CMOS technology. In Proceedings of the 2007 IEEE Custom Integrated Circuits Conference, San Jose, CA, USA, 16–19 September 2007; pp. 511–514. [Google Scholar]

- Zainudin, M.F.; Hussin, H.; Halim, A.K.; Karim, J. Aging analysis of high performance FinFET flip-flop under Dynamic NBTI simulation configuration. In Proceedings of the IOP Conference Series: Materials Science and Engineering, Kuching, Malaysia, 7–8 August 2018; Volume 341. [Google Scholar]

- Ong, T.-C.; Ko, P.-K.; Hu, C. Hot-carrier current modeling and device degradation in surface-channel p-MOSFETs. IEEE Trans. Electron Devices 1990, 37, 1658–1666. [Google Scholar] [CrossRef]

- Yan, A.; Hu, C.; Li, J.; Bai, N.; Huang, Z.; Ni, T.; Patrick, G.; Wen, X. Cost-Optimized Double-Node-Upset-Recovery Latch Designs with Aging Mitigation and Algorithm-Based Verification for Long-Term Robustness Enhancement. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2025, 33, 1765–1773. [Google Scholar] [CrossRef]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2026 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license.