Abstract

Silicon carbide (SiC) power converters are increasingly used in automotive, renewable energy, and industrial applications. While reliability assessments are typically performed at either the device or system level, an integrative approach that simultaneously evaluates both levels remains underexplored. This article presents a novel system-level simulation method with two strategies to evaluate the reliability of power devices and a resonant converter under varying temperatures and total ionizing doses (TIDs). Temperature-sensitive electrical parameters (TSEPs), such as on-state resistance () and threshold voltage shift (), are calibrated and analyzed using a B1505A curve tracer. These parameters are incorporated into the system-level simulation of a 300 W resonant converter with a boosting cell. Both Silicon (Si) and SiC-based power resonant converters are assessed for power application in space engineering and harsh environments. Additionally, gate-oxide degradation and -related issues are discussed based on the simulation results. The thermal-strategy results indicate that SiC MOSFETs maintain a more stable conduction loss at elevated temperatures, exhibiting higher reliability due to their high thermal conductivity. Conversely, increased TIDs result in a negative shift in conduction losses across all SiC devices under the radiation strategy, affecting the long-term reliability of the power converter.

1. Introduction

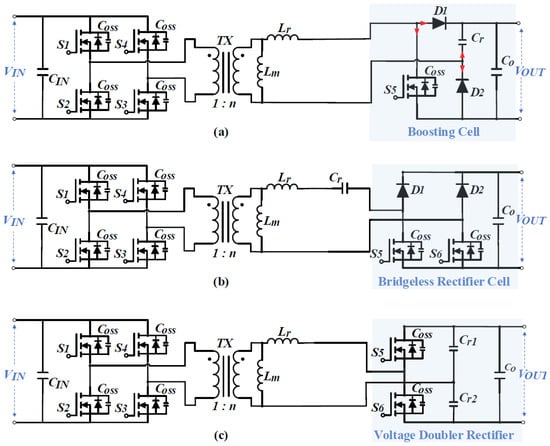

Silicon carbide (SiC) is a representative wide-bandgap semiconductor that supports a broad range of applications, including quantum technologies, luminescent nanostructures, ultra-fine fibers, and implantable biomedical devices [1,2,3,4]. The existence of multiple SiC polytypes with distinct stacking sequences leads to different physical properties. In particular, 4H-SiC, a common polytype of SiC, offers a high critical electric field and high thermal conductivity [5]. In the past decade, DC-DC power converters have gained significant attention due to their expanding role across sectors ranging from aerospace to renewable energy. In renewable energy systems, especially grid-tied photovoltaic applications galvanically isolated, unidirectional LLC (Inductor–Inductor–Capacitor) resonant converters have become common and the focus of numerous studies [6]. Efforts in low-voltage power converters have concentrated on improving key characteristics such as reliability, wide input and load ranges, low electromagnetic interference (EMI), and high efficiency. According to Parvez, Mohammad et al. [7], isolated resonant converters can be broadly classified into three types: resonant-boost converters, hybrid resonant converters, and resonant single-ended primary-inductor converters (SEPICs). Resonant-boost converters are commonly employed in solar-energy systems to accommodate fluctuations in solar input. Recent advancements have introduced hybrid resonant converters with improved rectifier cells, offering a broad input-voltage range and California Energy Commission (CEC) efficiencies exceeding 96% [8,9,10,11,12]. These topologies are designed to minimize component counts in rectifier tanks and extend the regulation range, as shown in Figure 1. For example, a resonant-boost converter with a simplified boosting rectifier cell has been proposed [12]. While this design reduces voltage stress on the resonant capacitor by clamping it at the output-voltage level, it does not fully accommodate variations in input voltage and output power. Although this topology has a limited input-voltage regulation range due to high step-up ratios and load currents [13], it remains valuable for studying the switching performance and reliability of modern power devices.

Figure 1.

Three types of resonant converters with a boost rectifier cell: (a) boosting rectifier cell with only one switch and two diodes [12]; (b) bridgeless rectifier cell with two switches and two diodes [9]; (c) voltage doubler with two switches [10].

Recently, SiC power device degradation has been extensively discussed at the device level under harsh environments such as high temperature and radiation [14,15,16,17]. However, the reliability of power converters, especially under high radiation doses, remains underexplored. Existing reliability assessments for power converters mostly rely on experimental testing, which is costly and case-specific. Thus, the development of system-level evaluation frameworks that explicitly incorporate device degradation is needed. Although several simulation-based SiC DC-DC converters have been designed and evaluated using the PSIM manufacturer simulation tool [18,19,20,21], and while these studies analyze power losses and overall efficiency, they lack in-depth analyses of device reliability and do not fully leverage the simulation tool’s capabilities. For system-level simulation of power converters, physics-based models often suffer from convergence issues and long runtimes [22,23,24], whereas simplified models in simulation tools such as PSIM or PLECS sacrifice accuracy. To achieve both computational efficiency and degradation-aware modeling, a methodology that explicitly incorporates degradation effects in SiC power MOSFETs is required.

In this study, a novel simulation framework to model thermal- and radiation-induced degradation and quantify its impact on power converter efficiency is developed. This approach facilitates extensive research without being constrained by datasheet limitations. Also, these two strategies offer a convenient approach for researchers and application engineers to evaluate the reliability of power converters under harsh environment conditions before conducting experiments. For comparison, both Si- and SiC-based resonant converters with a boost cell are evaluated in PSIM. In addition, the results show that SiC-based converters are more reliable than their Si-based counterparts in harsh environments.

2. New Proposed Simulation Methodology

2.1. PSIM Thermal Model

Dynamic simulation in complex converter topologies remains a challenge for achieving a balance between accuracy, convergence reliability, and simulation speed [25]. For new design topologies, the ideal models are first employed to verify the feasibility of the topology and its control scheme. Additionally, the thermal model can be employed to estimate switching losses and conduction losses in power devices. In PSIM [26], dedicated thermal models idealize switching transitions and evaluate losses using look-up tables. The parameters for the look-up table used in this work are shown in Table 1. The calculations in the PSIM simulation can account for various conditions, such as the conducted voltage and current across the switch, junction temperature and gate drive voltage, and physic parameters such as parasitic capacitance and . It provides a good correlation with actual power losses while significantly reducing the computational time compared to the SPICE model. Although the present thermal model does not account for device degradation, degradation-aware device models can be incorporated in the future to enable system-level performance analysis. From both reliability and lifetime perspectives [27,28], this integration offers clear benefits. It enables more predictive loss and stress estimation and reduces reliance on costly long-duration experiments.

Table 1.

Critical parameters in PSIM thermal model.

In PSIM, the calculation of conduction losses () and on/off switching losses () is given by [21]

where is the root-mean-square value of the conducted current (obtained from the switching waveform) and , which depends on the junction temperature . can be expressed as

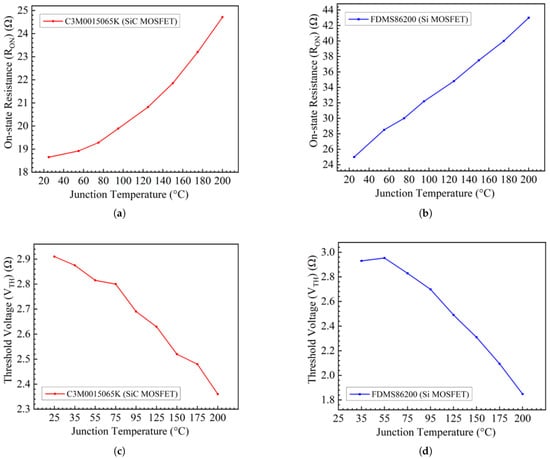

where is the normalized on-state resistance at (from the datasheet’s normalized versus temperature curve) and is the corresponding temperature coefficient. However, in the thermal strategy, is not applied in the simulation because the actual is obtained directly using a curve tracer. The junction temperature is fixed at , so the measured and from Figure 2 can be used in the thermal model without calculating , providing a flexible and practical solution for system evaluation.

Figure 2.

(a) SiC MOSFET (C3M0015065K) junction temperature vs. ; (b) Si MOSFET (FDMS86200) junction temperature vs. ; (c) SiC MOSFET (C3M0015065K) junction temperature vs. ; (d) Si MOSFET (FDMS86200) junction temperature vs. .

2.2. A New Simulation Method

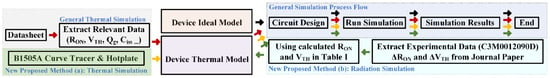

A newly proposed simulation method to assess the efficiency and reliability of the DC-DC resonant converter includes two strategies: (a) thermal simulation and (b) radiation simulation as illustrated in Figure 3. Both simulations utilize the PSIM simulation tool and its thermal model. In this paper, the SiC-based resonant converter is evaluated under a wide-range temperature and radiation dose conditions. The conventional simulation approach employs a thermal model to estimate the switching and conduction losses for each device in the system. This model is based on datasheet characteristics, which can limit the exploration and evaluation of device performance in system-level analysis, especially for scenarios such as a resonant converter operating at high temperatures exceeding 175 °C.

Figure 3.

Proposed simulation methodology with two strategies: thermal simulation and radiation simulation.

To analyze the performance and degradation of SiC devices in a resonant tank, a simulation method is illustrated in Figure 3. This method includes two key strategies:

- Thermal Strategy: This involves calibrating the power device using the B1505A curve tracer (Keysight, Santa Rosa, CA, USA), with the device placed on a hot plate for high-temperature testing. The resulting characteristics, typically not provided in the datasheet, are then applied in thermal simulation using a system-level simulation tool.

- Radiation Strategy: This utilizes relevant data, specifically the changes in and , from the article [14] on the commercial SiC power device (C3M012090D) (Wolfspeed, Durham, NC, USA) under investigation. The and values calculated at various total ionizing doses (TIDs), as shown in Table 2, are then integrated into the PSIM thermal model.

Table 2. Calculated and .

Table 2. Calculated and .

It is worth noting that PSIM-based thermal simulations have been adopted in prior converter-level studies, where simulation results were experimentally verified and showed good agreement with measured data [29,30,31]. In addition, the device degradation considered in this work is obtained from experimentally measured data reported in the literature as well as B1505A-based device characterization. Although this study does not include experimental validation, the simulation results exhibit good consistency with estimates obtained from widely accepted analytical loss models [21], supporting the physical plausibility of the observed trends.

Both thermal and radiation strategies offer valuable benefits for researchers engaged in extensive studies. While this work focuses on analyzing only the and parameters at the device level, other parameters listed in Table 1 can also be modified and examined. This approach enables device-level degradation insights to be extended to system-level analysis. Although current system-level simulators are limited and power loss remains the principal observable of the converter after device degradation, the framework developed here is readily extensible. The present method cannot yet resolve degradation effects at the control-waveform level. In the future, degradation-aware device models could relate device degradation to system-level dynamics, for example, by accounting for BTI (Bias Temperature Instability)-induced shifts in the gate plateau that delay rising and falling edges, and threshold voltage variation that affects the voltage slew rate [32,33,34]. In subsequent studies, false turn-on events could become observable under high slew-rate and crosstalk conditions, especially in the presence of both aging-induced and radiation-induced threshold shifts.

2.3. Device Calibration

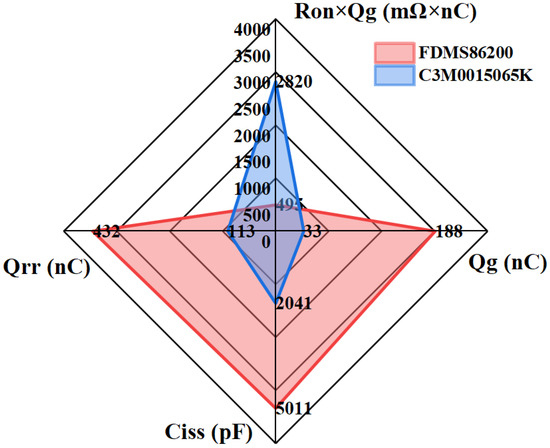

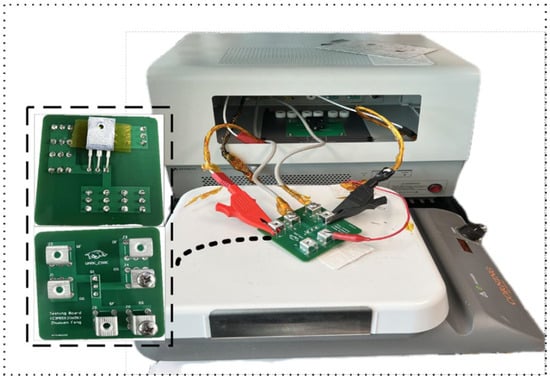

This study examines two commercial devices, a Si MOSFET (FDMS86200) (Onsemi, Scottsdale, AZ, USA) and a SiC MOSFET (C3M0015065K) (Wolfspeed, Durham, NC, USA), each with a typical of 15 mΩ. Table 1 summarizes the key device parameters, and Figure 4 compares their dynamic performance and figure of merit (FOM). To address potential discrepancies between datasheet transfer characteristics and actual device behavior, the B1505A curve tracer was used for precise measurement of and . The combination of an extended printed circuit board (PCB) and hot plate to control the junction temperature is illustrated in Figure 5. During testing, the device under test (DUT) was placed on a hot plate for 15 min to allow the junction temperature to stabilize at the target level. Also, other quasi-static parameters can be characterized as a function of temperature using the same setup, enabling quantitative assessment of temperature-accelerated degradation.

Figure 4.

Radar chart comparison of key parameters between Si MOSFETs (FDMS86200) and SiC MOSFETs (C3M0015065K).

Figure 5.

Experimental setup for device calibration on a hot plate for temperature-dependent characterization.

The methodology for extracting and , as described in [35], was applied at different temperatures in this work, with the results shown in Figure 2. The SiC MOSFET exhibited less variation in compared to the Si MOSFETs, which can be attributed to the thermal conductivity of the SiC. In fact, it is worth noting that the radiation strategy also employs the B1505A for device calibration prior to irradiation [14]. Moreover, a measurement setup similar to the temperature-accelerated degradation calibration can be used to characterize total ionizing dose (TID) effects, enabling assessment of both static and dynamic degradation [36].

2.4. Radiation Simulation

In radiation strategy, experimental data is extracted and calculated from [14] due to the lack of a radiation source. This approach provides valuable insights for application engineers to analyze device performance in harsh environments, which is discussed in detail below.

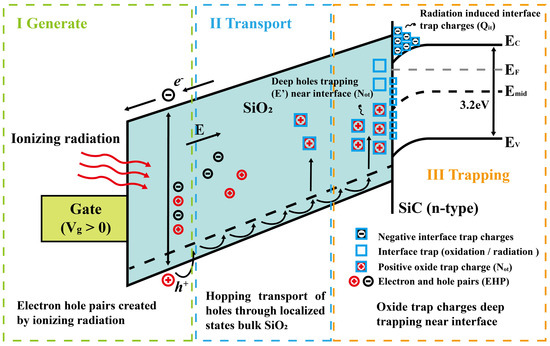

2.4.1. Physical Mechanism of SiC MOSFET Degradation

As previously mentioned, the of SiC MOSFETs mainly depends on channel resistance, which is influenced by mobility and . When a SiC MOSFET is exposed to gamma radiation, electron–hole pairs are generated in the gate oxide. Due to their high mobility, electrons are more likely to escape from the gate oxide, while holes become trapped within the gate oxide, leading to an accumulation of negative charges at the SiO2/SiC interface. Thus, the accumulation of oxide trap charges following irradiation leads to greater inversion in the NMOS channel and a negative shift in the threshold voltage. The mechanism of threshold voltage degradation under radiation doses in SiC MOSFETs is illustrated in Figure 6.

Figure 6.

Energy band diagram of radiation-induced charge dynamics in the SiO2/SiC system under positive gate bias.

To describe the TID irradiation-induced degradation of , a model derived by [14] can be applied:

where q is the elementary charge, is the number of generated electron–hole pairs, is the gate-oxide thickness, is the fraction of positive oxide trap charges, is the dielectric constant of oxide, is the hole yield as a function of the electric field, and Dose is the total ionizing dose in rads.

Under different bias conditions, the trapping effect results in varying degradation behavior due to the electric field. When the MOSFET is on, it operates under a gate bias condition; when off, it operates under drain bias. Under gate bias, a high positive electric field is applied in the gate oxide above the channel region, while under drain bias, a comparatively lower negative electric field is present above the near-channel region. As a result, SiC MOSFETs exhibit greater sensitivity to gate bias during -ray irradiation, particularly in terms of changes in and . In the simulation, SiC MOSFETs (C3M012090D) are used in [14]. The extracted and under gate bias, as shown in Table 2, are applied in the simulation.

In Equation (4), is proportional to the TIDs, the electric field in the gate oxide, and the oxide thickness. Given that the oxide layer in SiC MOSFETs is typically thicker than nm, electrons have sufficient space to accelerate under the electric field, gaining more than eV of energy. This energy allows them to collide with SiO2 lattice atoms, generating electron–hole pairs [37]. Due to the oxide thickness, variation in planar SiC MOSFET is significantly smaller than in trench SiC MOSFETs at higher dose levels [38,39]. However, limited research compares planar-gate and split-gate MOSFETs under high radiation doses. Based on Equation (4), it can be inferred that the variation in split-gate MOSFETs might be significantly smaller than that in planar MOSFETs, as the electric field in the gate oxide is much lower in split-gate designs.

2.4.2. Threshold Voltage Shift Induced by Oxide Traps

The of SiC MOSFETs can be affected by radiation-induced oxide traps. The sensitivity of depends on TIDs and the electric field generated by the trapped hole. In the experiment [14], a negative shift in and was observed under -ray irradiation. For worst-case assessment, the shift caused by radiation-induced trapped charges should be evaluated together with the shift induced by high-temperature gate bias (HTGB) under negative gate bias [40].

When HTGB and TIDs are simultaneously applied, Zhang et al. [41] observes a substantial shift in . Therefore, although the decreases under TIDs, the overall power consumption of power devices in harsh environments (with both high temperature and high radiation doses) increases, potentially reducing the efficiency of power applications. Unfortunately, limited research addresses the performance of power devices at the application level under harsh environments, including online measurements. Consequently, by experimentally characterizing parameter drifts under concurrent BTI and TID and integrating the extracted models into the proposed framework, the system-level impact on efficiency can be evaluated by using the proposed method.

3. Isolated Series Resonant Converter

In this paper, a galvanically isolated series resonant converter (SRC) topology is selected and designed. A brief introduction to the resonant converter is provided below.

3.1. Resonant Boost Converter Topology

The converter features a front-end full bridge and a boosting cell, connected through a galvanically isolated transformer [12]. It offers significant advantages, including reduced stress on the resonant capacitor, which regulates the output voltage, as well as a lower component count compared to the topologies in Figure 1. The proposed converter can operate in four distinct modes, all based on a discontinuous resonant current with a quality factor of less than one, irrespective of load conditions. The pure-SRC mode is employed solely in the simulation. The prototype developed for this study has a power rating of 300 W and achieves an output voltage of 355 V and the design parameters of the proposed converter are included in Table 3.

Table 3.

Design parameters of the proposed converter.

As a wide-input-range DC–DC resonant converter, this type is particularly suited for solar applications, especially in space solar applications. Therefore, it is essential to evaluate the performance of the converter in harsh environments, such as high temperature and high radiation doses. In this paper, two strategies are proposed and implemented to simulate the power losses of the converter under these extreme conditions.

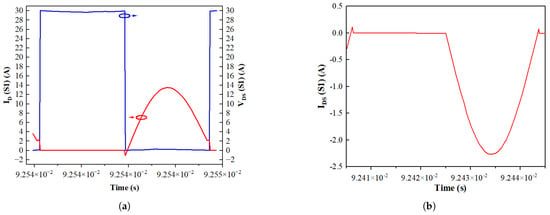

3.2. Zero-Voltage Switching

To minimize turn-on switching losses, zero-voltage switching (ZVS) has been implemented in this topology. As a result, turn-on switching loss is negligible, and the turn-off loss is determined by the fall time. The turn-off voltage slew rate of the device is influenced by the gate drive circuit design.

In the front-end full bridge, the transformer’s magnetizing inductance () serves as the current source during dead time. Thus, the magnetizing inductance should be designed such that the magnetizing current can fully charge and discharge the parasitic output capacitance of S1–S4, facilitating ZVS [12]. Figure 7 shows the drain–source voltage () and drain current of S1 over one period, clearly demonstrating ZVS in this design. However, it is important that the magnetizing inductance of the transformer be designed according to the following criterion:

where n is the transformer turns ratio, is the dead time in the primary-side gate signals, is the switching frequency of the power devices, and is the parasitic output capacitance of the front-end full-bridge switches.

Figure 7.

(a) (green) and (red) of S1 showing the implementation of ZVS during dead time; (b) drain current of S5 showing the implementation of ZCS during dead time.

When designing a resonant converter, it is crucial to account for the switch parasitic. In addition to the output capacitance, parameters such as gate charge and the dynamic characteristics of the body diode must align with the circuit design. The proposed strategy provides an effective approach for analyzing how these device parameters interact with the circuit, thereby ensuring optimal performance.

4. Simulation Results and Reliability Analysis

4.1. Temperature-Sensitive Electrical Parameters (TSEPs)

Due to their excellent material characteristics, SiC MOSFETs can operate at extremely high temperatures and are suitable for harsh environment applications. Various TSEPs of SiC MOSFETs, such as on-state resistance () and threshold voltage (), should be analyzed.

4.1.1. On-State Resistance ()

Gate-oxide degradation and total are critical aging indicators for SiC MOSFETs. In both typical planar MOSFET and trench MOSFET shown in Figure 1, the total is obtained by summing the individual resistances of each layer and region, which can be represented as

Here, is the channel resistance, is the source region resistance, is the resistance of the JFET region (Junction Field-Effect Transistor), and , , and represent the accumulation resistance, the resistance of the drift region, and the substrate resistance, respectively. is the source contact resistance, while is the drain contact resistance. However, the dominant contributors to are different between Si MOSFETs and SiC MOSFETs (1.2 kV planar MOSFET). In Si MOSFETs, and are the primary contributors due to lower breakdown electric-field strength and a thicker drift layer. To achieve a comparable breakdown-voltage rating, the lower critical electric field of Si requires a thicker drift layer to maintain the blocking voltage. In contrast, is a major contributor to in SiC MOSFETs due to lower inversion carrier mobility at the SiO2/SiC interface [42,43]. Therefore, excluding , the rest of the resistances can be defined as the residual resistance (). The total is the sum of and , where the contribution of channel resistance is given by [44]

where is the channel length, P is the pitch of the MOSFET elementary cell, is the electron mobility in the inversion layer, is the specific gate-oxide capacitance, is the applied gate voltage, and is the threshold voltage.

In [45], it is noted that and exhibit a positive temperature coefficient (PTC), while displays a negative temperature coefficient (NTC). As discussed above, is the primary contributor to in SiC MOSFETs. As shown in Figure 2, in the temperature range of 25–140 °C, the SiC device shows a relatively smaller increase in compared with the Si device. This behavior can be attributed to the dominant channel resistance, exhibiting a negative temperature coefficient (NTC) in this range, which partially offsets the positive temperature coefficient (PTC) increase in the residual resistance [46]. Many studies have reported that channel resistance can exhibit an NTC behavior [43,47,48], which is mainly associated with the temperature dependence of the carrier mobility and the effective gate overdrive . For SiC MOSFETs, is more temperature-sensitive due to the high interface-state density at the SiO2/SiC interface [46], which affects the temperature dependence of the effective gate overdrive . As a result, the effective gate overdrive increases as temperature increases, thereby partially reducing . This NTC behavior of results in a weaker temperature sensitivity of in SiC MOSFETs compared with Si MOSFETs over the studied temperature range. At a high temperature up to , no longer dominates ; instead, and in become more influential as the temperature increases [49]. Overall, the increase in for the SiC MOSFET remains smaller than that of the Si MOSFET at elevated temperatures in this study.

4.1.2. Threshold Voltage ()

As discussed in Section 2, is a radiation-sensitive parameter that tends to shift negatively during gamma-ray radiation. However, it is also sensitive to temperature changes. The threshold voltage of the SiC MOSFET can be expressed as follows [49]:

where is the dielectric constant of SiC, q is the electronic charge, is the doping concentration of the P-base region, is the flat-band voltage, is the Fermi potential from the substrate, and is the interface-state density. Notably, the commercial devices chosen from CREE have shown improvements in the SiO2/SiC interface [50]. With the reduction in near-interface traps (NITs), the stability of performs well under high temperatures. The rate of variation in with temperature can be expressed as follows [48]:

where T is temperature, is the work function difference between the metal and the semiconductor at the gate and substrate, and is the number of traps between the neutral level and the conduction band. The temperature dependence of is determined by the , and . Specifically, decreases with increasing temperature due to the rise in intrinsic carrier concentration. Additionally, also decreases with temperature as the Fermi level energy () shifts toward the mid-gap, which reduces the occupancy of electrons in the interface traps. In general, the of SiC MOSFETs shows a negative shift characteristic as the temperature increases.

4.2. Thermal Simulation Results

It is important to note that the switching loss for each MOSFET is only an estimate. In the simulation, both the external turn-on and turn-off resistances are set to , with other parameters shown in Table 2, which correspond to the switching loss in the PSIM thermal model, as discussed in Section 2.

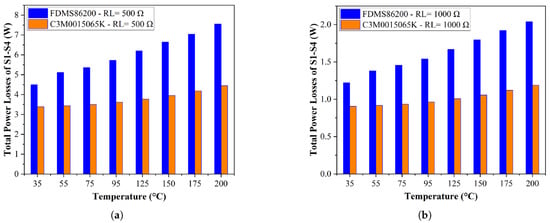

In the thermal strategy, the conduction losses of power devices in the front-end full bridge are primarily analyzed to compare the power consumption stability between Si and SiC MOSFETs, which can affect the power converter reliability. As shown in Figure 8, the change in total power conduction losses for SiC MOSFETs is less pronounced than for Si MOSFETs as temperature increases. At a 40.8% load (), the variation in for SiC MOSFETs is only 26%, compared to a significantly higher 67.7% for Si MOSFETs. Similarly, at an 81% load (), the variation in for SiC MOSFETs is just 21%, while for Si MOSFETs, it remains significantly higher at 67%.

Figure 8.

(a) Power conduction losses of Si (blue) and SiC (orange) MOSFETs (S1–S4) under different temperatures (Rload = 500 ). (b) Power conduction losses of Si (blue) and SiC (orange) MOSFETs (S1–S4) under different temperatures (Rload = 1000 ).

In summary, the power loss stability of the Si-based resonant converter is lower than that of the SiC-based resonant converter, primarily due to the superior stability of SiC under high temperatures. However, it is important to emphasize that the switching performance discussed is only an estimate and depends on the gate driver design. As previously noted, the switch’s fall time significantly affects switching performance, especially when achieving ZVS. SiC devices, with their high dv/dt and di/dt characteristics, enable faster turn-on and turn-off speeds compared to Si devices. The key consideration is the trade-off involving overshoot. In low input voltage scenarios, the overshoot voltage remains below the breakdown voltage, reducing potential risks. Therefore, SiC MOSFETs in today’s technology are more adaptable to harsh environments, even in low-power applications.

4.3. Radiation Simulation Results and Analysis

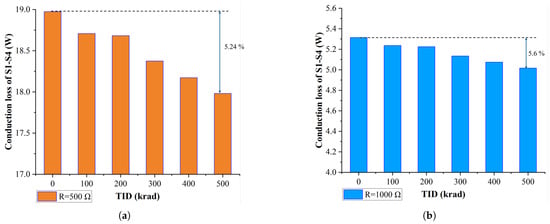

The radiation simulation results shown in Figure 9 indicate that SiC MOSFETs experience a decrease in as the TID increases from 0 to 500 krad, with a 5.24% reduction noted at a load resistance of . While this reduction in may initially appear beneficial due to the resulting lower power conduction losses, the threshold voltage shift observed under gamma-ray irradiation raises more significant concerns regarding long-term reliability. A negative shift in implies that the MOSFET can turn on more easily, which increases the risk of unintended switching in the presence of noise, ultimately compromising circuit performance and reliability. Furthermore, as the load decreases (e.g., at ), the overall power conduction losses continue to decrease further, but the impact on remains considerable. The accumulation of trapped charges in the gate oxide causes a more permanent degradation of , potentially leading to device failure after prolonged operation under radiation. While the decrease in contributes to lower conduction losses, this trade-off compromises long-term device reliability. In addition, the negative shift in increases the device’s sensitivity to environmental noise, which poses a significant risk in space applications where long-term reliability is critical.

Figure 9.

(a) Power conduction losses of SiC MOSFETs (S1–S4) under different TIDs (Rload = 500 ). (b) Power conduction losses of SiC MOSFETs (S1–S4) under different TIDs (Rload = 1000 ).

The combined effects of radiation exposure, high temperature, and prolonged operation must be analyzed in system-level design. A simulation-based method can aid in predicting potential issues that may arise in real experiments. For instance, the permanent degradation of and the alterations in could lead to catastrophic device failure, resulting in simulation that fails to accurately replicate real-life conditions.

4.4. Future Work

In the future, experimental validation will be pursued to further corroborate the proposed system-level methodology by integrating converter-level measurements with device characterization under elevated temperature or radiation stress, subject to the availability of suitable experimental facilities. In addition, more detailed degradation-aware device models will be incorporated to capture dynamic effects beyond steady-state losses, such as control-waveform distortion, switching transient variation, and gate-plateau shifts induced by device degradation. These extensions aim to enhance the capability of the framework for reliability-oriented system-level analysis under harsh operating conditions.

5. Conclusions

This paper proposes a simulation methodology that integrates thermal and radiation strategies within the PSIM thermal-modeling framework. In the thermal strategy, device calibration is performed using a B1505A curve tracer to correct deviations between datasheet-based and measured transfer characteristics. The simulation results indicate that the SiC-based resonant converter exhibits greater power loss stability than its Si-based counterpart at elevated temperatures. In the radiation strategy, the literature-reported experimental data are used to simulate power losses in the resonant converter under the total-ionizing-doses (TIDs) condition. Accordingly, the associated gate-oxide degradation and threshold voltage instability are discussed in this work. Although conduction losses may decrease under certain load conditions, the increase in TIDs is still expected to induce a permanent threshold voltage shift, which reduces the available gate drive operating margin and can adversely affect converter-level robustness. In addition, the absolute magnitude of radiation impact may be underestimated, since other radiation-sensitive effects are not captured in the present model.

Author Contributions

Conceptualization, Q.L. and Z.C.; methodology, Q.L., Z.C. and Z.F.; software, Z.F., A.A. and F.F.; validation, Z.F., P.L., F.F. and A.S.M.K.H.; formal experiment and analysis, Z.F.; investigation, Z.F., F.F., A.A., L.H., Z.C. and Q.L.; resources, Z.C. and Q.L.; data curation, Z.F., P.L., F.F. and A.S.M.K.H.; writing—original draft, Z.F.; writing—review and editing, Z.F., Z.C. and Q.L.; visualization, Z.F. and F.F.; supervision, Q.L., Z.C. and L.H.; project administration, Q.L., L.H. and Z.C.; funding acquisition, Q.L. and Z.C. All authors have read and agreed to the published version of the manuscript.

Funding

This research received no external funding.

Institutional Review Board Statement

Not applicable.

Informed Consent Statement

Not applicable.

Data Availability Statement

The original contributions presented in this study are included in the article. Further inquiries can be directed to the corresponding authors.

Conflicts of Interest

The authors declare no conflicts of interest.

References

- Castelletto, S.; Boretti, A. Silicon carbide color centers for quantum applications. J. Phys. Photonics 2020, 2, 022001. [Google Scholar] [CrossRef]

- Lebedev, A.S.; Suzdal’tsev, A.V.; Anfilogov, V.N.; Farlenkov, A.S.; Porotnikova, N.M.; Vovkotrub, E.G.; Akashev, L.A. Carbothermal synthesis, properties, and structure of ultrafine SiC fibers. Inorg. Mater. 2020, 56, 20–27. [Google Scholar] [CrossRef]

- Huczko, A.; Dabrowska, A.; Savchyn, V.; Popov, A.I.; Karbovnyk, I. Silicon carbide nanowires: Synthesis and cathodoluminescence. Phys. Status Solidi B 2009, 246, 2806–2808. [Google Scholar] [CrossRef]

- Saddow, S.E. Silicon carbide technology for advanced human healthcare applications. Micromachines 2022, 13, 346. [Google Scholar] [CrossRef] [PubMed]

- Kimoto, T. Material science and device physics in SiC technology for high-voltage power devices. Jpn. J. Appl. Phys. 2015, 54, 040103. [Google Scholar]

- Altin, N.; Ozdemir, S.; Khayamy, M.; Nasiri, A. A novel topology for solar PV inverter based on an LLC resonant converter with optimal frequency and phase-shift control. IEEE Trans. Ind. Appl. 2022, 58, 5042–5054. [Google Scholar] [CrossRef]

- Parvez, M.; Pereira, A.T.; Ertugrul, N.; Weste, N.H.E.; Abbott, D.; Al-Sarawi, S.F. Wide bandgap DC–DC converter topologies for power applications. Proc. IEEE 2021, 109, 1253–1275. [Google Scholar] [CrossRef]

- LaBella, T.; Yu, W.; Lai, J.S.; Senesky, M.; Anderson, D. A bidirectional-switch-based wide-input range high-efficiency isolated resonant converter for photovoltaic applications. IEEE Trans. Power Electron. 2013, 29, 3473–3484. [Google Scholar] [CrossRef]

- Zhao, X.; Zhang, L.; Born, R.; Lai, J.S. A high-efficiency hybrid resonant converter with wide-input regulation for photovoltaic applications. IEEE Trans. Ind. Electron. 2017, 64, 3684–3695. [Google Scholar] [CrossRef]

- Kim, S.; Kim, B.; Kwon, B.H.; Kim, M. An active voltage-doubler rectifier based hybrid resonant DC/DC converter for wide-input-range thermoelectric power generation. IEEE Trans. Power Electron. 2018, 33, 9470–9481. [Google Scholar] [CrossRef]

- Zhao, X.; Chen, C.W.; Lai, J.S. A high-efficiency active-boost-rectifier-based converter with a novel double-pulse duty cycle modulation for PV to DC microgrid applications. IEEE Trans. Power Electron. 2018, 34, 7462–7473. [Google Scholar]

- Bakeer, A.; Chub, A.; Blinov, A.; Lai, J.-S. Wide range series resonant DC–DC converter with a reduced component count and capacitor voltage stress for distributed generation. Energies 2021, 14, 2051. [Google Scholar]

- Sidorov, V.; Chub, A.; Vinnikov, D. Bidirectional isolated hexamode DC–DC converter. IEEE Trans. Power Electron. 2022, 37, 12264–12278. [Google Scholar] [CrossRef]

- Liang, S.; Yang, Y.; Shu, L.; Wu, Z.; Chen, B.; Yu, H.; Liu, H.; Wang, L.; Li, T.; Deng, G.; et al. Modeling irradiation-induced degradation for 4H-SiC power MOSFETs. IEEE Trans. Electron Devices 2023, 70, 1176–1180. [Google Scholar] [CrossRef]

- Liang, S.; Shu, L.; Wang, J.; Deng, G.; Wang, L. Dynamic degradation of planar-gate SiC MOSFETs after total ionizing dose radiation. IEEE Trans. Electron Devices 2024, 71, 4079–4086. [Google Scholar] [CrossRef]

- Peng, C.; Lei, Z.; Zhang, Z.; He, Y.; Ma, T.; Chen, Y. Bias and temperature dependence of radiation-induced degradation for SiC MOSFETs. IEEE Trans. Nucl. Sci. 2024, 71, 1186–1193. [Google Scholar] [CrossRef]

- Ugur, E.; Yang, F.; Pu, S.; Zhao, S.; Akin, B. Degradation assessment and precursor identification for SiC MOSFETs under high temperature cycling. IEEE Trans. Ind. Appl. 2019, 55, 2858–2867. [Google Scholar] [CrossRef]

- Farooq, H.; Khalid, H.A.; Ali, W.; Shahid, I. A comparative analysis of half-bridge LLC resonant converters using Si and SiC MOSFETs. Eng. Proc. 2021, 12, 43. [Google Scholar]

- Syed, S.A.; Khalid, H.A.; Farooq, H. Analytical and simulation comparison of losses in non-isolated DC/DC converter using Si and SiC switches for PV application. Eng. Proc. 2022, 20, 11. [Google Scholar]

- Farooq, H.; Khalid, H.A.; Khalid, M.U.; Syed, S.A. Efficiency analysis of GaN-based LLC resonant converter for PV applications. Eng. Proc. 2022, 20, 31. [Google Scholar]

- Pellitteri, F.; Busacca, A.; Martorana, C.; Miceli, R.; Stivala, S.; Messina, A.A.; Calabretta, M.; Vinciguerra, V. Power losses comparison between silicon carbide and silicon devices for an isolated DC–DC converter. In Proceedings of the 2021 IEEE 15th International Conference on Compatibility, Power Electronics and Power Engineering (CPE-POWERENG), Florence, Italy, 14–16 July 2021; IEEE: New York, NY, USA, 2021; pp. 1–6. [Google Scholar]

- Rashid, A.U.; Hossain, M.M.; Wu, Y.; Carlton, H.; Mantooth, A.; Brooks, B. An efficient electro-thermal compact model of SiC power MOSFETs including third quadrant behavior. IEEE Open J. Power Electron. 2022, 3, 348–367. [Google Scholar] [CrossRef]

- Mantooth, H.A.; Peng, K.; Santi, E.; Hudgins, J.L. Modeling of wide bandgap power semiconductor devices—Part I. IEEE Trans. Electron Devices 2014, 62, 423–433. [Google Scholar] [CrossRef]

- Rashid, A.U.; Hossain, M.M.; Emon, A.I.; Mantooth, H.A. Datasheet-driven compact model of silicon carbide power MOSFET including third-quadrant behavior. IEEE Trans. Power Electron. 2021, 36, 11748–11762. [Google Scholar] [CrossRef]

- Nelson, B.W.; Lemmon, A.N.; DeBoi, B.T.; Hossain, M.M.; Mantooth, H.A.; New, C.D.; Helton, J.C. Computational efficiency analysis of SiC MOSFET models in SPICE: Static behavior. IEEE Open J. Power Electron. 2020, 1, 499–512. [Google Scholar] [CrossRef]

- Powersim (PSIM). CAD Software by Powersim Inc. Available online: https://altair.com/psim (accessed on 28 December 2025).

- Pu, S.; Yang, F.; Vankayalapati, B.T.; Akin, B. Aging mechanisms and accelerated lifetime tests for SiC MOSFETs: An overview. IEEE J. Emerg. Sel. Top. Power Electron. 2021, 10, 1232–1254. [Google Scholar] [CrossRef]

- Ni, Z.; Lyu, X.; Yadav, O.P.; Cao, D. Review of SiC MOSFET based three-phase inverter lifetime prediction. In Proceedings of the 2017 IEEE Applied Power Electronics Conference and Exposition (APEC), Tampa, FL, USA, 26–30 March 2017; IEEE: New York, NY, USA, 2017; pp. 1007–1014. [Google Scholar]

- Xu, Y.; Ho, C.N.M.; Ghosh, A.; Muthumuni, D. Design, implementation, and validation of electro-thermal simulation for SiC MOSFETs in power electronic systems. IEEE Trans. Ind. Appl. 2021, 57, 2714–2725. [Google Scholar] [CrossRef]

- Trivedi, S.S.; Sant, A.V. Comparative analysis of dual active bridge DC–DC converter employing Si, SiC and GaN MOSFETs for G2V and V2G operation. Energy Rep. 2022, 8, 1011–1019. [Google Scholar] [CrossRef]

- Willers, L.R.; Silva, E.C.; e Silva, P.H.A.S.; Rocha, L.R.; Vieira, R.P. A method for SiC-MOSFET junction temperature estimation in traction inverters. In Proceedings of the IECON 2024—50th Annual Conference of the IEEE Industrial Electronics Society, Chicago, IL, USA, 3–6 November 2024; IEEE: New York, NY, USA, 2024; pp. 1–6. [Google Scholar]

- Gonzalez, J.O.; Wu, R.; Jahdi, S.; Alatise, O. Performance and reliability review of 650 V and 900 V silicon and SiC devices: MOSFETs, cascode JFETs and IGBTs. IEEE Trans. Ind. Electron. 2019, 67, 7375–7385. [Google Scholar] [CrossRef]

- Gonzalez, J.O.; Alatise, O.; Hu, J.; Ran, L.; Mawby, P.A. An investigation of temperature-sensitive electrical parameters for SiC power MOSFETs. IEEE Trans. Power Electron. 2016, 32, 7954–7966. [Google Scholar] [CrossRef]

- Gonzalez, J.O.; Alatise, O. Impact of BTI-induced threshold voltage shifts in shoot-through currents from crosstalk in SiC MOSFETs. IEEE Trans. Power Electron. 2020, 36, 3279–3291. [Google Scholar]

- Yin, S.; Tu, P.; Wang, P.; Tseng, K.J.; Qi, C.; Hu, X.; Zagrodnik, M.; Simanjorang, R. An accurate subcircuit model of SiC half-bridge module for switching-loss optimization. IEEE Trans. Ind. Appl. 2017, 53, 3840–3848. [Google Scholar] [CrossRef]

- Liang, S.; Wang, J.; Shu, L.; Yang, Y.; Wu, Z.; Li, T.; Wang, L.; Deng, G.; Fan, F.; Wang, C. Investigation on dynamic degradation of SiC MOSFETs after total ionizing dose radiation. In Proceedings of the 2023 IEEE Energy Conversion Congress and Exposition (ECCE), Nashville, TN, USA, 29 October–2 November 2023; IEEE: New York, NY, USA, 2023; pp. 5757–5762. [Google Scholar]

- Liang, X.; Cui, J.; Zheng, Q.; Zhao, J.; Yu, X.; Sun, J.; Zhang, D.; Guo, Q. Study of the influence of gamma irradiation on long-term reliability of SiC MOSFET. Radiat. Eff. Defects Solids 2020, 175, 559–566. [Google Scholar] [CrossRef]

- Luo, R.; Duan, Y.; Sun, B.; Zhang, J.Q.; Fan, J.; Liu, P. Total ionizing effects on static characteristics of 1200 V SiC MOSFET power devices with planar and trench structures. In Proceedings of the 2023 20th China International Forum on Solid State Lighting & 2023 9th International Forum on Wide Bandgap Semiconductors (SSLCHINA: IFWS), Xiamen, China, 27–30 November 2023; IEEE: New York, NY, USA, 2023; pp. 88–91. [Google Scholar]

- Shu, L.; Liao, H.L.; Wu, Z.Y.; Li, Y.Y.; Fang, X.Y.; Liang, S.W.; Li, T.D.; Wang, L.; Wang, J.; Zhao, Y.F. Comparison of gamma irradiation effects on short circuit characteristics of SiC MOSFET power devices between planar and trench structures. Electronics 2023, 12, 2891. [Google Scholar] [CrossRef]

- Yu, Q.; Ali, W.; Cao, S.; Wang, H.; Lv, H.; Sun, Y.; Mo, R.; Wang, Q.; Mei, B.; Sun, J.; et al. Application of total ionizing dose radiation test standards to SiC MOSFETs. IEEE Trans. Nucl. Sci. 2021, 69, 1127–1133. [Google Scholar] [CrossRef]

- Zhang, T.; Allard, B.; Bi, J. The synergetic effects of high temperature gate bias and total ionization dose on 1.2 kV SiC devices. Microelectron. Reliab. 2018, 88, 631–635. [Google Scholar] [CrossRef]

- Baliga, B.J. Fundamentals of Power Semiconductor Devices; Springer: Berlin/Heidelberg, Germany, 2018. [Google Scholar]

- Zhao, Z.; Wang, P.; Chen, T. A gate degradation independent online junction temperature estimation method for SiC MOSFETs based on residual resistance. IEEE Trans. Power Electron. 2024, 39, 13771–13782. [Google Scholar] [CrossRef]

- Farhadi, M.; Yang, F.; Pu, S.; Vankayalapati, B.T.; Akin, B. Temperature-independent gate-oxide degradation monitoring of SiC MOSFETs based on junction capacitances. IEEE Trans. Power Electron. 2021, 36, 8308–8324. [Google Scholar] [CrossRef]

- Wang, G.; Mookken, J.; Rice, J.; Schupbach, M. Dynamic and static behavior of packaged silicon carbide MOSFETs in paralleled applications. In Proceedings of the 2014 IEEE Applied Power Electronics Conference and Exposition—APEC 2014, Fort Worth, TX, USA, 16–20 March 2014; IEEE: New York, NY, USA, 2014; pp. 1478–1483. [Google Scholar]

- Chen, S.; Cai, C.; Wang, T.; Guo, Q.; Sheng, K. Cryogenic and high temperature performance of 4H-SiC power MOSFETs. In Proceedings of the 2013 Twenty-Eighth Annual IEEE Applied Power Electronics Conference and Exposition (APEC), Long Beach, CA, USA, 17–21 March 2013; IEEE: New York, NY, USA, 2013; pp. 207–210. [Google Scholar]

- Zhou, W.; Zhong, X.; Sheng, K. High temperature stability and the performance degradation of SiC MOSFETs. IEEE Trans. Power Electron. 2013, 29, 2329–2337. [Google Scholar] [CrossRef]

- Jiang, X.; Wang, J.; Yu, H.; Chen, J.; Zeng, Z.; Yang, X.; Shen, Z.J. Online junction temperature measurement for SiC MOSFET based on dynamic threshold voltage extraction. IEEE Trans. Power Electron. 2020, 36, 3757–3768. [Google Scholar] [CrossRef]

- Lu, X.; Wang, L.; Yang, Q.; Yang, F.; Gan, Y.; Zhang, H. Investigation and comparison of temperature-sensitive electrical parameters of SiC MOSFET at extremely high temperatures. IEEE Trans. Power Electron. 2023, 38, 9660–9672. [Google Scholar]

- Jiang, F.; Sheng, K.; Guo, Q. Comparative study of temperature-dependent characteristics for SiC MOSFETs. In Proceedings of the 2016 13th China International Forum on Solid State Lighting: International Forum on Wide Bandgap Semiconductors China (SSLChina: IFWS), Beijing, China, 15–17 November 2016; IEEE: New York, NY, USA, 2016; pp. 50–53. [Google Scholar]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2026 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license.