Abstract

This paper presents the analysis, design, and experimental validation of a Partial Power Processing (PPP) Single-Ended Primary Inductor Converter (SEPIC) for photovoltaic (PV) applications. The proposed topology limits the fraction of processed power through the active switching stage, thereby reducing MOSFET RMS current and associated conduction losses and improving overall conversion efficiency. A complete analytical framework is developed, including steady-state modeling, state-space formulation, and small-signal analysis. The theoretical results are validated through MATLAB/Simulink simulations and laboratory-scale experimental tests under multiple loading conditions. Comparative analysis against a conventional Full Power Processing (FPP) SEPIC converter demonstrates that the proposed PPP configuration achieves efficiencies up to 95% in simulation and up to 93% experimentally, compared to 87% for the FPP counterpart under identical nominal conditions ( V, kHz). Additionally, the PPP approach reduces the MOSFET RMS current by more than 50%, which directly translates into lower conduction losses and reduced device power dissipation. The results confirm that the proposed PPP-SEPIC converter constitutes a technically viable and energy-efficient solution for photovoltaic DC–DC power conversion systems.

1. Introduction

In recent years, global energy demand has increased, primarily driven by sustained population growth and the widespread electrification of modern devices and infrastructure. Simultaneously, worldwide energy consumption has been strongly associated with global warming due to emissions produced by conventional fossil-fuel-based generation systems. This environmental concern has intensified, as extreme temperature and precipitation records are increasingly reported on a yearly basis. Consequently, clean and sustainable energy sources have become a central focus of governmental policies and scientific research worldwide [1].

Among the various renewable energy sources currently deployed, hydroelectric, wind, and solar energy remain the most widely utilized technologies [2,3]. However, over the past decade, photovoltaic (PV) energy has exhibited the most rapid and sustained growth rate [4]. This expansion is largely attributed to the inherent abundance of solar resources and the continuous technological advancements in PV materials and manufacturing processes. Extensive research efforts have contributed to improving conversion efficiency while substantially reducing the cost of PV modules.

PV systems are typically interfaced with downstream power stages or the grid through multiple power conversion stages, including a DC–DC converter that regulates and adapts the voltage generated by the PV panels [5,6,7]. This stage is particularly critical because PV panels inherently produce relatively low output voltages, which must be efficiently boosted to meet grid or load requirements. Therefore, a wide range of converter topologies has been extensively developed and comparatively analyzed in the literature.

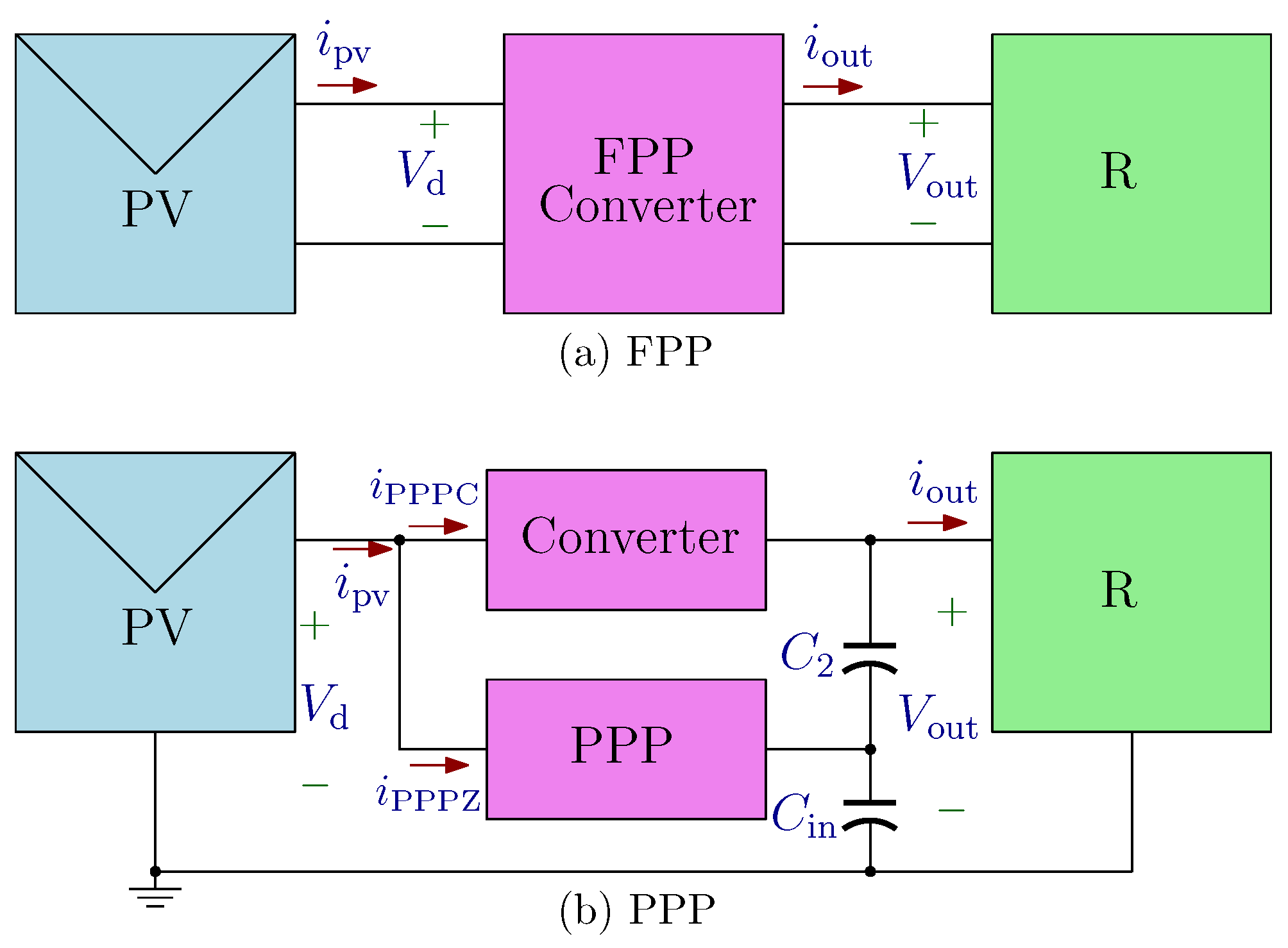

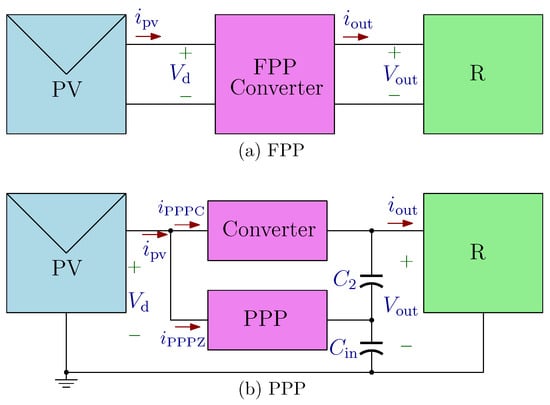

Power converters can be systematically classified according to the proportion of energy they process. Conventional Full Power Processing (FPP) converters handle the total power supplied by the source, whereas Partial Power Processing (PPP) converters process only a fraction of the transferred energy [8,9]. A general classification of these schemes is illustrated in Figure 1. Among the available PPP topologies, the PPP-SEPIC converter has attracted considerable attention due to its capability to efficiently step up voltage while reducing processed power and semiconductor stress [10,11,12].

Figure 1.

Block diagrams of two power-processing architectures: (a) Full Power Processing (FPP) and (b) Partial Power Processing (PPP). In the FPP configuration, the photovoltaic (PV) generator delivers its entire power to the converter, which fully conditions the power before delivering it to the load. In contrast, the PPP architecture allows only a fraction of the PV power to be processed by the converter.

This work introduces and evaluates a PPP-SEPIC converter specifically tailored for photovoltaic applications. Unlike its full-power counterpart, the proposed architecture confines the fraction of power processed by the active conversion stage, thereby reducing MOSFET RMS current and associated conduction losses while consistently improving overall conversion efficiency. The research focuses on the analytical design and performance evaluation of the converter, employing a partial power processing approach that inherently minimizes the amount of energy handled by the switching stage.

Although the PPP concept has been previously reported, its implementation using a SEPIC-based PPP structure for photovoltaic applications has not been thoroughly investigated under a complete analytical framework. The originality of this work therefore lies in the rigorous steady-state and small-signal modeling of the proposed topology, together with its experimental validation under a defined PV operating condition (17 V, approximately 100 W). It is important to clarify that the analytical model considers = 18 V as the nominal design value, while 17 V corresponds to the photovoltaic module operating point used in simulation and experimental validation. Furthermore, a systematic and quantitative comparison against a conventional FPP-SEPIC converter is provided, demonstrating the practical advantages of the PPP approach in terms of efficiency, component stress reduction, weight, size, and overall system cost [13].

2. Proposed PPP Architecture

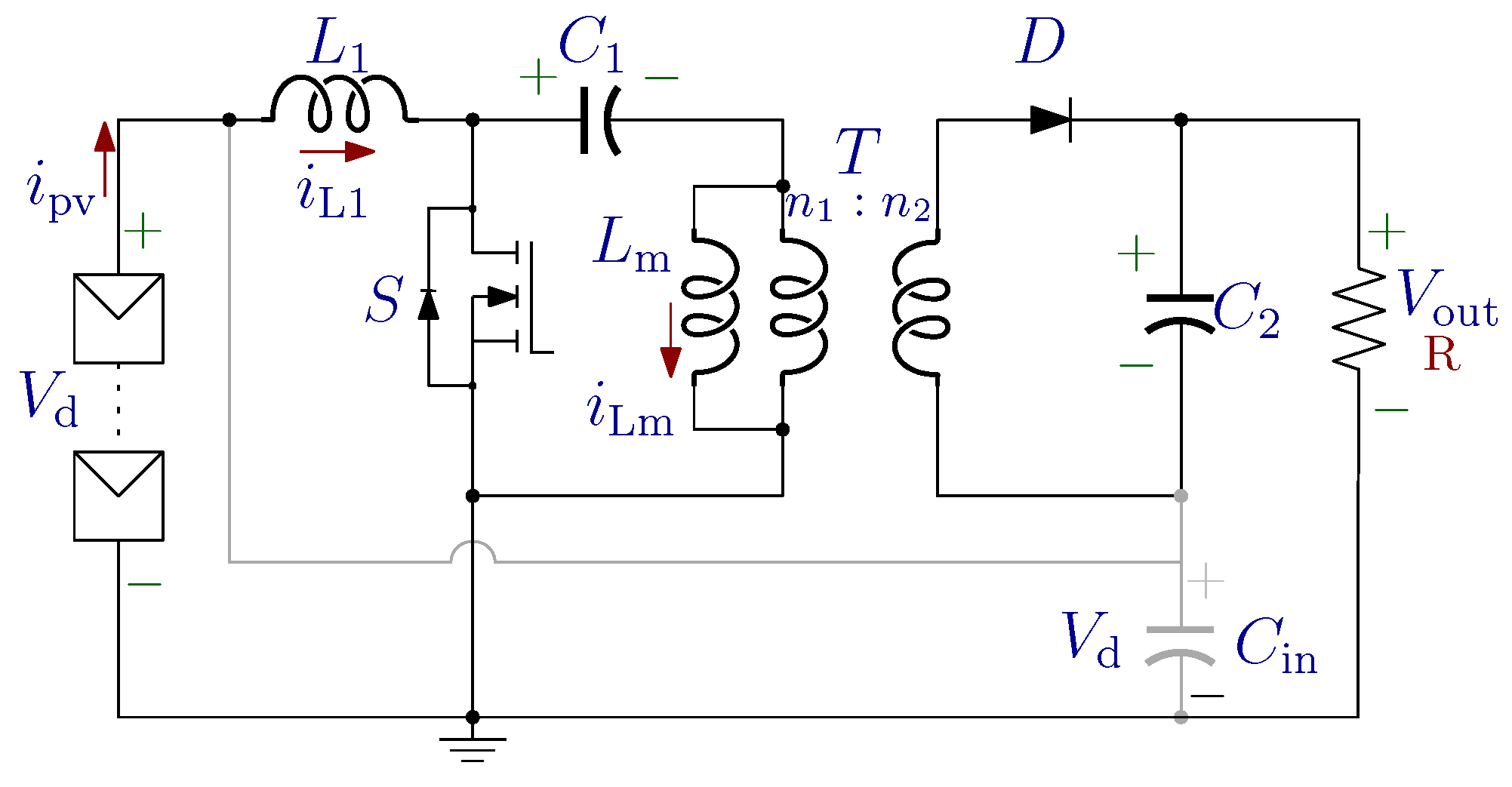

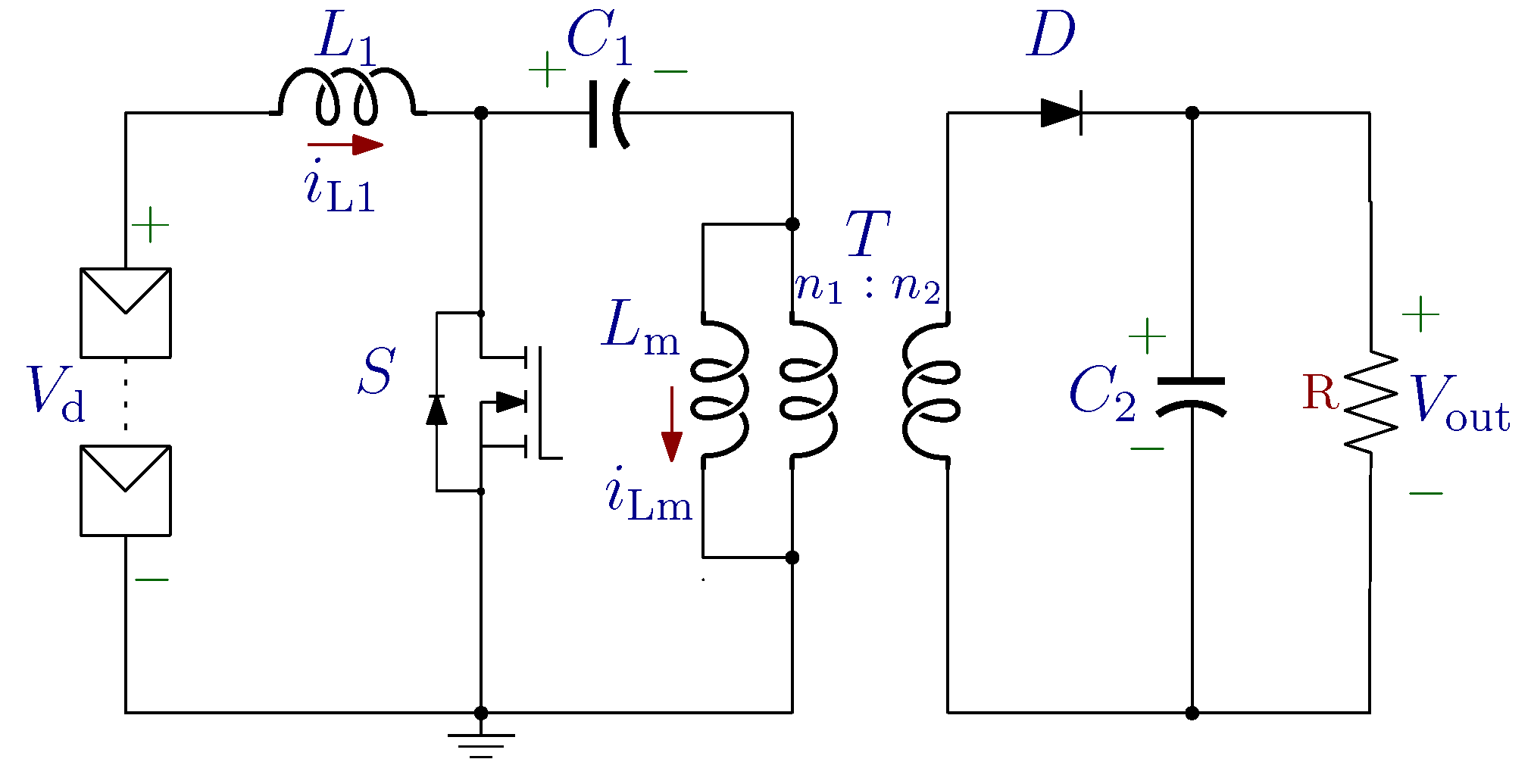

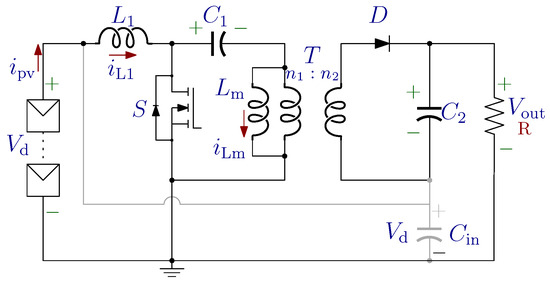

Figure 2 illustrates the proposed PPP-SEPIC architecture. Capacitor operates as the coupling element, blocking the DC component between the input branch and the active conversion path while simultaneously enabling controlled energy transfer and the inherent buck–boost functionality. Capacitor is used to filter the output voltage ripple, thereby ensuring a stable and well-regulated output voltage .

Figure 2.

Schematic diagram of the PPP-SEPIC converter with a coupled inductor (transformer). Galvanic isolation is achieved through the transformer T(: ).

The inductive elements provide controlled and continuous energy storage and delivery. Specifically, inductor smooths the current drawn from the source, thereby reducing input current ripple and improving source-side stability. Meanwhile, the magnetizing inductance of the coupled inductor (transformer) governs the energy transfer to the output and inherently limits the fraction of power processed by the active switching stage, which constitutes the core principle of PPP.

The switch is driven by a PWM control signal. The corresponding duty cycle for the control signal is defined as follows:

where is the switching period, which is related to the switching frequency by . The function denotes the PWM switching function associated with the main switch, defined as when the switch is ON and when it is OFF.

2.1. Proposed Architecture Analysis

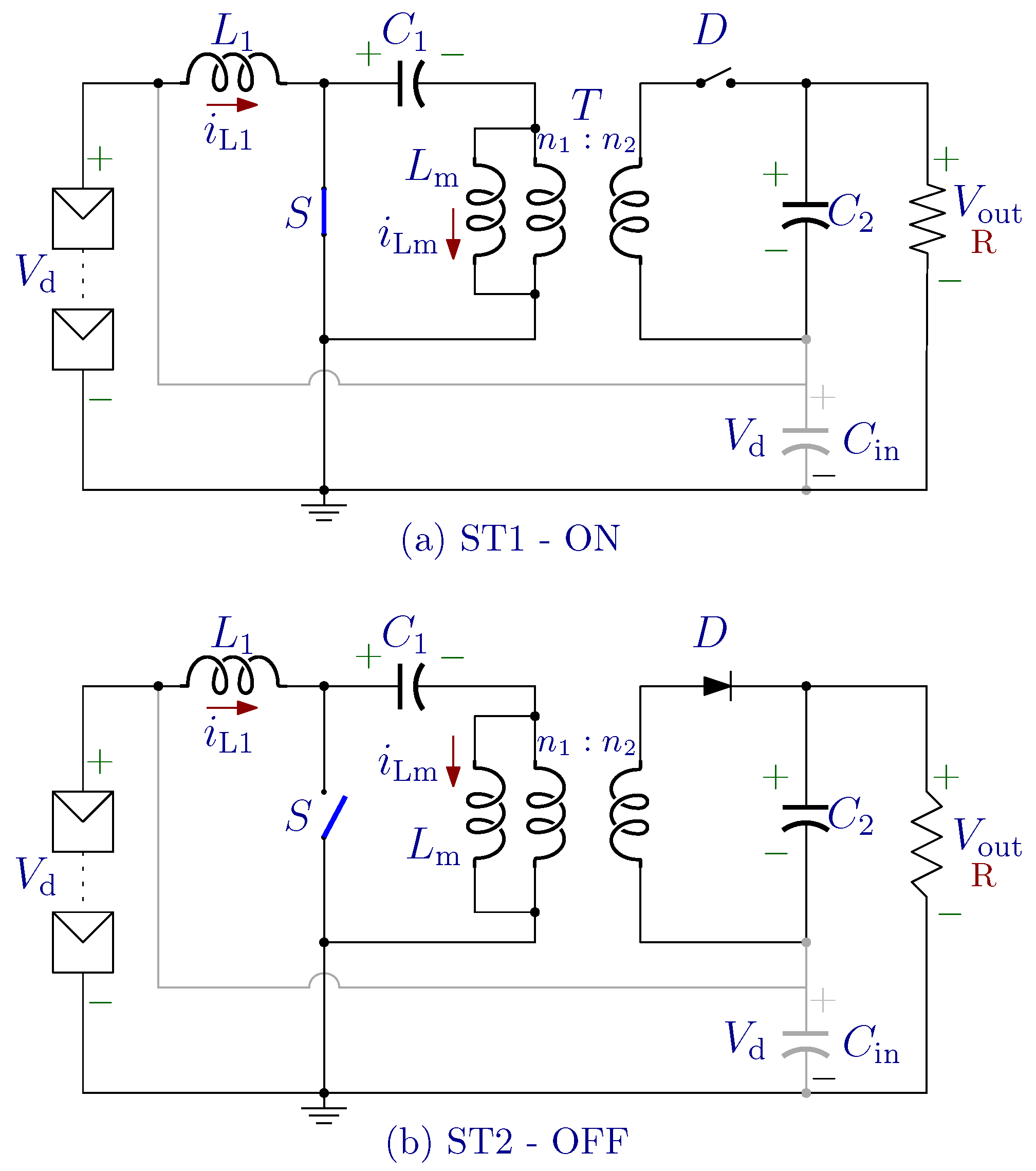

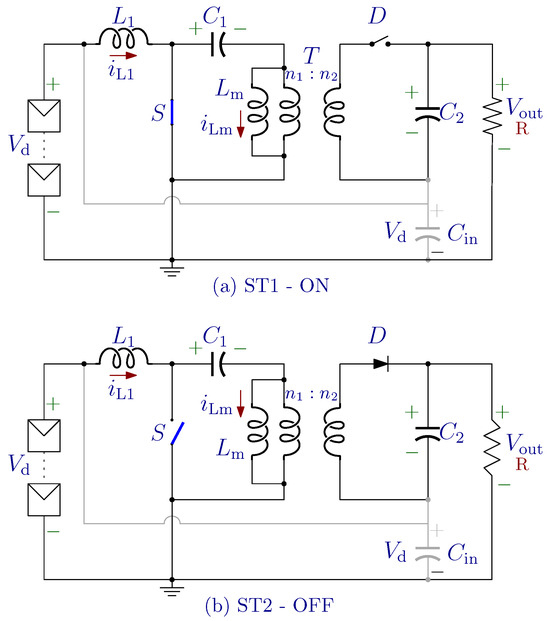

Since the proposed architecture includes only one control signal, two equivalent circuits can be obtained depending on the switch state when the converter operates in CCM. These equivalent circuits are shown in Figure 3. The converter operates in two intervals within each switching cycle:

Figure 3.

Two equivalent circuits corresponding to the switch states: (a) ST1—ON; (b) ST2—OFF.

Interval 1—Switch in conduction (ST1—ON):

When the switch is turned ON, the input inductor is directly energized by the input source, resulting in a linear increase of its current according to the applied voltage and inductance value. Simultaneously, the coupling capacitor transfers energy to the magnetizing inductance of the coupled inductor, thereby establishing controlled energy storage within the magnetic structure. During this interval, the diode remains reverse-biased, effectively isolating the output stage from the input branch. Consequently, the load R is exclusively supplied by the output capacitor , which gradually discharges to maintain the regulated output voltage. The energy stored in both and increases approximately linearly, as determined by the instantaneous voltage conditions.

Interval 2—Switch in cutoff (ST2—OFF):

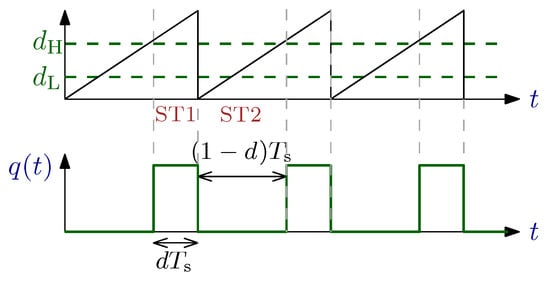

When the switch is turned OFF, the stored energy in and is simultaneously released and transferred to the output stage through the forward-biased diode. During this interval, the magnetic coupling element effectively contributes to voltage adaptation according to the transformer turns ratio, thereby modulating the output voltage level. The output capacitor is recharged while supplying the load, ensuring voltage continuity and reduced ripple. Meanwhile, capacitor is naturally recharged, preparing the converter for the subsequent switching cycle. The combined mechanism of direct and magnetically coupled energy transfer limits the fraction of total power processed by the active switching device, which constitutes the fundamental principle of PPP. Figure 4 illustrates both switching states.

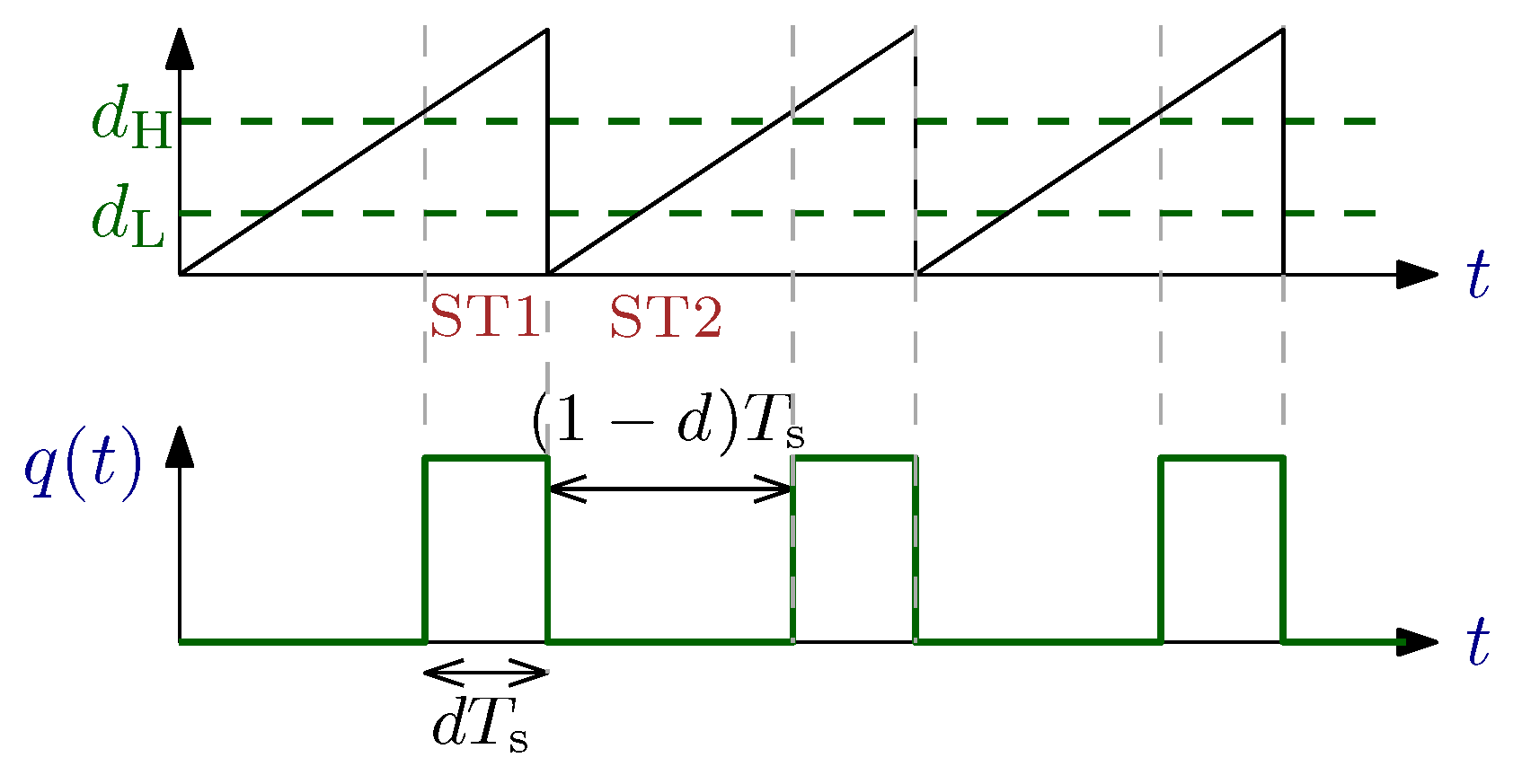

Figure 4.

Two-state modulation of the PPP-SEPIC over one switching period .The gate signal is high during ST1 (ON) for and low during ST2 (OFF) for .

Unlike a conventional boost DC–DC converter, where the entire input power is processed by the switching stage (full power processing), the proposed PPP-SEPIC topology allows a portion of the input power to be directly transferred to the load, while only a controlled fraction is processed through the active branch. The coupled transformer plays a fundamental role in this mechanism by enabling power sharing between the direct and processed paths.

The transformer not only provides galvanic isolation but also introduces an additional design degree of freedom through its turns ratio . The turns ratio is selected according to the desired output voltage and the nominal operating duty cycle. By properly choosing n, the converter can operate within a reduced duty-cycle range (approximately 0.1–0.7 in this design), which corresponds to the region of highest efficiency and reduced RMS current stress.

Therefore, the proposed topology differs conceptually from a boost converter in that it does not process the entire input power through the switching stage; instead, it regulates only a fraction of it, thereby improving overall efficiency and reducing component stress.

Table 1 presents a conceptual and structural comparison between the FPP-SEPIC and PPP-SEPIC topologies. Both converters are evaluated under identical nominal design assumptions to ensure a fair and consistent structural comparison. Although the two topologies share similar structural characteristics, the PPP-SEPIC fundamentally differs in the manner in which power is distributed between the direct and actively processed paths.

Table 1.

Architectural Comparison Between FPP-SEPIC and PPP-SEPIC Converters.

Despite employing a similar number of passive and active components and exhibiting comparable theoretical voltage conversion ratios, the PPP-SEPIC topology fundamentally differs in the manner in which power is distributed between the direct and actively processed paths. This distinct energy distribution mechanism constitutes the primary source of its performance enhancement, which is analyzed and validated in Section 4.

2.2. Architecture for Comparison

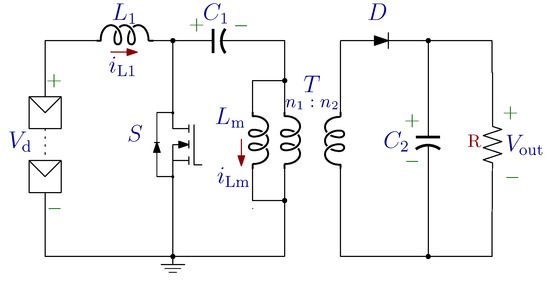

In order to thoroughly evaluate the characteristics and practical advantages of the proposed configuration, two converter topologies are comparatively analyzed. Figure 5 illustrates a conventional FPP-SEPIC converter, in which the entire energy generated by the photovoltaic source is necessarily processed through the active switching stage [14,15]. This configuration therefore represents an appropriate baseline for structurally and functionally assessing the improvements introduced by the PPP-based approach.

Figure 5.

FPP-SEPIC topology. This circuit corresponds to the FPP architecture previously illustrated in Figure 1a, where the entire PV-generated power is processed by the converter.

Previous studies have consistently reported that PPP converters can achieve high conversion efficiencies ranging from 94% to 98%. These results have been critically analyzed and systematically incorporated into the design methodology of the proposed PPP-SEPIC converter [16]. In particular, the reported efficiency benchmarks were carefully considered during the selection of the turns ratio, duty-cycle operating range, and component sizing, thereby ensuring that the proposed topology operates within its optimal efficiency region.

3. Converter Mathematical Model

Using the equations of the proposed circuit and the equivalent circuits shown in Figure 3, the averaged equations can be derived to obtain the mathematical model of the converter [17]. The averaged dynamic model for the inductor currents and capacitor voltages is presented in Equations (2)–(5).

The output current () can be calculated based on the output voltage and the load resistance, using . It is important to note that the output voltage is obtained by applying Kirchhoff’s Voltage Law (KVL) to the topology shown in Figure 2, as indicated in Equation (6) [18].

3.1. Steady State Analysis

The steady-state values for the inductor currents () and capacitor voltages () are obtained by setting the derivatives in Equations (2)–(5) to zero. Throughout the remainder of the document, uppercase letters are used to denote steady-state values. The system of equations can be more conveniently expressed in the canonical form of the state-space equations, as shown in (7) and (8), respectively. The state vector is defined by the inductor currents and capacitor voltages: . It is worth noting that the input u corresponds to the input source voltage , which is assumed to be constant, and the output y corresponds to the output voltage .

Based on (2)–(5), the state–space model can be derived as follows:

By performing the steady-state analysis and considering Equation (6), the output voltage is given by:

This expression represents the ideal steady-state voltage conversion ratio of the proposed converter. It is important to clarify that the voltage gain expression in (9) corresponds to the proposed PPP-SEPIC topology. In contrast, the conventional FPP-SEPIC follows the classical SEPIC conversion ratio given by Equation (10):

The difference arises from the distinct power-processing mechanism adopted in each topology. In the FPP configuration, the entire input power is processed by the switching stage, leading to the classical SEPIC gain. Conversely, in the PPP topology, part of the power is transferred directly through the passive path while only a fraction is processed by the active stage, resulting in an effective gain equivalent to a boost-type relationship. Therefore, although both topologies share similar structural elements, their effective voltage conversion ratios differ due to the distinct distribution of processed power.

3.2. Small-Signal AC Model

The development of the small-signal AC model can be carried out following the traditional approach, which consists of expressing the state and input variables as the sum of their DC components and small AC perturbations. This approach allows for the analysis of the system’s behavior under small disturbances and can be expressed as shown in Equation (11).

4. Loss Modeling

The efficiency of the power converter () can be readily computed as:

where and are the power consumed by the load resistor and the losses due to the inductors (), the MOSFET (), and the diode ():

Therefore, they are calculated as:

the values for inductors are .

4.1. Losses on Inductors

The losses on inductors and can be calculated using the equivalent series resistance (ESR) and the RMS value of the current through them. Since the mentioned inductors carry a triangular-shaped waveform current, the RMS can be obtained with:

4.2. Losses on the MOSFET

The losses in the MOSFET S consist of conduction losses and switching losses. The conduction losses depend on the on-state resistance and the RMS value of the current through the switch , whereas the switching losses depend on the turn-on and turn-off energy per switching event, and and the switching frequency , as given in (19). The first term represents the ohmic losses, while the second term accounts for the energy dissipated during each switching transition. The conduction losses depend on the on-state resistance and the RMS value of the current through the switch , whereas the switching losses depend on the turn-on and turn-off energy per switching event, and , respectively, together with the switching frequency , as seen in (22) and (22).

Similar to (21), the RSM is given by:

where is the average value of the current through the MOSFET, and the term is the ripple during the on-stage. It is evident that can be obtained during the on-stage: the MOSFET conducts the inductor current and , as (4) shows. Alternatively, can be calculated with:

4.3. Losses on the Diode

The losses in the diode D are mainly conduction losses, since the device does not experience active switching transitions as the MOSFET does. These conduction losses depend on the average current flowing through the diode and its forward voltage drop . Thus, the total losses on the diode can be expressed as:

In this case, the average values for the current and voltage of the diode are:

The negative sign in (30) arises from the chosen voltage reference for , which is defined with opposite polarity to the conduction direction of the diode.

4.4. Losses on the Converter

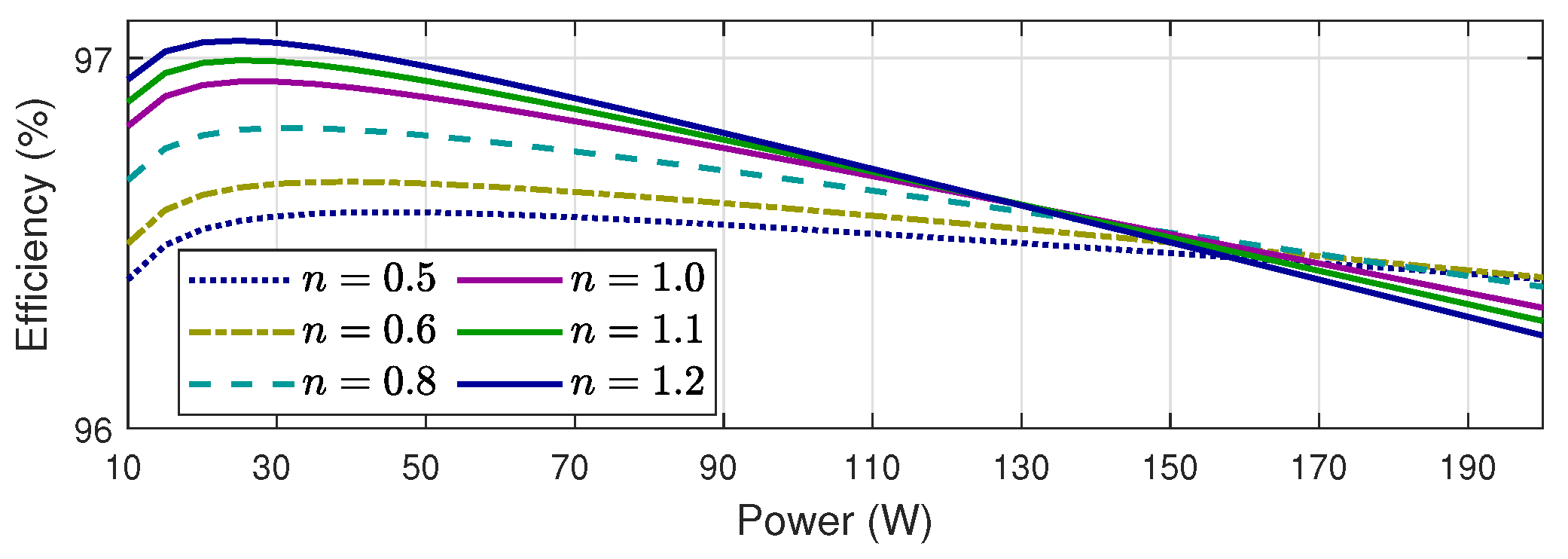

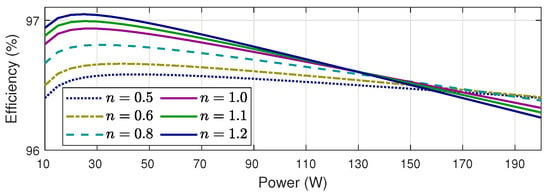

The efficiency curves in Figure 6 illustrate the behavior of the converter for different transformer turns ratios n, while maintaining a fixed duty cycle of 35%. For each operating point, the total losses are quantified using (17). Because the turns ratio directly affects the current distribution within the coupled inductors and the power stage, both the RMS current and the corresponding ripple change as n varies. The highest efficiency is presented in the range of approximately 20–80 W.

Figure 6.

Efficiency of the proposed converter as a function of output power for different turns-ratio values n.

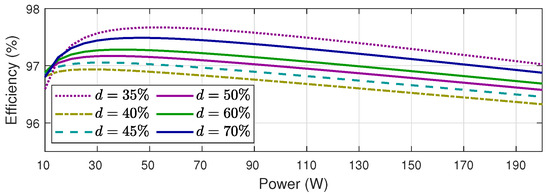

The efficiency curves in Figure 7 illustrate the behavior of the converter for different values of the duty cycle, while keeping the transformer turns ratio fixed. For each operating point, the total losses are quantified using (17). As the duty cycle changes, the average and RMS currents through the inductors and semiconductor devices are modified, which in turn affects the conduction and switching losses. Higher duty cycles tend to increase the inductor current and reduce the voltage conversion stress.

Figure 7.

Efficiency of the proposed converter as a function of output power for different duty cycle values.

At low output power, the differences among duty cycles are more pronounced due to the dominance of conduction losses. As the output power increases, efficiency decreases for all cases because inductor ESR losses and semiconductor switching losses grow with current.

5. Results and Discussion

Table 2 presents a detailed comparison between the results obtained from the averaged mathematical model and those derived from numerical simulation under different resistive load conditions. The validation is performed at nominal design parameters ( V) using a purely resistive load to ensure controlled operating conditions.

Table 2.

Comparison between the mathematical model and simulation results.

For this analysis, the input source is intentionally considered ideal in the analytical model in order to rigorously verify the accuracy of the theoretical derivation. In contrast, parasitic elements are explicitly included in the simulation model to more realistically represent practical implementation effects. Despite these modeling differences, the results exhibit a high degree of correlation between both approaches, with only minor deviations observed in the predicted voltages and currents.

These findings confirm the validity of the proposed averaged model and demonstrate its capability to accurately capture the steady-state behavior of the converter under nominal operating conditions.

In the original efficiency evaluation, a resistive load model was employed to represent the steady-state operating condition of the DC output stage. While a purely resistive load is commonly used for steady-state efficiency characterization, an additional simulation including an inductive component (R = 5 in series with L = 2 mH) has now been incorporated to address the reviewer’s concern.

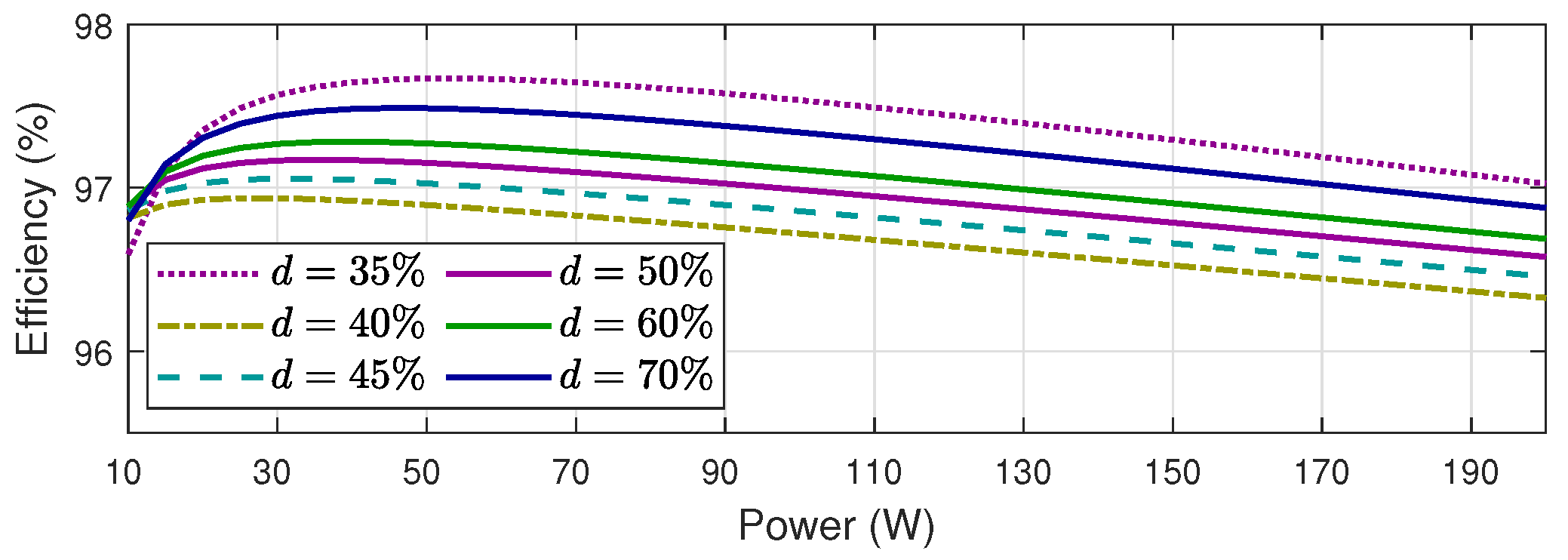

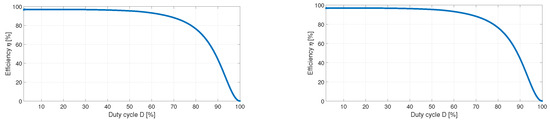

The updated results, presented in Figure 8, demonstrate that the inclusion of the inductive component does not significantly modify the steady-state efficiency behavior across the evaluated duty-cycle range. The observed deviation remains negligible, confirming that resistive-load-based efficiency analysis provides an accurate representation of steady-state performance for the proposed PPP-SEPIC converter. The maximum steady-state efficiency deviation between the resistive and RL cases remained below 1% within the nominal operating range.

Figure 8.

Efficiency comparison of the proposed PPP-SEPIC converter under two loading conditions. Left: purely resistive load (R = 5 ). Right: resistive–inductive load (R = 5 , L = 2 mH). The inclusion of the inductive component improves current continuity and modifies transient behavior; however, the steady-state efficiency variation across the evaluated duty-cycle range remains negligible.

As expected, inductive effects primarily influence transient response, while steady-state power conversion efficiency is predominantly governed by RMS currents and conduction/switching losses as derived in Section 4.

To further validate the proposed topology, a set of simulations were performed using MATLAB/Simulink R2018b. These simulations enable a direct and quantitative comparison between the FPP-SEPIC topology and the proposed PPP-SEPIC configuration. For consistency and fairness, both models were implemented using identical passive and active components, as well as the same photovoltaic panel operating under identical nominal conditions.

5.1. Switching Frequency Selection

The switching frequency of 70 kHz was selected as a practical design compromise between conversion efficiency and passive component size. Increasing the switching frequency reduces the required inductance and capacitance values, thereby enabling the use of smaller magnetic and filtering components. However, switching losses increase proportionally with frequency, since the energy dissipated during each transition accumulates with the switching rate. The switching loss can be reasonably approximated as:

Consequently, higher switching frequencies increase switching losses and may therefore reduce the overall converter efficiency. At the 100 W power level considered in this work, switching frequencies in the range of 50–100 kHz are widely adopted in silicon-based DC–DC converters to achieve a balanced trade-off between magnetic component size and switching losses. Therefore, the selected value of 70 kHz represents a technically justified operating point.

5.2. Simulation Results and Performance Comparison

A silicon-based MOSFET device was consistently considered in both the simulation and the experimental validation stages. Conduction losses were estimated based on the parameter , while switching losses were modeled as frequency-dependent according to the transition times and the corresponding operating conditions. Importantly, the same switching device model was employed for both PPP and FPP configurations to ensure a consistent comparison.

Table 3 presents a quantitative comparison between the proposed PPP-SEPIC and the conventional FPP-SEPIC topologies. Both converters were evaluated under identical photovoltaic operating conditions (, , ) to ensure a fair and controlled assessment.

Table 3.

Comprehensive comparison between FPP-SEPIC and PPP-SEPIC under identical PV operating conditions (, , ). Metrics measured over the last 200 switching cycles.

Under these conditions, the PPP configuration achieves an efficiency of 95%, compared to 87% for the FPP topology. This corresponds to total conduction and switching losses of approximately 5 W and 13 W, respectively. Furthermore, the PPP approach reduces RMS current stress on the MOSFET (−55.5%) and on the second inductor (−76.7%), while maintaining a comparable output voltage ripple. Additionally, the PPP topology exhibits lower harmonic distortion, with THD() = 1.278% compared to 2.227% for the FPP configuration, corresponding to a 42.6% reduction. Since a purely resistive load was considered, THD() matches THD(). This confirms that the PPP configuration not only reduces RMS current stress and power losses but also improves the spectral quality of the output voltage.

It is important to note that the voltage gain expressions correspond to ideal steady-state relationships. The simulated output voltages are slightly lower due to semiconductor voltage drops, winding resistances, and parasitic losses explicitly included in the model.

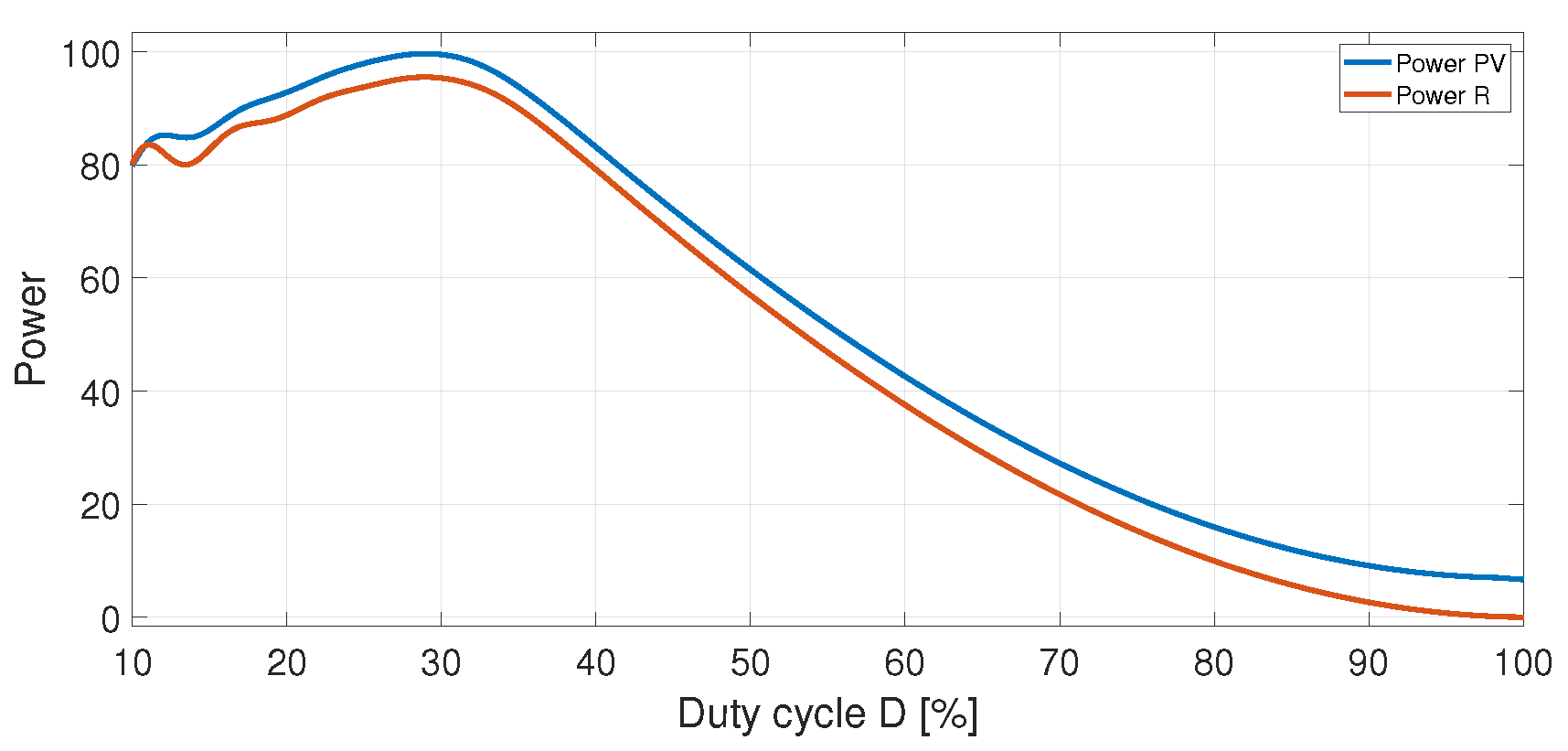

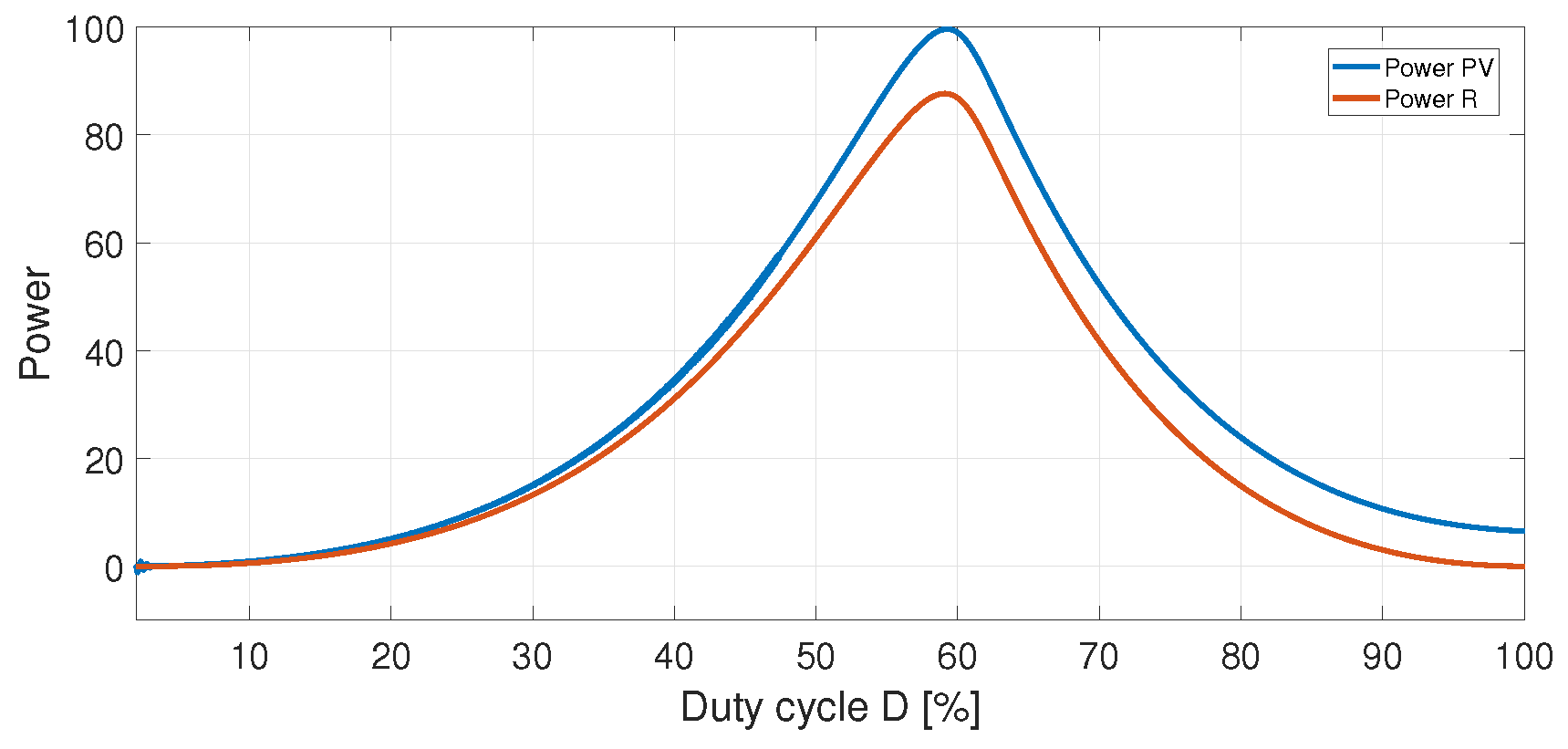

For the simulation study, the Global Solar Energy FG-2BTM-100 photovoltaic module was considered as the input source, providing a maximum output power of 100 W under nominal conditions. In the PPP-SEPIC configuration, maximum power transfer is achieved at a duty cycle of approximately 30%, whereas in the conventional FPP-SEPIC converter, the maximum power point occurs near a duty cycle of 60%.

The higher efficiency observed in the PPP-SEPIC topology can be primarily attributed to its operation at a significantly lower duty cycle [19]. Since the MOSFET conduction loss is proportional to the square of its RMS current, and the RMS current increases approximately with the square root of the duty ratio, reducing the duty cycle from about 0.60 to 0.30 nearly halves the conduction loss component, assuming comparable operating conditions.

Moreover, switching losses are inherently reduced in the PPP configuration because only a fraction of the total power flows through the active switching stage. This effectively lowers the current during turn-on and turn-off transitions, thereby decreasing the energy dissipated per switching event and improving overall efficiency. In the presented simulations, semiconductor losses were explicitly included in the device models. MOSFET conduction losses were calculated as , while the diode model incorporated both forward voltage drop and internal series resistance. Switching losses were analytically estimated as frequency-dependent based on the energy dissipated per transition. The switching transition times were obtained from the manufacturer’s datasheet of the selected MOSFET device under nominal operating conditions. Therefore, the reported efficiency values account for both conduction and switching losses in the PPP and FPP configurations.

Full parameter values are comprehensively listed in Appendix A (Table A1). The same set of electrical and magnetic parameters was consistently used for both topologies to ensure a fair and technically consistent efficiency comparison.

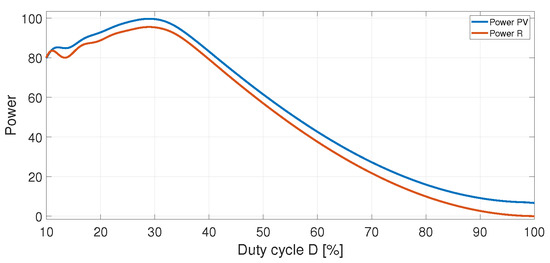

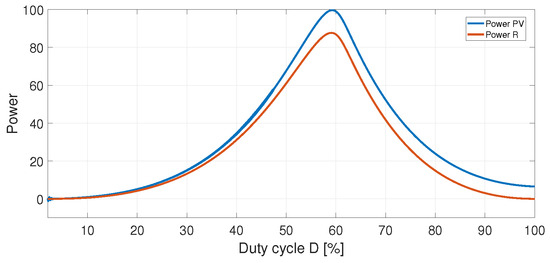

The simulation results presented in Figure 9 depict the input power (blue curve) and the power delivered to the load resistor (red curve) as a function of the duty cycle. The plot systematically illustrates the power behavior over the entire duty-cycle operating range. It can be observed that the maximum power transfer occurs at a duty cycle of approximately 30%, corresponding to the optimal operating condition of the PPP-SEPIC configuration.

Figure 9.

Simulation results (PPP-SEPIC): input and output power versus duty cycle.

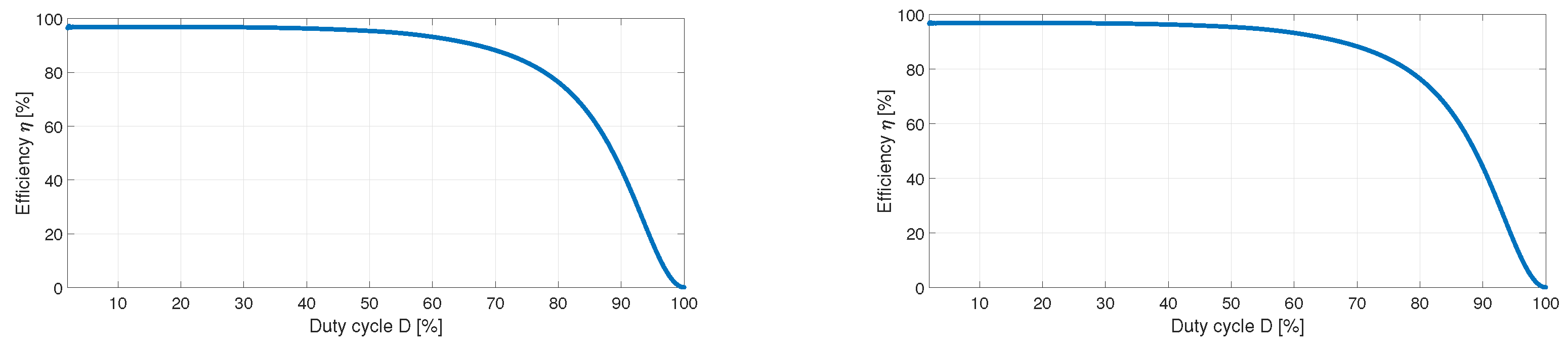

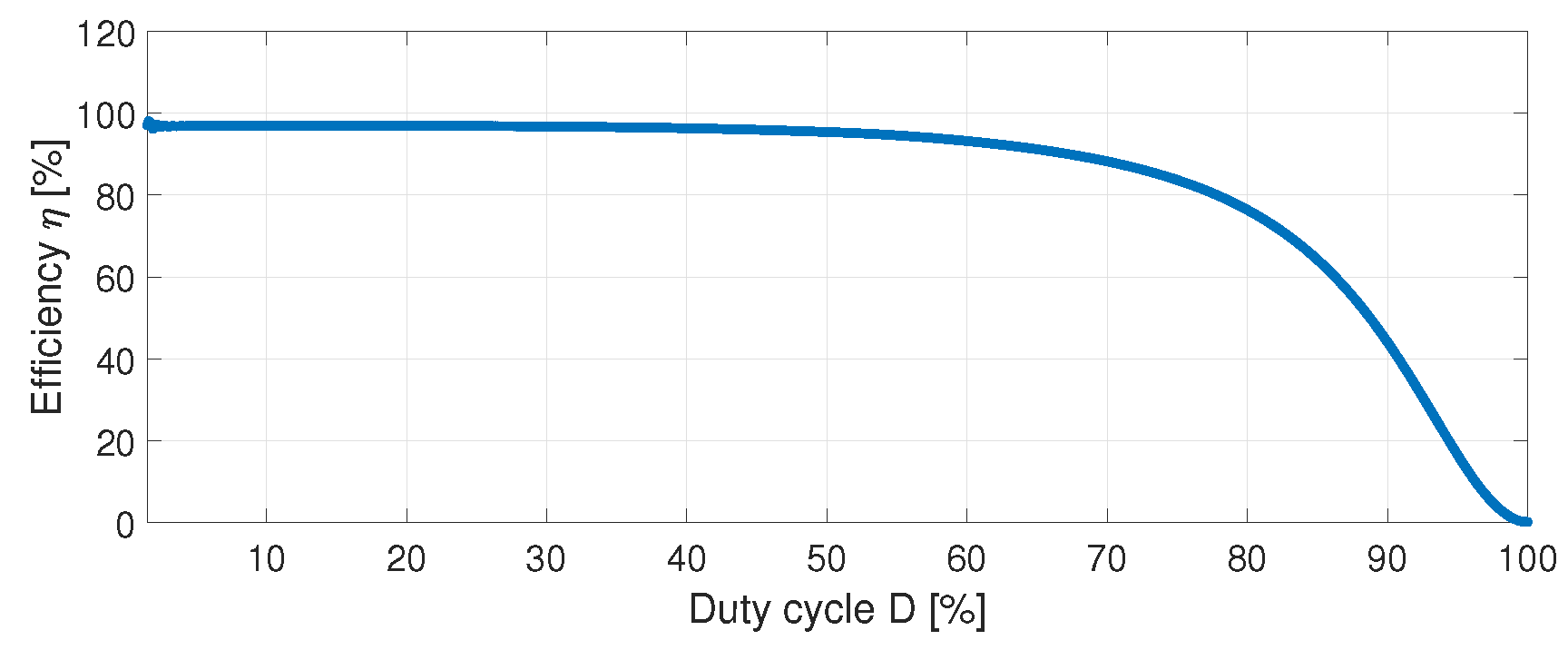

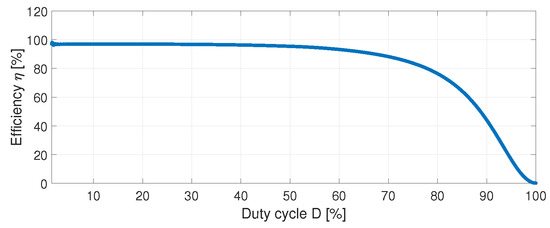

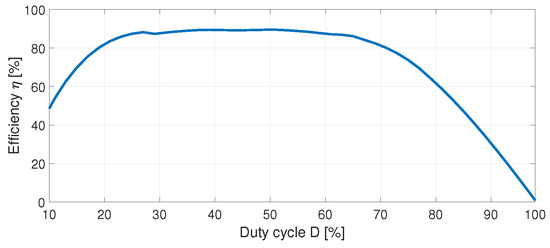

Figure 10 shows the simulated efficiency of the proposed PPP-SEPIC converter as a function of the duty cycle. The efficiency curve was obtained from the ratio between the instantaneous output and input powers, averaged over several switching periods while sweeping the duty cycle from 0 to 1.

Figure 10.

Simulated efficiency of the PPP-SEPIC converter as a function of the duty cycle.

At low duty-cycle values, a transient response is initially observed due to the energy stored in the coupling capacitors and the temporary imbalance between the current paths. Once steady-state operation is established (), the converter consistently maintains an efficiency close to 95%, thereby confirming the effective energy transfer through the partial power processing branch.

For higher duty-cycle values (), the efficiency gradually decreases as conduction losses increase in the main switching device and associated passive components. This behavior is consistent with the quadratic dependence of conduction losses on RMS current, which rises with increasing duty ratio.

Overall, these results validate the expected operational principle of the PPP-SEPIC topology, in which only a controlled fraction of the total input power flows through the active processing branch. This selective power processing mechanism effectively reduces total power losses when compared to the conventional FPP-SEPIC configuration.

Figure 11 presents the corresponding simulation results for the conventional Full Power Processing (FPP) SEPIC topology. The figure illustrates the variation of input and output power over the entire duty-cycle range. It can be clearly observed that the maximum power transfer occurs at a duty cycle of approximately 60%, which corresponds to the nominal operating region of the FPP configuration.

Figure 11.

Simulation results (FPP-SEPIC): input (PV) and output (R) power versus duty cycle.

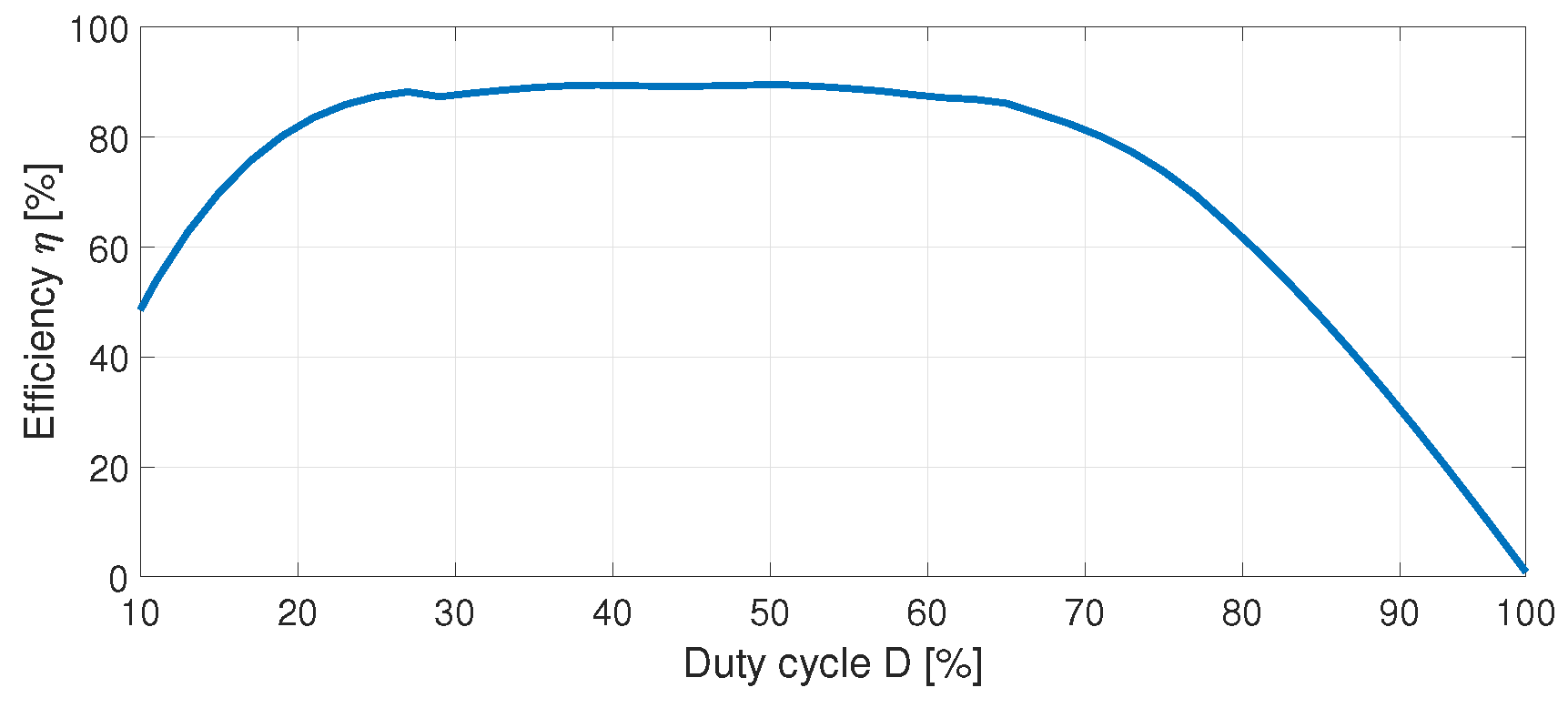

Figure 12 illustrates the simulated efficiency of the FPP-SEPIC converter as a function of the duty cycle. A relatively high-efficiency plateau is observed for duty-cycle values approximately between 0.30 and 0.60, with the highest efficiency occurring slightly above the nominal maximum power transfer point (D = 0.60), where conduction and switching losses are reasonably balanced.

Figure 12.

Simulated efficiency of the FPP-SEPIC converter as a function of the duty cycle.

As the duty cycle increases beyond 0.7, an efficiency degradation occurs due to the rapid increase in inductor RMS currents, elevated switch conduction losses, and higher diode losses associated with the inherent voltage-gain characteristic of the SEPIC topology. In this region, the converter operates under extreme step-up conditions, which lie outside the recommended design and optimal operating range. It is important to note that the maximum efficiency point does not necessarily coincide with the maximum power transfer point shown in Figure 12, since efficiency depends on the ratio between delivered power and total losses.

Therefore, the observed efficiency reduction at high duty-cycle values does not represent normal operating behavior, but rather reflects the intrinsic physical limitations of the FPP-SEPIC topology under excessive gain requirements.

Overall, the results demonstrate that the conventional full-power SEPIC converter inherently experiences higher energy losses, since the entire transferred power must be processed through the active switching device and associated passive components. This complete power processing mechanism inevitably increases conduction and switching losses, particularly under high-duty-cycle operating conditions.

In contrast, the proposed PPP-SEPIC architecture processes only a controlled fraction of the total input power, thereby reducing the current stress in the switching stage and associated magnetic elements. As a result, the converter consistently achieves higher and more stable efficiency levels—typically exceeding 90% across a wide portion of the operating range.

This comparative analysis highlights the effectiveness of the Partial Power Processing approach in minimizing conversion losses and enhancing the overall energy performance of photovoltaic power conversion systems.

5.3. Thermal, Reliability, and Scalability Considerations

Although a dedicated thermal characterization, such as infrared thermography, was not explicitly conducted in this study, the thermal performance can be reasonably inferred from the reduced processed power reported in Table 3. Since the PPP stage processes only a controlled fraction of the total input power, both the RMS and average currents in the semiconductor devices are inherently reduced compared to a conventional FPP approach.

Given that conduction losses scale approximately with , a reduction in current stress directly implies lower power dissipation. Consequently, a lower junction temperature rise can be expected under comparable operating conditions. This reduced temperature rise is strongly associated with decreased thermal stress and may therefore contribute positively to long-term reliability.

Regarding scalability, the PPP approach is particularly attractive for photovoltaic applications in which the input and output voltages are relatively close, since the fraction of processed power remains inherently limited. This characteristic helps preserve the efficiency advantages as power levels increase. Future work will include comprehensive experimental thermal validation and long-term operation testing in order to quantitatively assess lifetime-related performance metrics.

5.4. Advantages, Limitations, and Future Work

The proposed PPP-SEPIC converter offers several relevant advantages: (i) a substantially reduced processed power fraction compared to conventional FPP structures, (ii) experimentally validated efficiency improvement and measurable power loss reduction, and (iii) potentially lower semiconductor stress due to reduced device RMS currents (Table 3).

The main limitations are primarily associated with: (i) the dependency on the photovoltaic operating point and the required voltage conversion ratio, (ii) design constraints in magnetic components, such as the transformer and inductors, and (iii) the need for carefully implemented control strategies in PPP-based structures.

Future work will systematically focus on integrating advanced MPPT control strategies, experimentally validating performance at higher power levels, conducting infrared thermal characterization to quantify junction temperature trends, and performing long-term operational testing in order to evaluate reliability under realistic photovoltaic operating conditions.

6. Experimental Results

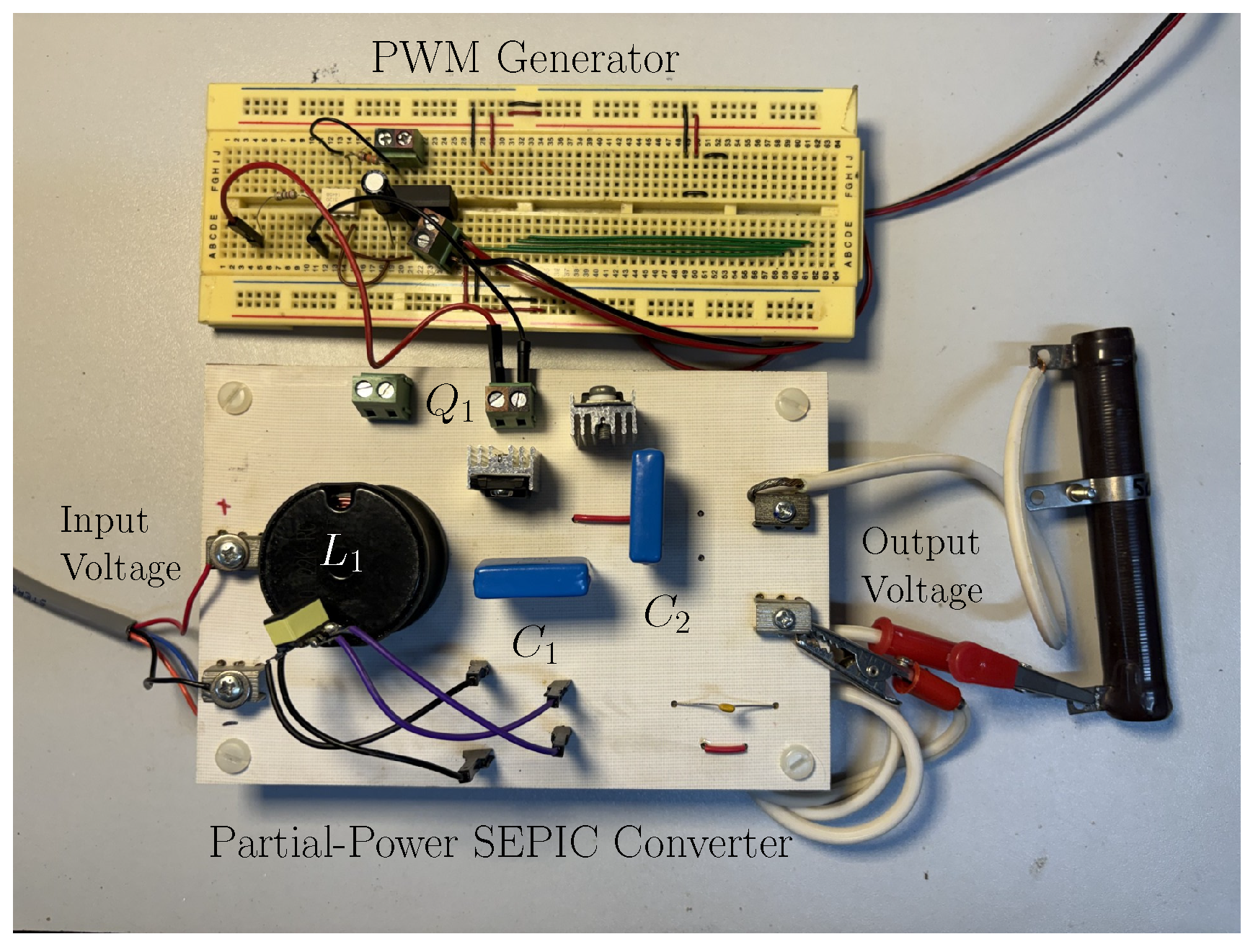

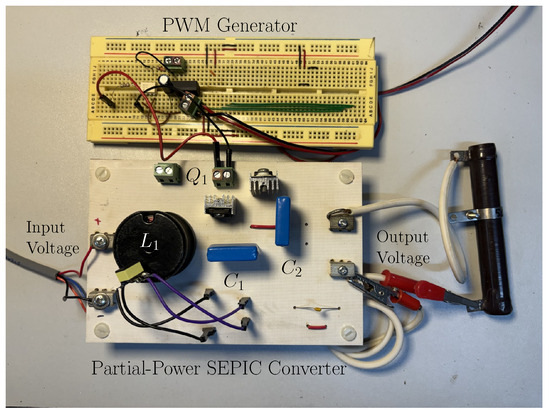

In order to validate the theoretical proposal, a laboratory-scale prototype was built and is depicted in Figure 13.

Figure 13.

Experimental prototype of the partial power processing SEPIC converter, including the PWM signal generator, passive components, measurement points, the main switch , the coupling capacitor and the output capacitor .

In order to provide a broader experimental validation under different loading conditions, additional tests were performed at multiple operating points. For each test, the input and output voltages and currents were measured using calibrated instruments, and the efficiency was calculated as , where and . The results are summarized in Table 4.

Table 4.

Experimental results for the PPP-SEPIC prototype under different input voltage levels and load conditions.

The experimental results presented in Table 4 provide a comprehensive validation of the PPP-SEPIC prototype under different input voltage levels and load conditions.

For the 100 load (Tests 1–6), the converter maintains a high efficiency across the evaluated input voltage range (15–25 V). The maximum measured efficiency (96.0%) occurs at = 17 V (Test 2), while efficiency gradually decreases to 91.6% at = 25 V (Test 6). This slight reduction at higher input voltage levels is mainly attributed to increased conduction losses, magnetic core losses, and parasitic resistive effects, which become more significant as the processed power increases.

To further evaluate the converter under higher loading conditions, additional tests were performed with reduced load resistances. For R = 50 (Test 7), operating at = 17 V and = 13.5 W, the measured efficiency was 93.0%. When the load was further reduced to 30 (Tests 8 and 9), the output power increased to approximately 19.9 W and 23.5 W, and the efficiency decreased to 87.0% and 82.0%, respectively.

The observed efficiency drop at higher output power levels is primarily associated with increased RMS currents in the semiconductor devices and magnetic elements. Since conduction losses scale proportionally with I2R, the higher current stress under low-resistance loading conditions results in increased total power dissipation. Additionally, magnetic losses and non-ideal layout parasitics inherent to the laboratory-scale prototype contribute to the efficiency reduction at elevated power levels.

It is important to emphasize that even under the highest tested power condition (Test 9), the converter maintains stable operation in continuous conduction mode (CCM), as verified experimentally.

The experimental validation of the proposed PPP-SEPIC converter was performed using a laboratory-scale prototype, as illustrated in Figure 13. The prototype was implemented to experimentally verify the analytical predictions and simulation results under controlled conditions.

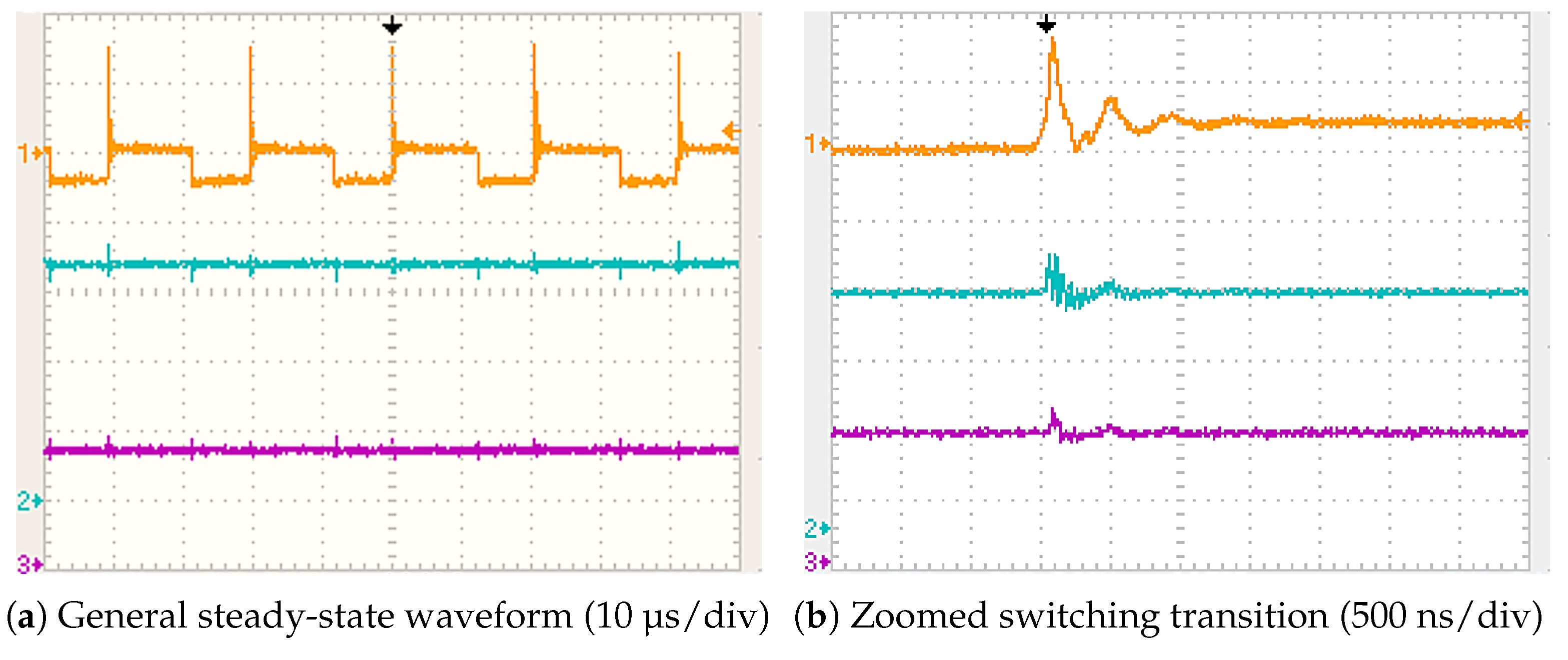

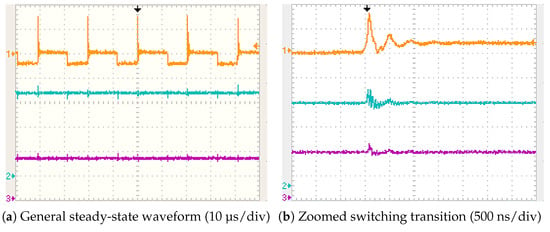

Representative steady-state waveforms corresponding to Test 7 ( = 17 V, R = 50 , = 13.5 W) are shown in Figure 14. Figure 14a presents the overall steady-state behavior (10 µs/div), confirming stable voltage regulation and controlled inductor current ripple. Figure 14b provides a zoomed view of the switching transition (500 ns/div), clearly illustrating the switching dynamics and current ripple behavior.

Figure 14.

Experimental steady-state waveforms of the PPP-SEPIC prototype corresponding to Test 1 ( = 17 V, = 13.5 W). (a) Overall steady-state operation. Channel 1 (orange): inductor current , 1 V/div. Channel 2 (cyan): voltage across coupling capacitor , 5 V/div. Channel 3 (purple): output capacitor voltage , 5 V/div. Time scale: 10 µs/div. The arrow indicates the switching instant that is magnified in subfigure (b). (b) Zoomed view of the switching transition (500 ns/div), illustrating current ripple and switching behavior. The measured switching frequency is approximately 70 kHz. The waveforms confirm continuous conduction mode (CCM) and stable partial power processing operation.

The zoomed waveform confirms the expected switching operation at approximately 70 kHz and demonstrates proper energy transfer between the direct and processed paths, validating the partial power processing principle under experimental conditions.

Overall, the experimental results validate the theoretical analysis and simulation results, confirming that the PPP-SEPIC topology achieves high efficiency under light and medium load conditions while maintaining stable operation under increased power levels.

7. Conclusions

This work has presented the complete analytical modeling, simulation, and experimental validation of a PPP-SEPIC converter for photovoltaic applications. The proposed topology was mathematically characterized using steady-state and small-signal models, providing a rigorous theoretical framework for performance evaluation.

Comparative results demonstrate that, under identical photovoltaic operating conditions, the PPP configuration significantly improves energy conversion efficiency compared to the conventional FPP-SEPIC topology. Simulation results indicate efficiencies up to 95%, while experimental validation confirms efficiencies reaching 93% under light and medium load conditions. The efficiency improvement is primarily attributed to the reduced duty-cycle operation and the partial processing of input power, which lowers RMS current stress and semiconductor losses.

Experimental tests conducted under different loading conditions further confirm stable steady-state operation and continuous conduction mode behavior. The agreement between analytical, simulation, and experimental results validates the correctness of the proposed modeling approach.

Overall, the PPP-SEPIC topology represents an effective strategy for enhancing efficiency and reducing device stress in photovoltaic DC–DC conversion systems. Future research will focus on thermal characterization, high-power scalability assessment, and advanced MPPT control integration to further evaluate long-term reliability and system-level performance.

Author Contributions

Conceptualization, J.F.R.-C. and P.M.G.-V.; methodology, J.F.R.-C. and P.M.G.-V.; software, J.F.R.-C.; validation, J.F.R.-C., P.M.G.-V., H.R.R.-C., C.C.-A. and J.d.J.C.-M.; formal analysis, J.F.R.-C. and H.R.R.-C.; investigation, J.F.R.-C.; resources, P.M.G.-V.; data curation, J.F.R.-C.; writing—original draft preparation, J.F.R.-C.; writing—review and editing, J.F.R.-C., P.M.G.-V., H.R.R.-C., C.C.-A. and J.d.J.C.-M.; visualization, J.F.R.-C.; supervision, P.M.G.-V. and J.d.J.C.-M. All authors have read and agreed to the published version of the manuscript.

Funding

This research received no external funding.

Institutional Review Board Statement

Not applicable.

Informed Consent Statement

Not applicable.

Data Availability Statement

Data are contained within the article.

Acknowledgments

The authors gratefully acknowledge the TecNM-Instituto Tecnológico de Ciudad Madero, for providing laboratory facilities and infrastructure used for the experimental validation of the proposed converter.

Conflicts of Interest

The authors declare no conflict of interest.

Abbreviations

The following abbreviations are used in this manuscript:

| PPP | Partial Power Processing |

| FPP | Full Power Processing |

| PV | Photovoltaic |

| SEPIC | Single-Ended Primary Inductor Converter |

| CCM | Continuous Conduction Mode |

Appendix A. Simulation Parameters

Table A1 lists the nominal design parameters used for theoretical modeling. The actual PV operating point in simulation slightly deviates due to the I–V characteristics of the photovoltaic module.

Table A1.

Parameters.

Table A1.

Parameters.

| Notation | Parameter | Value |

|---|---|---|

| Input voltage | 18 V | |

| Output voltage | 25 V | |

| Switching frequency | 70 kHz | |

| Input power | 100 W | |

| Capacitors | 100 F | |

| Inductor 1 | 1.27 mH | |

| Inductor 2 | 3.44 mH | |

| N-channel MOSFET (120 V, low ) | TK56A12N1 | |

| Ultrafast recovery diode (100 V, 20 A) | TS20U10CG |

References

- Elavarasan, R.M.; Shafiullah, G.; Padmanaban, S.; Kumar, N.M.; Annam, A.; Vetrichelvan, A.M.; Mihet-Popa, L.; Holm-Nielsen, J.B. A Comprehensive Review on Renewable Energy Development, Challenges, and Policies of Leading Indian States with an International Perspective. IEEE Access 2020, 8, 74432–74457. [Google Scholar] [CrossRef]

- Buticchi, G.; Lam, C.S.; Xinbo, R.; Liserre, M.; Barater, D.; Benbouzid, M.; Gomis-Bellmunt, O.; Ramos-Paja, C.A.; Kumar, C.; Zhu, R. The Role of Renewable Energy System in Reshaping the Electrical Grid Scenario. IEEE Open J. Ind. Electron. Soc. 2021, 2, 451–468. [Google Scholar] [CrossRef]

- Jana, A.K.; Saha, S. Comparative Performance analysis of Machine Learning Algorithms for stability forecasting in Decentralized Smart Grids with Renewable Energy Sources. In Proceedings of the 2024 International Conference on Electrical, Computer and Energy Technologies (ICECET), Sydney, Australia, 25–27 July 2024; IEEE: Piscataway, NJ, USA, 2024; pp. 1–7. [Google Scholar] [CrossRef]

- Ahmed, S.; Ali, A.; Ahmed Ansari, J.; Abdul Qadir, S.; Kumar, L. A Comprehensive Review of Solar Photovoltaic Systems: Scope, Technologies, Applications, Progress, Challenges, and Recommendations. IEEE Access 2025, 13, 69723–69750. [Google Scholar] [CrossRef]

- Abdel-Rahim, O.; Wang, H. A new high gain DC-DC converter with model-predictive-control based MPPT technique for photovoltaic systems. CPSS Trans. Power Electron. Appl. 2020, 5, 191–200. [Google Scholar] [CrossRef]

- Chub, A.; Hassanpour, N.; Yadav, N.; Jalakas, T.; Blinov, A.; Vinnikov, D. Analysis of Design Requirements and Optimization Possibilities of Partial Power Converter for Photovoltaic String Applications in DC Microgrids. IEEE Access 2024, 12, 14605–14619. [Google Scholar] [CrossRef]

- Anzola, J.; Aizpuru, I.; Romero, A.A.; Loiti, A.A.; Lopez-Erauskin, R.; Artal-Sevil, J.S.; Bernal, C. Review of Architectures Based on Partial Power Processing for DC-DC Applications. IEEE Access 2020, 8, 103405–103418. [Google Scholar] [CrossRef]

- Firdous, Z.; Mekhilef, S.; Siddique, M.D.; Mubin, M. Resonant and Quasi-Z Source Based Multiport Converter for High Power EV Fast Charging with Full and Partial Power Processing. IEEE Trans. Ind. Appl. 2026, 62, 1802–1815. [Google Scholar] [CrossRef]

- Carmona, R.; Rojas, C.A.; Stowhas-Villa, A.; Wilson-Veas, A.H.; Peralta, A.; Renaudineau, H.; Rivera, S. Reconfigurable Full and Partial Power Processing GaN-FET-Based T-Type DAB DC–DC Converter. IEEE J. Emerg. Sel. Top. Power Electron. 2025, 13, 7049–7062. [Google Scholar] [CrossRef]

- Santos, N.G.F.d.; Zientarski, J.R.R.; Martins, M.L.d.S. A Two-Switch Forward Partial Power Converter for Step-Up/Down String PV Systems. IEEE Trans. Power Electron. 2022, 37, 6247–6252. [Google Scholar] [CrossRef]

- dos Santos, N.G.F.; Zientarski, J.R.R.; Martins, M.L.d.S. A Review of Series-Connected Partial Power Converters for DC–DC Applications. IEEE J. Emerg. Sel. Top. Power Electron. 2022, 10, 7825–7838. [Google Scholar] [CrossRef]

- Nabinejad, A.; Rajaei, A.; Mardaneh, M. A Systematic Approach to Extract State-Space Averaged Equations and Small-Signal Model of Partial-Power Converters. IEEE J. Emerg. Sel. Top. Power Electron. 2020, 8, 2475–2483. [Google Scholar] [CrossRef]

- Zientarski, J.R.R.; Martins, M.L.d.S.; Pinheiro, J.R.; Hey, H.L. Series-Connected Partial-Power Converters Applied to PV Systems: A Design Approach Based on Step-Up/Down Voltage Regulation Range. IEEE Trans. Power Electron. 2018, 33, 7622–7633. [Google Scholar] [CrossRef]

- Mo, L.; Wang, Y.; Jiang, C.; Wang, X.; Zhang, B. A Novel Topology Derivation Method Revealed From Classical Cuk, Sepic, and Zeta Converters. IEEE Trans. Power Electron. 2024, 39, 7828–7833. [Google Scholar] [CrossRef]

- Lee, S.W.; Do, H.L. Isolated SEPIC DC–DC Converter with Ripple-Free Input Current and Lossless Snubber. IEEE Trans. Ind. Electron. 2018, 65, 1254–1262. [Google Scholar] [CrossRef]

- Zientarski, J.R.R.; da Silva Martins, M.L.; Pinheiro, J.R.; Hey, H.L. Evaluation of Power Processing in Series-Connected Partial-Power Converters. IEEE J. Emerg. Sel. Top. Power Electron. 2019, 7, 343–352. [Google Scholar] [CrossRef]

- Erickson, R.W.; Maksimovic, D. Fundamentals of Power Electronics; Kluwer Academic Publishers: Norwell, MA, USA, 2001. [Google Scholar]

- Drummond, R.; Couto, L.D.; Zhang, D. Resolving Kirchhoff’s Laws for Parallel Li-Ion Battery Pack State-Estimators. IEEE Trans. Control Syst. Technol. 2022, 30, 2220–2227. [Google Scholar] [CrossRef]

- Zhou, K.; Li, H.; Gao, S. A High-Gain DC–DC Converter with Low Duty Cycle Drive. IEEE Trans. Transp. Electrif. 2025, 11, 13298–13308. [Google Scholar] [CrossRef]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2026 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license.