A Switched-Capacitor-Based Quasi-H7 Inverter for Common-Mode Voltage Reduction

Abstract

1. Introduction

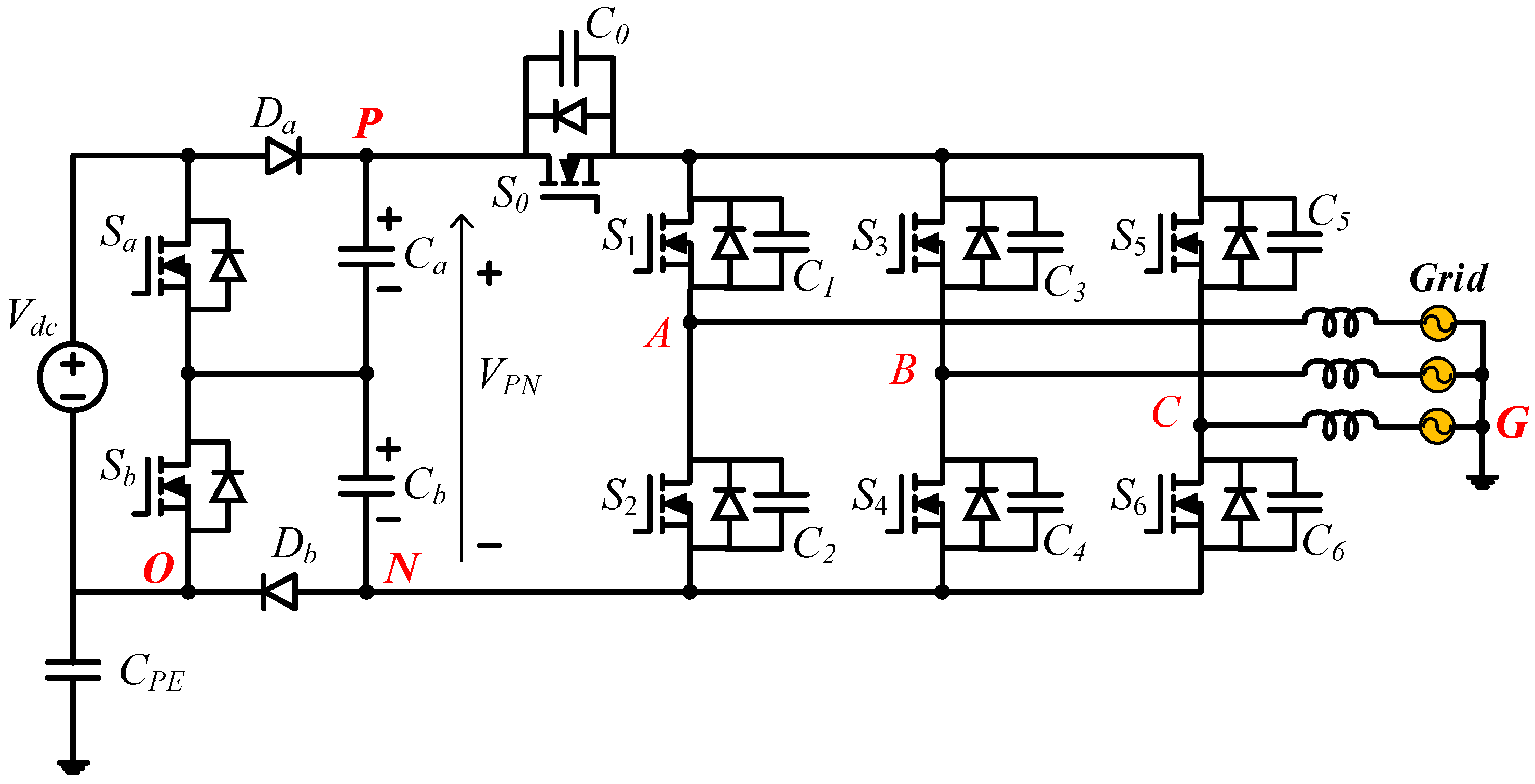

2. Topology and Operating Principle of the SC-qH7 Inverter

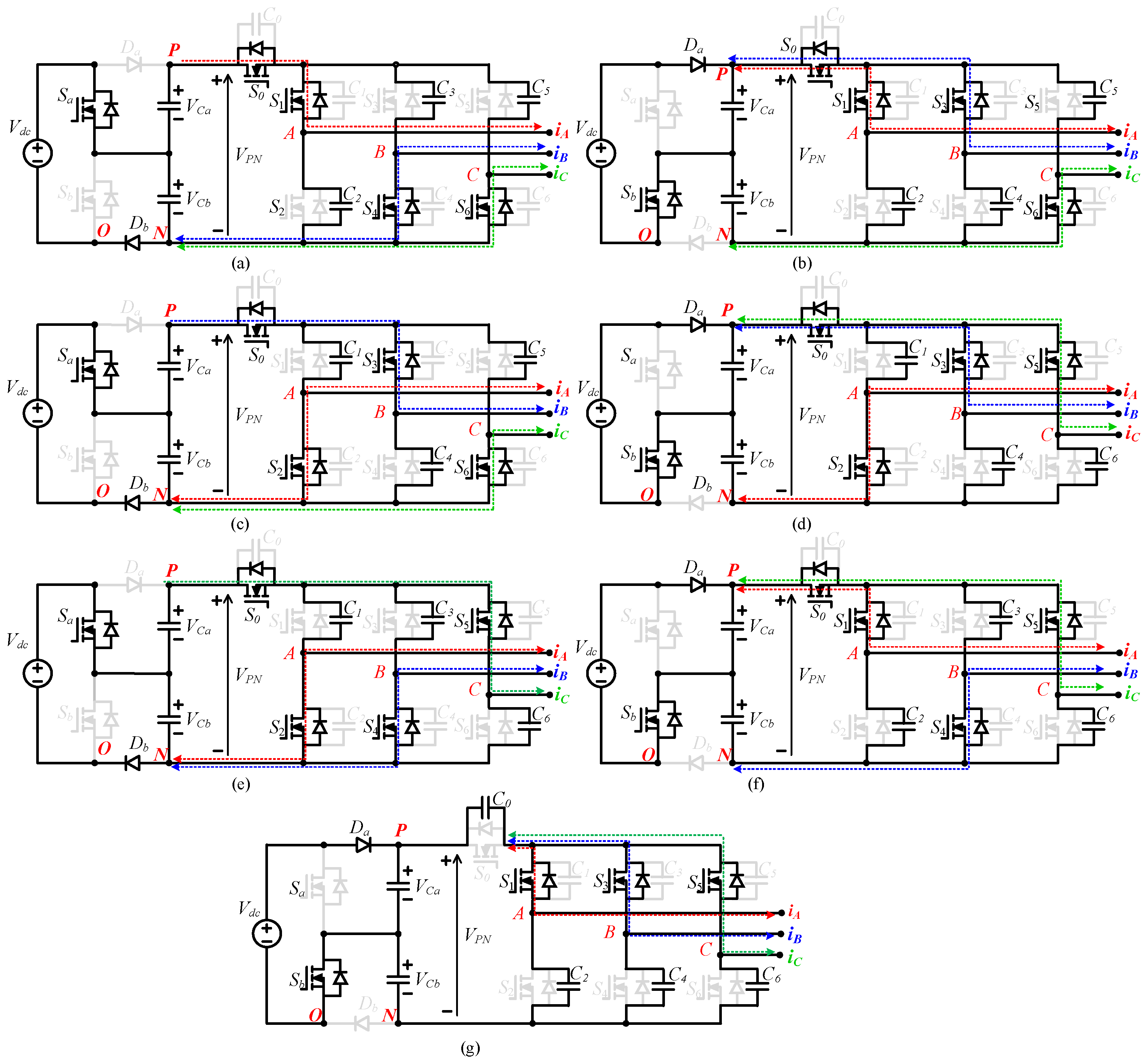

2.1. Operating Principle of Proposed SC-qH7 Inverter

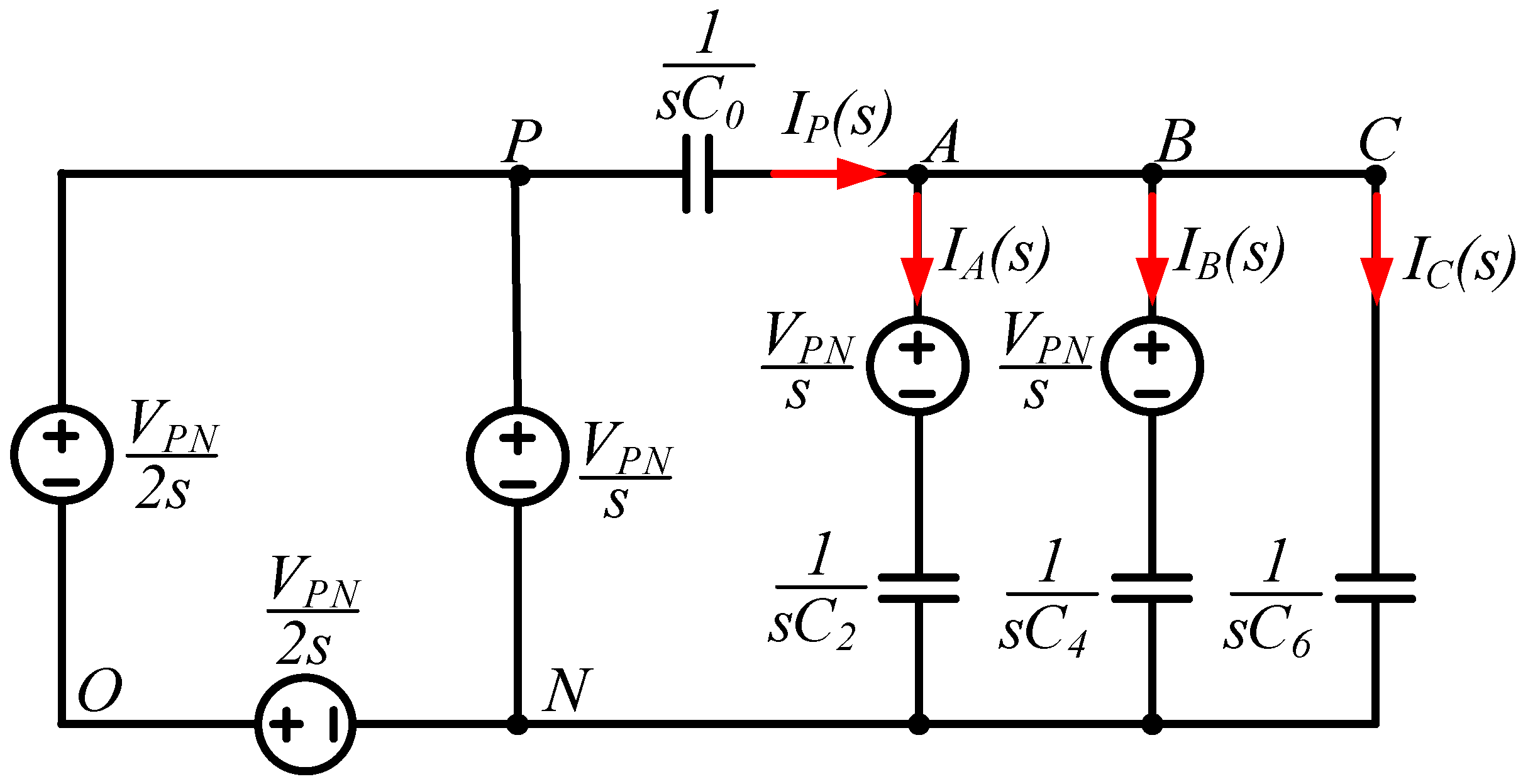

2.2. Capacitor Model During Freewheeling Mode

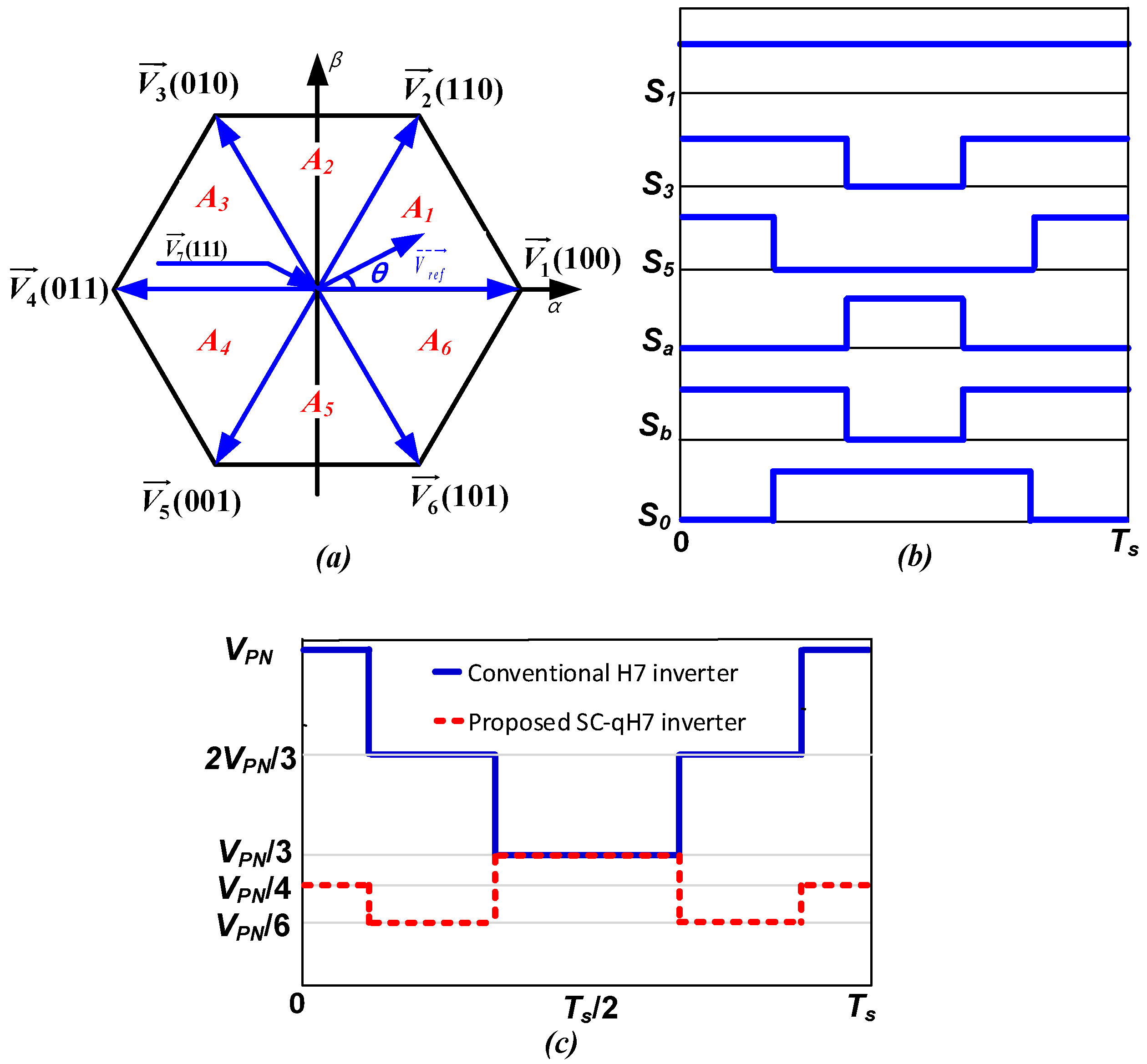

3. PWM Control Technique of SC-qH7 Inverter

4. Simulation and Experiment Results

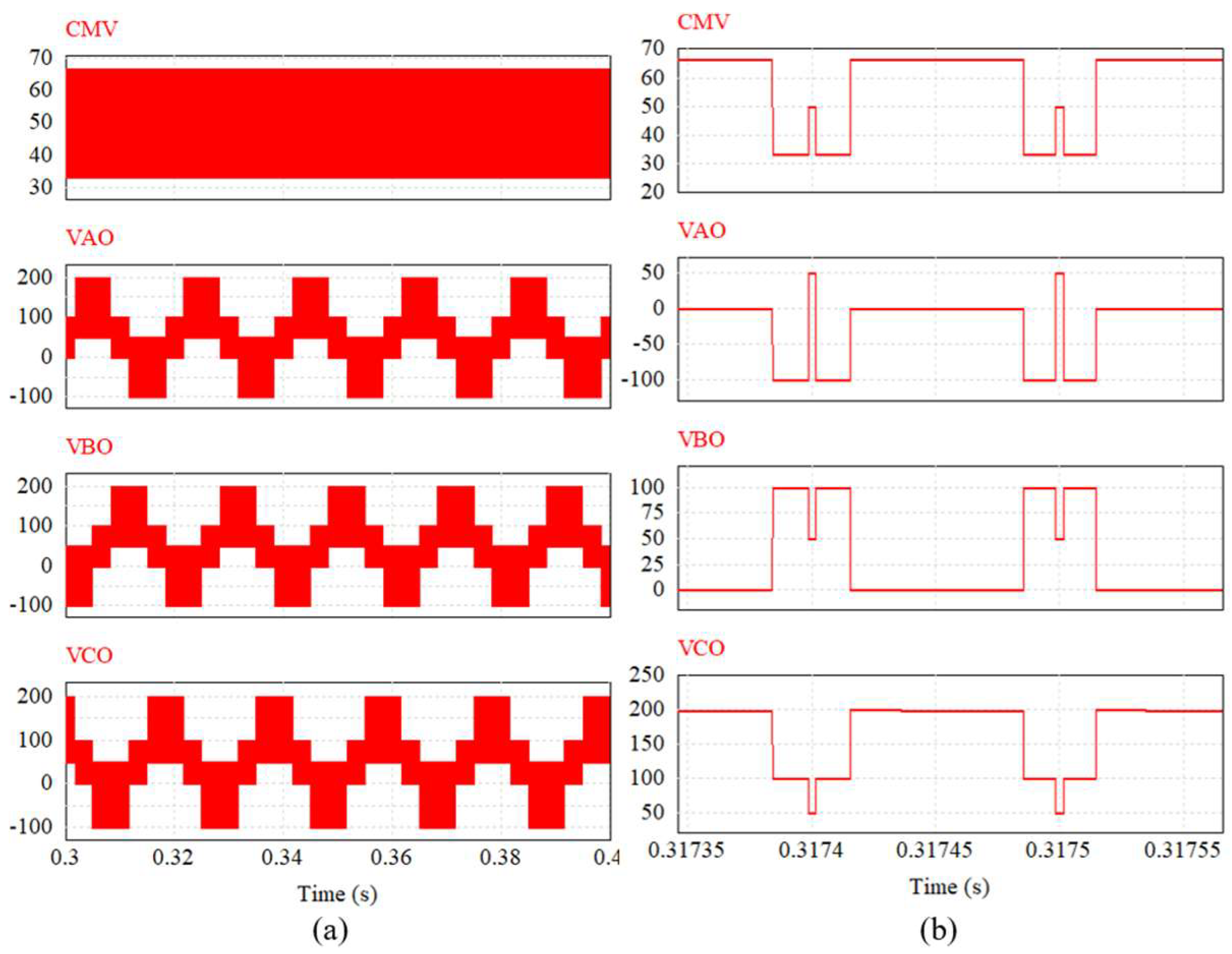

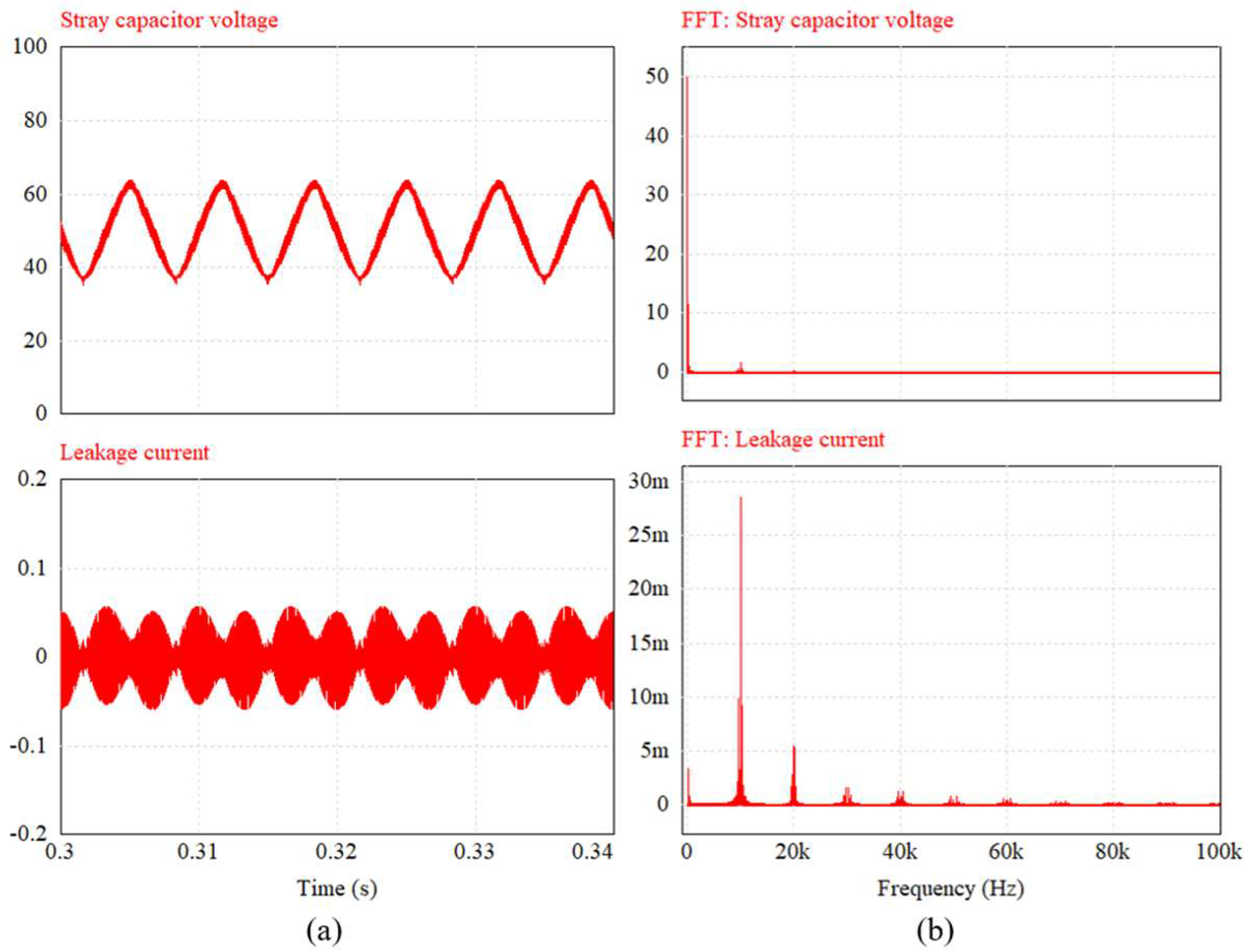

4.1. Simulation Results

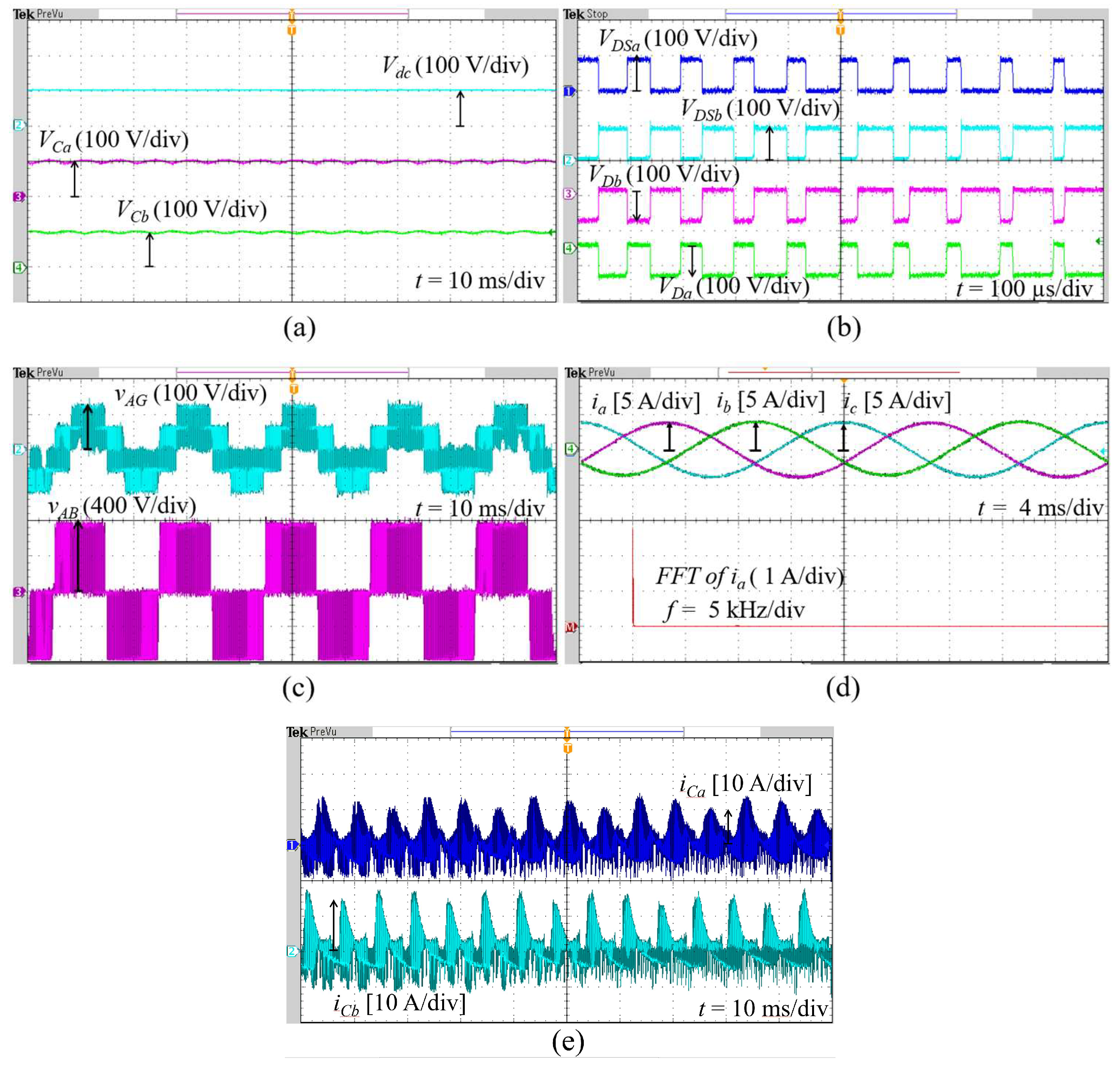

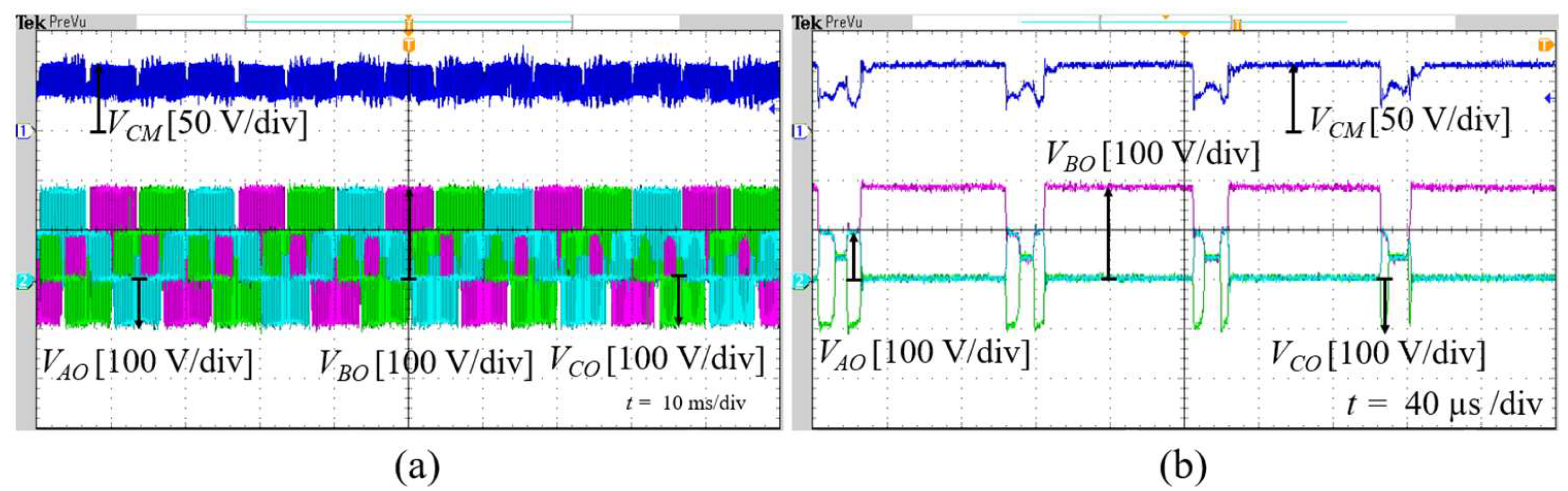

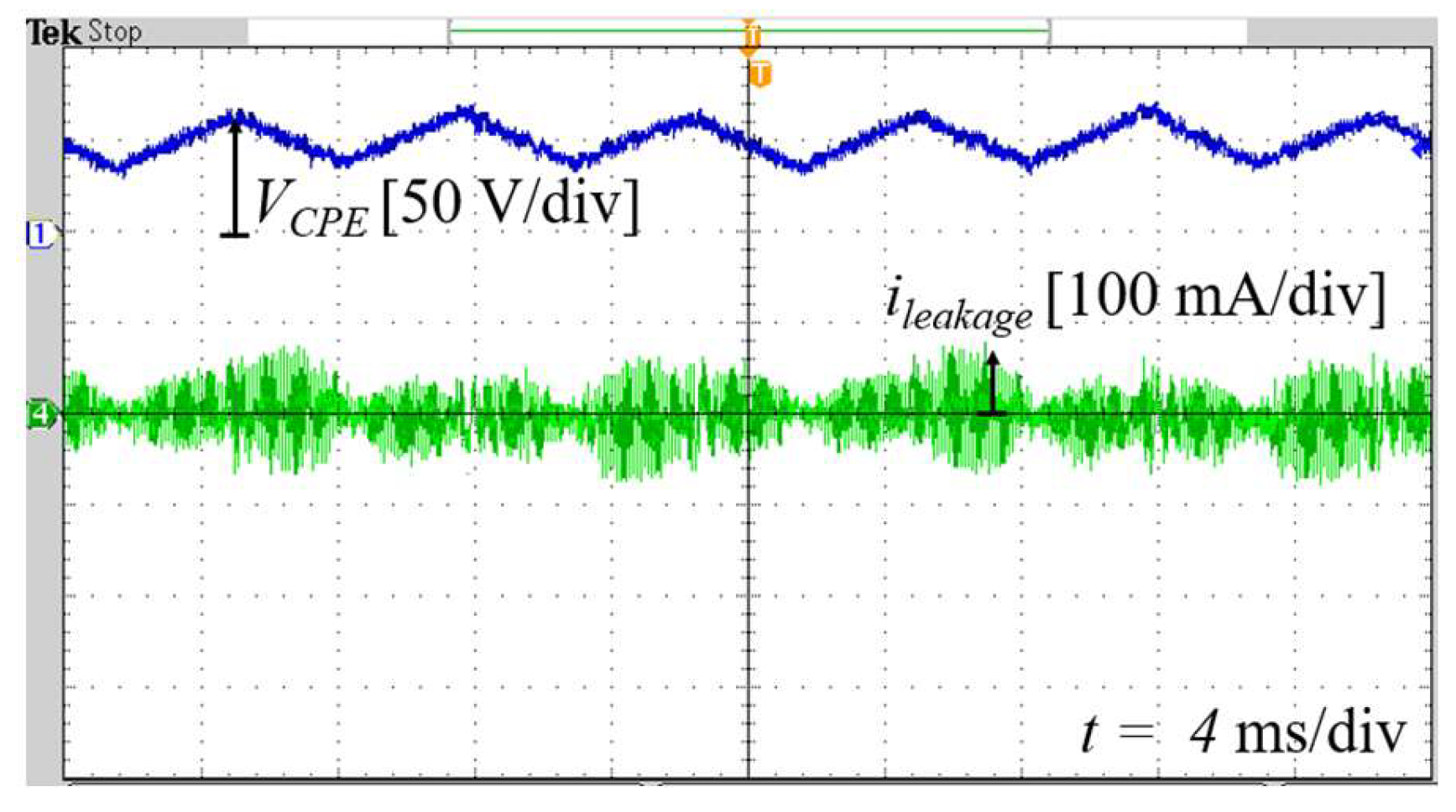

4.2. Experimental Results

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Lopez, O.; Freijedo, F.D.; Yepes, A.G.; Comesaña, P.F.; Malvar, J.; Teodorescu, R.; Gandoy, J.D. Eliminating ground current in a transformerless photovoltaic application. IEEE Trans. Energy Convers. 2010, 25, 140–147. [Google Scholar] [CrossRef]

- Yang, B.; Li, W.; Gu, Y.; Cui, W.; He, X. Improved transformerless inverter with common-mode leakage current elimination for a photovoltaic grid-connected power system. IEEE Trans. Power Electron. 2012, 27, 752–762. [Google Scholar] [CrossRef]

- Adabi, J.; Boora, A.A.; Zare, F.; Nami, A.; Ghosh, A.; Blaabjerg, F. Common-mode voltage reduction in a motor drive system with a power factor correction. IET Power Electron. 2012, 5, 366–375. [Google Scholar] [CrossRef]

- Murai, Y.; Kubota, T.; Kawase, Y. Leakage current reduction for a high-frequency carrier inverter feeding an induction motor. IEEE Trans. Ind. Appl. 1992, 28, 858–863. [Google Scholar] [CrossRef]

- Tran, T.T.; Nguyen, M.K.; Duong, T.D.; Choi, J.H.; Lim, Y.C.; Zare, F. A Switched-Capacitor-Voltage-Doubler Based Boost Inverter for Common-Mode Voltage Reduction. IEEE Access 2019, 7, 98618–98629. [Google Scholar] [CrossRef]

- Wang, L.; Shi, Y.; Shi, Y.; Xie, R.; Li, H. Ground leakage current analysis and suppression in a 60-kW 5-level T-type transformerless SiC PV inverter. IEEE Trans. Power Electron. 2018, 33, 1271–1283. [Google Scholar] [CrossRef]

- IEC 62109-2:2011; Safety for Power Converters for Use in Photovoltaic Power Systems—Part 2: Particular Requirements for Inverters. International Electrotechnical Commission: Geneva, Switzerland, 2011.

- Un, E.; Hava, A.M. Performance characteristics of the reduced common mode voltage near state PWM method. In Proceedings of the European Conference on Power Electronics and Applications, Aalborg, Denmark, 2–5 September 2007; pp. 1–10. [Google Scholar]

- Un, E.; Hava, A.M. A near-state PWM method with reduced switching losses and reduced common-mode voltage for three-phase voltage source inverters. IEEE Trans. Ind. Appl. 2009, 45, 782–793. [Google Scholar] [CrossRef]

- Janabi, A.; Wang, B. Hybrid SVPWM scheme to minimize the common-mode voltage frequency and amplitude in voltage source inverter drives. IEEE Trans. Power Electron. 2019, 34, 1595–1610. [Google Scholar] [CrossRef]

- Medekhel, L.; Hettiri, M.; Labiod, C.; Srairi, K.; Benbouzid, M. Enhancing the Performance and Efficiency of Two-Level Voltage Source Inverters: A Modified Model Predictive Control Approach for Common-Mode Voltage Suppression. Energies 2023, 16, 7305. [Google Scholar] [CrossRef]

- Zheng, J.; Peng, C.; Zhao, K.; Lyu, M. A Low Common-Mode SVPWM for Two-Level Three-Phase Voltage Source Inverters. Energies 2023, 16, 7294. [Google Scholar] [CrossRef]

- Dadu, A.M.; Mekhilef, S.; Soon, T.K.; Seyedmahmoudian, M.; Horan, B. Near State Vector Selection-Based Model Predictive Control with Common Mode Voltage Mitigation for a Three-Phase Four-Leg Inverter. Energies 2017, 10, 2129. [Google Scholar] [CrossRef]

- Xiaoqiang, G.; Ran, H.; Jiamin, J.; Zhigang, L.; Xiaofeng, S.; Guerrero, J.M. Leakage current elimination of four-leg inverter for transformerless three-phase PV systems. IEEE Trans. Power Electron. 2016, 31, 1841–1846. [Google Scholar]

- Yang, D.; Yang, K.; Gao, F. Topology Optimization Analysis of Leakage Current Suppression in Three-Level Four-Leg Photovoltaic Grid-Connected Inverter. IEEE Access 2023, 11, 50145–50156. [Google Scholar] [CrossRef]

- Freddy, T.K.S.; Rahim, N.A.; Hew, W.-P.; Che, H.S. Modulation Techniques to Reduce Leakage Current in Three-Phase Transformerless H7 Photovoltaic Inverter. IEEE Trans. Ind. Electron. 2015, 62, 322–331. [Google Scholar] [CrossRef]

- Concari, L.; Barater, D.; Buticchi, G.; Concari, C.; Liserre, M. H8 Inverter for common-mode voltage reduction in electric drives. IEEE Trans. Ind. Appl. 2016, 52, 4010–4019. [Google Scholar] [CrossRef]

- Rahimi, R.; Farhangi, S.; Farhangi, B.; Moradi, G.R.; Afshari, E.; Blaabjerg, F. H8 inverter to reduce leakage current in transformerless three-phase grid-connected photovoltaic systems. IEEE J. Emerg. Sel. Top. Power Electron. 2018, 6, 910–918. [Google Scholar] [CrossRef]

- Gupta, A.K.; Agrawal, H.; Agarwal, V. A Novel three-phase transformerless H-8 topology with reduced leakage current for grid-tied solar PV applications. IEEE Trans. Ind. Appl. 2019, 55, 1765–1774. [Google Scholar] [CrossRef]

- Ye, Y.; Cheng, K.W.E. A Family of Single-Stage Switched-Capacitor–Inductor PWM Converters. IEEE Trans. Power Electron. 2013, 28, 5196–5205. [Google Scholar] [CrossRef]

- Rosas-Caro, J.C.; Mayo-Maldonado, J.C.; Valdez-Resendiz, J.E.; Alejo-Reyes, A.; Beltran-Carbajal, F.; López-Santos, O. An Overview of Non-Isolated Hybrid Switched-Capacitor Step-Up DC–DC Converters. Appl. Sci. 2022, 12, 8554. [Google Scholar] [CrossRef]

- DIN VDE V 0126-1-1 VDE V 0126-1-1:2013-08; Automatic Disconnection Device between a Generator and the Public Low-Voltage Grid. VDE Publishing House: Berlin, Germany, 2013.

| Switching State | Bridge States (S1S3S5) | State of S7 | VCMV |

|---|---|---|---|

| State 1 | 100 | 1 | Vdc/3 |

| State 2 | 110 | 1 | 2Vdc/3 |

| State 3 | 010 | 1 | Vdc/3 |

| State 4 | 011 | 1 | 2Vdc/3 |

| State 5 | 001 | 1 | Vdc/3 |

| State 6 | 101 | 1 | 2Vdc/3 |

| State 7 | 111 | 0 | Vdc |

| Switching Mode | Switches | Diodes | Output Leg Voltage | VCM | ||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|

| S1 | S3 | S5 | Sa | Sb | S0 | Da | Db | VAN | VBN | VCN | ||

| Mode 1 | On | Off | Off | On | Off | On | Off | On | VPN | 0 | 0 | VPN/3 |

| Mode 2 | On | On | Off | Off | On | On | On | Off | VPN | VPN | 0 | VPN/6 |

| Mode 3 | Off | On | Off | On | Off | On | Off | On | 0 | VPN | 0 | VPN/3 |

| Mode 4 | Off | On | On | Off | On | On | On | Off | 0 | VPN | VPN | VPN/6 |

| Mode 5 | Off | Off | On | On | Off | On | Off | On | 0 | 0 | VPN | VPN/3 |

| Mode 6 | On | Off | On | Off | On | On | On | Off | VPN | 0 | VPN | VPN/6 |

| Mode 7 | On | On | On | Off | On | Off | Off | On | 0 | 0 | 0 | VPN/4 |

| Sector | Switching Sequence |

|---|---|

| A1 | (111) |

| A2 | (111) |

| A3 | (111) |

| A4 | (111) |

| A5 | (111) |

| A6 | (111) |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Nguyen, T.-T.N.; Tran, T.-T.; Ngo, M.-D.; Ahn, S.-J. A Switched-Capacitor-Based Quasi-H7 Inverter for Common-Mode Voltage Reduction. Energies 2025, 18, 3218. https://doi.org/10.3390/en18123218

Nguyen T-TN, Tran T-T, Ngo M-D, Ahn S-J. A Switched-Capacitor-Based Quasi-H7 Inverter for Common-Mode Voltage Reduction. Energies. 2025; 18(12):3218. https://doi.org/10.3390/en18123218

Chicago/Turabian StyleNguyen, Thi-Thanh Nga, Tan-Tai Tran, Minh-Duc Ngo, and Seon-Ju Ahn. 2025. "A Switched-Capacitor-Based Quasi-H7 Inverter for Common-Mode Voltage Reduction" Energies 18, no. 12: 3218. https://doi.org/10.3390/en18123218

APA StyleNguyen, T.-T. N., Tran, T.-T., Ngo, M.-D., & Ahn, S.-J. (2025). A Switched-Capacitor-Based Quasi-H7 Inverter for Common-Mode Voltage Reduction. Energies, 18(12), 3218. https://doi.org/10.3390/en18123218