Composite Sinusoidal Waveform Generated by Direct Digital Synthesis for Healthy Charging of Lithium-Ion Batteries

Abstract

1. Introduction

2. Methods

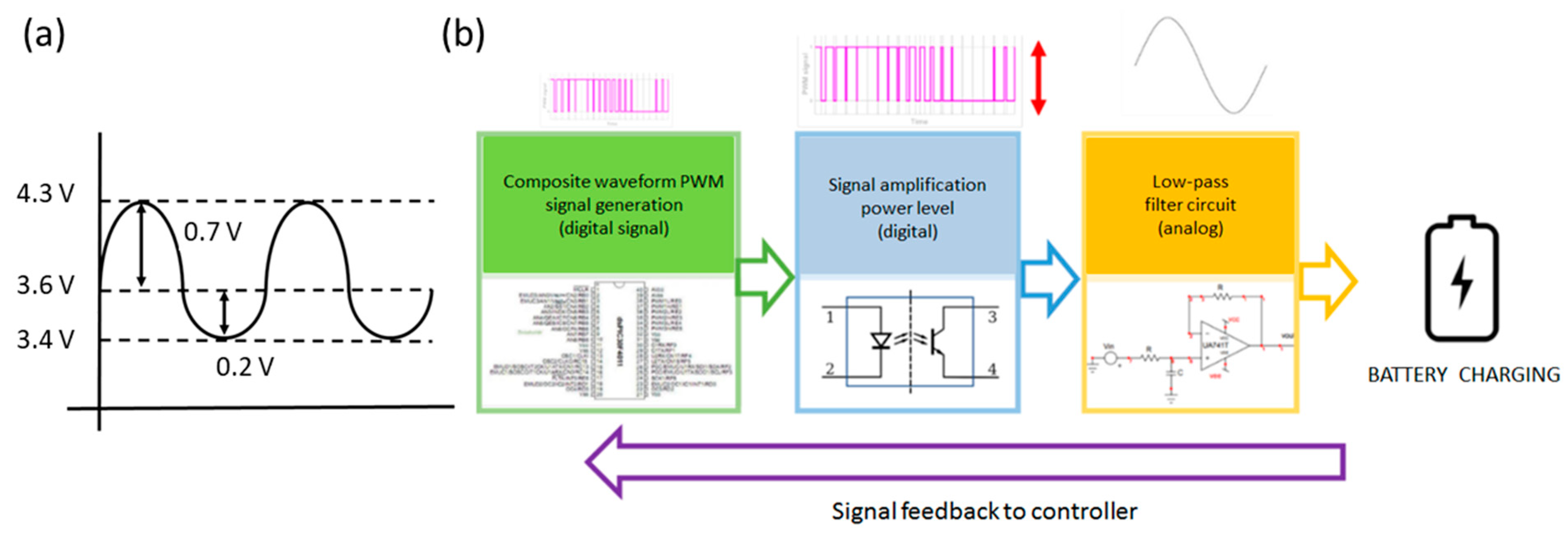

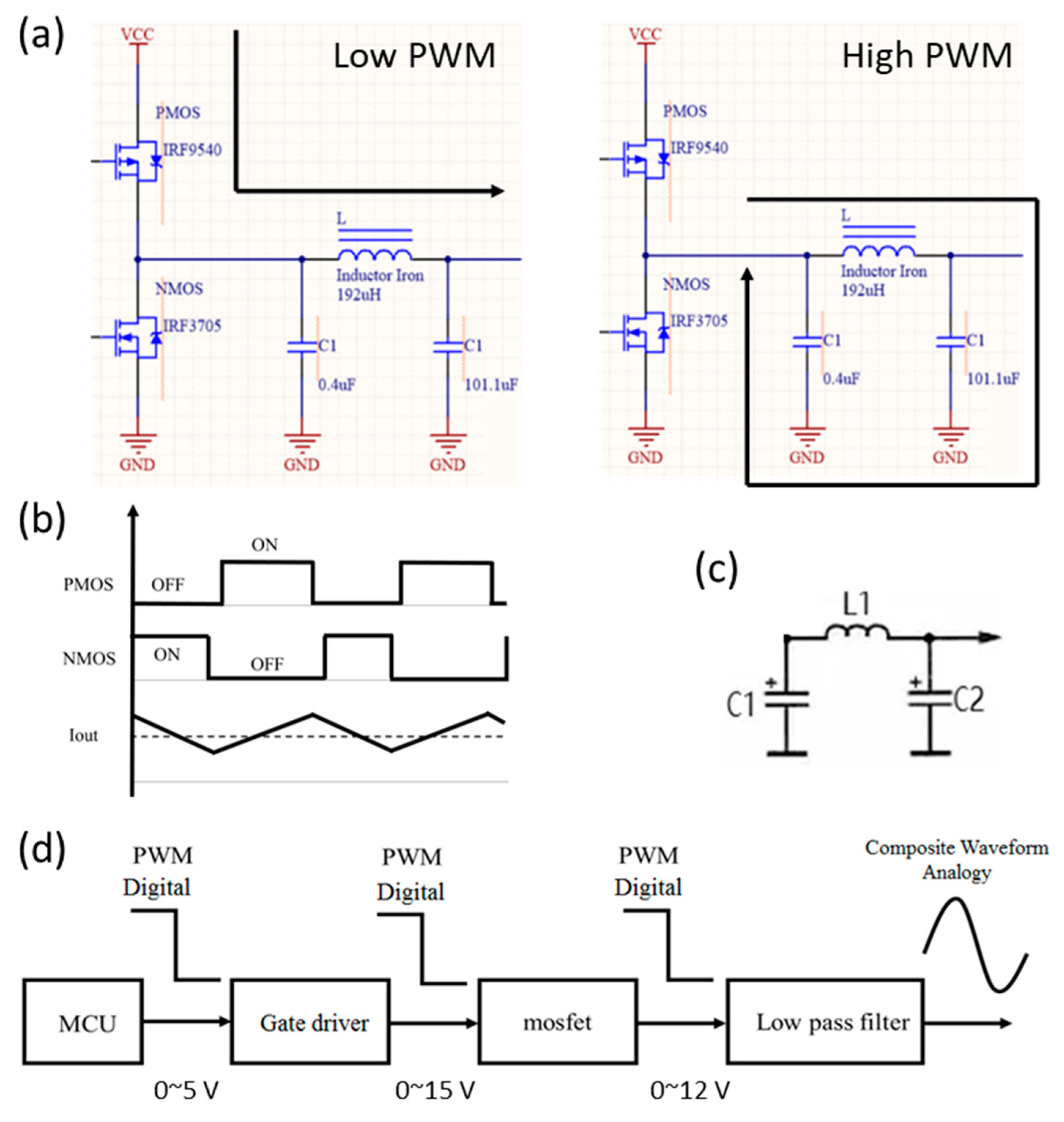

2.1. Direct Digital Synthesis (DDS) and Buck Converter

2.2. Waveform Generation

2.3. Design of the Charging Circuit

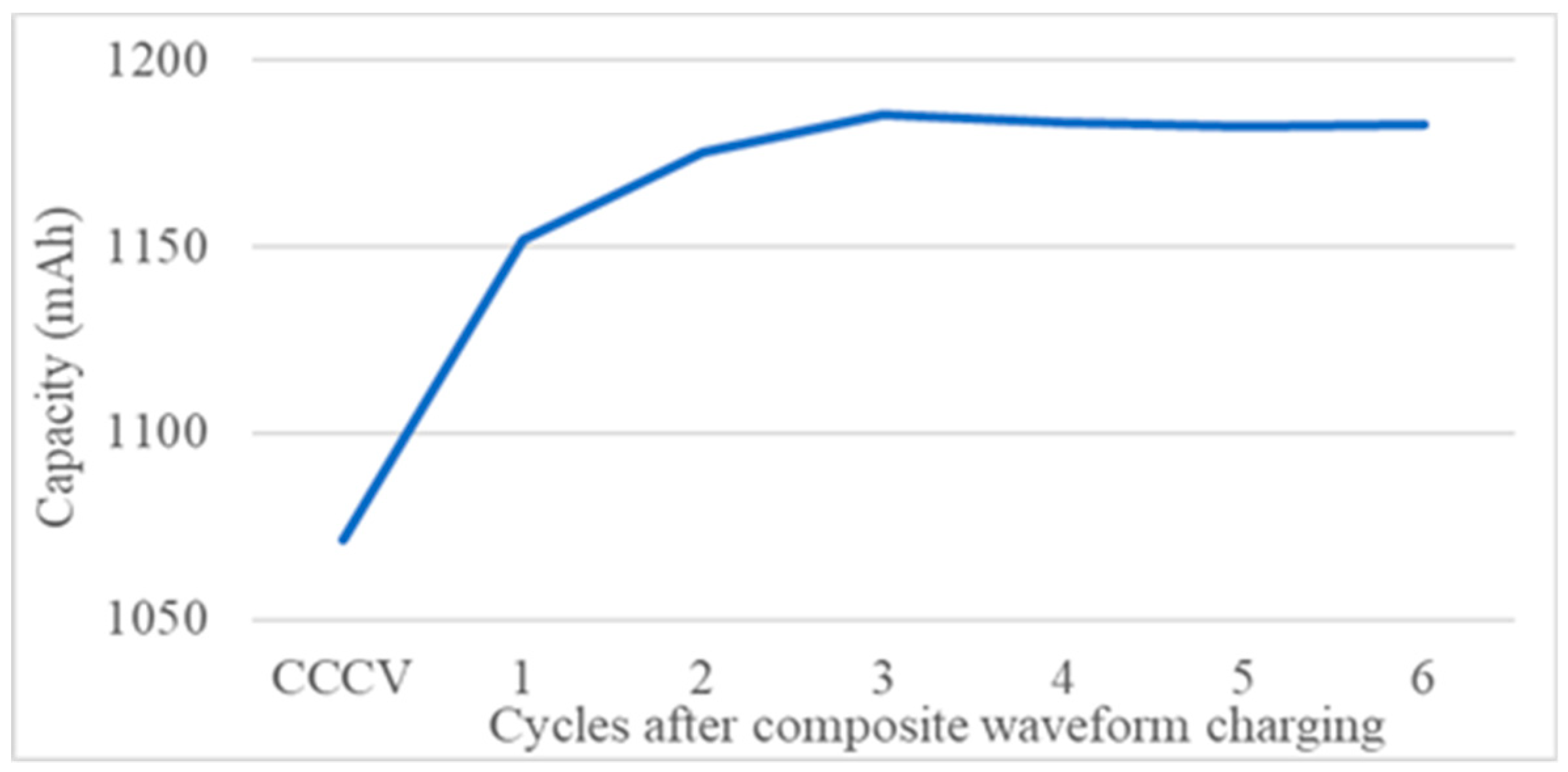

3. Result and Discussion

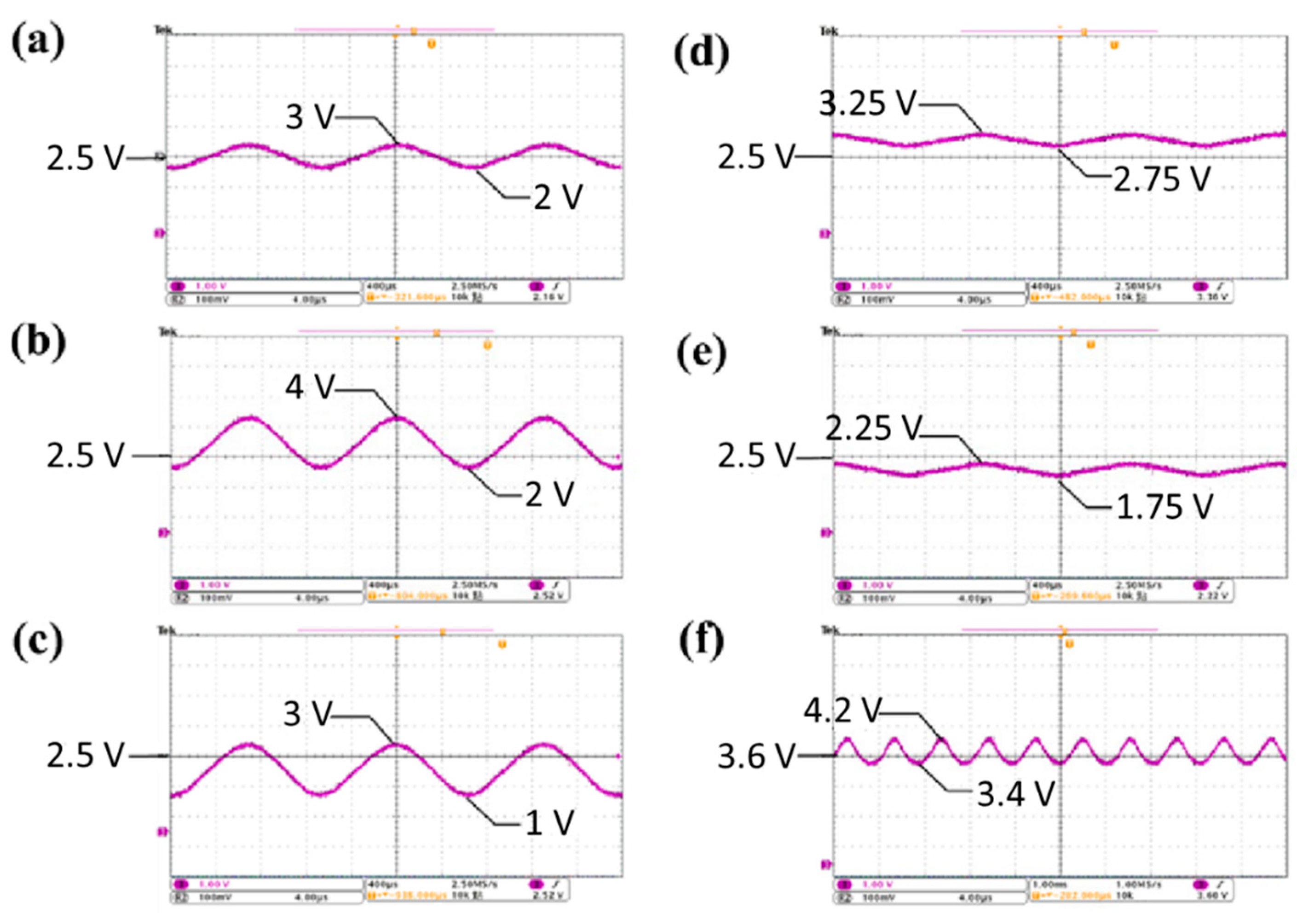

3.1. Verification of the Integrated Amplitude and Level Functions

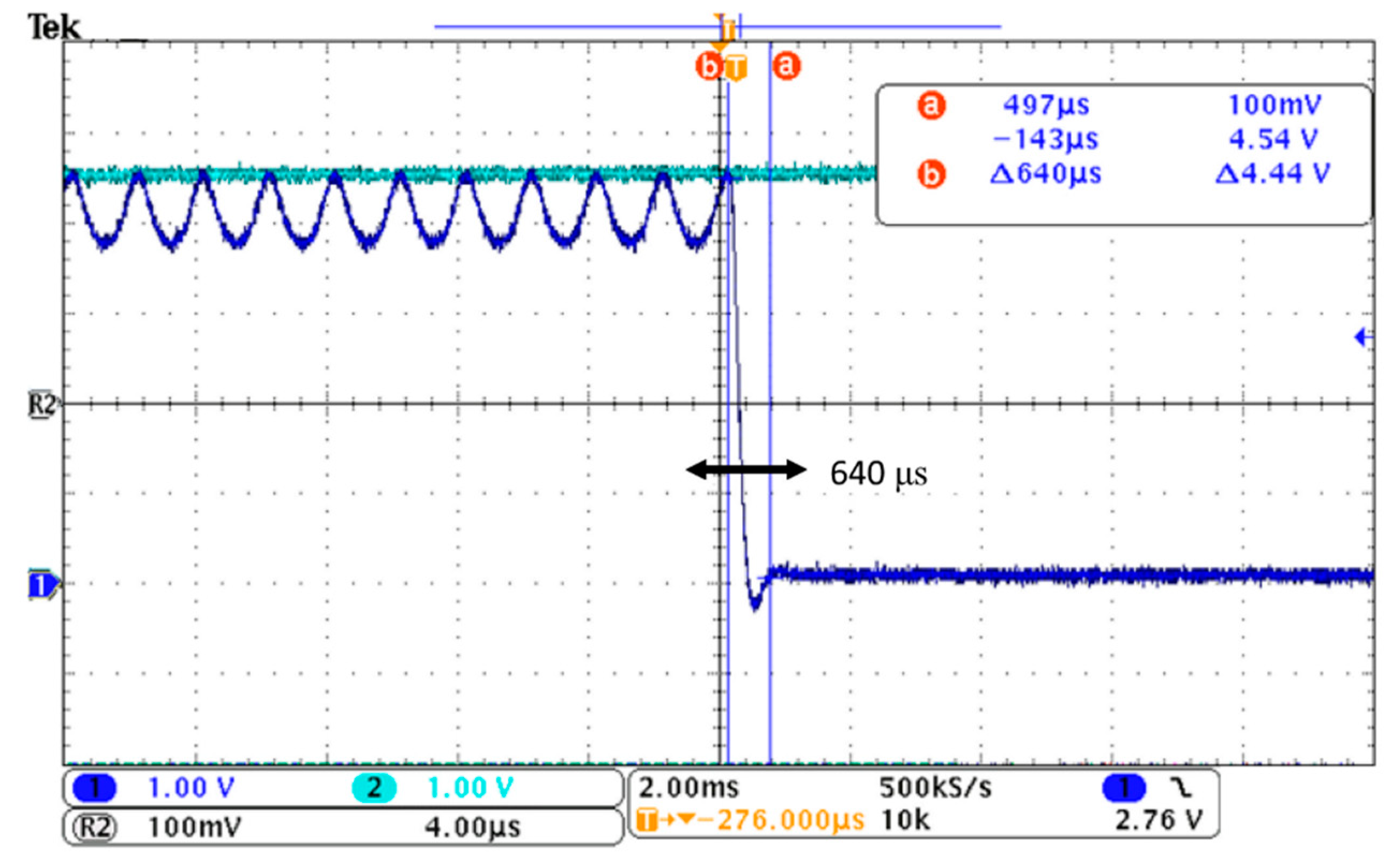

3.2. Verification of the Overvoltage Protection Function

3.3. Verification of the Charging Circuit

4. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Barre, A.; Deguilhem, B.; Grolleau, S.; Gerard, M.; Suard, F.; Riu, D. A review on lithium-ion battery ageing mechanisms and estimations for automotive applications. J. Power Sources 2005, 241, 680–689. [Google Scholar] [CrossRef]

- Verma, P.; Maire, P.; Novák, P. A review of the features and analyses of the solid electrolyte interphase in Li-ion Batteries. Electrochim. Acta 2010, 55, 6332–6341. [Google Scholar] [CrossRef]

- Arora, P.; White, R.E.; Doyle, M. Capacity fade mechanisms and side reactions in lithium-ion batteries. J. Electrochem. Soc. 1998, 145, 3647–3667. [Google Scholar] [CrossRef]

- Thomas, E.V.; Bloom, I.; Christophersen, J.P.; Battaglia, V.S. Statistical methodology for predicting the life of lithium-ion cells via accelerated degradation testing. J. Power Sources 2008, 184, 312–317. [Google Scholar] [CrossRef]

- Amine, K.; Chen, C.H.; Liu, J.; Hammond, M.; Jansen, A.; Dees, D.; Bloom, I.; Vissers, D.; Henriksen, G. Factors responsible for impedance rise in high power lithium-ion batteries. J. Power Sources 2001, 97–98, 684–687. [Google Scholar] [CrossRef]

- Leng, F.; Tan, C.M.; Pecht, M. Effect of temperature on the aging rate of Li ion battery operating above room temperature. Sci. Rep. 2015, 5, 12967. [Google Scholar] [CrossRef] [PubMed]

- Li, J.; Murphy, E.; Winnick, J.; Kohl, P.A. The effects of pulse charging on cycling characteristics of commercial lithium-ion batteries. J. Power Sources 2001, 102, 302–309. [Google Scholar] [CrossRef]

- Thandiwe, I. Pulse Charging Circuit and Method; Motorola Inc.: Schaumburg, IL, USA, 2002. [Google Scholar]

- Benjamin, F. The reFLEX principle of charging nickel-cadmium and other batteries. In Proceedings of the IEEE Power Processing Electronics Specialists Conference, Atlantic City, NJ, USA, 22–23 May 1972; pp. 111–119. [Google Scholar]

- Chen, L.-R.; Wu, S.-L.; Shieh, D.-T.; Chen, T.-R. Sinusoidal-ripple-current charging strategy and optimal charging frequency study for Li-ion batteries. IEEE Trans. Ind. Electron. Control Instrum. 2013, 60, 88–97. [Google Scholar] [CrossRef]

- Chen, P.-T.; Yang, F.-H.; Sangeetha, T.; Gao, H.-M.; Huang, K.D. Moderate Energy for Charging Li-Ion Batteries Determined by First-Principles Calculations. Batter. Supercaps. 2018, 1, 209–214. [Google Scholar] [CrossRef]

- Chen, P.-T.; Yang, F.-H.; Cao, Z.-T.; Jhang, J.-M.; Gao, H.-M.; Yang, M.-H.; Huang, K.D. Reviving aged lithium-ion batteries and prolonging their cycle life by sinusoidal waveform charging strategy. Batter. Supercaps 2019, 2, 673–677. [Google Scholar] [CrossRef]

- Chen, P.-T.; Pai, P.-H.; Yang, C.-J.; Huang, K.D. Development of transmission systems for parallel hybrid electric vehicles. Appl. Sci. 2019, 9, 8. [Google Scholar] [CrossRef]

- Chen, P.-T.; Shen, D.-J.; Yang, C.-J.; Huang, K.D. Development of a hybrid electric motorcycle that accords energy efficiency and controllability via inverse differential gear and power mode switching control. Appl. Sci. 2019, 9, 1787. [Google Scholar] [CrossRef]

- Chen, P.-T.; Ding, P.-F.; Yang, C.-J.; Huang, K.D. Hybrid power system design for multifunctional mini loader vehicles. Appl. Sci. 2019, 9, 4439. [Google Scholar] [CrossRef]

- McCune, E. Time-filtered squarewave output from direct digital synthesis. In Proceedings of the 2010 IEEE MTT-S International Microwave Symposium, Anaheim, CA, USA, 23–28 May 2010; pp. 996–999. [Google Scholar]

- Ayesh, M.M.; Ibrahim, S.A.; Ragai, H.F.; Rizk, M.M. A low-power high-speed charge-steering ADC-based equalizer for serial links. In Proceedings of the 2015 IEEE International Conference on Electronics, Circuits, and Systems (ICECS), Cairo, Egypt, 6–9 December 2015; pp. 500–501. [Google Scholar]

- Payra, A.; Dutta, P.; Sarkar, A.; Sen, S.K. Design of a self regulated flash type ADC with high resolution. In Proceedings of the Michael Faraday IET International Summit 2015, Kolkata, India, 12–13 September 2015; pp. 591–595. [Google Scholar]

- High Performance Digital Signal Controllers. Available online: https://www.microchip.com/pressreleasepage/new-dsc-accelerates-dsp-performance-for-time-critical-control (accessed on 12 February 2020).

- Anushka, P.V.; Mani, N.; Issac, K. Switched-inductor semi-quadratic buck converter. In Proceedings of the 2017 International Conference on Technological Advancements in Power and Energy (TAP Energy), Kollam, India, 21–23 December 2017; pp. 1–6. [Google Scholar]

- Liu, S.; Liu, J.; Yang, Y.; Zhong, J. Design of intrinsically safe buck DC/DC converters. In Proceedings of the 2005 International Conference on Electrical Machines and Systems, Nanjing, China, 27–29 September 2005; pp. 1327–1331. [Google Scholar]

- Premalatha, L.; Vanajaranjan, P. Spectral analysis of DC-DC buck converter with chaotic dynamics. In Proceedings of the 2005 Annual IEEE India Conference-Indicon, Kollam, India, 11–13 December 2005; pp. 605–608. [Google Scholar]

- Li, Y.; Ji, Z. T-S modeling, Simulation and control of the buck converter. In Proceedings of the 2008 Fifth International Conference on Fuzzy Systems and Knowledge Discovery, Shandong, China, 18–20 October 2008; pp. 663–667. [Google Scholar]

- GKarim, H.; Golestanifar, A.; Ghaderi, A.; Salimpour, N. Ultra sharp transition-band low-pass filter with miniaturized size for GSM applications. Radio Eng. 2018, 27, 425–430. [Google Scholar]

- Cao, S.; Han, Y.; Chen, H.; Li, J. An ultra-wide stop-band LPF using asymmetric Pi-shaped koch fractal DGS. IEEE Access 2017, 5, 27126–27131. [Google Scholar] [CrossRef]

- Li, C.; Guo, B.; Li, N. Design on digital LPF for time domain harmonic detecting algorithm. In Proceedings of the 2009 IEEE 6th International Power Electronics and Motion Control Conference, Wuhan, China, 17–20 May 2009; pp. 2406–2410. [Google Scholar]

- Shi, J.; Yao, J.; Liu, K. Study on the method of GPS height interpolation in the linear measurement projects. In Proceedings of the 2011 International Conference on Electric Technology and Civil Engineering (ICETCE), Lushan, China, 22–24 April 2011; pp. 3553–3555. [Google Scholar]

- Tan, G.; Feng, Y.; Shen, H. A combined interpolation method for waveform reconstruction in beacon transmitter detector. In Proceedings of the IET International Communication Conference on Wireless Mobile and Computing (CCWMC 2011), Shanghai, China, 14–16 November 2011; pp. 270–273. [Google Scholar]

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Chen, P.-T.; Zeng, F.-Y.; Zhang, X.-H.; Chung, R.-J.; Yang, C.-J.; Huang, K.D. Composite Sinusoidal Waveform Generated by Direct Digital Synthesis for Healthy Charging of Lithium-Ion Batteries. Energies 2020, 13, 814. https://doi.org/10.3390/en13040814

Chen P-T, Zeng F-Y, Zhang X-H, Chung R-J, Yang C-J, Huang KD. Composite Sinusoidal Waveform Generated by Direct Digital Synthesis for Healthy Charging of Lithium-Ion Batteries. Energies. 2020; 13(4):814. https://doi.org/10.3390/en13040814

Chicago/Turabian StyleChen, Po-Tuan, Fu-Yen Zeng, Xuan-Hao Zhang, Ren-Jei Chung, Cheng-Jung Yang, and K. David Huang. 2020. "Composite Sinusoidal Waveform Generated by Direct Digital Synthesis for Healthy Charging of Lithium-Ion Batteries" Energies 13, no. 4: 814. https://doi.org/10.3390/en13040814

APA StyleChen, P.-T., Zeng, F.-Y., Zhang, X.-H., Chung, R.-J., Yang, C.-J., & Huang, K. D. (2020). Composite Sinusoidal Waveform Generated by Direct Digital Synthesis for Healthy Charging of Lithium-Ion Batteries. Energies, 13(4), 814. https://doi.org/10.3390/en13040814