Abstract

This paper studies the temperature effects on device aging, particularly the random telegraph noise (RTN) degradation and the threshold voltage () shift in a stacked CMOS image sensor (CIS) caused by hot-carrier stress (HCS). Measurements indicate that both are worse when stressed at lower temperatures. Further, the RTN traps generated by HCS can be deactivated effectively by a subsequent high-temperature annealing at 240 °C for up to 360 min. In contrast, the RTN traps in chips not stressed by hot carriers are essentially unaffected by annealing at the same temperature for the same amount of time. This suggests that the physical structure of the RTN traps caused by process-induced damage (PID) without HCS might be different from that generated by HCS. The exact microscopic nature of the differences between these two kinds of RTN traps is not clear and requires further investigation. This work also suggests that RTN degradation could be a useful indicator for device aging for reliability testing and modeling.

1. Introduction

Device aging and reliability are important issues for all semiconductor products. CMOS image sensors (CISs) are no exception [1]. Some well-known aging mechanisms include hot-carrier injection (HCI), bias temperature instability (BTI), time-dependent dielectric breakdown (TDDB), and electron migration (EM) [2,3,4,5,6,7,8,9]. In this work, we focus on HCI-induced device degradation and recovery.

As the pixel pitch of state-of-the-art CISs continues to shrink down to the range of 0.4 to 0.5 microns [10,11,12,13,14], it is inevitable that the number of photons captured by a pixel reduces accordingly. Therefore, it becomes increasingly challenging to maintain a high full-well capacity and a low readout noise to meet the targets of dynamic range and signal-to-noise ratio. Random telegraph noise (RTN) is one of the major components of the low-frequency noises in CISs. However, statistical studies of RTN, especially in the context of device aging, are seldom reported in the literature.

Previously, we reported the increase in RTN caused by hot-carrier stress (HCS) in a stacked CIS at room temperature [15,16]. We pointed out the notable differences between the RTN degradation and the transistor shift commonly monitored in reliability testing. In this study, the HCS temperatures are extended to cover a wider range from −35 °C to 120 °C. Furthermore, we investigate the effects of high-temperature annealing on RTN after HCS. By analyzing the time-domain noise waveforms, all pixels in an 8.3 Mpixel array are sorted into two categories, RTN and non-RTN. Then, we trace the changes in the noise behavior of each pixel throughout a series of stress and annealing experiments. The results lead to an important observation that the RTN traps generated by HCS can be annealed effectively by high-temperature treatment, but the RTN traps caused by PID cannot be eliminated easily.

Despite the fact that RTN in MOSFET has been known for several decades, there is no consensus on the origins of RTN traps. The microscopic structures of RTN traps are still up for debate. The mechanisms of the generation and annihilation of RTN traps are not fully understood. The existence of different categories of RTN traps that some can be systematically eliminated by high-temperature annealing and some cannot is neither predicted nor explained by existing atomic models or ab initio theoretical calculations. The goal of this paper is to provide experimental evidence to emphasize this observation. This is supported by a statistical analysis of 1M devices. To our knowledge, the key points we highlighted have not been reported or answered before. We hope this work will stimulate further studies on the nature of RTN traps.

2. Materials and Methods

2.1. Test Chip Design and Characteristics

The test chip is a two-layer stacked and backside-illuminated (BSI) CMOS image sensor with an 8.3 Mpixel (2512V × 3296H) resolution and a 0.8 µm pixel pitch. The top layer consists of a pixel array, fabricated in a 1P4M 45 nm CIS process. The bottom layer consists of analog readout circuits and a digital processor, fabricated in a 1P7M 22 nm mixed-mode process. The two layers are face-to-face stacked by a wafer-level hybrid bond (HB) technology. The array has a 4V × 2H shared-pixel structure and is read out by 1648 12-bit column ADCs with front amplifiers supporting 1 to 8 analog gains. The average DNL of the ADCs is within ±0.5 DN (digital number). The average INL is less than 0.5% of the full signal range.

A simplified chip architecture is shown in Figure 1. The three pixel devices (RST, RSL, SF) can be operated up to 3.3 V. The device under test (DUT) is the source follower (SF) NMOS with W = 0.16 µm, L = 0.87 µm, and a 5.7 nm dielectric thickness, biased by a constant current source of 7.2 µA in normal operations. The conversion factor from the ADC output to the SF input is 292 µV/DN at gain of 1 and 36.5 µV/DN at gain of 8. The median read noise (including an amplifier at a gain of 1 and ADC) is about 190 µV-rms operated at a 60 MHz clock and a 1.48 fps frame rate. The random noise (RN) is measured at gain of 8. The threshold voltage shift () is measured at gain of 1. Both are calculated back to input-referred values at the SF gates. Throughout this paper, the CIS chip is operated in the dark under a test mode where the transfer gates (TGs) are disabled, and the SF input is fixed by an external voltage via the RSV terminal such that photon shot noises and dark leakage are not involved. The measured outputs are primarily SF temporal noises.

Figure 1.

A simplified test chip signal chain and an illustration of the hot-carrier stress condition, where the red circles represent electrons and the blue circles represent holes. The device under stress is the SF. PD0–7 indicate the photodiodes, and TG0–7 indicate the transfer gates in each pixel group. The total number of SF is 628 × 1648 = 1.03 M.

2.2. Hot-Carrier Injection and the Temperature Dependence

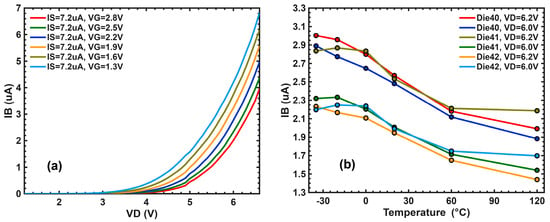

Under normal imaging operations, the SF drain voltage () is set to 3.1 V. When is increased, the channel conduction electrons are accelerated by the lateral electric fields and gain kinetic energies. The energetic (hot) electrons can, in turn, generate more electron–hole pairs through impact ionization, manifested as a rapid increase in the substrate current () due to unrecombined holes. When the electron energy exceeds the electron affinity difference between Si and SiO2 (about 3.25 eV), it can jump over or tunnel through the Si-SiO2 barrier to damage the oxide. In this experiment, the source voltage () of the SF is about 1.5 V. A significant increase in substrate current is observed when exceeds 5.5 V, i.e., when the of the SF is higher than 4 V. Figure 2 shows the data measured from the SF devices in separate test keys.

Figure 2.

The substrate current is a key indicator of hot-carrier injection. (a) as a function of stepped by at room temperature, where is biased at 7.2 µA. (b) The temperature dependence of at 6.0 and 6.2 V, where is fixed at 2.8 V.

2.3. Hot-Carrier Stress and High-Temperature Annealing Experiments

In hot-carrier stress experiments, is raised to 6 V, and the temperatures are maintained at 35 °C, 0 °C, 20 °C, 60 °C, and 120 °C for each selected sample. The time intervals for the series of stresses are 10, 20, 50, 100, 200, and 400 min. In this paper, the accumulated stress times (i.e., 0, 10, 30, 80, 180, 380, and 780 min) are used as the reference time. Before, after, and between two consecutive stresses, the samples are measured at V at room temperature. In annealing experiments, the stressed samples are annealed in normal laboratory ambient air at temperatures of 120 °C, 160 °C, 200 °C, and 240 °C for a sequence of accumulated annealing times of 10, 30, 60, 160, and 360 min under power-off conditions. Similarly, the samples are measured at room temperature before, after, and between two consecutive annealing processes under normal operating conditions. The value caused by the stress and annealing is calculated as , where and denote the accumulated stress and annealing time, respectively.

We have verified that the RTN of a stressed sample does not show any noticeable relaxation effects at room temperature up to a few weeks.

3. Results

3.1. Temperature Dependence of the Hot-Carrier Stress

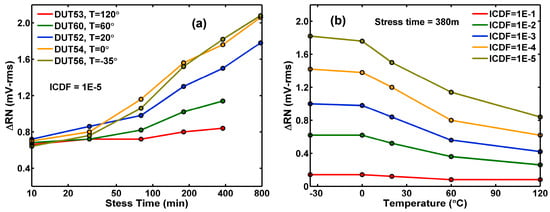

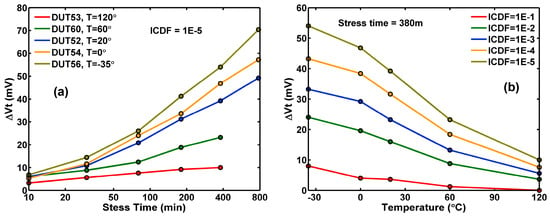

The value at the 10 ppm tail of the inverse cumulative distribution function (ICDF) versus stress time for temperatures ranging from 35 °C to 120 °C is plotted in Figure 3a. It shows that the degradation is worse at lower temperatures. Figure 3b shows that the temperature dependence of various constant-ICDF contours is similar and consistent.

Figure 3.

(a) value at the distribution tail (ICDF = 10−5) as a function of stress time from 35 °C to 120 °C. (b) Constant-ICDF contours of after a stress of 380 min versus temperature.

The RN degradation and the shift are correlated to the amount of injected hot electrons and proportional to the measured substrate currents, which show a similar temperature dependence in Figure 2 and Figure 3. This behavior is consistent with what has been reported in the literature [17,18,19].

However, the trend is not universal. Later studies [20,21] indicate that the HCS degradation is higher at lower temperatures only for long-channel devices (approximately L > 100 nm). The trend is opposite for short-channel devices (L < 100 nm) due to different mechanisms. The SF under test has L = 870 nm; therefore, it is a long-channel device. For the rest of this article, we selected the device stressed at −35 °C for recovery experiment. For high-temperature annealing, we selected the results of 240 °C for discussion.

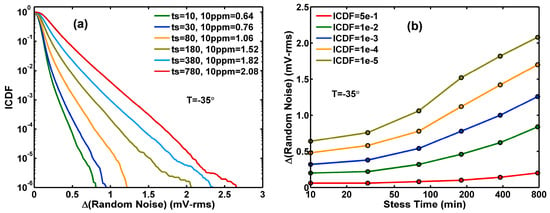

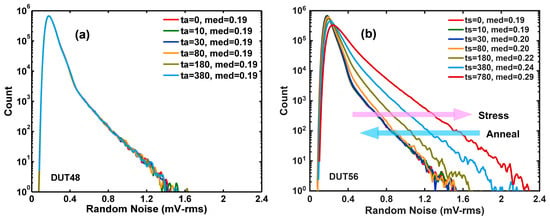

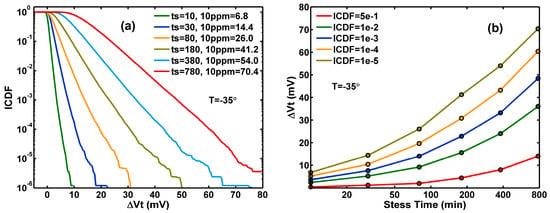

3.2. Effects of Stress and Annealing on Random Noise Distributions

Figure 4a shows the gradual change in the ICDF curves for a stress time () ranging from 10 to 780 min. The values at 10 ppm levels are shown in the legends and plotted in Figure 4b along with several different ICDF values versus stress times. After the HCI stress, the same sample is annealed at 240 °C for up to 360 min. Figure 5a,b shows the change over the annealing time (). Note that all measurements are performed at room temperature between two consecutive stress and annealing processes. Comparing Figure 5 to Figure 4, we can see that annealing is almost like a reversed process of stress. This means that the damage delivered to the device by HCI stress can be mostly repaired by annealing. The speed of the recovery is relatively faster during the first 10 min at 240 °C. However, the recovery is close to but not 100% complete. We can see this by comparing the ICDF curve at the end of the annealing ( 360) to the curve at the beginning of the stress ( 10), which is shown as the black dotted curve in Figure 5a.

Figure 4.

Hot-carrier stress at −35 °C. (a) A family of ICDF curves of RN for stress times ranging from 10 to 780 min. (b) A family of constant-ICDF contours as functions of the stress time.

Figure 5.

High-temperature annealing at 240 °C. (a) A family of ICDF curves of for annealing times ranging from 10 to 360 min. The black dotted curve corresponds to the beginning of the stress. (b) A family of constant-ICDF contours as functions of the annealing time.

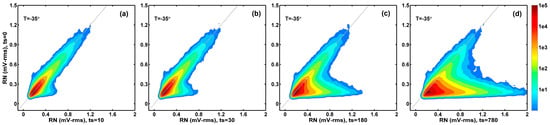

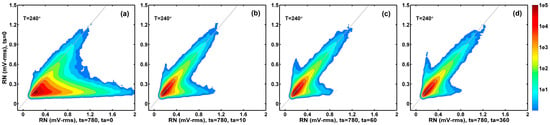

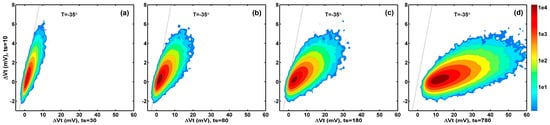

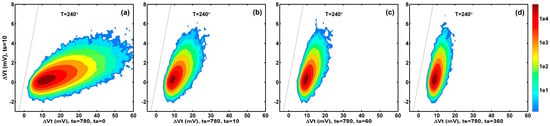

The details in the changes during the stress and annealing experiments can be seen clearly in 2D correlation histograms between RN at each stage of stress (or annealing) compared to the initial condition. Figure 6 compares the RN value at 10, 30, 180, and 780 min to the RN value before stress ( 0). Figure 7 compares the RN value at 10, 10, 60, and 360 min after 780 min of stress to the RN value before stress ( 0). As pointed out previously [15,16], the prominent feature in the 2D histograms is that there are two distinct groups of devices. The devices centering around the diagonal line (gray color) show small RN changes. On the other hand, the group of devices in the lower-right branch of the 2D histogram contribute to a large portion of the RN changes. They are mostly the RTN devices generated by the stress and recovered in the subsequent annealing, which is discussed in the next paragraph. The annealing process in Figure 7 is like a time reversal of the degradation process in Figure 6.

Figure 6.

Correlation between the RN value after stress and the RN value before stress. A total of (a) 10 min of stress; (b) 30 min of stress; (c) 180 min of stress; and (d) 780 min of stress.

Figure 7.

Correlation between the RN value after annealing and the RN value before stress. A total of (a) 0 min of annealing; (b) 10 min of annealing; (c) 60 min of annealing; and (d) 360 min of annealing.

In conventional device aging and reliability testing, the threshold voltage shift () plays a more prominent role than RN degradation. In this study, both are characterized at the same time and compared side by side. Their physical origins are closely related, and some of the aging behaviors are similar. Although is not at the center of the following discussion, we include the results in Appendix A as a complementary reference. There is a one-to-one correspondence between Figure A1, Figure A2, Figure A3, Figure A4 and Figure A5 and Figure 3, Figure 4, Figure 5, Figure 6 and Figure 7, respectively.

3.3. Classification of the Random Noise Types

For CIS process and product development purposes, RN histograms and ICDF plots are sufficient to evaluate the RTN performance from wafer to wafer and from lot to lot. A common practice [22,23,24] is to set an empirical RN threshold and calculate the percentage of pixels above the threshold as an RTN performance index. Apparently, this is a simplification for the convinience of benchmarking. In real silicon, we find that the distribution of RTN pixels in the full array is more complicated.

In this paper, we follow the methodology developed in previous work [15,16,25,26] to classify the pixel RN types according to their time-domain noise waveforms. In general, the known pixel noises in the dark are the thermal noises, the flicker noises, and the RTN, assuming the reset KTC noises are suppressed by a true CDS (correlated double sampling) operation. The pixels showing multiple identifiable discrete levels in noise waveforms are classified RTN pixels. The pixels with nearly ideal Gaussian noise distributions are considered non-RTN pixels. There is a gray area between these two types of noises. Some pixels do not show mutliple discrete levels but the noise distributions significantly deviate from the Gaussian forms. We tentatively call these RTN-like pixels (e.g., Figure 12 of [16]).

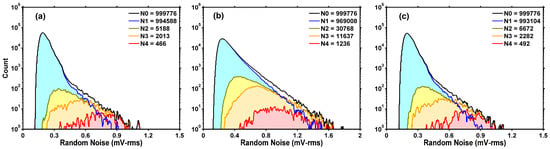

Figure 8a–c show the result of sorting all the pixels before stress, after stress, and after annealing, respectively. In the legend, is the number of pixels showing three or more discrete levels; is the number of pixels showing two or more discrete levels; equals plus the number of RTN-like pixels; is the number of non-RTN pixels; and is the total number of pixels. Since eight pixels share one SF, which dominates the readout noise, the total number of SFs in Figure 8 is about one-eighth of 8.3 million. In the rest of this paper, we treat as the number of generalized RTN pixels. In other words, each pixel is classified as either RTN or non-RTN (i.e., ). From Figure 8, we can see that it is not possible to choose a well-defined threshold to separate RTN pixels from non-RTN pixels.

Figure 8.

Sorting results of all devices in three stages: (a) before stress, (b) after stress, and (c) after annealing. The meaning of the numbers , and are defined in the text.

3.4. Key Findings

The separation of RTN and non-RTN devices allows us to keep track of the change in behavior of the individual devices throughout the stress and anneal experiments. In Table 1, the numbers of RTN and non-RTN devices before stress, after stress, and after annealing are summarized. There are eight possible experimental outcomes. Each outcome can be labeled by a 3-bit binary code as the case number, where a “1” means RTN and a “0” means non-RTN. For instance, one device in case 010 means that it is non-RTN before stress, turns into RTN after stress, and changes back to non-RTN after annealing.

Table 1.

The number of RTN and non-RTN devices before stress, after stress, and after annealing. The eight possible outcomes are labeled by case numbers of 3 binary bits, where “1” represents RTN and “0” represents non-RTN. RTN data are labelled by light blue background color and non-RTN data are labelled by pink color.

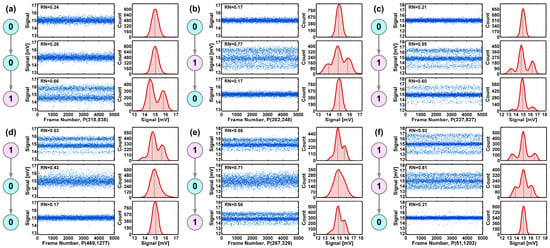

The first observation is that the cause-and-effect is not as simple as one might expect. Intuitively, we might anticipate that the effect of HCS is to generate RTN traps. However, the result shows that HCS could not only turn some non-RTN devices into RTN devices but could also turn some RTN devices into non-RTN devices. Vice versa, the annealing also works both ways. The underlying physical process seems complicated. It indicates that the results are not entirely deterministic but depend on certain probabilities. To visualize and to confirm the transitions, six examples are selected and plotted in Figure 9, excluding the trivial no-change cases 000 and 111.

Figure 9.

Six selected examples corresponding to (a) case 001, (b) case 010, (c) case 011, (d) case 100, (e) case 110, and (f) case 110. The noise waveforms and histograms before stress, after stress, and after annealing are shown in top, middle, and bottom panels of each figure, respectively.

Secondly, although there are devices in all the eight possible cases, the most outstanding one is obviously case 010 with the most transitions. In the initial condition before stress, there are 5188 RTN devices, or 0.5% of the total population. After 780 min of stress at −35 °C, 28,388 devices are turned from non-RTN to RTN, about 5.5 times the initial RTN number. Among these 28,388 RTN devices, 27,856 return to being non-RTN after annealing at 240 °C for 360 min. The recovery rate is about 98%. This indicates that the RTN traps generated by HCS can be effectively deactivated by high-temperature annealing.

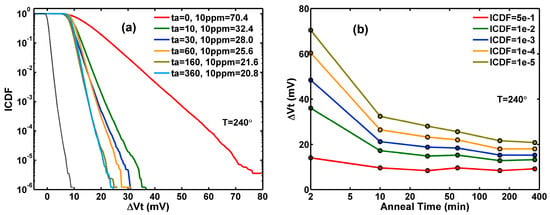

Thirdly, two distinct types of RTN traps are observed. “Soft” RTN traps, generated by HCS, are readily annealed at 240 °C, while “hard” RTN traps, caused by PID, are resistant to annealing. The contrast is evident by comparing the RN histograms of an unstressed sample to those of a stressed sample. Figure 10a shows that the RN histograms of an unstressed sample remain unchanged after 240 °C annealing for up to 360 min, indicating that PID-induced RTN traps are largely unaffected. Figure 10b shows that for a stressed sample, HCS significantly degrades the RN histograms due to new RTN traps. Most of the new RTN traps are deactivated by high-temperature annealing and the initial RN distribution is nearly restored.

Figure 10.

(a) DUT48 (unstressed) has a comparable performance to DUT56 before stress. The RN distributions are not changed by high-temperature annealing. (b) DUT56 (stressed) shows a degraded RN histogram that is restored to its initial condition after annealing, indicating deactivation of HCS-generated RTN traps. In the legends, “med” denotes the median of RN.

4. Discussion

RTN traps are, in general, related to defects introduced into the gate dielectric or bulk Si during a long sequence of manufacturing steps. For instance, some could be due to high-energy ion implantation, and some could be related to reactive ion etching. It is often difficult to pinpoint the exact source and eliminate RTN traps completely. In the CIS chips we characterized, the percentage of RTN pixels in a large array is small, typically in the order of 0.1% to 0.5%. PID-induced RTN traps are stable in room temperature for several months or even years. In this study, we find that they cannot be easily deactivated by high-temperature annealing. One explanation is that at the time of fab-out, the RTN traps have survived the high-temperature treatment in the backend-of-line (BEOL) process up to a few hundreds of degrees Celsius for hours; therefore, they cannot be annealed further. They may be tentatively called “hard” RTN traps.

On the other hand, HCS generates many new and relatively “soft” RTN traps, which can be easily eliminated by a subsequent 240 °C annealing. This important distinction among different RTN traps has not been pointed out in the literature to the best of our knowledge.

Several studies have linked HCI-induced interface states and oxide traps to the dissociation of Si-H bonds, which creates Si dangling bonds [21,27,28,29,30,31,32,33,34]. Reversely, the annealing of these traps at high temperature could be explained by hydrogen re-passivating the Si dangling bonds. Hydrogen and hydrogen-related chemicals are commonly used in many semiconductor fabrication processes. Once introduced, the hydrogen atom can diffuse easily through the Si and oxide lattice. The nominal Si-H bond strength is about 3.6 eV; however, some reports have shown that the Si-H bond can be broken by hot electrons of energies much less than 3.6 eV [33,34].

The defects in bulk SiO2 and on the Si-SiO2 interface have many complicated forms such as Si dangling bonds ( centers), oxygen vacancies (E’ centers), hydroxyl-E’ centers, hydrogen bridges, peroxyl radicals, and non-bridging oxygen hole centers [35,36,37]. Electronic excitation or charge trapping on some of these sites may alter their atomic configurations and electrical characteristics. It is possible that the differences between hard and soft RTN traps are related to the atomic structural differences in the traps, although our macroscopic data cannot lead to any specific microscopic pictures.

5. Conclusions

We point out one key difference between native or built-in RTN traps in samples unstressed after fab-out and RTN traps created by hot-carrier stress. The latter can be mostly eliminated by 240 °C annealing in ambient air for a few hours, while the former cannot be annealed easily. The underlying physics is not clarified yet. We hope that this study can stimulate further investigations, perhaps by atomic structure calculation and simulation, to better understand the dynamics and mechanisms of the generation and annihilation of RTN traps.

Author Contributions

Conceptualization, methodology, and writing, C.Y.-P.C.; measurement and data analysis, T.M.-H.W.; test chip analog design, C.C.-M.L., S.-F.Y., C.-L.L. and Z.-D.W.; test chip digital design, J.C.-Y.H. and C.-H.C.; characterization system design, H.T. and T.M.-H.W. All authors have read and agreed to the published version of the manuscript.

Funding

This research received no external funding.

Institutional Review Board Statement

Not applicable.

Informed Consent Statement

Not applicable.

Data Availability Statement

Data is contained within the article.

Acknowledgments

We like to thank the process team for their support.

Conflicts of Interest

All authors are employed by Taiwan Semiconductor Manufacturing Company (TSMC). The authors declare that the research was conducted in the absence of any commercial or financial relationships that could be construed as a potential conflict of interest.

Abbreviations

The following abbreviations are used in this manuscript:

| CIS | CMOS Image Sensor |

| BSI | Backside-Illuminated |

| RN | Random Noise |

| RTN | Random Telegraph Noise |

| HCS | Hot-Carrier Stress |

| HCI | Hot-Carrier Injection |

Appendix A

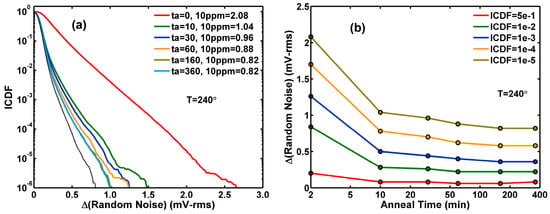

In conventional reliability testing and modeling, the threshold voltage shift () is one of the most important parameters. On the other hand, RN degradation () is not routinely monitored. Nevertheless, in real devices, these two aging effects always happen hand in hand. The physical causes of both effects are related to the generation of oxide traps and interface states. In this work, and are characterized at the same time during the stress and annealing process. In the main text, we focus on the discussion of . For completeness, the data are presented here in Figure A1, Figure A2, Figure A3, Figure A4 and Figure A5 as counterparts of Figure 3, Figure 4, Figure 5, Figure 6 and Figure 7 on . From the standpoint of statistical distributions and the temperature dependencies, the values in Figure A1, Figure A2 and Figure A3 are very similar to the values in Figure 3, Figure 4 and Figure 5. However, the evolution of the correlation plots in Figure A4 and Figure A5 are notably different from Figure 6 and Figure 7, as previously pointed out [14,15]. Unlike Figure 6 and Figure 7, the 2D histograms in Figure A4 and Figure A5 do not show two distinct branches. The degradation and recovery of happen more uniformly to the entire population, while the value is significantly larger for RTN devices than that for non-RTN devices.

Figure A1.

(a) at the distribution tail (ICDF = 10−5) as a function of stress time from −35 °C to 120 °C. (b) Constant-ICDF contours of after 380 min of stress as a function of temperature.

Figure A2.

Hot-carrier stress at −35 °C. (a) A family of ICDF curves of for stress times ranging from 10 to 780 min. (b) A family of constant-ICDF contours as functions of the stress time.

Figure A3.

High-temperature annealing at 240 °C. (a) A family of ICDF curves of for annealing times ranging from 10 to 360 min. The black dotted curve corresponds to the beginning of the stress. (b) A family of constant-ICDF contours as functions of the annealing time.

Figure A4.

Correlation between after stress and before stress. A total of (a) 10 min of stress; (b) 30 min of stress; (c) 180 min of stress; and (d) 780 min of stress.

Figure A5.

Correlation between after annealing and before stress. A total of (a) 0 min of annealing; (b) 10 min of annealing; (c) 60 min of annealing; and (d) 360 min of annealing.

References

- Chao, C.Y.-P.; Wu, T.M.-H.; Liu, C.C.-M.; Yeh, S.-F.; Lee, C.-L.; Tu, H.; Wu, Z.-D.; Huang, J.C.-Y.; Chang, C.-H. Recovery of Random Telegraph Noise in a Stacked CMOS Image Sensor by High-Temperature Annealing after Hot-Carrier Stress. In Proceedings of the 2025 Int’l Image Sensor Workshop (IISW), Awaji, Japan, 2–5 June 2025; pp. 69–72. [Google Scholar] [CrossRef]

- Gupta, D.C.; Brown, G.A. Gate Dielectric Integrity—Material Process, and Tool Qualification; American Society for Testing and Materials (ASTM): West Conshohoken, PA, USA, 2000. [Google Scholar]

- Dumin, D.J. (Ed.) Oxide Wearout, Breakdown, and Reliability. In Oxide Reliability—A Summary of Silicon Oxide Wearout, Breakdown, and Reliability; World Scientific Publishing Company: Singapore, 2002; pp. 1–102. [Google Scholar]

- Grasser, T. (Ed.) Hot Carrier Degradation in Semiconductor Devices; Springer International Publishing AG: Cham, Switzerland, 2015. [Google Scholar]

- Grasser, T. (Ed.) Noise in Nanoscale Semiconductor Devices; Springer International Publishing AG: Cham, Switzerland, 2020. [Google Scholar]

- Tan, S.; Tahoori, M.; Kim, T.; Wang, S.; Sun, Z.; Kiamehr, S. Chapter 13 Transistor Aging Effects and Reliability—Introduction. In Long-Term Reliability of Nanometer VLSI Systems—Modeling, Analysis and Optimization; Springer Nature Switzerland AG: Cham, Switzerland, 2019; pp. 279–304. [Google Scholar]

- McPherson, J.W. Chapter 12.7 Hot-Carrier Injection. In Reliability Physics and Engineering—Time-to-Failure Modeling, 3rd ed.; Springer Nature Switzerland AG: Cham, Switzerland, 2019; pp. 207–211. [Google Scholar]

- El-Kareh, B.; Hutter, L.N. Chapter 11 Chip Reliability. In Silicon Analog Components—Device Design, Process Integration, Characterization, and Reliability, 2nd ed.; Springer Nature Switzerland AG: Cham, Switzerland, 2020; pp. 539–620. [Google Scholar]

- Rossi, D. Chapter 2 The Effects of Ageing on the Reliability and Performance of Integrated Circuits. In Ageing of Integrated Circuits—Causes, Effects and Mitigation Techniques; Halak, B., Ed.; Springer Nature Switzerland AG: Cham, Switzerland, 2020; pp. 35–64. [Google Scholar]

- Lee, G.-D.R.; Kim, D.-H.; Kwon, D.; Park, J.-E.; Cho, D.; Kang, J.; Park, G.; Kang, J.; Jang, M.; Oh, S.; et al. A 0.5 μm Pixel 3-layer Stacked CMOS Image Sensor with Deep Contact and In-pixel Cu-Cu Bonding Technology. In Proceedings of the IEEE Int’l Electron Devices Meeting (IEDM), San Francisco, CA, USA, 9–13 December 2023; pp. 40.1.1–40.1.4. [Google Scholar]

- Kim, D.-H.; Cho, K.; Ji, H.-C.; Kim, M.; Kim, J.; Kim, T.; Seo, S.; Im, D.; Lee, Y.-N.; Choi, J.; et al. A 1/1.56-inch 50Mpixel CMOS Image Sensor with 0.5 μm pitch Quad Photodiode Separated by Front Deep Trench Isolation. In Proceedings of the IEEE Int’l Solid-State Circuit Conference (ISSCC), San Francisco, CA, USA, 18–22 February 2024; pp. 118–119. [Google Scholar]

- Satake, Y.; Tanaka, Y.; Sato, S.; Takase, M.; Hoyano, M.; Kasukawa, S.; Tomita, M.; Kikuchi, Y.; Yamamoto, J.; Tokuhiro, K.; et al. Low Dark Noise and 8.5 ke− Full Well Capacity in a 2-Layer Transistor Stacked 0.8 μm Dual Pixel CIS with Intermediate Poly-Si Wiring. In Proceedings of the IEEE Int’l Electron Devices Meeting (IEDM), San Francisco, CA, USA, 7–11 December 2024; pp. 1–4. [Google Scholar]

- Kim, M.; Kim, D.; Chang, K.E.; Woo, K.; Yoon, K.; Ko, H.; Kim, J.; Cho, K.; Ji, H.-C.; Kim, S.-I.; et al. A 0.5 μm pixel-pitch 200-Megapixel CMOS Image Sensor with Partially Removed Front Deep Trench Isolation for Enhanced Noise Performance and Sensitivity. In Proceedings of the 2025 Int’l Image Sensor Workshop (IISW), Awaji, Japan, 2–5 June 2025; pp. 29–32. [Google Scholar]

- Baek, S.; An, S.; Sul, D.; Fujita, M.; Jung, S.; Na, Y.; Jung, T.; Jeong, H.; Lee, M.; Park, E.; et al. A 0.45 μm-pitch Photodiode Based 1-layer Dual Pixel for CMOS Image Sensor with High Full-Well Capacity and Low Noise. In Proceedings of the 2025 Int’l Image Sensor Workshop (IISW), Awaji, Japan, 2–5 June 2025; pp. 33–36. [Google Scholar]

- Chao, C.Y.-P.; Wu, T.M.-H.; Yeh, S.-F.; Lee, C.-L.; Tu, H.; Huang, J.C.-Y.; Chang, C.-H. Hot Carrier Injection Induced Random Telegraph Noise Degradation in a 0.8 μm-pitch 8.3Mpixel Stacked CMOS Image Sensor. In Proceedings of the 2023 Int’l Image Sensor Workshop (IISW), Crieff, UK, 22–25 May 2023; pp. 44–47. [Google Scholar] [CrossRef]

- Chao, C.Y.-P.; Wu, T.M.-H.; Yeh, S.-F.; Lee, C.-L.; Tu, H.; Huang, J.C.-Y.; Chang, C.-H. Random Telegraph Noise Degradation Caused by Hot Carrier Injection in a 0.8 μm-Pitch 8.3Mpixel Stacked CMOS Image Sensor. Sensors 2023, 23, 7959. [Google Scholar] [CrossRef] [PubMed]

- Tzou, J.J.; Yao, C.C.; Cheung, R.; Chan, H. Hot-Electron-Induced MOSFET Degradation at Low Temperatures. IEEE Electron Device Lett. 1985, 6, 450–452. [Google Scholar] [CrossRef]

- Heremans, P.; Bosch, G.V.D.; Bellens, R.; Groeseneken, G.; Maes, H. Temperature Dependence of the Channel Hot-Carrier Degradation of n-Channel MOSFET’s. IEEE Trans. Electron Devices 1990, 37, 980–993. [Google Scholar] [CrossRef]

- Song, M.; MacWillians, K.P.; Woo, J.C.S. Comparison of NMOS and PMOS Hot Carrier Effects from 300 to 77 K. IEEE Trans. Electron Devices 1997, 44, 268–276. [Google Scholar] [CrossRef]

- Tyaginov, S.; Jech, M.; Franco, J.; Sharma, P.; Kaczer, B.; Grasser, T. Understanding and Modeling the Temperature Behavior of Hot-Carrier Degradation in SiONn MOSFETs. IEEE Electron Device Lett. 2016, 37, 84–87. [Google Scholar] [CrossRef]

- Ruch, B.; Pobegen, G.; Grasser, T. Investigation of the Temperature Dependence of Hot-Carrier Degradation in Si MOSFETs Using Spectroscopic Charge Pumping. IEEE Trans. Electron Devices 2020, 67, 4092–4098. [Google Scholar] [CrossRef]

- Park, S.; Lee, C.; Park, S.; Park, H.; Lee, T.; Park, D.; Heo, M.; Park, I.; Yeo, H.; Lee, Y.; et al. A 64Mpixel CMOS Image Sensor with 0.56 μm Unit Pixels Separated by Front Deep-Trench Isolation. In Proceedings of the IEEE Int’l Solid-State Circuit Conference (ISSCC), San Francisco, CA, USA, 20–26 February 2022; pp. 108–109. [Google Scholar]

- Kitamura, S.; Kimizuka, N.; Honjo, A.; Baba, K.; Kurobe, T.; Kumano, H.; Toyofuku, T.; Takeuchi, K.; Nishimura, S.; Kato, A.; et al. Low-Noise Multi-Gate Pixel Transistor for Sub-Micron Pixel CMOS Image Sensors. In Proceedings of the 2022 Symposium on VLSI Technology and Circuits (VLSI), Honolulu, HI, USA, 12–17 June 2022; pp. 347–348. [Google Scholar]

- Kikuchi, Y.; Tomita, M.; Hayashi, T.; Chib, H.; Ogita, T.; Okawa, T.; Nishida, K.; Sugimoto, M.; Yoneyama, D.; Umeki, T.; et al. Noise Performance Improvements of 2-Layer Transistor Pixel Stacked CMOS Image Sensor with Non-doped Pixel-FinFETs. In Proceedings of the 2023 Symposium on VLSI Technology and Circuits (VLSI), Kyoto, Japan, 11–16 June 2023; pp. T07.4.1–T07.4.2. [Google Scholar]

- Chao, C.Y.-P.; Wu, M.-H.; Yeh, S.-F.; Chang, C.-H.; Lee, C.-L.; Chou, K.-Y.; Tu, H. Statistical analysis of random telegraph noises of MOSFET subthreshold currents using a 1M array test chip in a 40 nm process. IEEE J. Electron Devices Soc. 2021, 9, 972–984. [Google Scholar] [CrossRef]

- Chao, C.Y.-P.; Tu, H.; Wu, T.M.-H.; Chou, K.-Y.; Yeh, S.-F.; Yin, C.; Lee, C.-L. Statistical analysis of the random telegraph noise in a 1.1 μm pixel, 8.3 MP CMOS image sensor using on-chip time constant extraction method. Sensors 2017, 17, 2704. [Google Scholar] [CrossRef] [PubMed]

- Lyding, J.W.; Hess, K.; Kizilyalli, I.C. Reduction of hot electron degradation in metal oxide semiconductor transistors by deuterium processing. Appl. Phys. Lett. 1996, 68, 2526–2528. [Google Scholar] [CrossRef]

- Tuttle, B.; Van de Walle, C.G. Structure, energetics, and vibrational properties of Si-H bond dissociation in silicon. Phys. Rev. B 1999, 59, 12884–12889. [Google Scholar] [CrossRef]

- Lee, J.; Cheng, K.; Chen, Z.; Hess, K.; Lyding, J.W.; Kim, Y.-K.; Lee, H.-S.; Kim, Y.-W.; Suh, K.-P. Application of High-Pressure Deuterium Annealing for Improving the Hot Carrier Reliability of CMOS Transistors. IEEE Electron Device Lett. 2000, 21, 221–223. [Google Scholar]

- Koike, N.; Tatsuuma, K. A Drain Avalanche Hot Carrier Lifetime Model for n- and p-Channel MOSFET’s. In Proceedings of the Int’l Reliability Physics Symposium (IRPS), Dallas, TX, USA, 7–11 April 2002; pp. 86–92. [Google Scholar]

- Kwon, H.-M.; Han, I.-S.; Kwon, S.-K.; Jang, J.-H.; Kwak, H.-Y.; Choi, W.-I.; Ha, M.-L.; Lee, J.-I.; Hwang, H.-S.; Lee, H.-D. Effects of High-Pressure Annealing on Random Telegraph Signal Noise Characteristic of Source Follower Block in CMOS Image Sensor. IEEE Electron Device Lett. 2013, 34, 190–192. [Google Scholar] [CrossRef]

- de Jong, M.J.; Salm, C.; Schmitz, J. Observations on the recovery of hot carrier degradation of hydrogen/deuterium passivated nMOSFETs. Microelectron. Reliab. 2017, 76–77, 136–140. [Google Scholar] [CrossRef]

- Jech, M.; El-Sayed, A.-M.; Tyaginov, S.; Waldhör, D.; Bouakline, F.; Saalfrank, P.; Jabs, D.; Jungemann, C.; Waltl, M.; Grasser, T. Quantum Chemistry Treatment of Silicon-Hydrogen Bond Rupture by Nonequilibrium Carriers in Semiconductor Devices. Phys. Rev. Appl. 2021, 16, 014026. [Google Scholar] [CrossRef]

- Wang, R.; Sun, Z.; Liu, Y.-Y.; Yu, Z.; Wang, Z.; Jiang, X.; Huang, R. Understanding Hot Carrier Reliability in FinFET Technology from Trap-based Approach. In Proceedings of the IEEE Int’l Electron Devices Meeting (IEDM), San Francisco, CA, USA, 11–16 December 2021; pp. 661–664. [Google Scholar]

- Skuja, L. Optical active oxygen-deficiency-related centers in amorphous silicon dioxide. J. Non-Cryst. Solids 1998, 239, 16–48. [Google Scholar] [CrossRef]

- Pantelides, S.T.; Lu, Z.-Y.; Nicklaw, C.; Bakos, T.; Rashkeev, S.N.; Fleetwood, D.M.; Schrimpf, R.D. The E’ center and oxygen vacancies in SiO2. J. Non-Cryst. Solids 2008, 239, 217–223. [Google Scholar] [CrossRef]

- Wilhelmer, C.; Waldhoer, D.; Jech, M.; El-Sayed, A.-M.B.; Cvitkovich, L.; Waltl, M.; Grasser, T. Ab initio investigations in amorphous silicon dioxide: Proposing a multi-state defect model for electron and hole capture. Microelectron. Reliab. 2022, 139, 114801. [Google Scholar] [CrossRef]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2026 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license.