An Energy-Efficient FPGA-Based Real-Time IMDD OFDM-PON Enabled by an Efficient FFT

Abstract

1. Introduction

2. Operation Principle

2.1. FPGA Power Consumption Model for OFDM-PON

2.2. Block Memory-Efficient Architecture for Half-Parallel FFT

3. Energy-Efficient Scheme for the Half-Parallel 64-Point FFT

3.1. Overall Architecture of the FPGA-Based Real-Time IMDD OFDM-PON Energy-Efficient Half Parallel 64-Point FFT Design

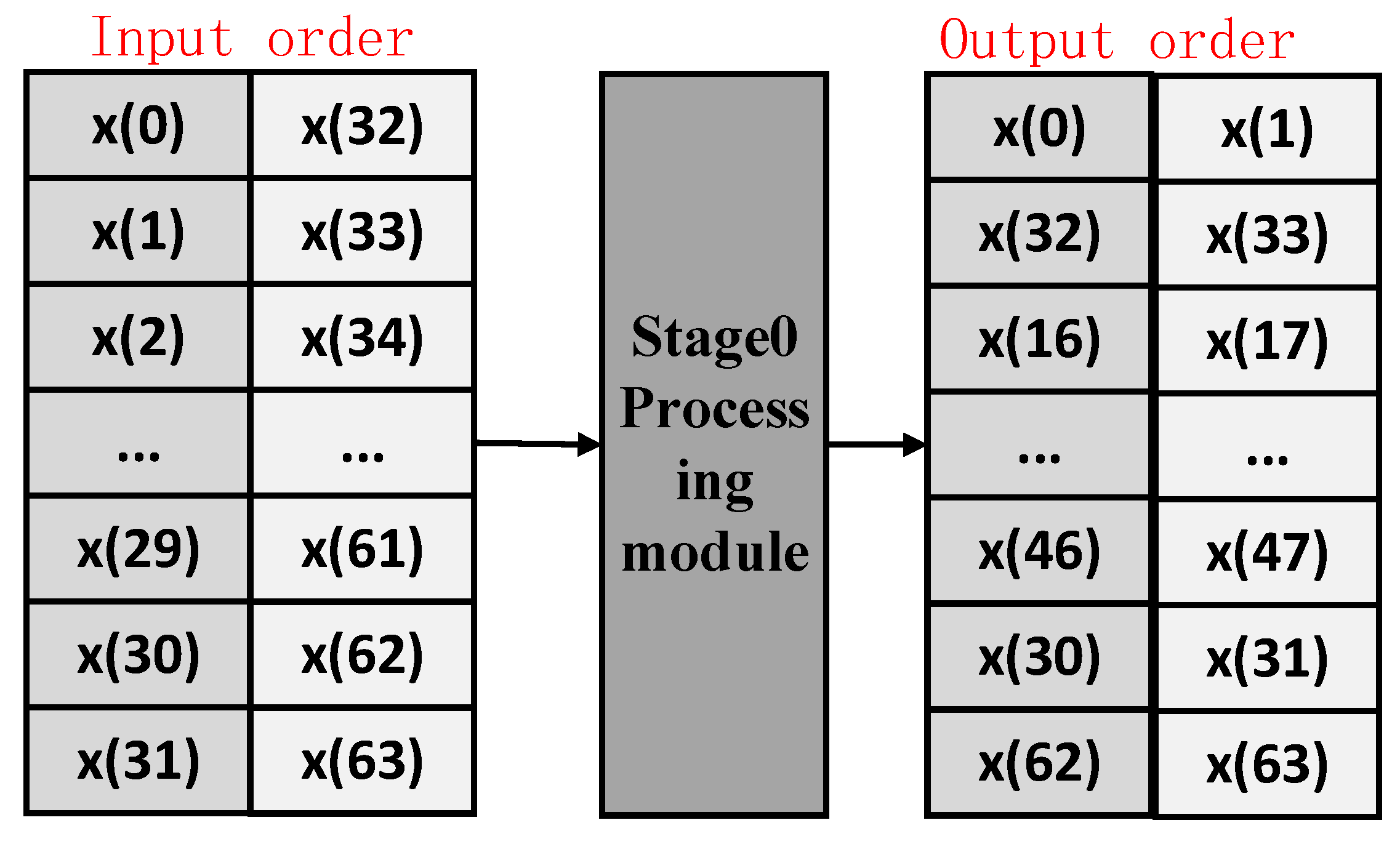

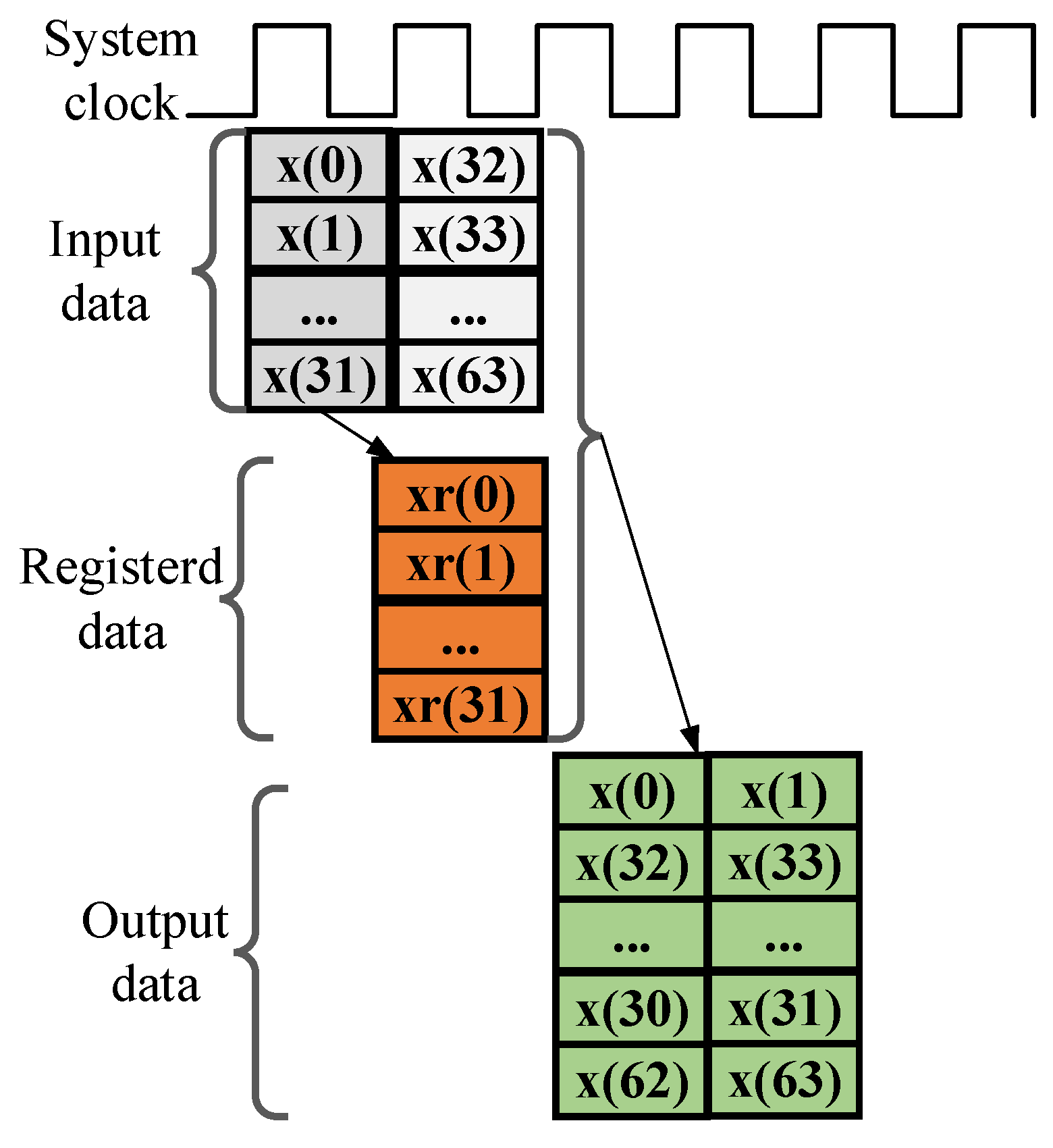

3.1.1. Stage 0 Processing Module: Input Reordering

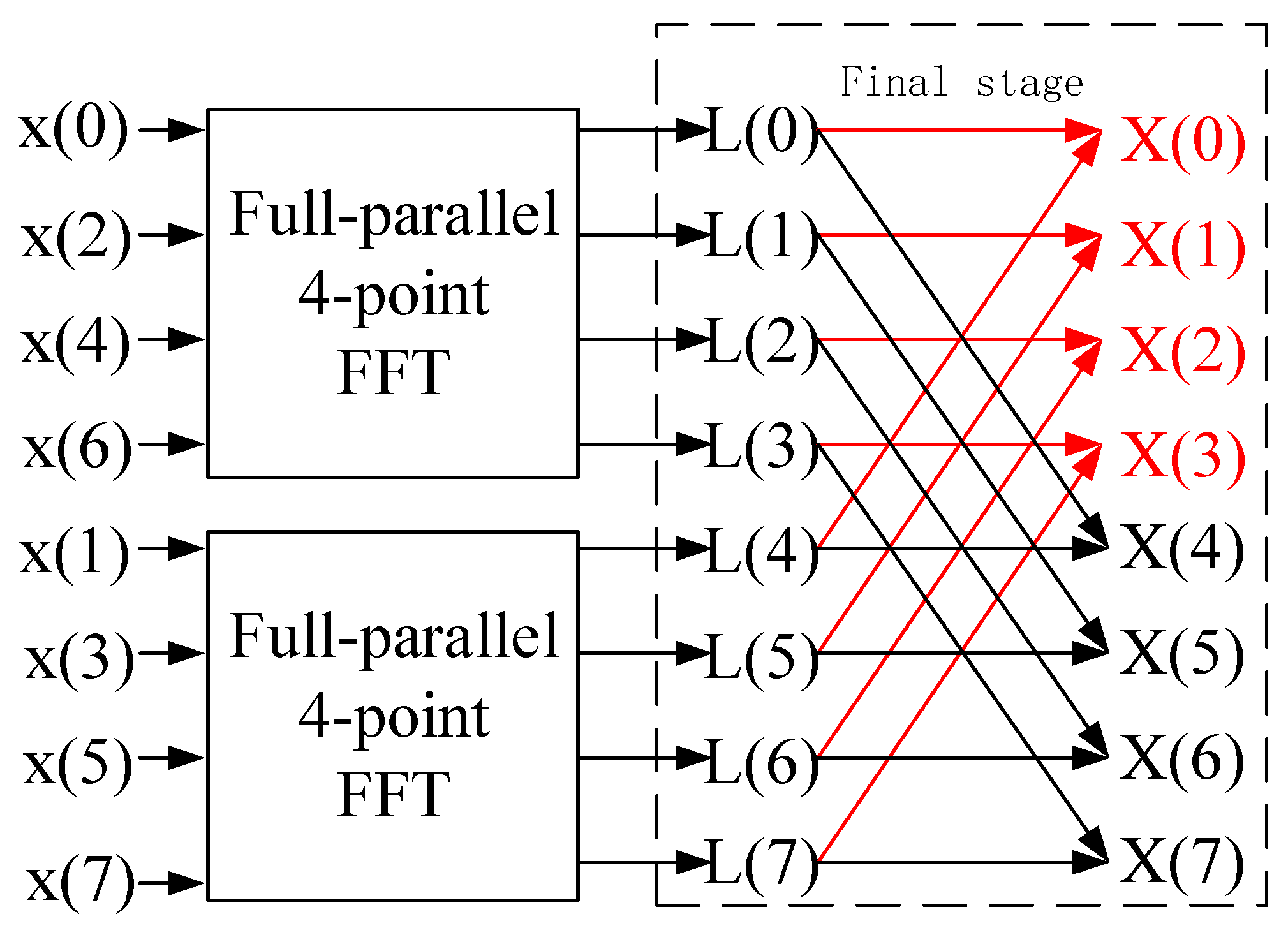

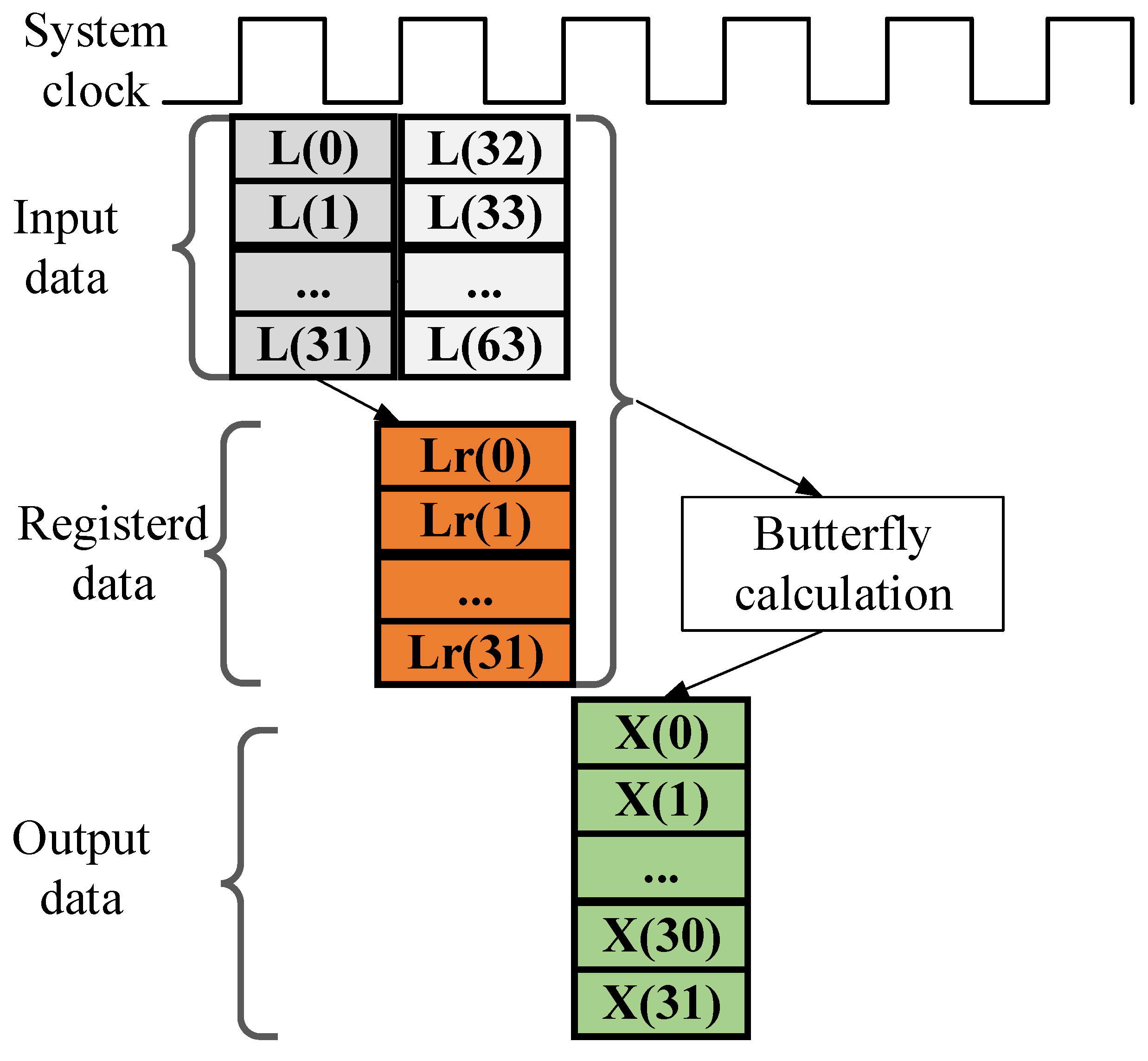

3.1.2. Final Processing Module: Output Combination

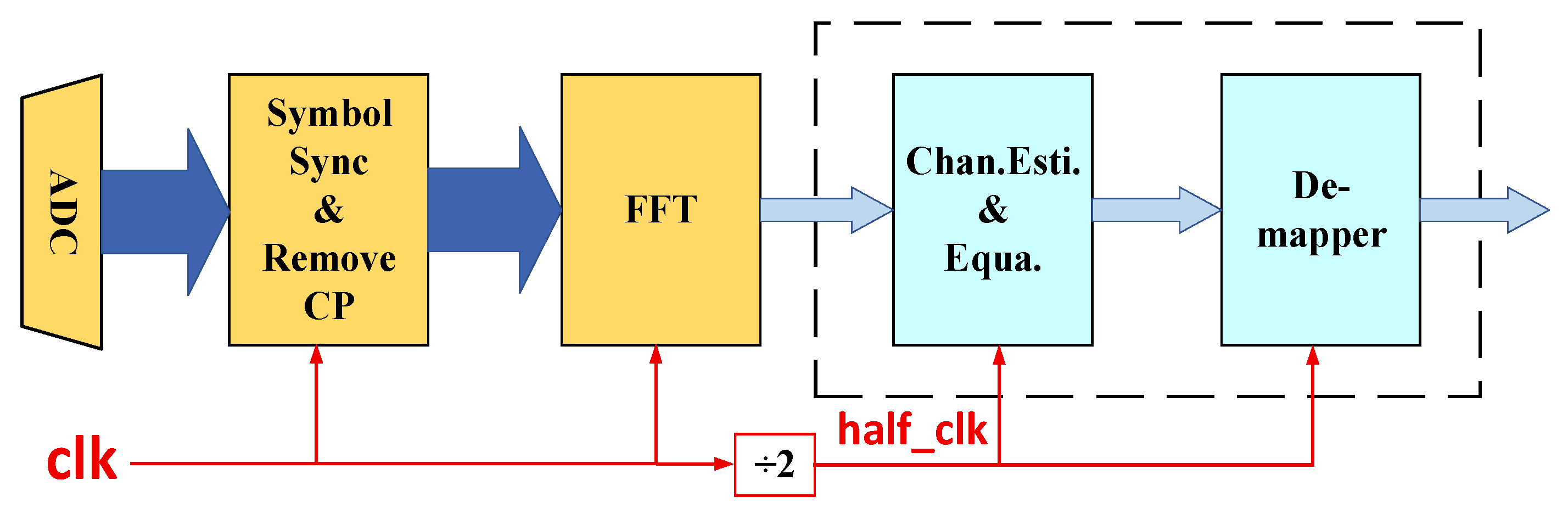

3.2. System-Level Energy-Efficient Solution for FPGA-Based Real-Time IMDD OFDM-PON Receiver

4. Experimental Setup

5. Experimental Results

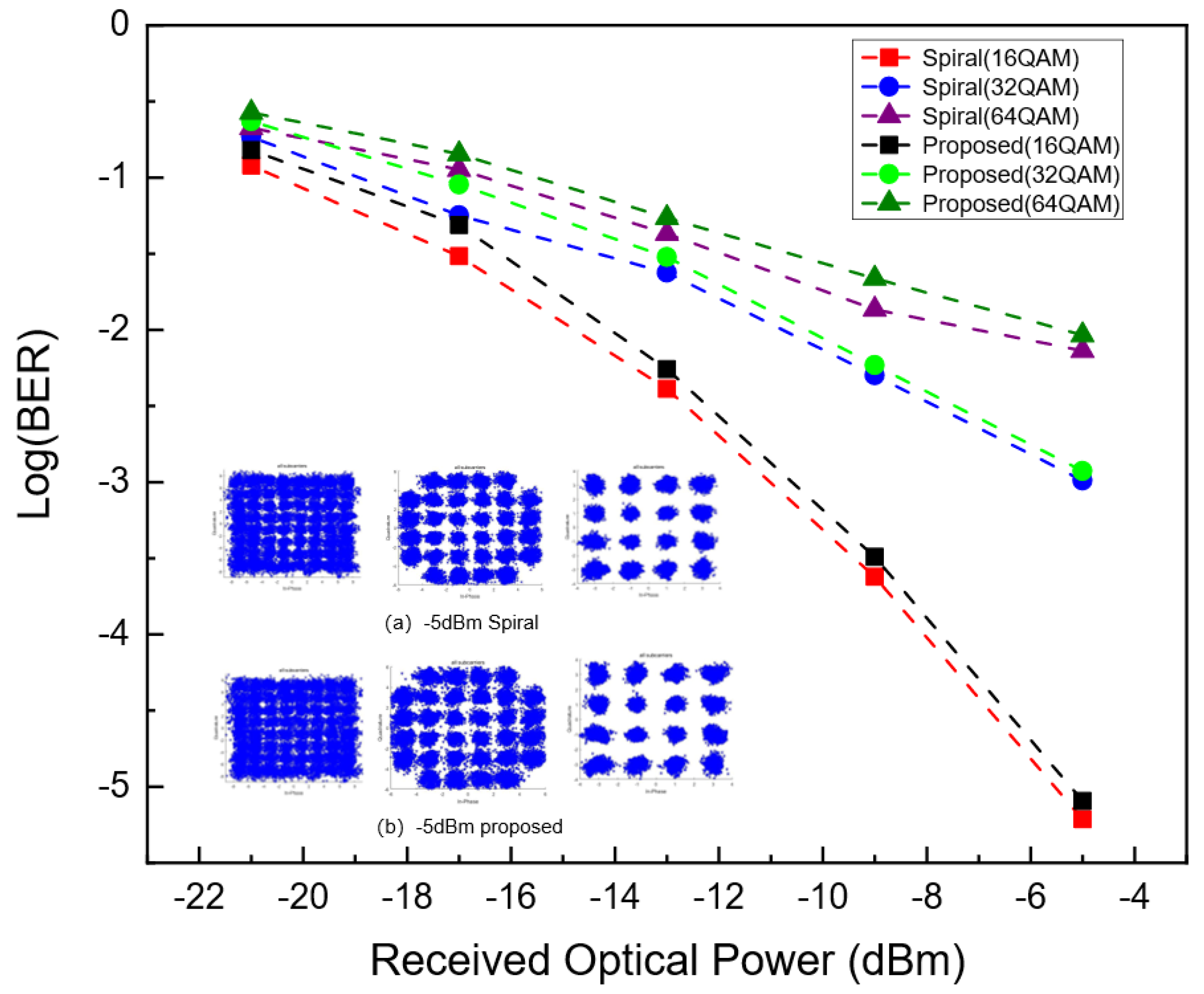

5.1. Real-Time Experimental Verification of the BER Performance of the Proposed FFT

5.1.1. Selection of BER Performance Indicator and FFT Bit Resolution

5.1.2. Comparative BER Performance of Spiral FFT and Proposed FFT

5.1.3. BER Performance of the Proposed FFT with Adaptive Modulation

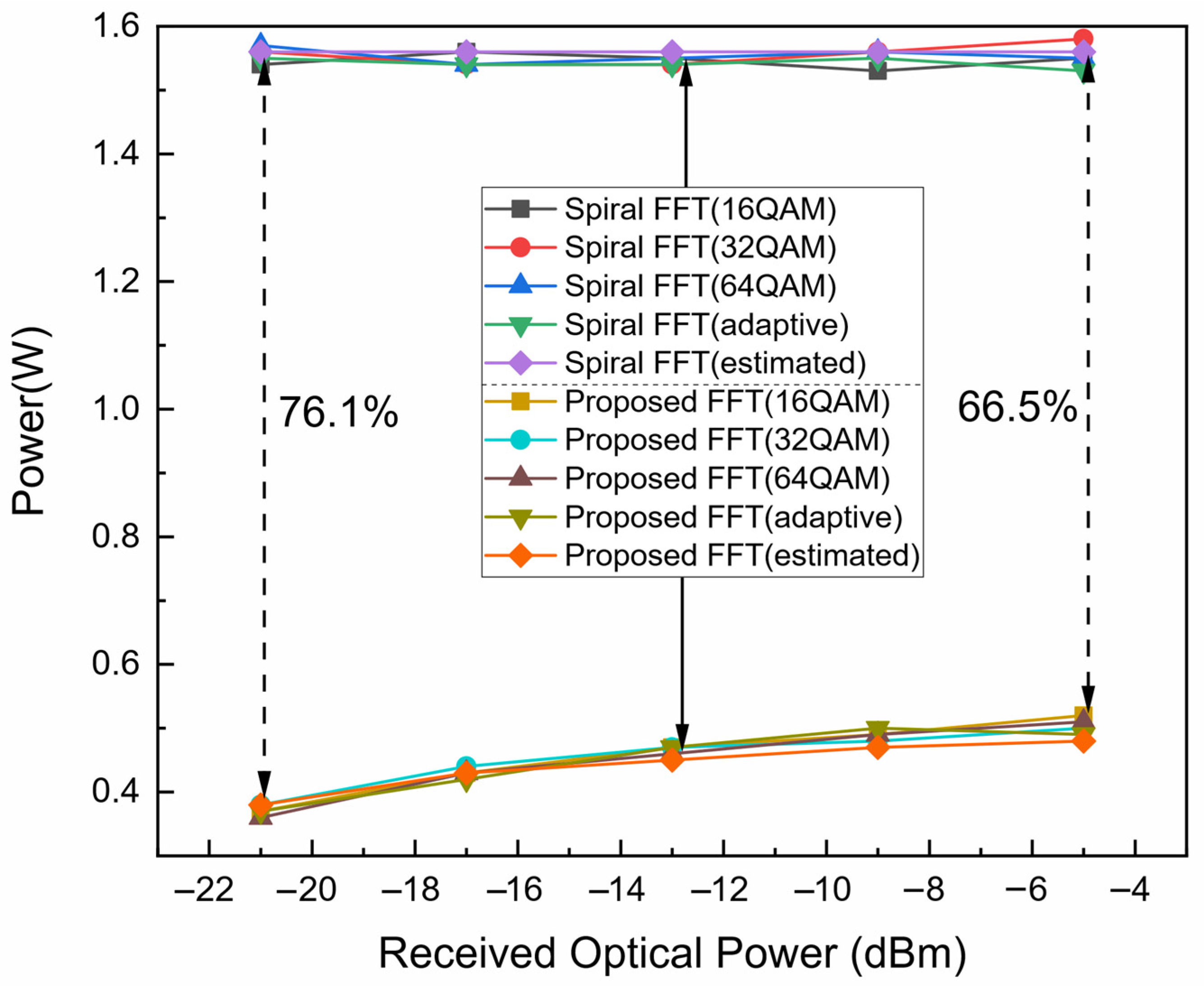

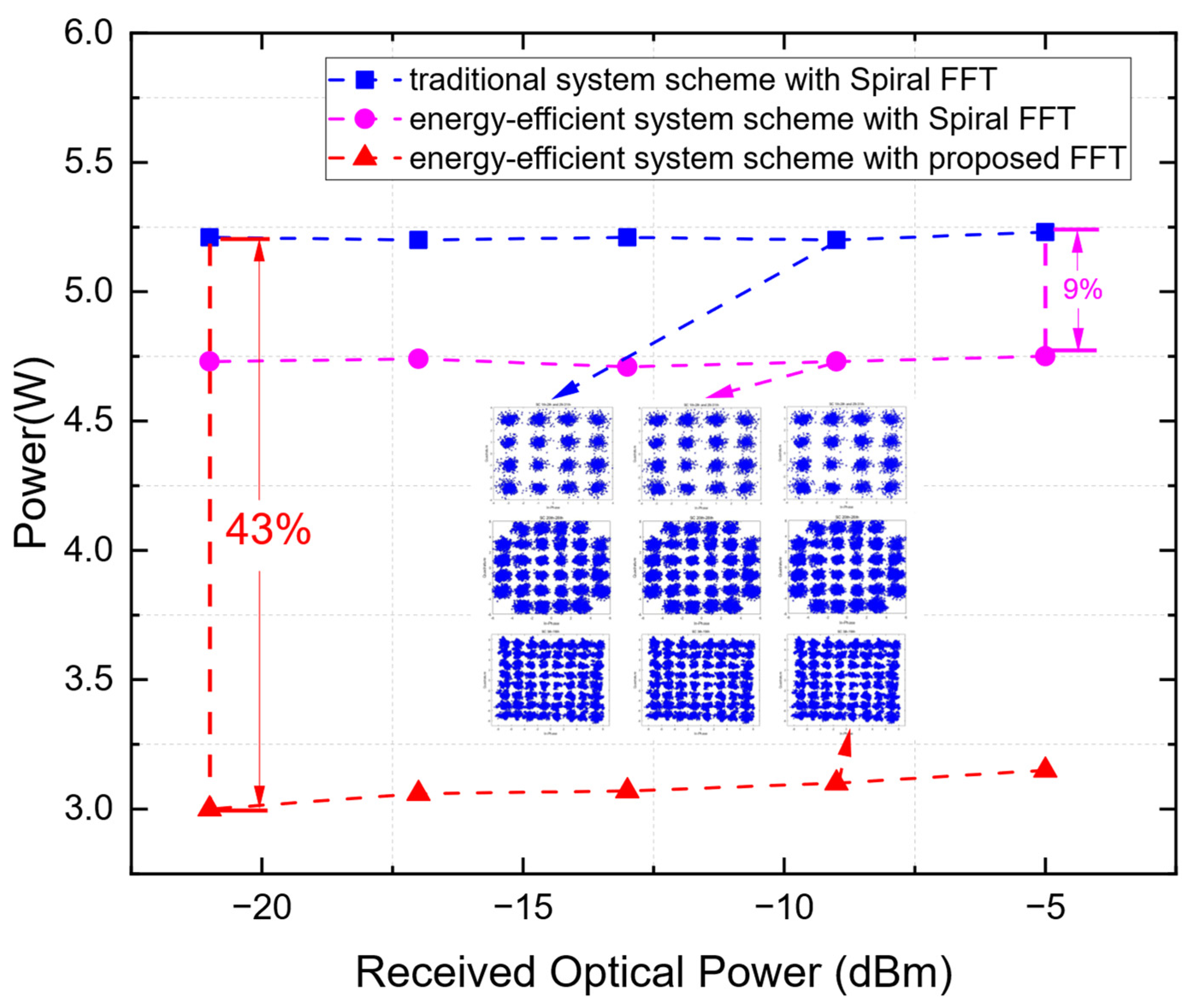

5.2. Real-Time Experimental Verification of the Energy-Efficient Effect of Proposed FFT

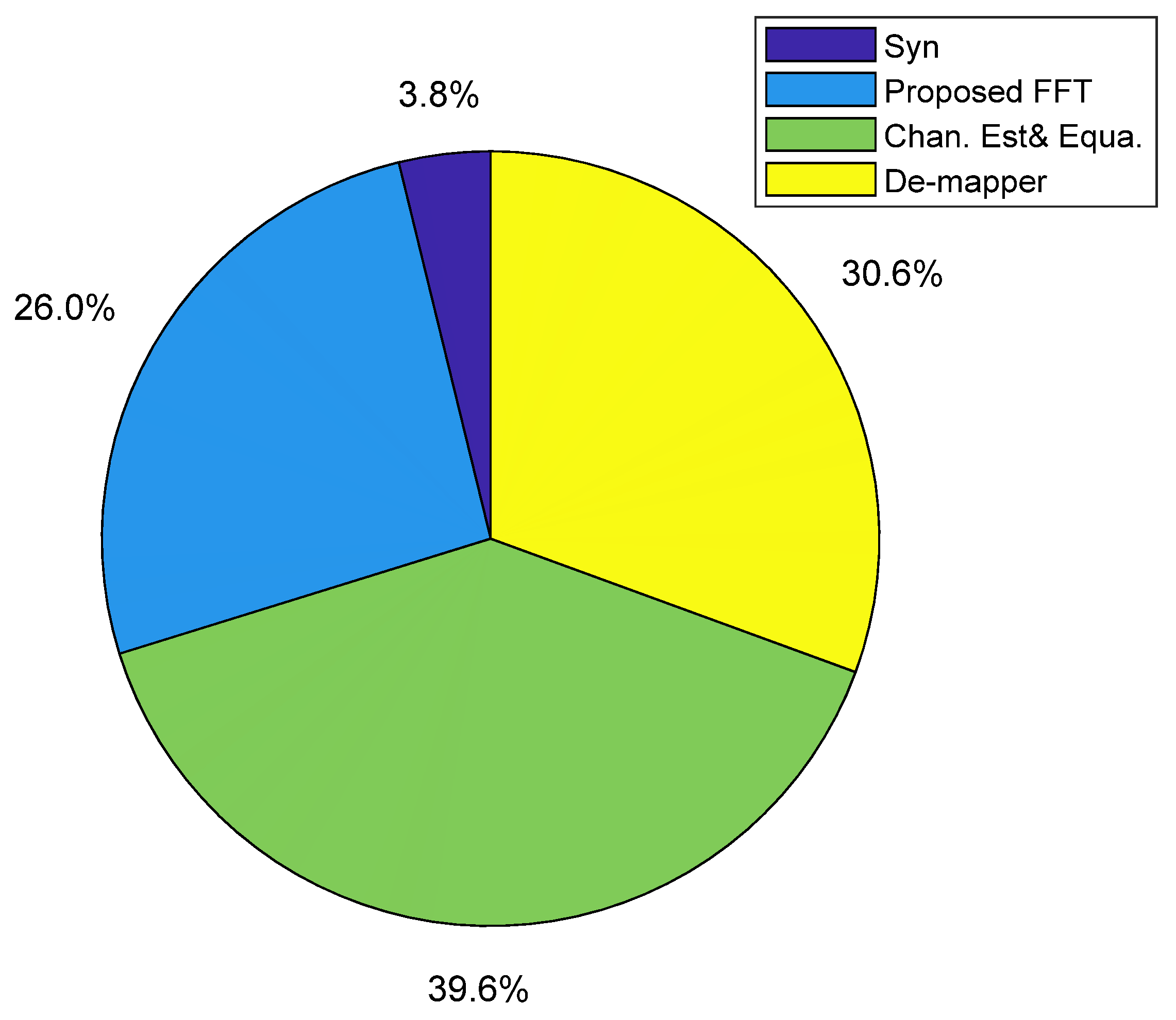

5.3. Real-Time Experimental Verification of the Energy-Efficient Effect of the Overall Energy-Efficient Scheme

6. Conclusions

Author Contributions

Funding

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Abdollahbeigi, B.; Salehi, F. The role of information and communication industry (ICT) in the reduction of greenhouse gas emissions in Canada. Int. Res. J. Bus. Stud. 2021, 13, 307–315. [Google Scholar] [CrossRef]

- Arfeen, M.Z.; Butt, R.A.; Ahmed, F.; Quang, N.N. A Comprehensive Framework For Itu Next Generation Pons. J. Electr. Electron. Eng. 2022, 1, 165–172. [Google Scholar] [CrossRef]

- Nikoukar, A.; Hwang, I.S.; Wang, C.J.; Ab-Rahman, M.S.; Liem, A.T. A SIEPON based transmitter sleep mode energy-efficient mechanism in EPON. Opt. Fiber Technol. 2015, 23, 78–89. [Google Scholar] [CrossRef]

- Helmy, A.; Nayak, A. Towards more dynamic energy-efficient bandwidth allocation in EPONs. In Proceedings of the 2018 IEEE Global Communications Conference (GLOBECOM), Abu Dhabi, United Arab Emirates, 9–13 December 2018; IEEE: New York, NY, USA, 2018; pp. 1–6. [Google Scholar]

- Lee, J.; Park, J.; Han, S.K. OFDM-NOMA Optical Transmission Utilizing Dispersion-Induced Power Fading of SMF for Multi-Distance PON. J. Light. Technol. 2025, 43, 4607–4615. [Google Scholar] [CrossRef]

- Hu, X.; Cao, P.; Zhang, L.; Jiang, L.; Su, Y. Energy-efficient optical network units for OFDM PON based on time-domain interleaved OFDM technique. Opt. Express 2014, 22, 13043–13049. [Google Scholar] [CrossRef] [PubMed]

- Skubic, B.; de Betou, E.I.; Ayhan, T.; Dahlfort, S. Energy-efficient next-generation optical access networks. IEEE Commun. Mag. 2012, 50, 122–127. [Google Scholar] [CrossRef]

- Qin, Y.; Zhang, J. Novel toggle-rate based energy-efficient scheme for heavy load real-time IM-DD OFDM-PON with ONU LLID identification in time-domain using amplitude decision. Opt. Express 2017, 25, 16771–16782. [Google Scholar] [CrossRef] [PubMed]

- Zhang, J.; Zhao, J.; Huang, H.; Ye, N.; Giddings, R.P.; Li, Z.; Qin, D.; Zhang, Q.; Tang, J.M. A clock-gating-based energy-efficient scheme for ONUs in real-time IMDD OFDM-PONs. J. Light. Technol. 2020, 38, 3573–3583. [Google Scholar] [CrossRef]

- Inan, B.; Adhikari, S.; Karakaya, O.; Kainzmaier, P.; Mocker, M.; von Kirchbauer, H.; Hanik, N.; Jansen, S.L. Real-time 93.8-Gb/s polarization-multiplexed OFDM transmitter with 1024-point IFFT. Opt. Express 2011, 19, B64–B68. [Google Scholar] [CrossRef] [PubMed]

- Bouziane, R.; Milder, P.A.; Koutsoyannis, R.; Benlachtar, Y.; Hoe, J.C.; Glick, M.; Killey, R. Dependence of optical OFDM transceiver ASIC complexity on FFT size. In Proceedings of the Optical Fiber Communication Conference, Los Angeles, CA, USA, 4–8 March 2012; Optica Publishing Group: Washington, DC, USA, 2012; p. JW2A.58. [Google Scholar]

- Kimura, H.; Nakamura, H.; Kimura, S.; Yoshimoto, N. Numerical analysis of dynamic SNR management by controlling DSP calculation precision for energy-efficient OFDM-PON. IEEE Photon. Technol. Lett. 2012, 24, 2132–2135. [Google Scholar] [CrossRef]

- Kimura, H.; Asaka, K.; Nakamura, H.; Kimura, S.; Yoshimoto, N. Energy efficient IM-DD OFDM-PON using dynamic SNR management and adaptive modulation. Opt. Express 2014, 22, 1789–1795. [Google Scholar] [CrossRef] [PubMed]

- Zhang, J.; Tang, Z.; Giddings, R.; Wu, Q.; Wang, W.; Cao, B.; Zhang, Q.; Tang, J. Stage-Dependent DSP operation range clipping-induced bit resolution reductions of full parallel 64-Point FFTs incorporated in FPGA-Based optical OFDM receivers. J. Light. Technol. 2016, 34, 3752–3760. [Google Scholar] [CrossRef]

- Zhang, J.J.; Wang, W.L.; Giddings, R.P.; Zhang, Q.W.; Peng, J.J.; Chen, J.; Tang, J.M. Analytical Solution of Stage-Dependent Bit Resolution of Full Parallel Variable Point FFTs for Real-Time DSP Implementation. J. Light. Technol. 2018, 36, 5177–5187. [Google Scholar] [CrossRef]

- Spiral. Spiral Software/Hardware Generation for Performance. Available online: http://www.spiral.net/hardware/dftgen.html (accessed on 10 September 2025).

- Nasser, Y.; Lorandel, J.; Prevotet, J.C.; Helard, M. RTL to transistor level power modeling and estimation techniques for FPGA and ASIC: A survey. IEEE Trans. Comput. Aided Des. Integr. Circuits Syst. 2021, 40, 479–493. [Google Scholar] [CrossRef]

- Verma, G.; Mishra, S.; Aggarwal, S.; Singh, S.; Shekhar, S.; Virdi, S.K. Power consumption analysis of BCD adder using xpower analyzer on VIRTEX FPGA. Indian J. Sci. Technol. 2015, 8, IPL160. [Google Scholar] [CrossRef]

| Parameters | Value |

|---|---|

| 2.08 × 10−5 W/MHz | |

| 2.63 × 10−5 W/MHz | |

| 7.69 × 10−5 W/MHz | |

| 4.42 × 10−3 W/MHz | |

| 9.73 × 10−4 W/MHz |

| Parameters | Value |

|---|---|

| FFT/IFFT points | 64 |

| Data-carrying subcarriers | From 2 to 28 |

| Modulation format | 2/4/8/16/32/64-QAM |

| ADC/DAC resolution | 10/12-bit |

| ADC& DAC sample rate | 4 GS/s |

| OFDM frame CP | 16 samples (4 ns) |

| PRBS | 215 − 1 |

| Transmitter output power | +7.75 dBm |

| DFB wavelength | 1549.98 nm |

| DFB modulation bandwidth | 2.7 GHz |

| DFB bias current | 45 mA |

| DFB driving voltage | 2 Vpp |

| PIN detector bandwidth | 40 MHz~3 GHz |

| PIN responsivity | 0.9 mA/mW |

| Receive Optical Power | Stage Index | |||||

|---|---|---|---|---|---|---|

| 1 | 2 | 3 | 4 | 5 | 6 | |

| −5 dBm | 11 | 12 | 11 | 11 | 11 | 11 |

| −9 dBm | 11 | 12 | 10 | 11 | 10 | 11 |

| −13 dBm | 11 | 12 | 10 | 10 | 10 | 10 |

| −17 dBm | 11 | 12 | 9 | 10 | 9 | 10 |

| −21 dBm | 11 | 12 | 8 | 9 | 8 | 9 |

| Received Optical Power | FF/LUT/LUTRAM/BRAM/DSP |

|---|---|

| −5 dBm | 10,816/9855/0/0/0 |

| −9 dBm | 10,424/9639/0/0/0 |

| −13 dBm | 9896/9231/0/0/0 |

| −17 dBm | 9482/8949/0/0/0 |

| −21 dBm | 8602/7789/0/0/0 |

| Quantization Bits | FF/LUT/LUTRAM/BRAM/DSP |

|---|---|

| 16 | 19,813/12,855/2840/96/172 |

| 15 | 14,368/11,876/2020/48/172 |

| 14 | 13,385/11,203/2007/48/172 |

| 13 | 12,402/10,567/1997/48/172 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Zheng, Z.; Chen, T.; Qu, Y.; Xu, Z.; Chi, Y.; Wang, X.; Zhang, J. An Energy-Efficient FPGA-Based Real-Time IMDD OFDM-PON Enabled by an Efficient FFT. Sensors 2025, 25, 7302. https://doi.org/10.3390/s25237302

Zheng Z, Chen T, Qu Y, Xu Z, Chi Y, Wang X, Zhang J. An Energy-Efficient FPGA-Based Real-Time IMDD OFDM-PON Enabled by an Efficient FFT. Sensors. 2025; 25(23):7302. https://doi.org/10.3390/s25237302

Chicago/Turabian StyleZheng, Zhe, Tianyang Chen, Yuanzhe Qu, Zhengjun Xu, Yingying Chi, Xin Wang, and Junjie Zhang. 2025. "An Energy-Efficient FPGA-Based Real-Time IMDD OFDM-PON Enabled by an Efficient FFT" Sensors 25, no. 23: 7302. https://doi.org/10.3390/s25237302

APA StyleZheng, Z., Chen, T., Qu, Y., Xu, Z., Chi, Y., Wang, X., & Zhang, J. (2025). An Energy-Efficient FPGA-Based Real-Time IMDD OFDM-PON Enabled by an Efficient FFT. Sensors, 25(23), 7302. https://doi.org/10.3390/s25237302