A Multimode 28 GHz CMOS Fully Differential Beamforming IC for Phased Array Transceivers

Abstract

:1. Introduction

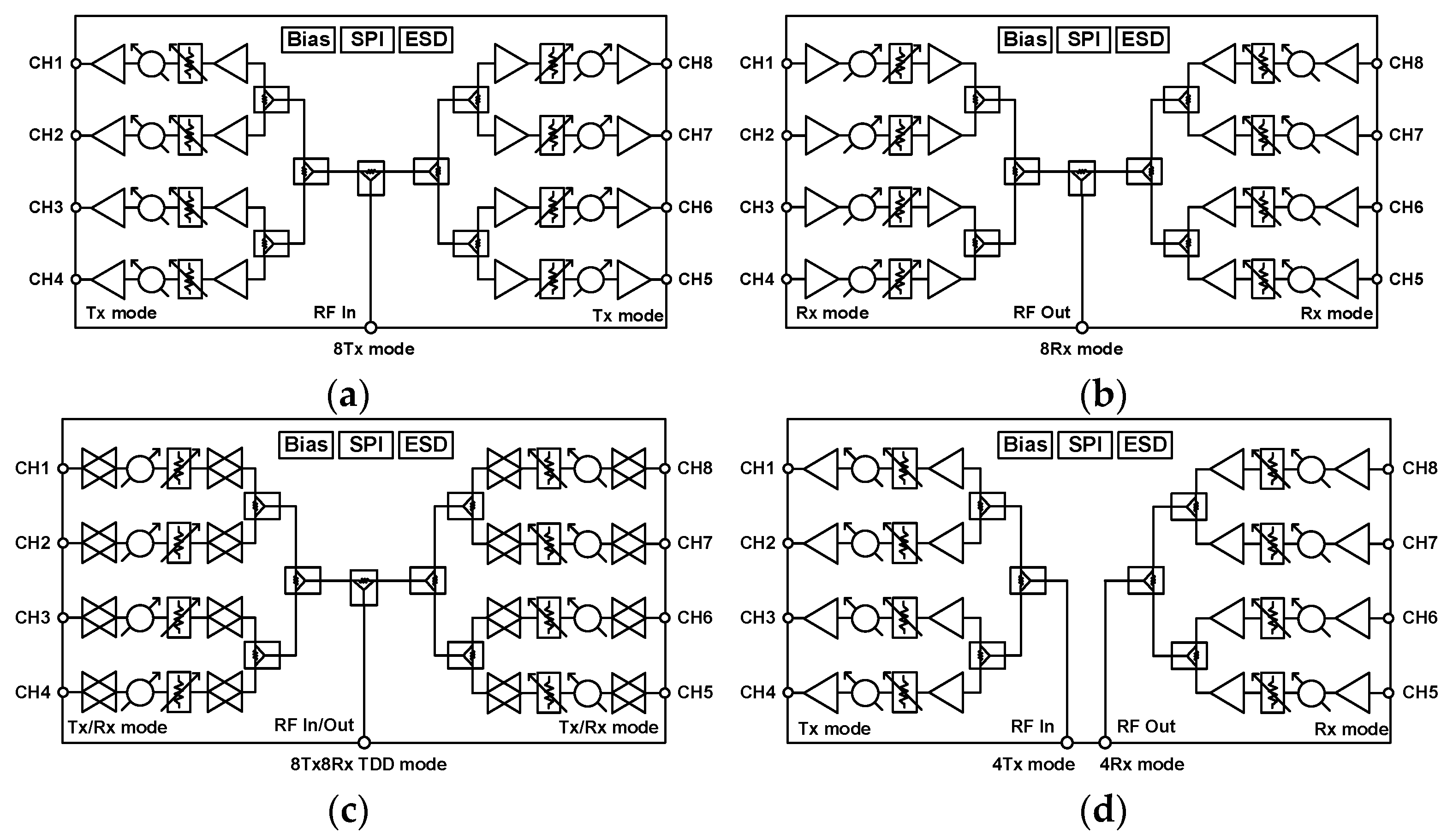

2. Design of 28 GHz Eight-Channel Multimode Beamforming IC

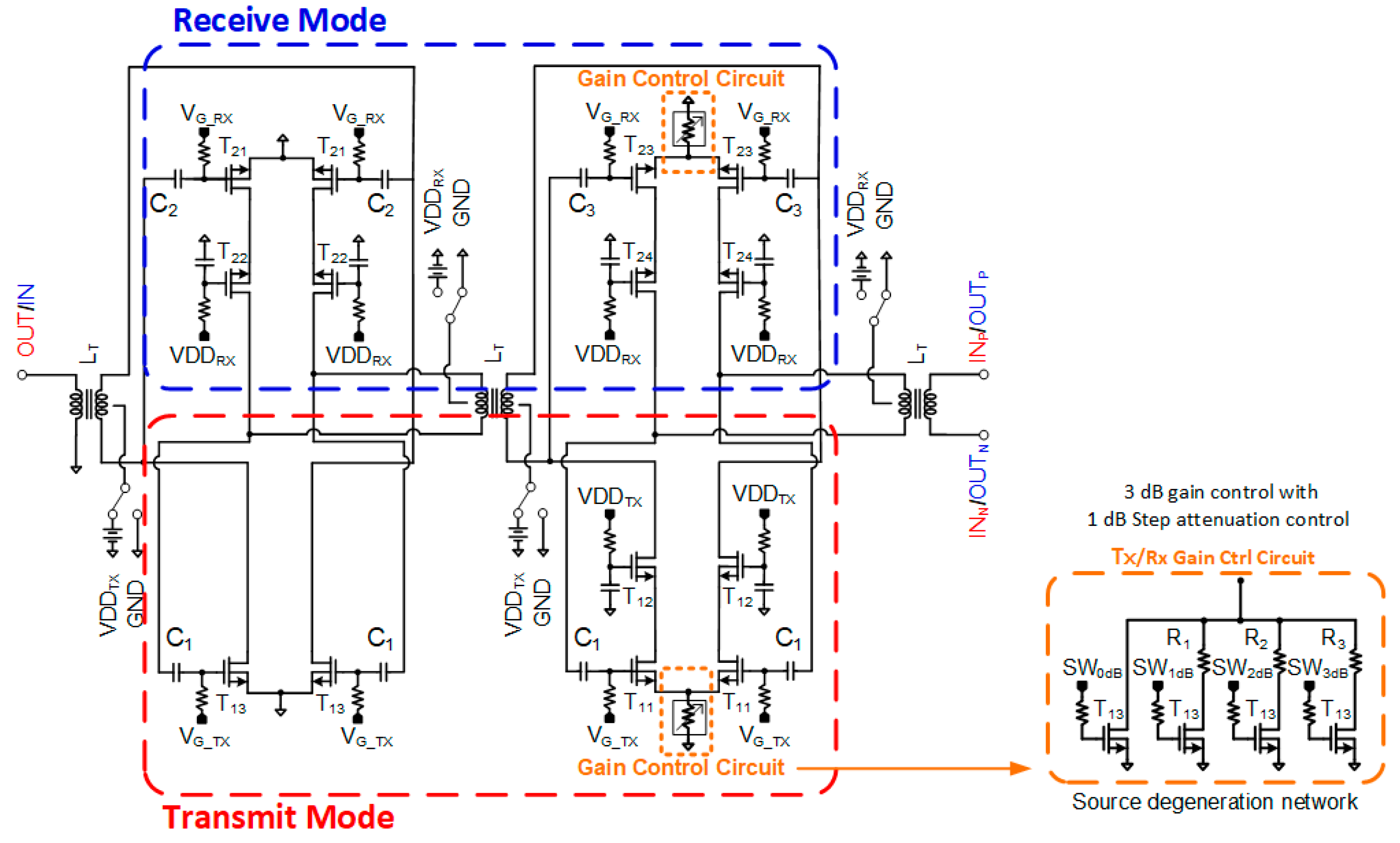

2.1. Differential Two-Stage Bi-Directional Amplifier

2.2. Differential Phase Shifters and Attenuators

2.3. Differential Two-Way Power Divider

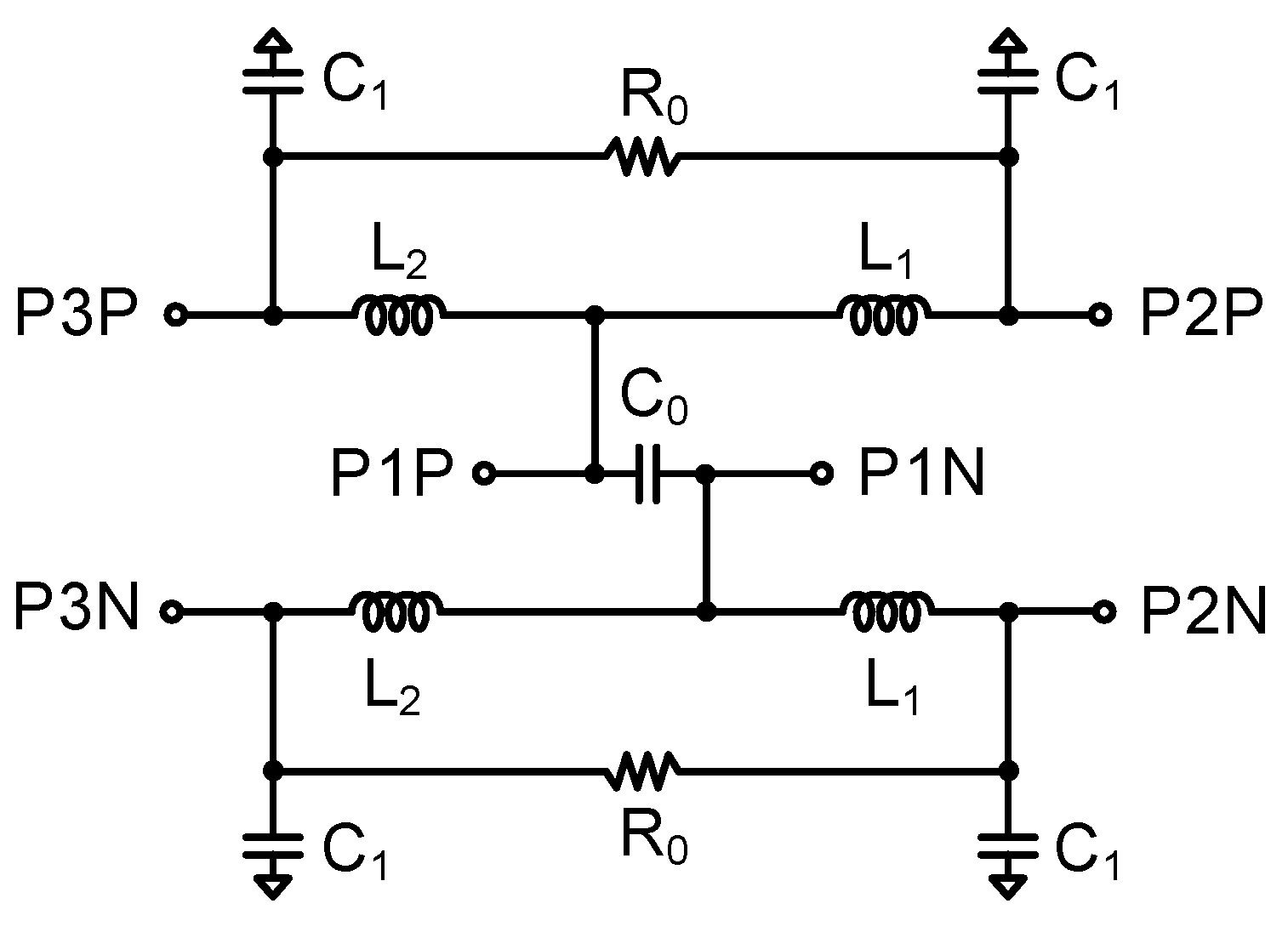

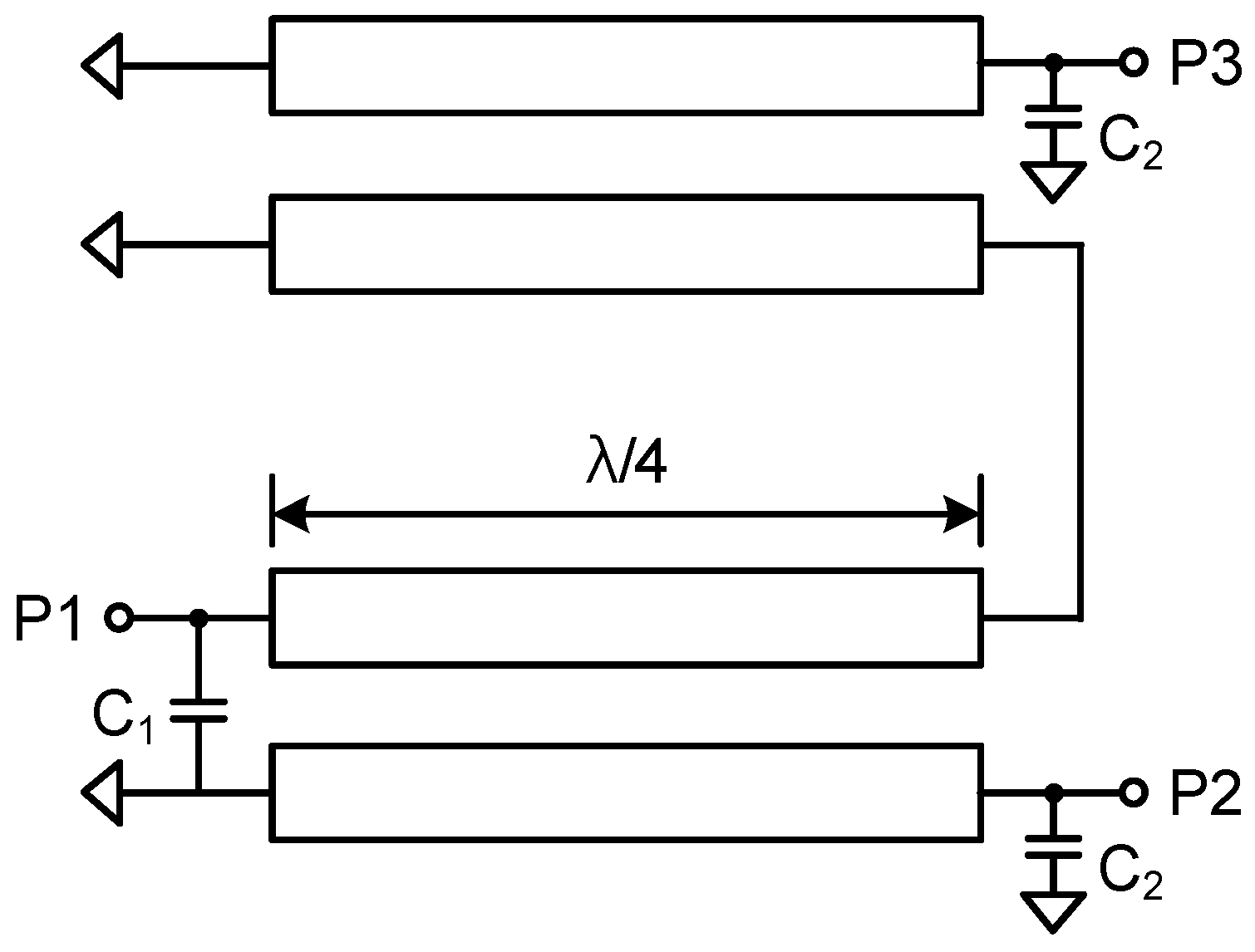

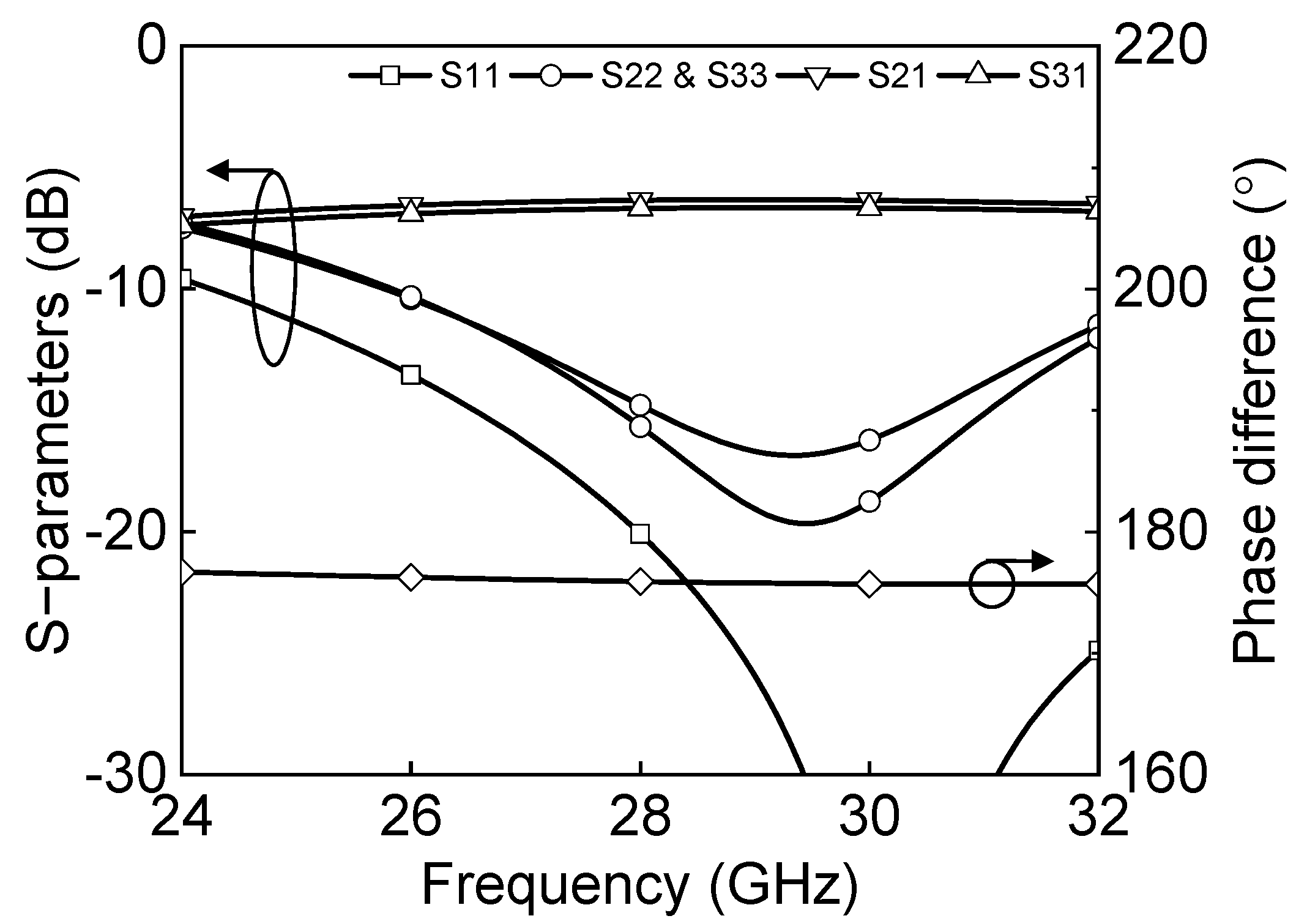

2.4. Marchand Balun

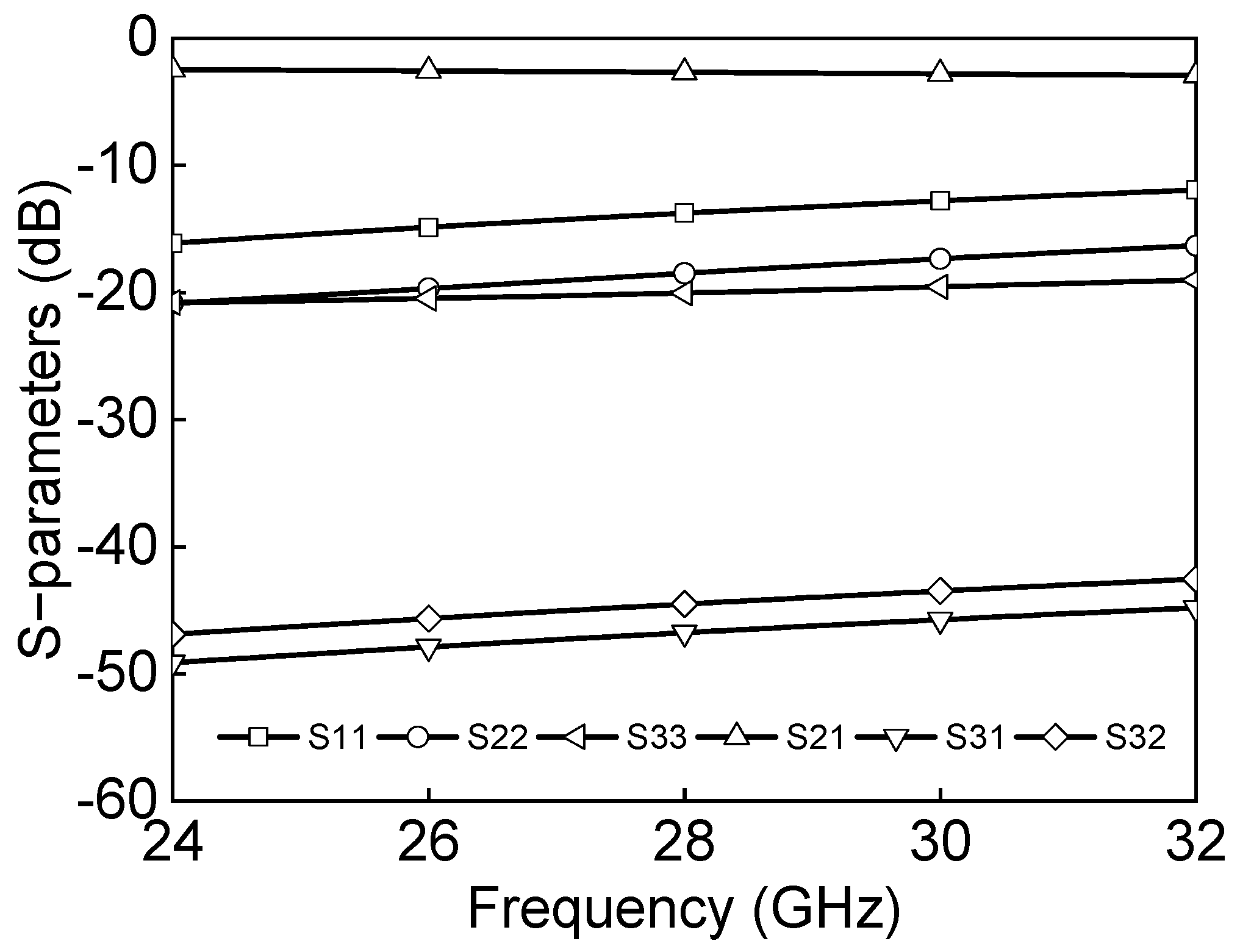

2.5. Differential SPDT Switch

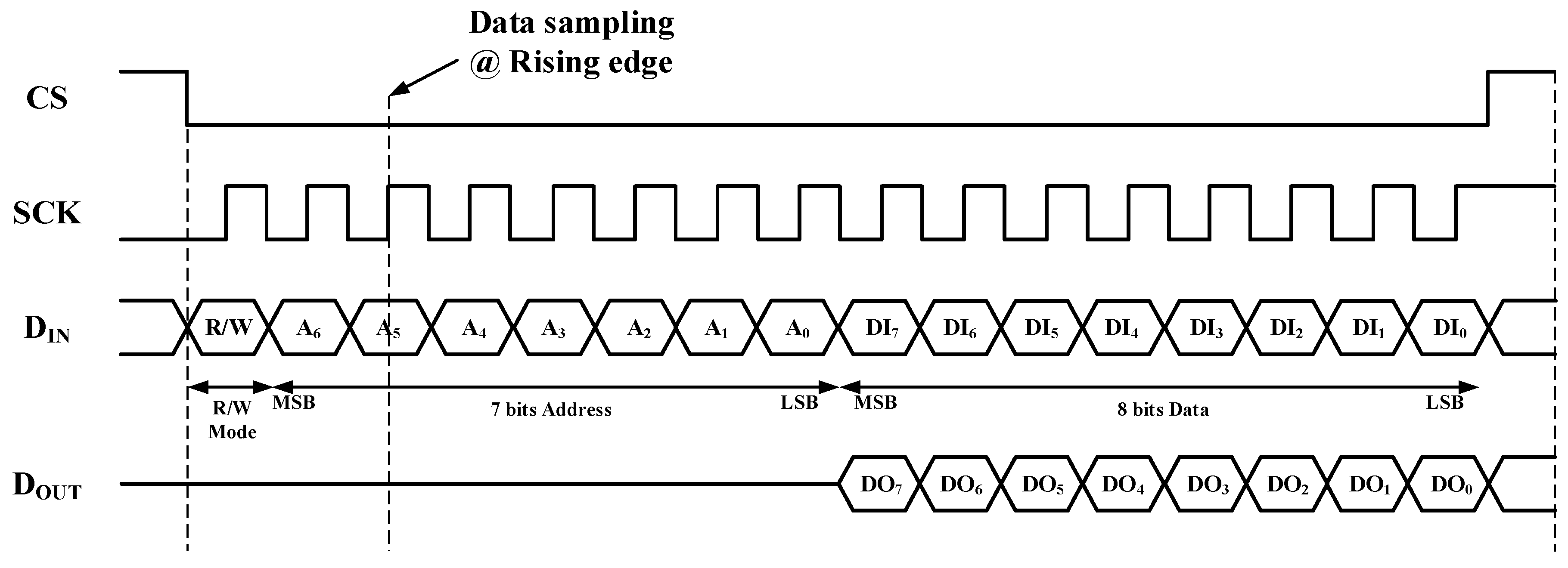

2.6. Serial Peripheral Interface

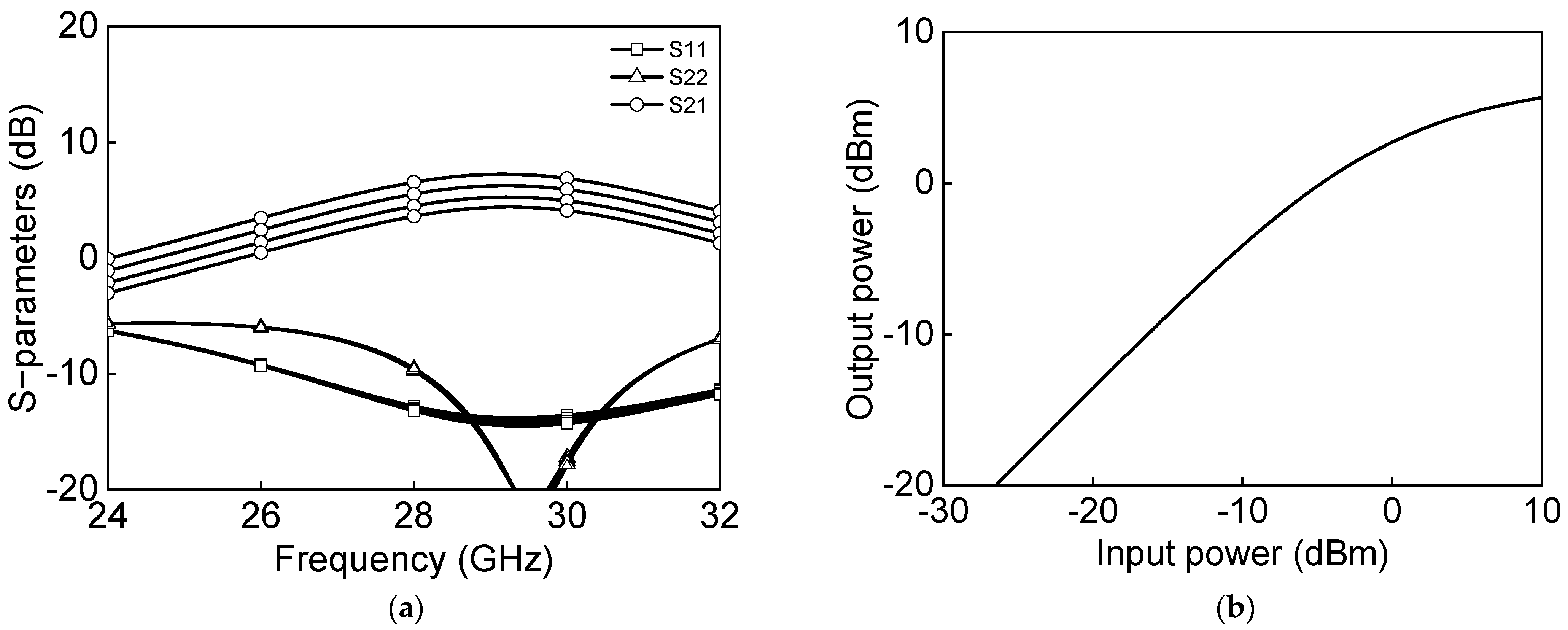

3. Measurement Results

4. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Ahmed, N.; Kibaroglu, K.; Sayginer, M.; Rebeiz, G.M. An In-Situ Self-Test and Self-Calibration Technique Utilizing Antenna Mutual Coupling for 5G Multi-Beam TRX Phased Arrays. In Proceedings of the 2019 IEEE MTT-S International Microwave Symposium (IMS), Boston, MA, USA, 2–7 June 2019; pp. 1229–1232. [Google Scholar]

- Kibaroglu, K.; Sayginer, M.; Phelps, T.; Rebeiz, G.M. A 64-Element 28-GHz Phased-Array Transceiver with 52-dBm EIRP and 8–12-Gb/s 5G Link at 300 Meters without Any Calibration. IEEE Trans. Microw. Theory Tech. 2022, 70, 1715–1724. [Google Scholar] [CrossRef]

- Park, J.; Baek, D.; Kim, J.-G. A 28 GHz 8-Channel Fully Differential Beamforming IC in 65 nm CMOS Process. In Proceedings of the 2019 49th European Microwave Conference (EuMC), Paris, France, 29 September–4 October 2019; pp. 476–479. [Google Scholar]

- Park, J.; Lee, S.; Chun, J.; Jeon, L.; Hong, S. A 28-GHz Four-Channel Beamforming Front-End IC with Dual-Vector Variable Gain Phase Shifters for 64-Element Phased Array Antenna Module. IEEE J. Solid-State Circuits 2023, 58, 1142–1159. [Google Scholar] [CrossRef]

- Shinjo, S.; Nakatani, K.; Kamioka, J.; Komaru, R.; Noto, H.; Nakamizo, H.; Yamaguchi, S.; Uchida, S.; Okazaki, A.; Yamanaka, K. A 28GHz-Band Highly Integrated GaAs RF Frontend Module for Massive MIMO in 5G. In Proceedings of the 2018 IEEE MTT-S International Microwave Workshop Series on 5G Hardware and System Technologies (IMWS-5G), Dublin, Ireland, 27–29 August 2018; pp. 1–3. [Google Scholar]

- Sadhu, B.; Tousi, Y.; Hallin, J.; Sahl, S.; Reynolds, S.K.; Renstrom, O.; Sjogren, K.; Haapalahti, O.; Mazor, N.; Bokinge, B.; et al. A 28-GHz 32-Element TRX Phased-Array IC with Concurrent Dual-Polarized Operation and Orthogonal Phase and Gain Control for 5G Communications. IEEE J. Solid-State Circuits 2017, 52, 3373–3391. [Google Scholar] [CrossRef]

- Huang, M.Y.; Chi, T.; Li, S.; Huang, T.Y.; Wang, H. A 24.5–43.5-GHz Ultra-Compact CMOS Receiver Front End with Calibration-Free Instantaneous Full-Band Image Rejection for Multiband 5G Massive MIMO. IEEE J. Solid-State Circuits 2020, 55, 1177–1186. [Google Scholar] [CrossRef]

- Dunworth, J.D.; Jin, S.; Keeler, R.; Kwack, J.; Murphy, J.; Chevalier, P.; Pekarik, J.; Lee, K.; Ryu, K.; Lee, J.; et al. A 28 GHz Bulk-CMOS Dual-Polarization Phased-Array Transceiver with 24 Channels for 5G User and Basestation Equipment. In Proceedings of the 2018 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 11–15 February 2018; pp. 70–72. [Google Scholar]

- Chu, C.-Y.; Huang, C.-Y.; Chang, H.-S.; Hsieh, Y.-C.; Shih, C.-J.; Wang, Y.-H.; Chuang, H.-Y.; Wu, J.-S.; Horng, T.-S. A Fully-Integrated Ka-Band 4TX/4RX Phased-Array Transceiver IC in 65nm CMOS. In Proceedings of the 2016 IEEE International Symposium on Radio-Frequency Integration Technology (RFIT), Taipei, Taiwan, 12–14 December 2016; pp. 1–3. [Google Scholar]

- Kibaroglu, K.; Sayginer, M.; Rebeiz, G.M. A Low-Cost Scalable 32-Element 28-GHz Phased Array Transceiver for 5G Communication Links Based on a 2 × 2 Beamformer Flip-Chip Unit Cell. IEEE J. Solid-State Circuits 2018, 53, 1260–1274. [Google Scholar] [CrossRef]

- Li, Z.; Pang, J.; Kubozoe, R.; Luo, X.; Wu, R.; Wang, Y.; You, D.; Fadila, A.A.; Alvin, J.; Liu, B.; et al. A 28 GHz CMOS Differential Bi-Directional Amplifier for 5G NR. In Proceedings of the 2020 25th Asia and South Pacific Design Automation Conference (ASP-DAC), Beijing, China, 13–16 January 2020; pp. 5–6. [Google Scholar]

- Jung, M.; Min, B.-W. A Compact Ka-Band 4-bit Phase Shifter with Low Group Delay Deviation. IEEE Microw. Wirel. Compon. Lett. 2020, 30, 414–416. [Google Scholar] [CrossRef]

- Yuan, Y.; Mu, S.-X.; Guo, Y.-X. 6-Bit Step Attenuators for Phased-Array System with Temperature Compensation Technique. IEEE Microw. Wirel. Compon. Lett. 2018, 28, 690–692. [Google Scholar] [CrossRef]

- Janisz, K.; Wincza, K.; Gruszczynski, S. Differential Lumped-Element Wilkinson Power Divider for Use in MMIC Systems. In Proceedings of the 2017 Mediterranean Microwave Symposium, Ljubljana, Slovenia, 22–24 November 2017; pp. 1–3. [Google Scholar]

- Lee, W.; Hong, S. Small-Size Low-Loss 28-GHz Body-Floated CMOS DPDT Switch Using Shared Matching Network. IEEE Microw. Wirel. Compon. Lett. 2018, 28, 1113–1115. [Google Scholar] [CrossRef]

- Pang, J.; Wu, R.; Wang, Y.; Dome, M.; Kato, H.; Huang, H.; Narayanan, A.T.; Liu, H.; Liu, B.; Nakamura, T.; et al. A 28-GHz CMOS Phased-Array Transceiver Based on LO Phase-Shifting Architecture with Gain Invariant Phase Tuning for 5G New Radio. IEEE J. Solid-State Circuits 2019, 54, 1228–1242. [Google Scholar] [CrossRef]

- Kim, H.-T.; Park, B.-S.; Song, S.-S.; Moon, T.-S.; Kim, S.-H.; Chang, J.-M.; Ho, Y.-C. A 28-GHz CMOS direct conversion transceiver with packaged 2 × 4 antenna arrays for 5G cellular system. IEEE J. Solid-State Circuits 2018, 53, 1245–1259. [Google Scholar] [CrossRef]

| Ref. | This Work | [4] | [16] | [17] |

|---|---|---|---|---|

| Tech (CMOS) | 65 nm | 65 nm | 65 nm | 28 nm |

| Freq. (GHz) | 27.0–29.5 | 26.5–30 | 26.5–29.5 | 25.8–28 |

| Number of channels | 8 TRx | 4TRx | 4 TRx | 8 TRx |

| Single-ended/Differential | Differential | Differential | Differential | Single-ended |

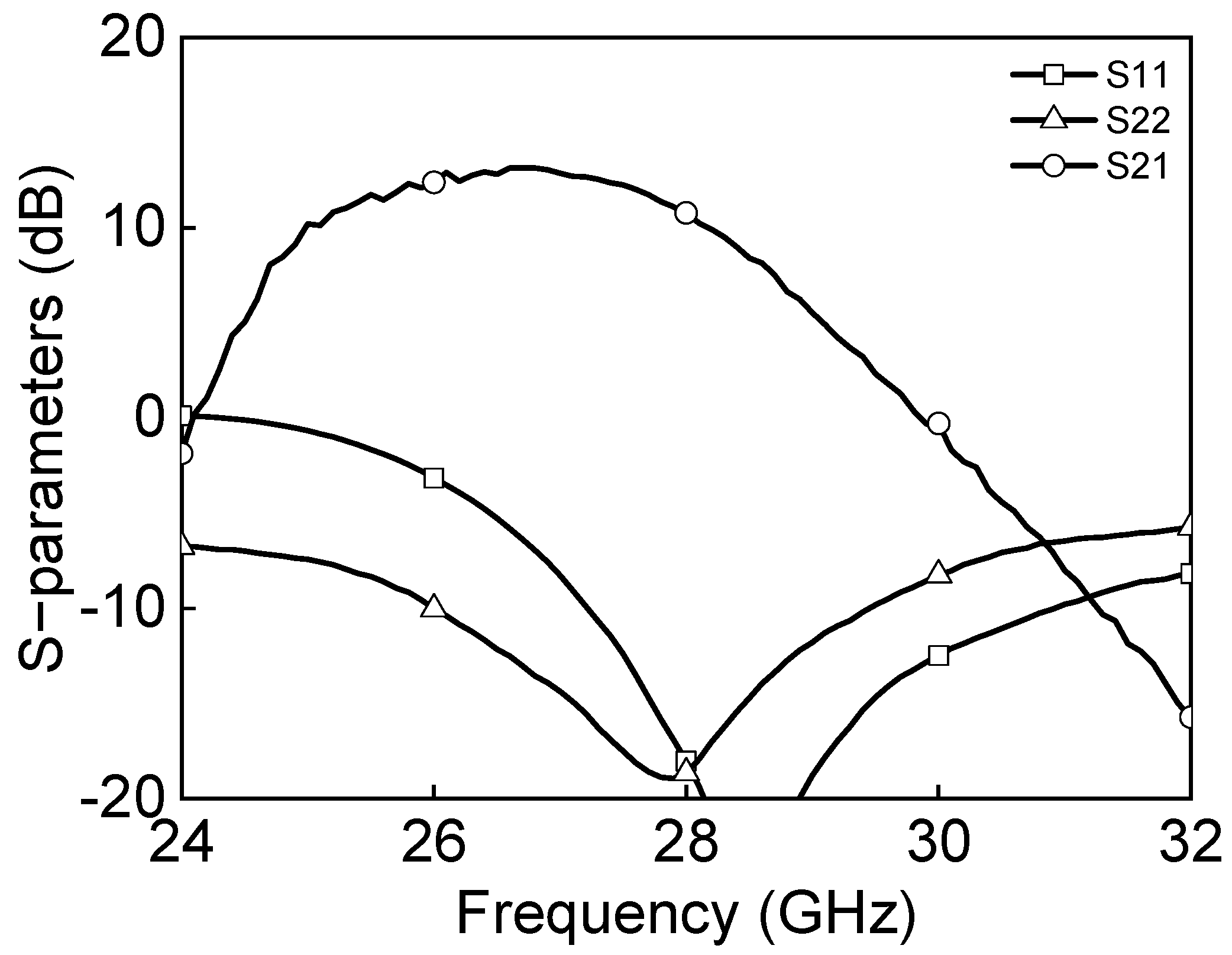

| Tx/Rx Gain (dB) | 11/9 | 18.6/14.8 | 9/11 | N/A |

| P1dB/PSAT (dBm) | −2.5/1.3 | 13.3/- | 15.7/18 | 9.5/10.5 |

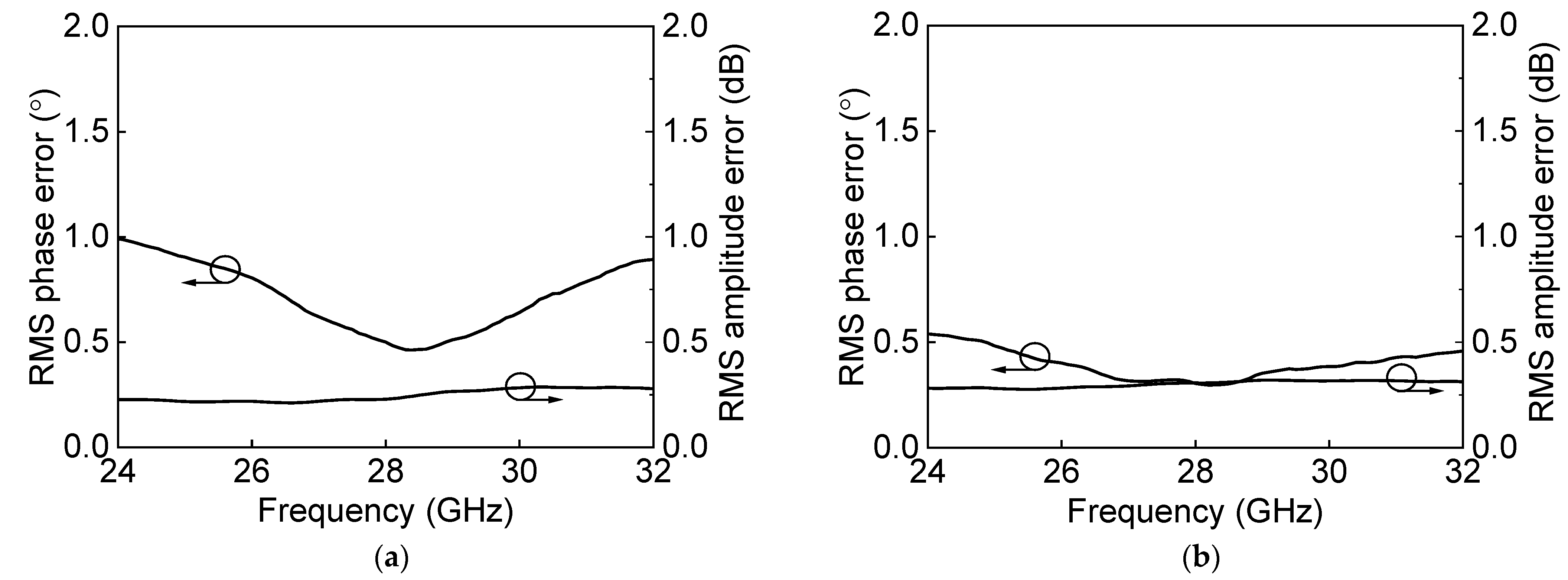

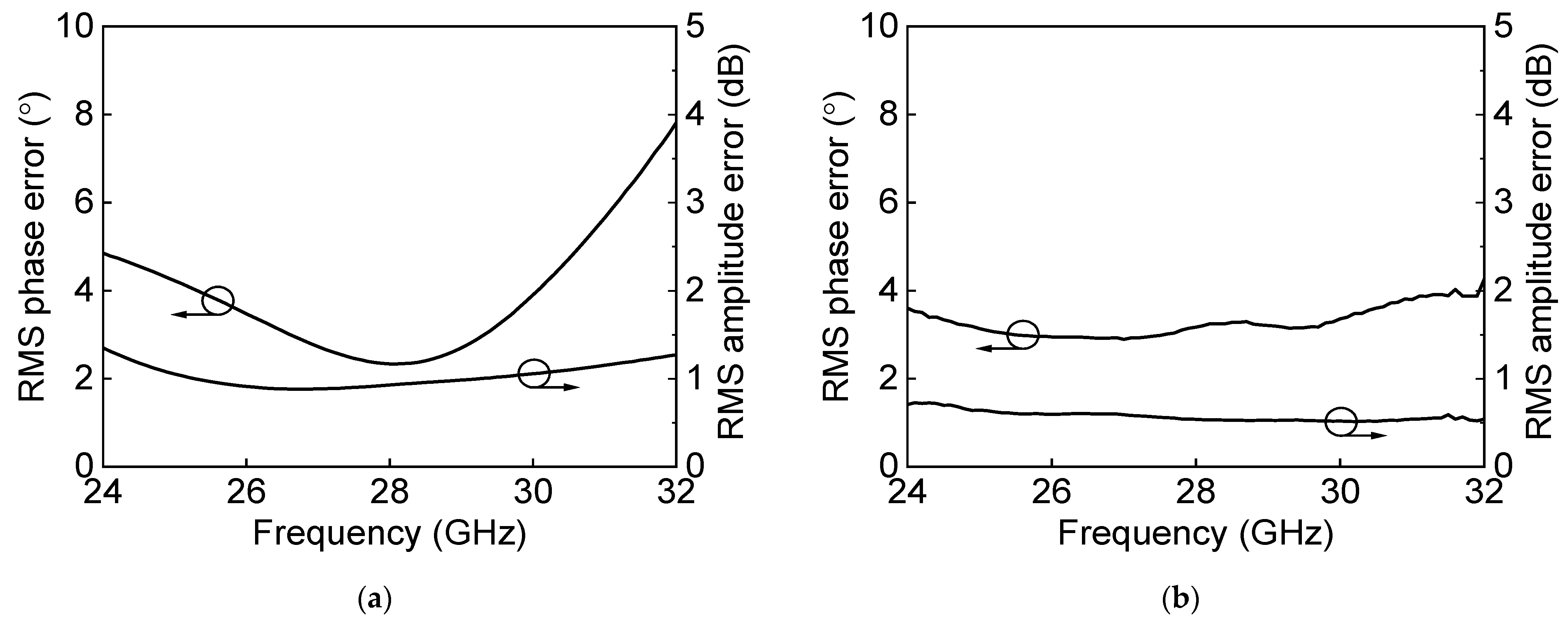

| Phase shift step (o) | 6 bit/5.6 | 6 bit/5.6 | 2 + 3 + 10 bit/0.3 ** | 3 bit/45 |

| RMS amplitude error (dB) | 0.6 | 0.21 | 0.04 | 1 |

| RMS phase error (o) | 3.2 | 1.4 | 0.3 | 7 |

| Tx/Rx PDC of 1channel (mW) | 181/181 | 73/- | 299/148 | 85/50 * |

| Mode | 8Tx only 8Rx only 8Tx8Rx TDD 4Tx4Rx- independent | 4Tx only 4Rx only 4Tx4Rx- independent | 4Tx only 4Rx only 4Tx4Rx- independent | 8Tx only 8Rx only 8Tx8Rx TDD |

| Chip Size (mm2) | 10.5 | 0.92 *** | 12 | 7.3 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Bhatta, A.; Park, J.; Baek, D.; Kim, J.-G. A Multimode 28 GHz CMOS Fully Differential Beamforming IC for Phased Array Transceivers. Sensors 2023, 23, 6124. https://doi.org/10.3390/s23136124

Bhatta A, Park J, Baek D, Kim J-G. A Multimode 28 GHz CMOS Fully Differential Beamforming IC for Phased Array Transceivers. Sensors. 2023; 23(13):6124. https://doi.org/10.3390/s23136124

Chicago/Turabian StyleBhatta, Ayush, Jeongsoo Park, Donghyun Baek, and Jeong-Geun Kim. 2023. "A Multimode 28 GHz CMOS Fully Differential Beamforming IC for Phased Array Transceivers" Sensors 23, no. 13: 6124. https://doi.org/10.3390/s23136124

APA StyleBhatta, A., Park, J., Baek, D., & Kim, J.-G. (2023). A Multimode 28 GHz CMOS Fully Differential Beamforming IC for Phased Array Transceivers. Sensors, 23(13), 6124. https://doi.org/10.3390/s23136124