92.5% Average Power Efficiency Fully Integrated Floating Buck Quasi-Resonant LED Drivers Using GaN FETs

Abstract

1. Introduction

2. Materials and Methods

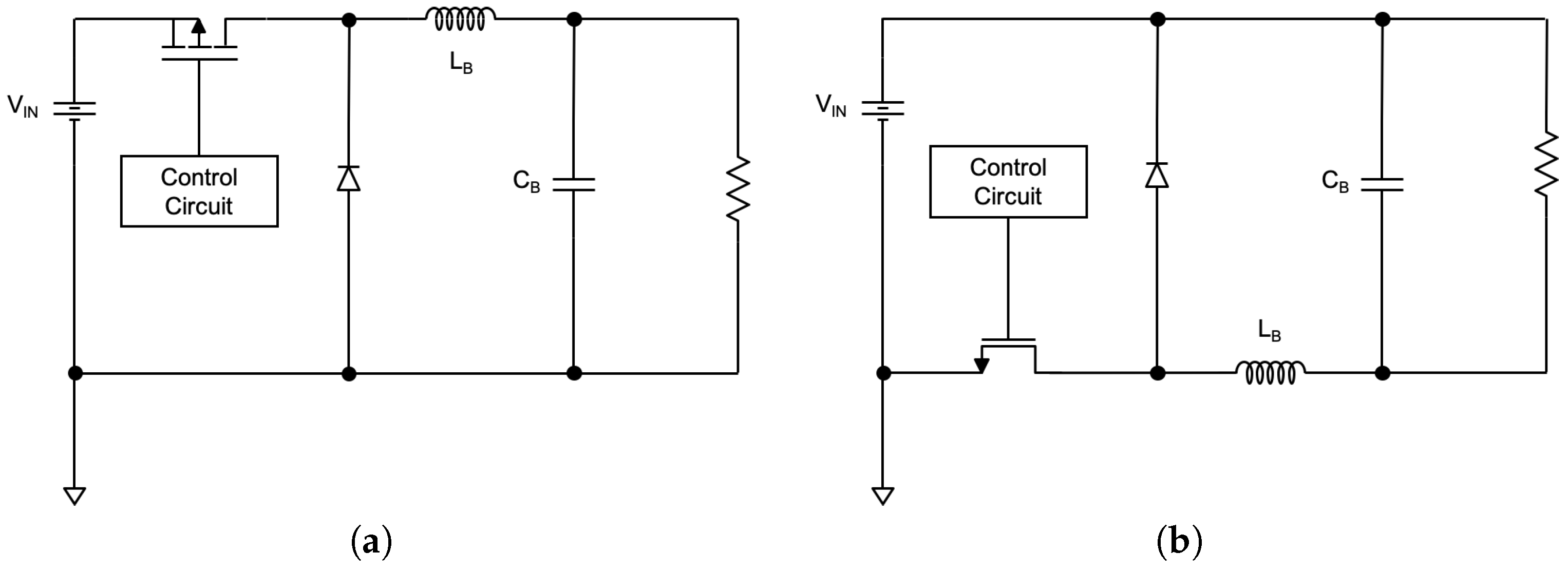

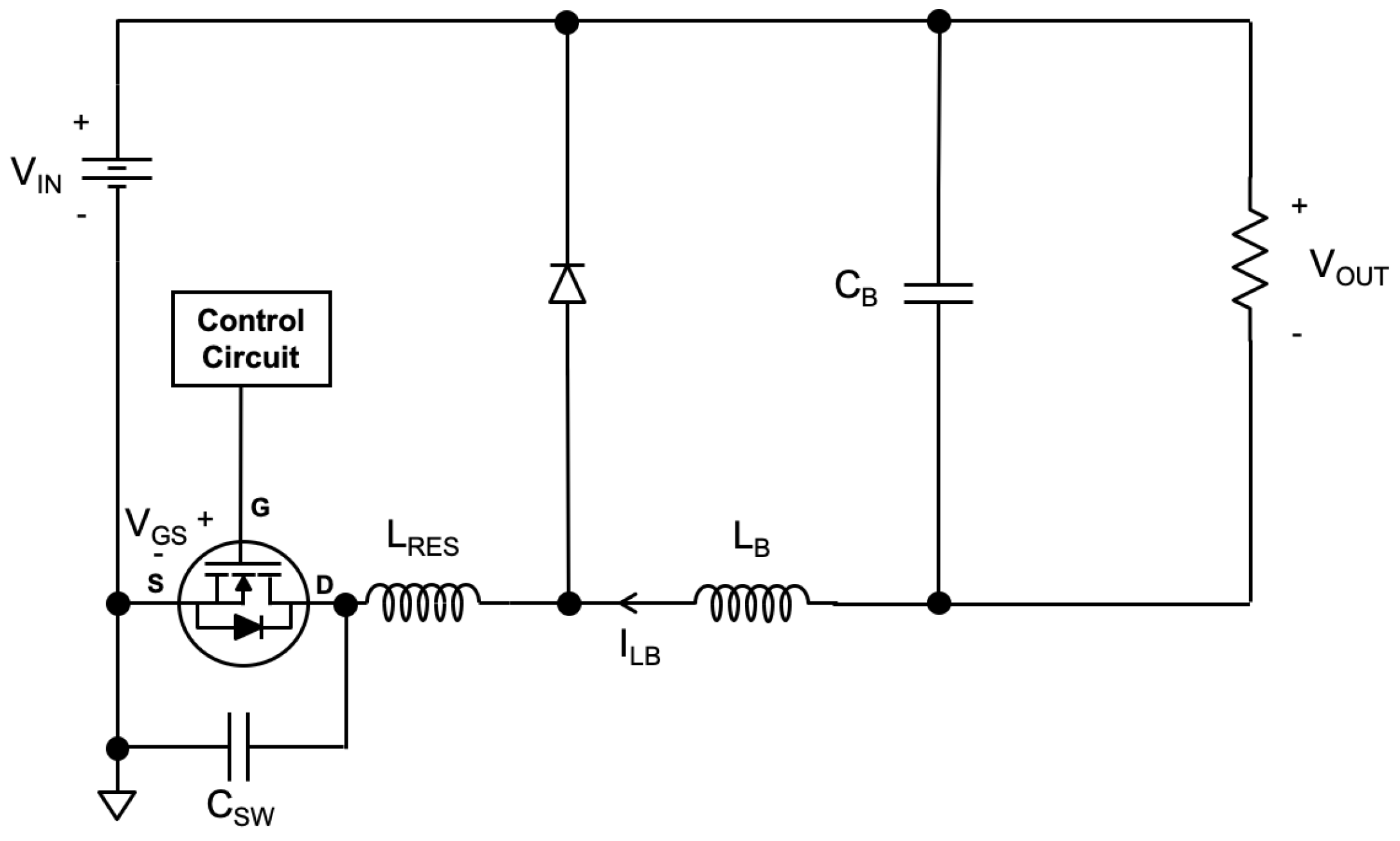

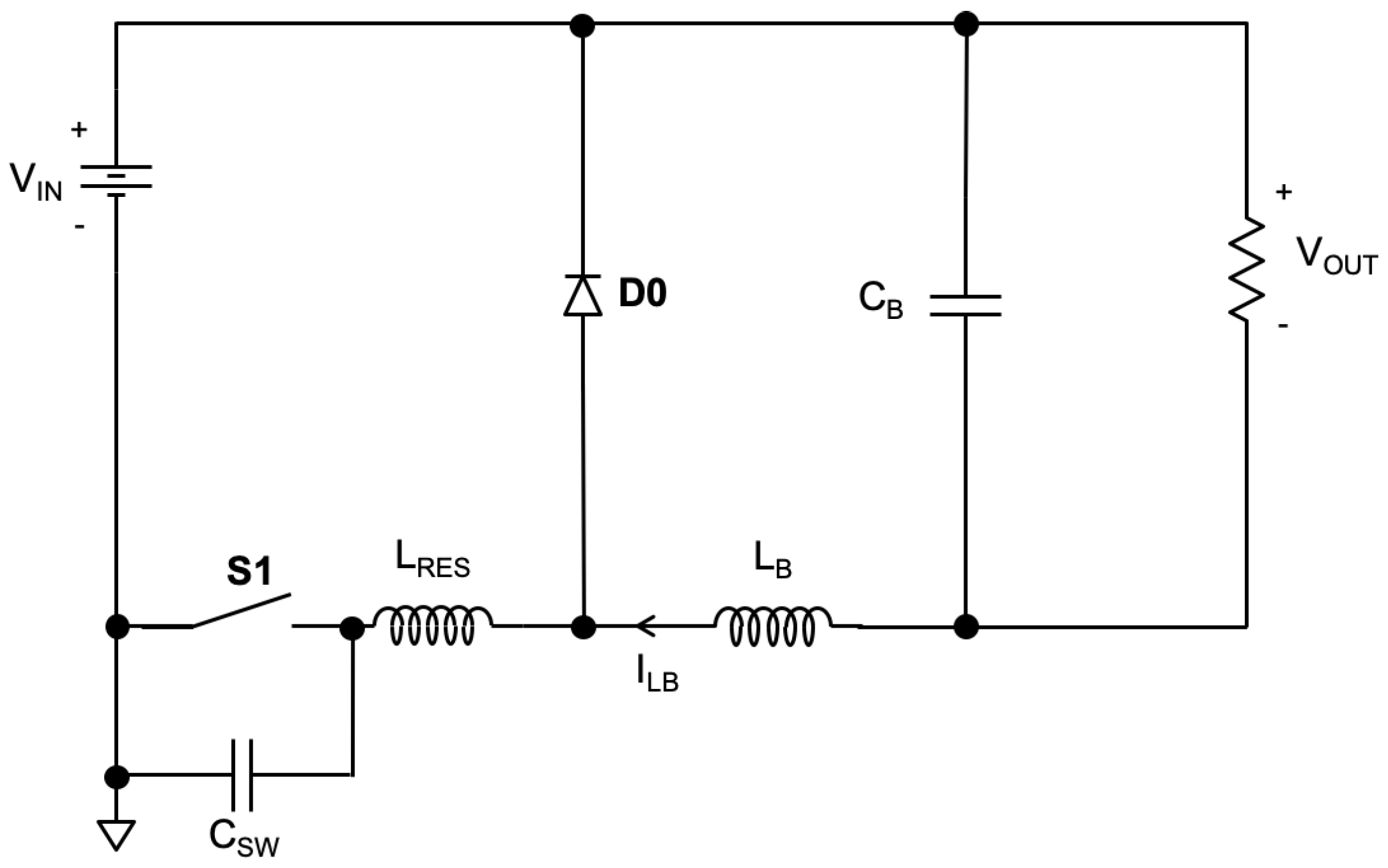

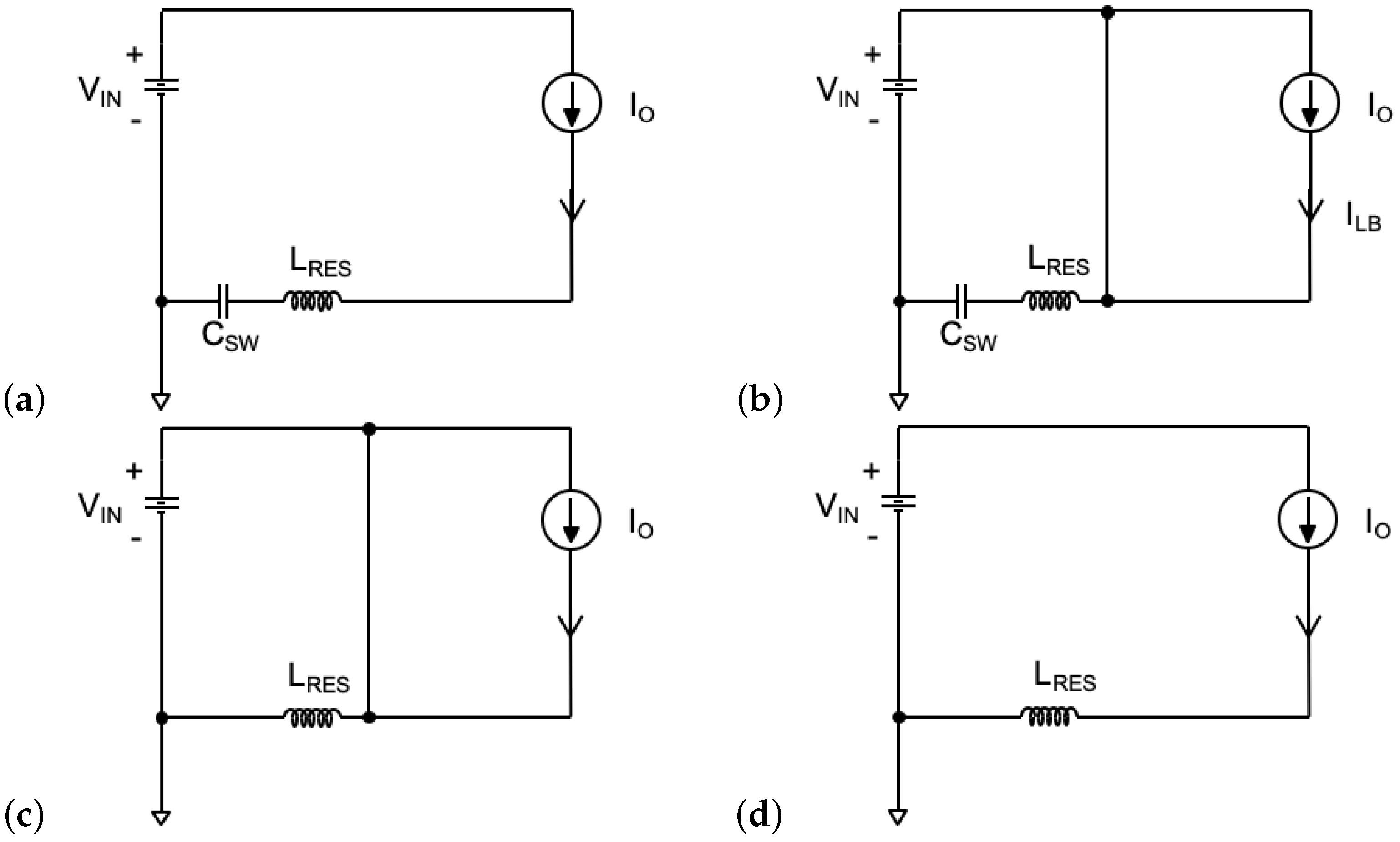

2.1. Quasi Resonant Floating Buck Converter Design

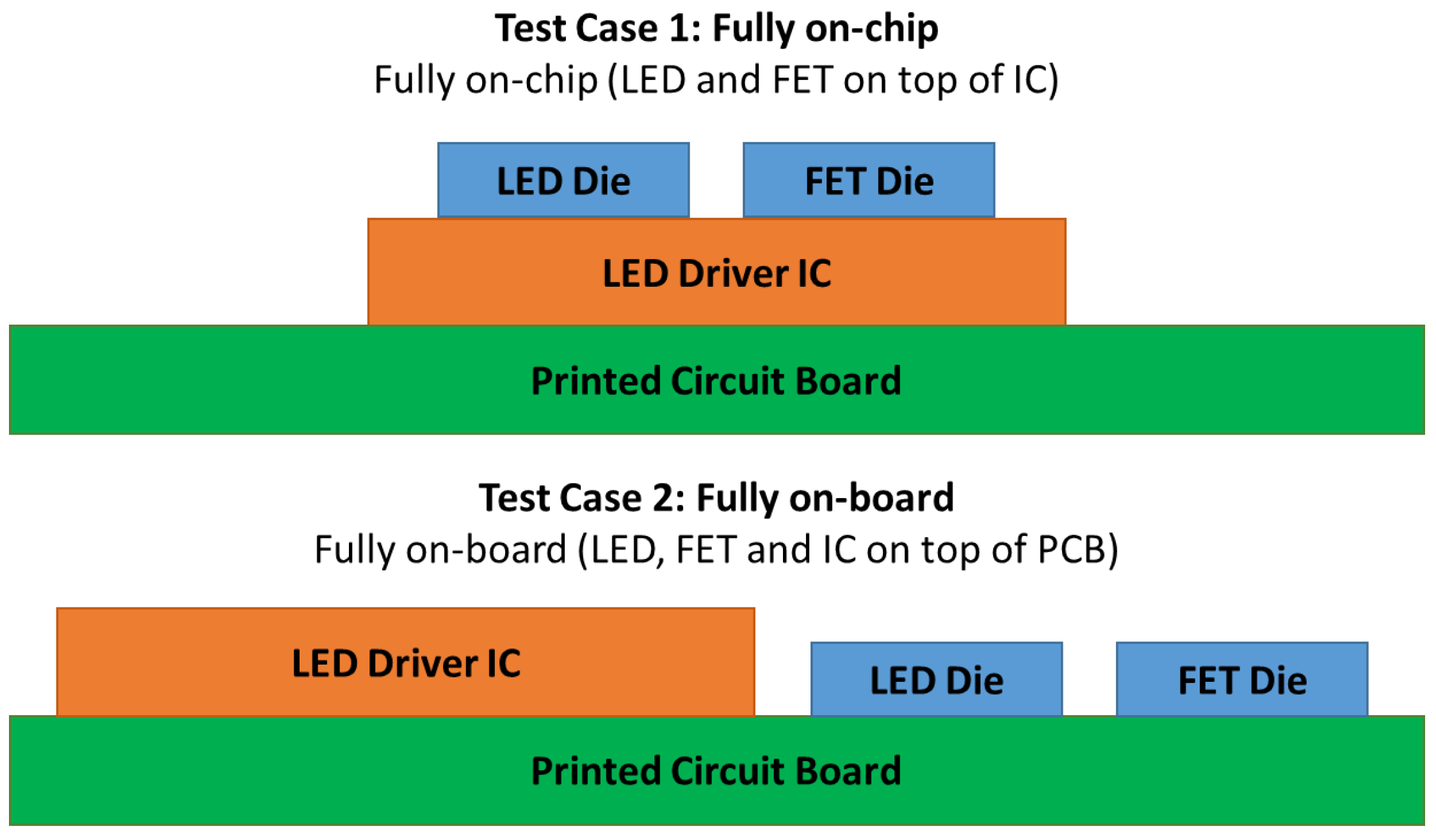

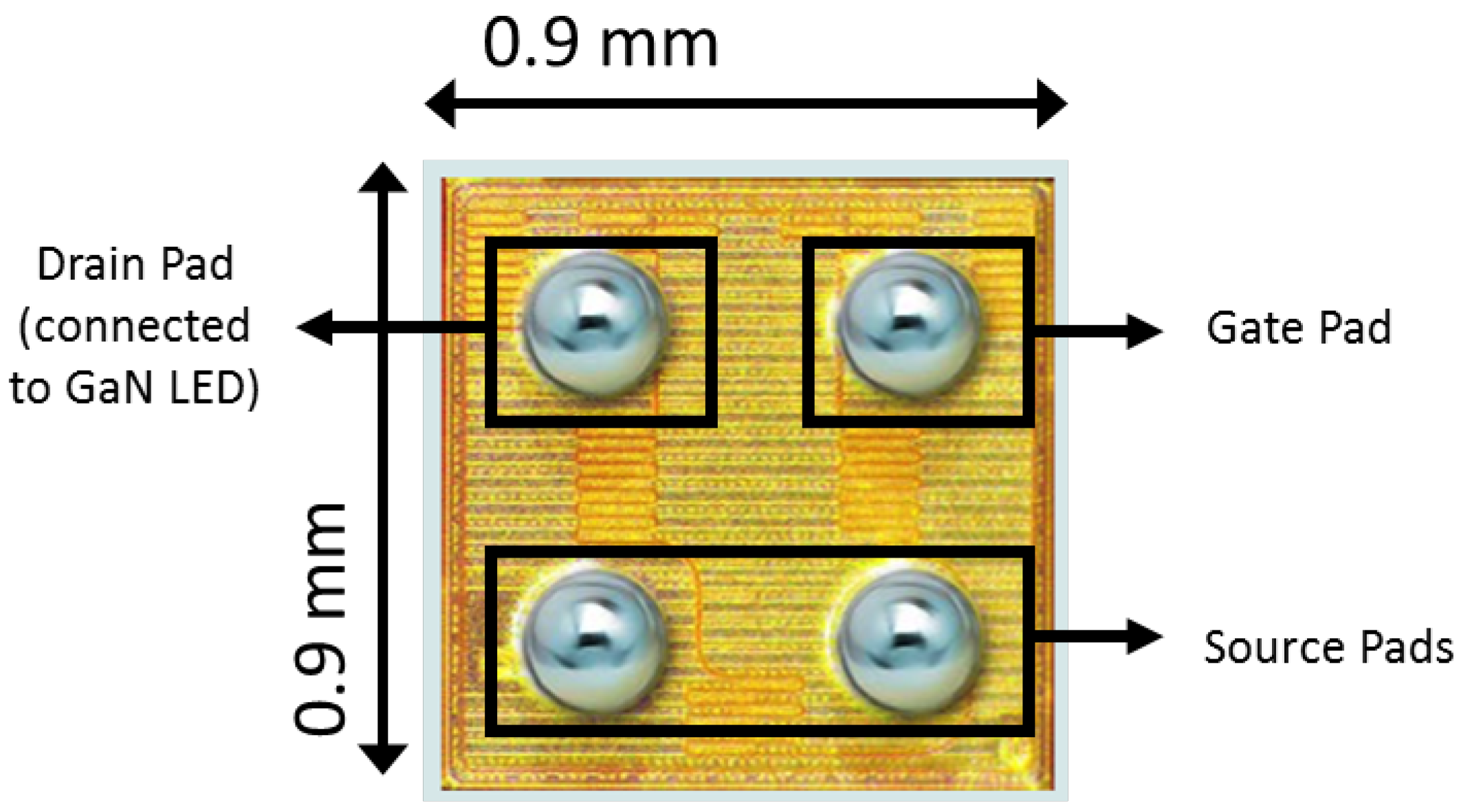

2.2. Assembly of GaN FETs

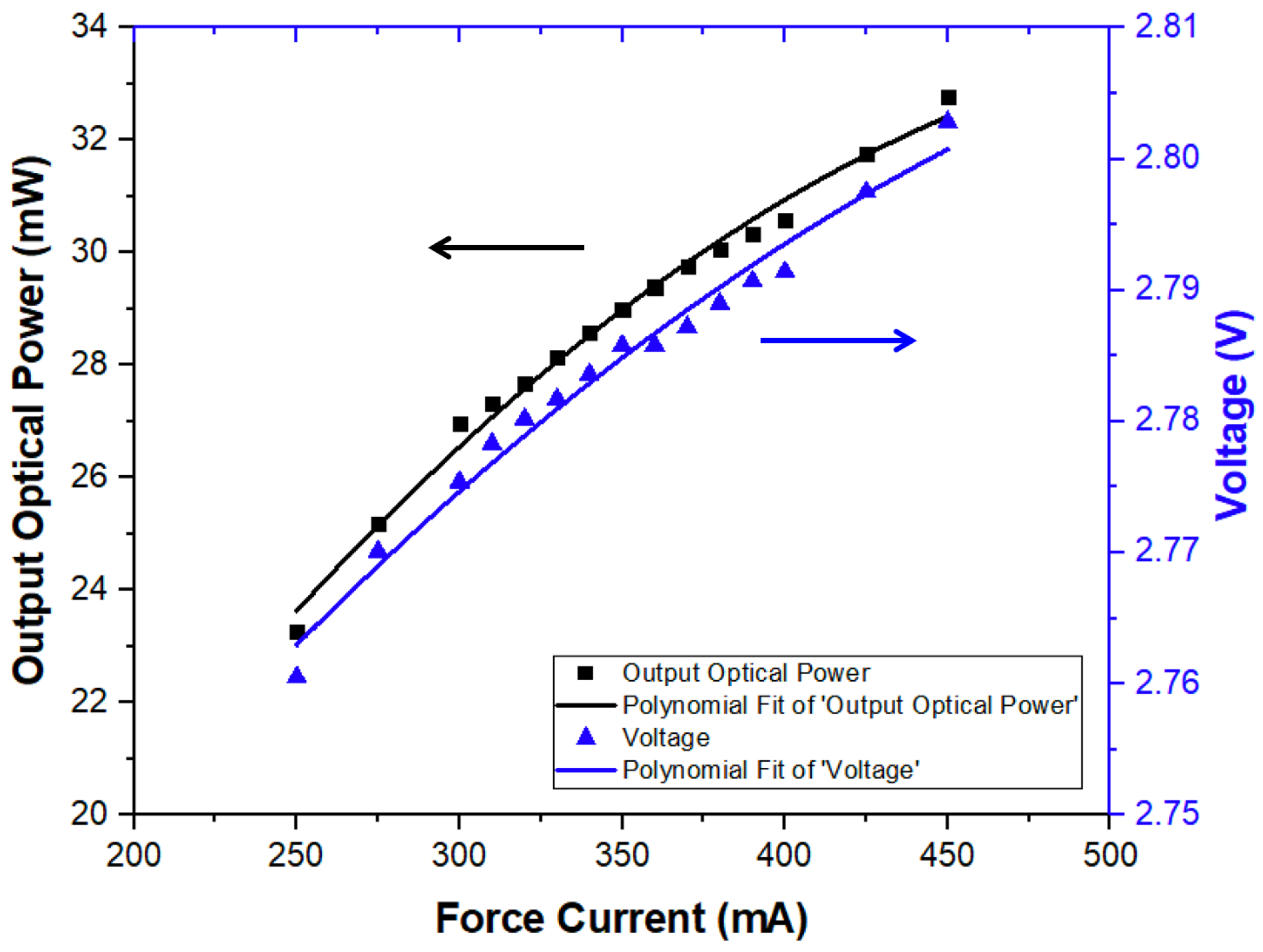

2.3. Fabrication and Assembly of Custom GaN LED

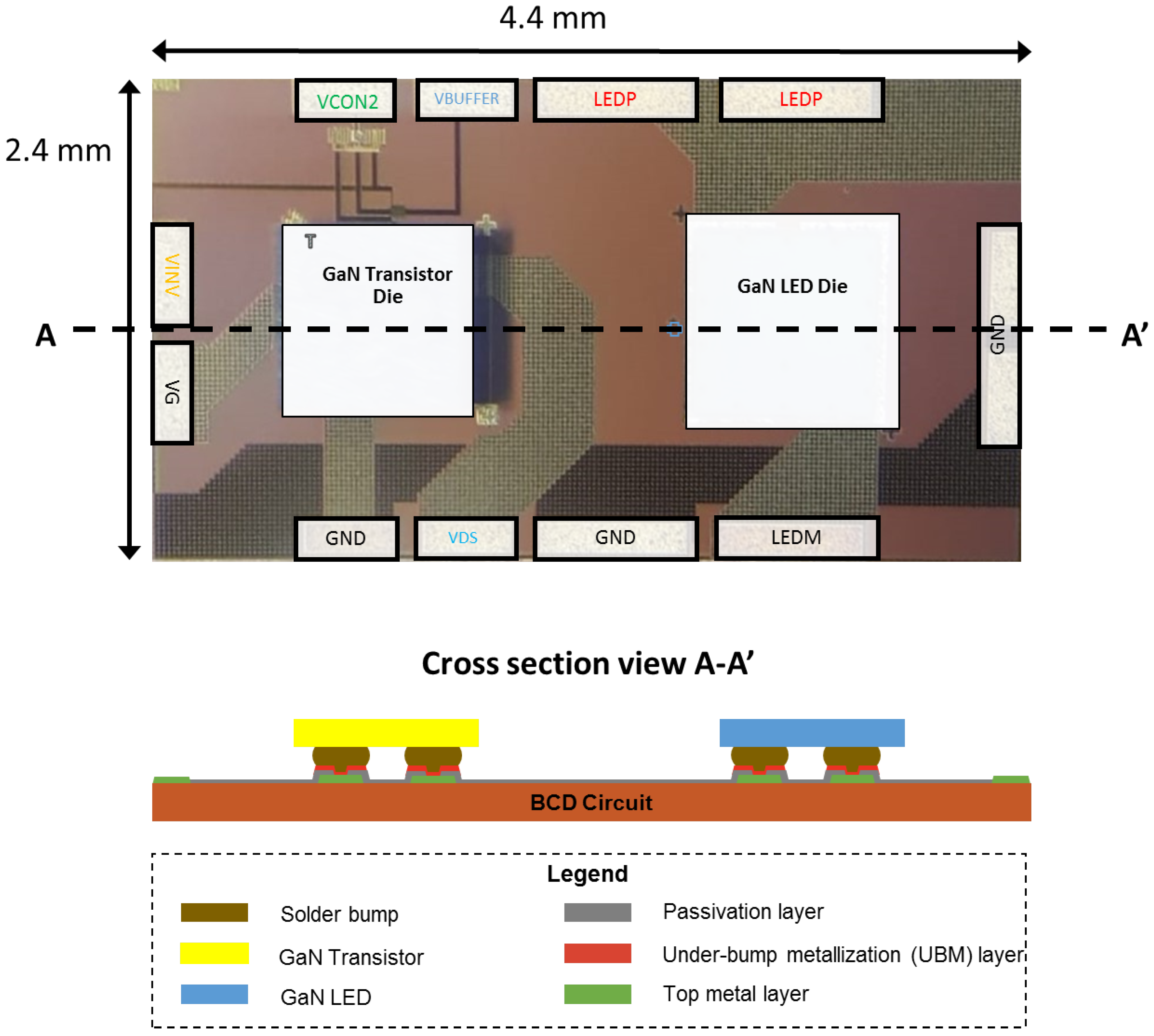

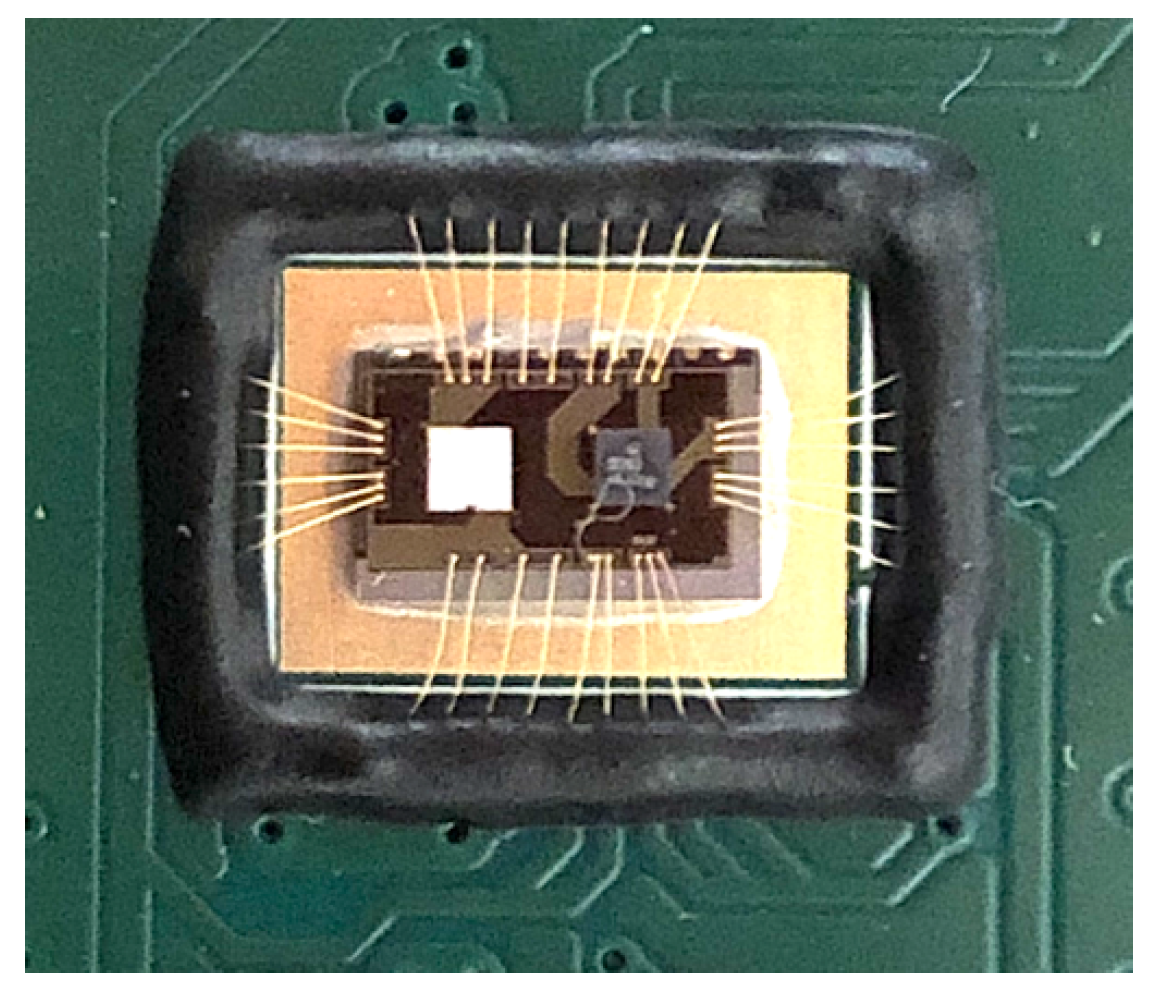

2.4. Fabrication of LED Driver IC

3. Measured Results and Discussions

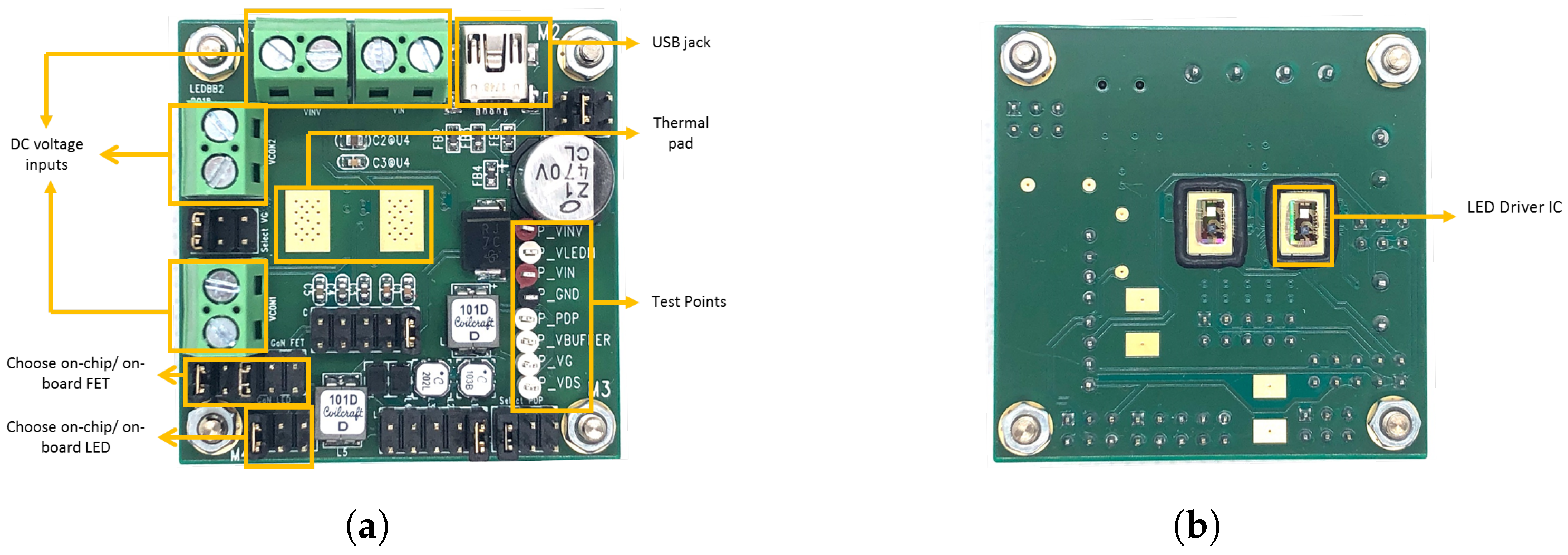

3.1. PCB Design

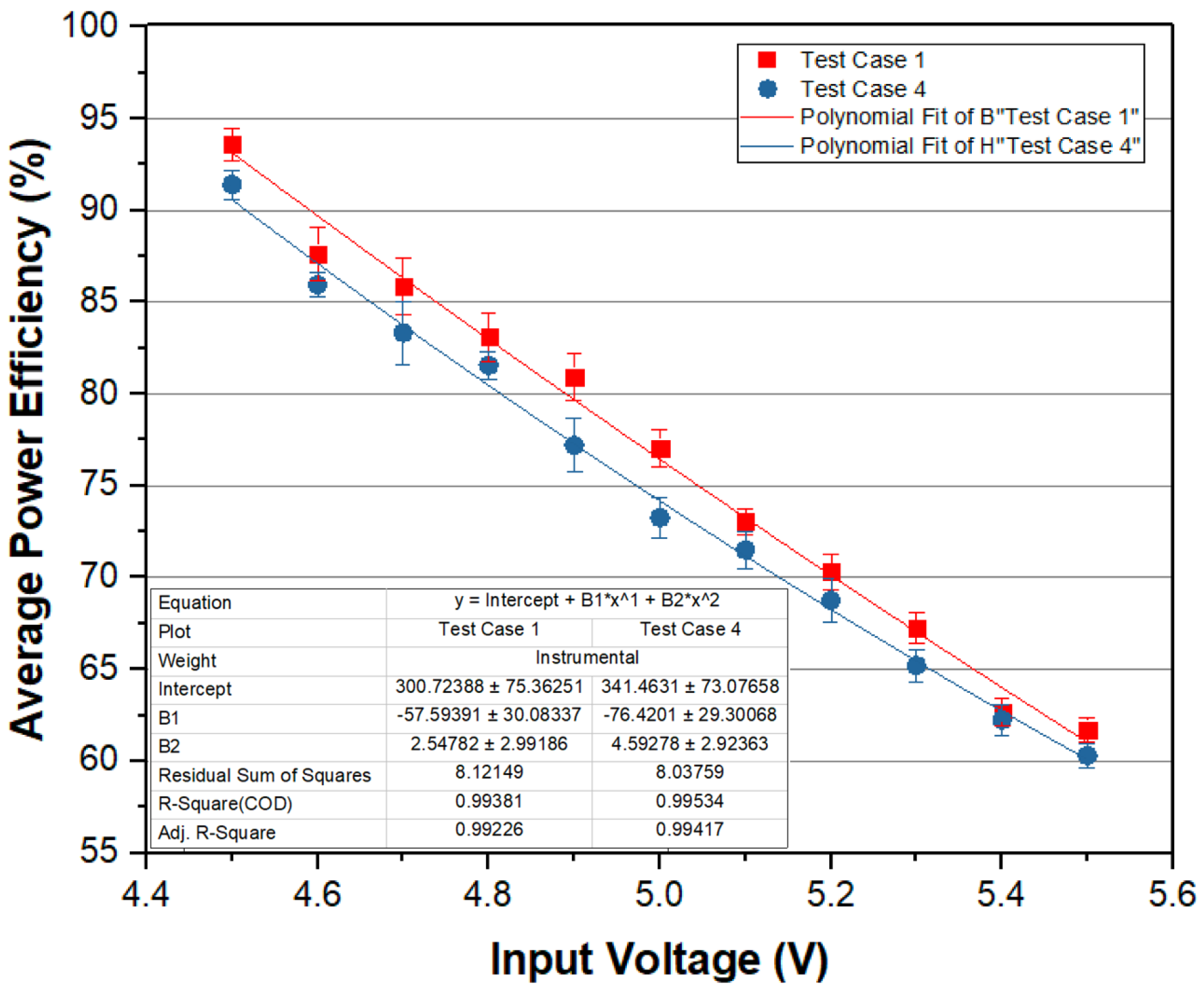

3.2. Functionality

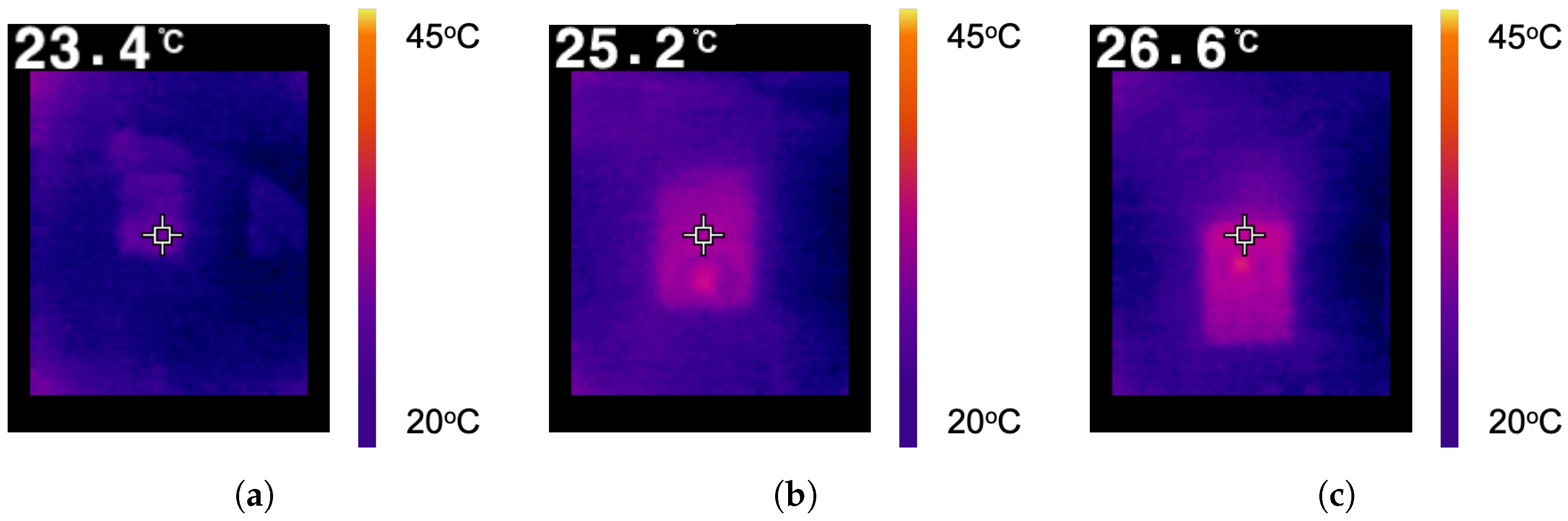

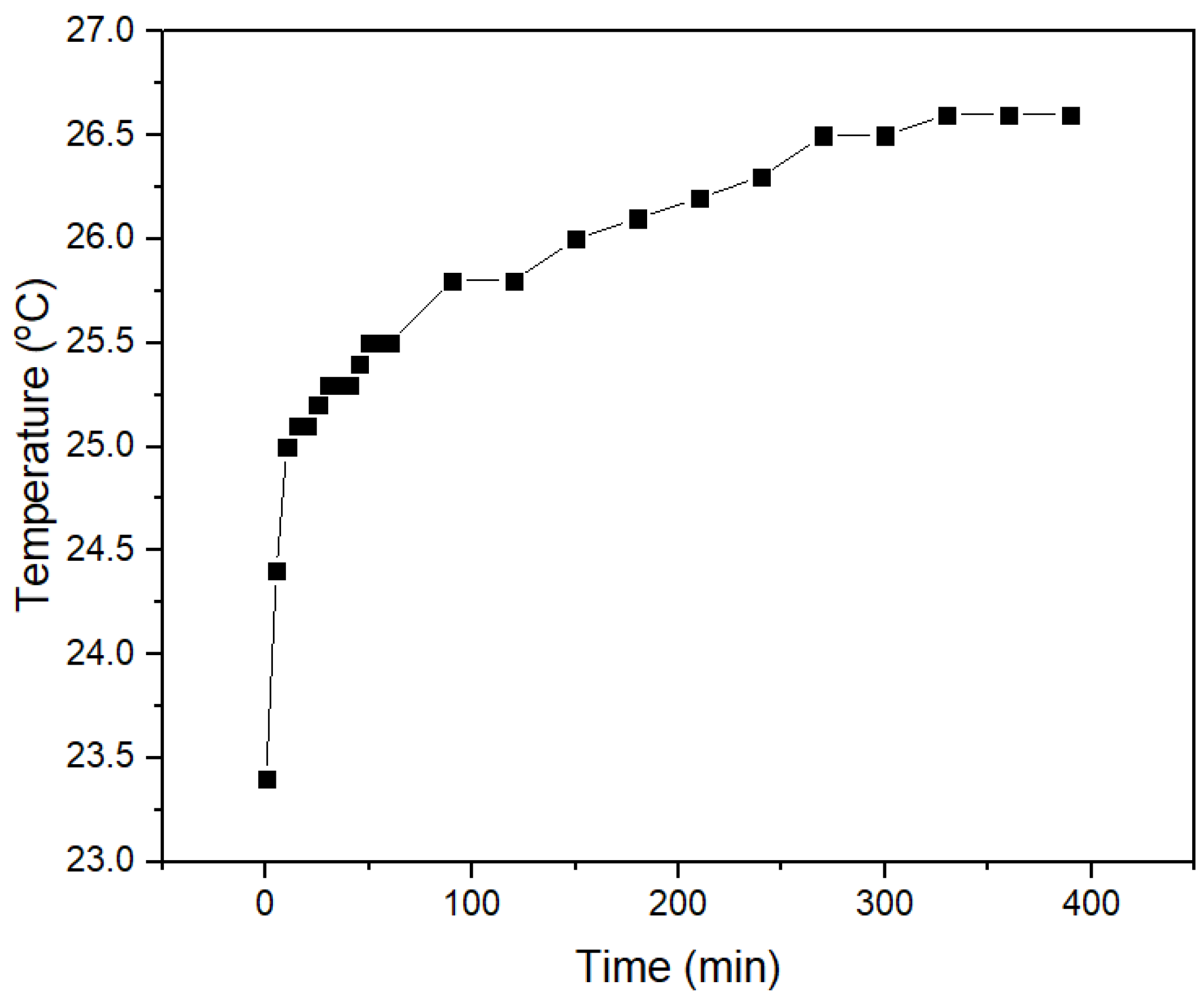

3.3. Thermal Testing

4. Conclusions

Author Contributions

Acknowledgments

Conflicts of Interest

Abbreviations

| BCD | Bipolar CMOS DMOS |

| CMOS | Complementary-Metal-Oxide-Semiconductor |

| DMOS | Double-Diffused Metal-Oxide Semiconductor. |

| FET | Field Effect Transistor |

| FC | Flip-Chip |

| EDB | Economic Development Board |

| IC | Integrated Circuits |

| IR | Infrared |

| KCL | Kirchhoff’s Current Law |

| KVL | Kirchhoff’s Voltage Law |

| LED | Light-Emitting Diode |

| MCPCB | Metal-Core Printed Circuit Board |

| MDPI | Multidisciplinary Digital Publishing Institute |

| NTU | Nanyang Technological University |

| PCB | Printed Circuit Board |

| QRC | Quasi Resonant Converter |

| SUTD | Singapore University of Technology and Design |

| UBM | Under-Bump Metallization |

| ZVS | Zero Voltage Switching |

References

- Craford, M.G. An overview of visible light emitting diode (LED) development and the potential for AlInGaP devices. IEEE Trans. Electron Devices 1993, 40, 2098. [Google Scholar] [CrossRef]

- Qu, X.; Wang, H.; Zhan, X.; Blaabjerg, F.; Chung, H.S. A Lifetime Prediction Method for LEDs Considering Real Mission Profiles. IEEE Trans. Power Electron. 2017, 32, 8718–8727. [Google Scholar] [CrossRef]

- Soh, M.Y.; Ng, W.X.; Zou, Q.; Lee, D.; Teo, T.H.; Yeo, K.S. Real-Time Audio Transmission Using Visible Light Communication. In Proceedings of the 2018 IEEE Region 10 Conference, Jeju, Korea, 28–31 October 2018; pp. 2223–2226. [Google Scholar] [CrossRef]

- Li, L.; Gao, Y.; Jiang, H.; Mok, P.K.; Lau, K.M. An Auto-Zero-Voltage-Switching Quasi-Resonant LED Driver With GaN FETs and Fully Integrated LED Shunt Protectors. IEEE J. Solid-State Circuits 2018, 53, 913–923. [Google Scholar] [CrossRef]

- Bandyopadhyay, S.; Neidorff, B.; Freeman, D.; Chandrakasan, A.P. 90.6% Efficient 11 MHz 22 W LED driver Using GaN FETs And Burst-Mode Controller With 0.96 Power Factor. In Proceedings of the 2013 IEEE International Solid-State Circuits Conference Digest of Technical Papers, San Francisco, CA, USA, 17–21 February 2013; pp. 368–369. [Google Scholar] [CrossRef]

- Caring Circuit. PCB Prototyping Fabrication Price Table. Available online: http://www.caringcircuit.com/fab-pcb-price-qt-1.html (accessed on 12 December 2019).

- Meng, F.; Disney, D.; Liu, B.; Volkan, B.; Zhou, A.; Liang, Z.; Yi, X.; Selvaraj, L.; Peng, L.; Ma, K.; et al. Heterogeneous Integration of GaN and BCD Technologies and Its Applications to High Conversion-ratio DC-DC Boost Converter IC. IEEE Trans. Power Electron. 2019, 34, 1993–1996. [Google Scholar] [CrossRef]

- Soh, M.Y.; Teo, T.H.; Selvaraj, S.L.; Peng, L.; Disney, D.; Yeo, K.S. Design of fully integrated low-power low-voltage LED lighting with heterogeneous integration of GaN and BCD Technologies. MDPI Electron. 2019, 8, 351. [Google Scholar] [CrossRef]

- Soh, M.Y.; Ng, W.X.; Teo, T.H.; Selvaraj, S.L.; Peng, L.; Disney, D.; Zou, Q.; Yeo, K.S. Design and Characterization of Micro-LED Matrix Display With Heterogeneous Integration of GaN and BCD Technologies. IEEE Trans. Electron Devices 2019, 66, 4221–4227. [Google Scholar] [CrossRef]

- Liu, M.; Hsu, S.S.H. A Miniature 300-MHz Resonant DC–DC Converter With GaN and CMOS Integrated in IPD Technology. IEEE Trans. Power Electron. 2018, 33, 9656–9668. [Google Scholar] [CrossRef]

- Selvaraj, S.L.; Peng, L.; Qiong, Z.; Seng, Y.K.; Disney, D. Heterogeneous Integration of GaN LED on CMOS Driver Circuit for Mobile Phone Applications. In Proceedings of the 2018 IEEE 2nd Electron Devices Technology and Manufacturing Conference (EDTM), Kobe, Japan, 13–16 March 2018; pp. 71–73. [Google Scholar] [CrossRef]

- Mojab, A.; Hemmat, Z.; Riazmontazer, H.; Rahnamaee, A. Introducing Optical Cascode GaN HEMT. IEEE Trans. Electron Devices 2017, 64, 796–804. [Google Scholar] [CrossRef]

- Hahn, H.; Funck, C.; Geipel, S.; Kalisch, H.; Vescan, A. The III-Nitride Double Heterostructure Revisited: Benefits for Threshold Voltage Engineering of MIS Devices. IEEE Trans. Electron Devices 2016, 63, 606–613. [Google Scholar] [CrossRef]

- Tabisz, W.A.; Lee, F.C. Zero-Voltage-Switching Multiresonant Technique-A Novel Approach To Improve Performance Of High-Frequency Quasi-Resonant Converters. IEEE Trans. Power Electron. 1989, 4, 450–458. [Google Scholar] [CrossRef]

- Rashid, M.H. Power Electronics Handbook: Devices, Circuits and Applications; Elsevier: Amsterdam, The Netherlands, 2010. [Google Scholar]

- Mack, R.A. Demystifying Switching Power Supplies; Elsevier: Amsterdam, The Netherlands, 2011. [Google Scholar]

- Mohan, N.; Undeland, T.M.; Robbins, W.P. Power Electronics: Converters, Applications, and Design; John Wiley & Sons: Hoboken, NJ, USA, 2003. [Google Scholar]

- Hinov, N.L.; Rangelov, N.R. Buck ZVS DC-DC Quasi-Resonant Converter: Design, Modeling, Simulation and Experimentation. Annu. J. Electron. 2015, 9, 232–237. [Google Scholar]

- Corporation, E.P.C. EPC2036—Enhancement Mode Power Transistor; PC Corporation: El Segundo, CA, USA, 2018. [Google Scholar]

- Jang, S.Y.; Wolf, J.; Ehrmann, O.; Gloor, H.; Schreiber, T.; Reichl, H.; Paik, K.W. CrCu based UBM (under bump metallization) study with electroplated Pb/63Sn solder bumps-interfacial reaction and bump shear strength. IEEE Trans. Compon. Packag. Technol. 2003, 26, 245–254. [Google Scholar] [CrossRef]

- Chan, K.; Zhong, Z.; Ong, K. Study of under bump metallisation barrier layer for lead-free solder. Solder. Surf. Mt. Technol. 2003, 15, 46–52. [Google Scholar] [CrossRef]

- FLIR. FLIR TG165 Imaging IR Thermometer; FLIR: Wilsonville, OR, USA, January 2017. [Google Scholar]

- International Electrotechnical Commission. Information Technology Equipment-Safety—Part 1: General Requirements [IEC 60950–1-Ed. 1]; International Electrotechnical Commission: Geneva, Switzerland, 2001. [Google Scholar]

| Circuit Parameter | Value |

|---|---|

| 5 V | |

| 2.5 V | |

| 2 uH | |

| 10 uF | |

| 100 nH | |

| 90 pF | |

| , switching frequency | 11 MHz |

| , resonant frequency | 21.8 MHz |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Soh, M.Y.; Selvaraj, S.L.; Peng, L.; Yeo, K.S. 92.5% Average Power Efficiency Fully Integrated Floating Buck Quasi-Resonant LED Drivers Using GaN FETs. Electronics 2020, 9, 575. https://doi.org/10.3390/electronics9040575

Soh MY, Selvaraj SL, Peng L, Yeo KS. 92.5% Average Power Efficiency Fully Integrated Floating Buck Quasi-Resonant LED Drivers Using GaN FETs. Electronics. 2020; 9(4):575. https://doi.org/10.3390/electronics9040575

Chicago/Turabian StyleSoh, Mei Yu, S. Lawrence Selvaraj, Lulu Peng, and Kiat Seng Yeo. 2020. "92.5% Average Power Efficiency Fully Integrated Floating Buck Quasi-Resonant LED Drivers Using GaN FETs" Electronics 9, no. 4: 575. https://doi.org/10.3390/electronics9040575

APA StyleSoh, M. Y., Selvaraj, S. L., Peng, L., & Yeo, K. S. (2020). 92.5% Average Power Efficiency Fully Integrated Floating Buck Quasi-Resonant LED Drivers Using GaN FETs. Electronics, 9(4), 575. https://doi.org/10.3390/electronics9040575