Abstract

Process Variation (PV), Bias Temperature Instability (BTI) and Time-Dependent Dielectric Breakdown (TDDB) are the critical factors that affect the reliability of semiconductor chip design. They cause the system to be unstable and increase the soft error rate. In this paper, a compact on-chip degradation technique using runtime leakage current monitoring has been proposed. The proposed sensor-based adaptive technique compensates for the variation due to PV and aging using the body-bias-voltage-generator circuit. Simulation experiments for three and ten-year stress have been performed. Simulation results proved the superiority of the proposed sensor which provides 33% (up to 0.75 V) more output voltage and 98% sensitivity at 1 V supply voltage compared to the state-of-the-art sensor. The proposed technique mitigates up to 80% PV and BTI effects in SRAM compared to the state-of-the-art techniques.

1. Introduction

Constant Voltage Scaling (CVS) is a method that enables device dimensions to decrease deeper into the nanometer scale while maintaining a constant supply voltage. Using this method increases the electric field across the gate oxide (between the channel and the gate oxide). It also causes the occurrence of degradation phenomena such as Negative Bias Temperature Instability (NBTI), Positive Bias Temperature Instability (PBTI), Time-Dependent Dielectric Breakdown (TDDB) and Hot Carrier Injection (HCI) [1,2]. These degradation mechanisms make it too hard to meet the circuit lifetime specification using deep nanometer scaled dimensions. Additionally, the NBTI and PBTI are the critical factors causing degradation bellow 2 nm oxide thickness [2]. Since FinFET devices are not doped, the current density is very high at the channel-gate-oxide interface which causes acceleration of the charge carrier to interface into the gate oxide from the channel and it further increases with the stress [3]. Junctionless-FinFET also has a potential to replace the conventional MOSFET but it also has a problem of BTI and process variation [4]. Hence, it is a primary need to design a robust SRAM memory.

The robustness of the semiconductor memory can be dramatically impacted by the aforementioned degradation mechanisms. SRAM is an on-chip semiconductor memory which can be used as a cache memory along with the multi-core processors. It bridges the speed gap between the logic and the main memory. A microprocessor is a power-hungry unit which transforms the dissipated power into heat which further increases the effect of NBTI that is directly proportional to temperature. BTI becomes crucial due to the thermal runaway. The soft error rate increases in SRAM due to BTI. This error can be reduced by increasing the gate length. Hence, reliability can be improved for high temperature operation [5]. There has been some research done on NBTI resilient SRAM circuit design. In the past, there was no much interest in using on-chip NBTI mitigation techniques since they require large on-chip area and total power budget. In the modern technology area in not a major issue and production yield is decreasing due to complex chip fabrication process. The on-chip mitigation techniques help to increase the yield and life ot the chip [6]. Singh et al have proposed an oscillator frequency based NBTI sensor which collects the data from the test on-chip PMOS transistor for the specific stress mode [7]. The data is supplied to the measurement mode which decides the recovery mode. The 20 Byte SRAM register was used for stress measurement. The stress circuit consisted of the analog comparator which used fourteen transistors, and the measurement circuit is designed by the NAND Gate based oscillator along with the level converter circuits. The main disadvantage of this sensor circuit is that it produces a nonlinear output with the linear change of the stress time. Furthermore, the output becomes unstable with temperature variations and area overhead.

Sai et al have proposed a multi-path aging sensor [8] which does not require placing a sensor in the longest path that might reduce the performance. This sensor works on the principle of differential multiple error detection which uses an analog differential circuit for stress detection. The main advantage of this sensor lies in its capability of detecting and mitigating the delay fault. Detection of the fault is performed in two or more paths at a time. However, the sensor is nonlinear and has a high area overhead [8]. An impressive NBTI sensor has been proposed for the SRAM register files by Yang et al [9]. This sensor can detect the change in the threshold voltage of the PMOS transistors. Further, the in-situ and in-field technique along with software framework have been used to create the recovery vectors using the measured degraded threshold voltage. However, high computational complexity and the requirement of an off-chip software are the drawbacks of these techniques. Shah et al also proposed an NBTI-based sensor to measure the current change for the SRAM [10]. Despite the compact nature of this sensor, its accuracy and linearity are inferior. In this paper, a new stress measurement sensor for 6T cell based SRAM has been proposed. The proposed sensor monitors the change in the leakage current and converts it into voltage which is then used by a measurement circuit to make a decision and perform the mitigation. Due to its very high input impedance due to diode connected transistors, the sensor is very sensitive towards the change in input leakage current. Two push-pull amplifiers are used with a tuning transistor to give a very high output swing. Sizing of an On-chip transistor can be used to tune the accuracy level of the proposed sensor.

The remainder of the proposed work is as follows. Section 2 discusses the effects of NBTI on the 6T SRAM cell, introduces a circuit-level solution, and explains the remaining research gaps. In Section 3, the proposed stress measurement sensor and simulation results are discussed. The mathematical model of the proposed sensor and analysis of the simulation results are also discussed in this section. The proposed architecture and compensation technique are discussed in Section 4. Section 5 compares the proposed sensor and SRAM architecture to the state-of-the=art sensors circuit. Finally, in Section 6, the conclusion is drawn along with future work.

2. Aging Effects on the SRAM

The NBTI and PBTI cause an increase in the threshold voltages of the PMOS and NMOS, respectively, under DC and AC stress following the power-law model. The simplified expression for the DC stress is given by [11] shown in Equation (1)

where n is the time constant with value for the molecular hydrogen diffusion, t is the aging time and depends on the technology and material parameters. It also contains the stress and recovery time constants which depend on the material, interfaces trap density, biasing and transistor dimensions. NMOS and PMOS transistors of the SRAM also experience AC stress whose effect is less than that of the DC stress. The AC stress is given by [12]:

where is the perfection parameter which depends on the operating AC frequency. It has already been testified that the lifetime of the circuit is four times greater when under AC stress than DC stress. The sufficient time of the transistor in a 6T SRAM cell depends on the clock frequency and the change of the input at the gate terminal. The NMOS and PMOS devices experience DC stress when they are in the ON state and perform recovery when they are in the OFF.

Two principal physical mechanisms were used to analyze the N/PBTI for SRAM: one is contributed by the interface traps and the other uses the deep traps inside the oxide layer. These are modeled as follows [13] for 45 nm and below technology nodes:

where is the inversion charge exponent for the interface-trap-inducing threshold voltage degradation, is the oxide electric field dependence for the interface trap inducing threshold voltage degradation, is the stress time exponent, E is the electric field. A device is known to be at partial-recovery when it is relaxed in which case it reduces the total degradation. This is modeled as follows:

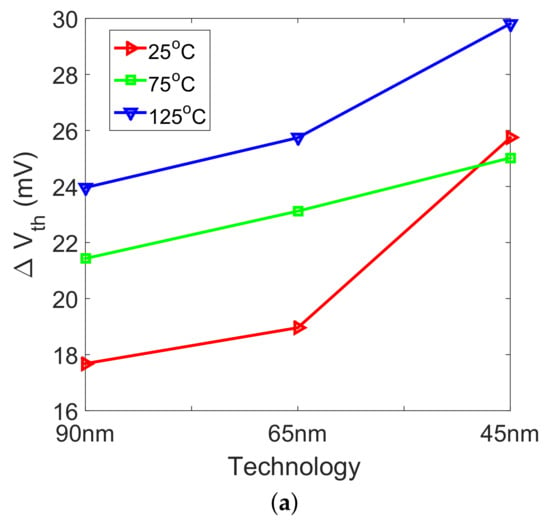

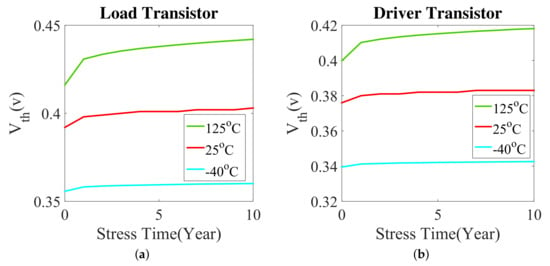

where is the channel current exponent for the threshold voltage degradation caused by HCI and the g quantity model which depends on the duty cycle of the clock. The HCI effect was modeled to represent the dependence of bias on a wide range of drain-gate voltage [13]. The change in the threshold voltage for the PMOS transistor with respect to various nanometer technologies is shown in Figure 1a. The simulation result shows the quick response in initial stress; then it slows down; hence, in the early age of the chip recovery is required. Figure 1b shows experimental data collected from various published works which also show the quick variation in the initial stage of the chip lifetime as the temperature increases [14].

Figure 1.

(a) Threshold voltage variation of PMOS transistor at at stress time of 105s [15,16] (b) Change

in life time with the temperature [14].

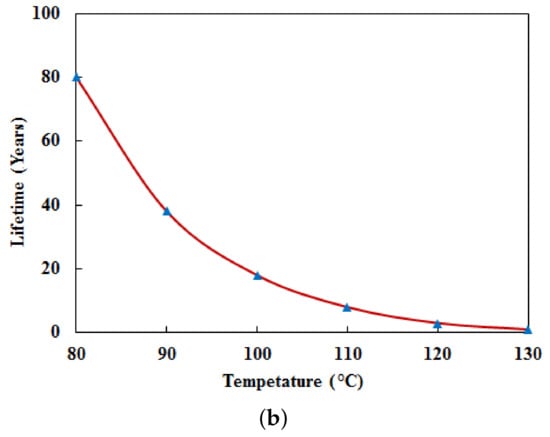

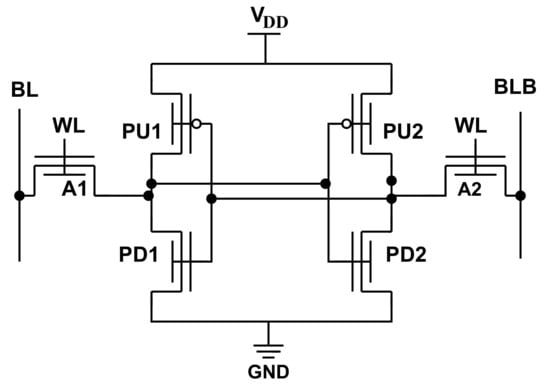

Figure 2 shows the basic 6T SRAM cell circuit diagram [17]. PU1 and PU2 are the pull-up transistors, A1 and A2 are the access transistors, PD1 and PD2 are the driver transistors. In the proposed design, a body biasing circuit is used to compensate for the process variation and aging effects. The body terminals of the NMOS and PMOS transistors are separated using the dual-well technology based layouts which are shown in Figure 3. According to Equation (3), the threshold voltage of the pull-up PMOS transistors increases due to NBTI degradation with aging time. The sub-threshold leakage current decreases exponentially as the threshold voltage of PMOS transistors increases with aging time. Accordingly, the total leakage power of SRAM cell decreases with aging time, as shown in Figure 1 for 45 nm technology. However, the increasing value of the threshold voltage of the PMOS transistors in SRAM cell affects the performance and stability. BTI decreases the read SNM, holds SNM, writes margin, word line write margin (WLWM). BTI increases the circuit delay, read and access time failure probability. The read and hold SNM degrades over the aging time under the stressed conditions because of the reduction of the trip-point voltage of the left inverter. The write margin of the SRAM cell gets improved with stress time since the node storing logic “1” (Q) becomes weak and therefore writing becomes easier [18,19].

Figure 2.

6T SRAM cell.

Figure 3.

6T SRAM cell layout with separate body terminals.

3. Proposed Stress Measurement Sensor

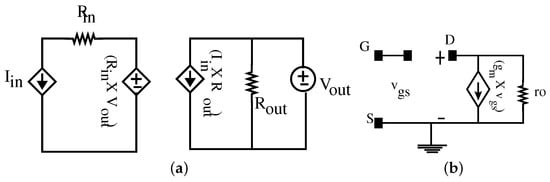

The proposed sensor design is somewhat similar to the design of an analog amplifier. A current to voltage converter based on-chip PV and NBTI sensor circuit has been proposed to compensate for the damages due to PV, BTI (NBTI and PBTI). Figure 4a shows the two-port network of the current to voltage amplifier where is the input impedance, is the input current source, is the dependent voltage sour is the voltage-dependent current source, is the output impedance, and is the output voltage. The small-signal equivalent circuit of the MOSFET is shown in Figure 4b. This circuit also works like a current to voltage converter circuit as mentioned earlier. However, the input impedance and the gain should be maximized in order to linearize the output swing of the circuit and improve its accuracy.

Figure 4.

(a) Two port equivalent network of the proposed circuit. (b) Small signal equivalent model of transistor based CCVS.

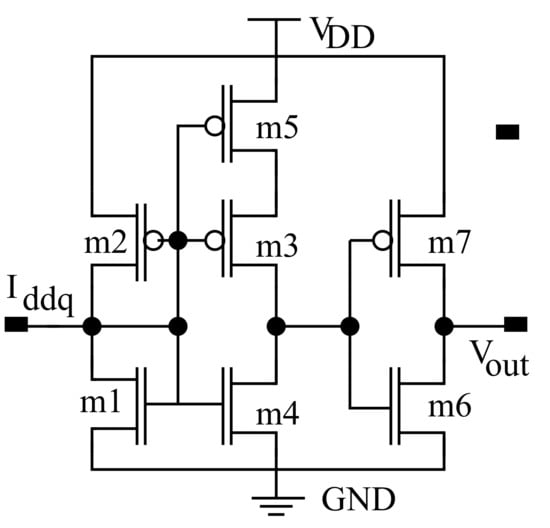

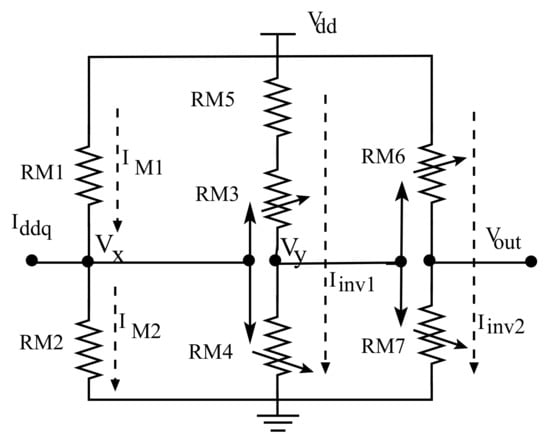

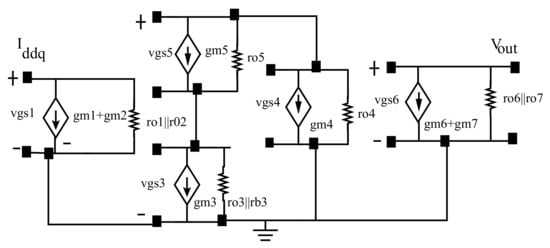

The modified circuit of the BTI and process variation sensor design is shown in Figure 5. The m1 and m2 transistors convert the current to voltage. Amplification is performed by m3 and m4 transistors. The m1 and m2 transistors are diode-connected and work as a resistor in combination with a voltage device. The m5 transistor works as a tuning device which is used to tune the linearity and output swing of the circuit. We can tune the sensor using M5 transistor width. The layout of the proposed sensor at 45 nm (freePDK) is shown in Figure 6.

Figure 5.

Proposed NBTI sensor circuit.

Figure 6.

Layout of the proposed sensor circuit.

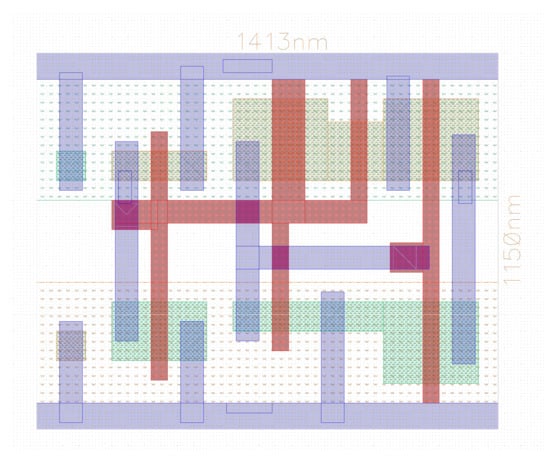

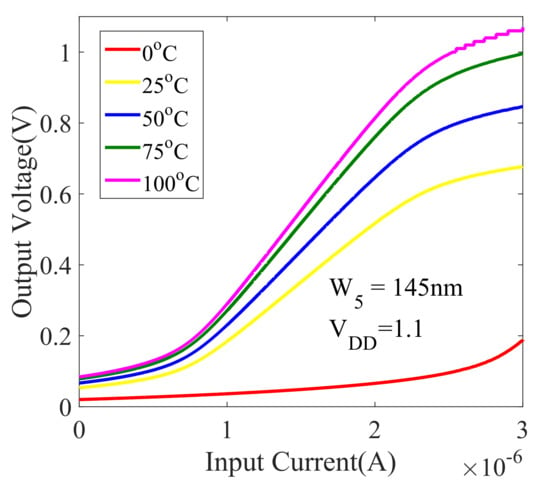

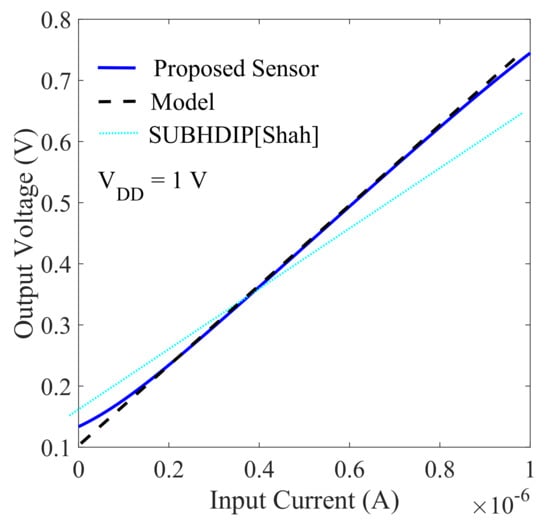

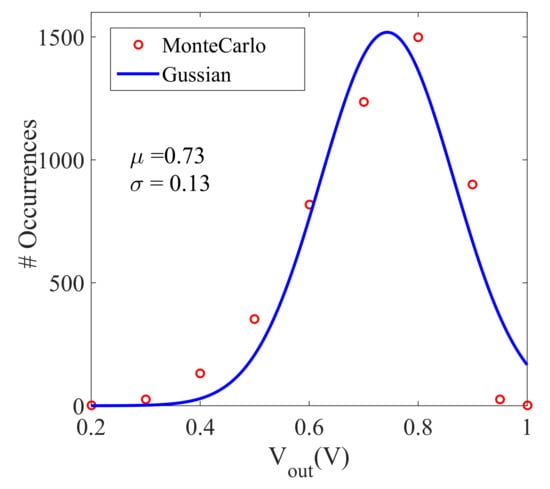

Figure 7 shows the simulation based optimization results for M5. It shows the output voltage for different m5 transistor widths and temperatures. It shows an almost linear relationship between the output voltage and the input current when the transistor width is between 140 nm to 170 nm for the input current ranges from 0 to 1 nA. The proposed sensor is tested for 1 KB SRAM memory where column array size is 128 bits (128 SRAM cell is connected in the column). The maximum leakage current is found to have a value of 3 A for a process corner. It is clear from Figure 8 that over a 3 A range of leakage current, the optimum linear relationship can be achieved by setting = V and = 145 nm. This linear range is achieved by increasing the supply voltage. The m6 and m7 transistors constitute the output stage amplifier for the required full output voltage swing. Simulation result of the sensor shown in Figure 9 shows the ability of the proposed sensor circuit to achieve a large change in the output voltage with a small change of the input current. The range of the output voltage swing ranges from V to V at 1 V supply, which is higher than the output voltage ranges achieved by the state-of-the-art sensor [20]. In order to demonstrate the effect of process variation on the proposed sensor, 5000 Monte Carlo simulations were performed to show the variation in the threshold voltage. The Simulation result is shown in Figure 10 which shows that the mean value and the standard deviation (SD) of the output voltage are smaller than those of the outputs generated by the state-of-the-art designs [20].

Figure 7.

Tuning of the sensor circuit using the M5 transistor.

Figure 8.

Transfer characteristics for the proposed sensor for A range.

Figure 9.

Comparative analysis ot transfer characteristics for the proposed sensor.

Figure 10.

Monte Carlo and Gaussian distribution for output voltage of the proposed sensor.

Mathematical Modeling of the Sensor

The physical operation of the sensor can be described by analyzing its electrical equivalent circuit which is shown in Figure 11. The circuit consists of three-stages: The first stage is the current-to-voltage converter circuit which is designed from the diode-connected transistors followed by the variable resistor circuit. is connected to the gate terminals of the input transistors. Due to the the very high input impedance, is assumed to be zero. Where is shown in the Figure 11.

Figure 11.

Resistor equivalent model of the proposed circuit.

A small change in the can change which causes a change in the voltage which turns m3 and m4 transistors. Hence, the resistance values of , , and depend on and as shown in Equation (7).

where is the current flowing through the first inverter circuit which is followed by the second inverter circuit. Equivalently, and depend on and as shown in Equation (8).

Hence, the output voltage of the sensor circuit is dependent on and . These parameters are also functions of the input current with an amplification factor.

where is the current flowing through the second inverter. This current is a function of which is again a function of with an amplification factor. is a fitting parameter which depends on the technology used. The above analysis explains the electrical behavior of the proposed sensor circuit. However, the exact value of the input impedance and the response of the output voltage with respect to a small change in the Pico-ampere input current can be only found from the small-signal equivalent model of the sensor circuit.

The simplified small-signal equivalent model of the sensor circuit is shown in Figure 12. It is used to find the transfer function of the proposed sensor. By applying the KCL at the output node, the gain or transfer function of the sensor circuit can be derived as follows:

Figure 12.

Small Signal model of the proposed circuit.

If all the transistors have the same dimension and biasing conditions, then the above expression can be simplified as follows:

where is the trans-conductance and is the output resistance of the transistors. The is a function of the output resistance and trans-conductance of the transistors. The sensitivity of the proposed sensor defined by the ratio of the change in output to the change in input as , has the value of mV/nA which is much higher than the sensitivity of the SUBHDIP sensor [20]. The input resistance in the proposed circuit is very high due to the presence of the gate oxide and a diode-connected transistor. The output resistance should be as small as possible for a good amplifier design. The output resistance can be calculated at the node in Figure 12 by applying a test voltage source and using KCL as follows:

A further simplification yields the following:

where and are known parameters that depend on transistor sizing, threshold, and supply voltage [21]. Figure 9 shows a comparison between the simulation of the proposed sensor circuit and its mathematical model. The simulation results show similar characteristics with the model.

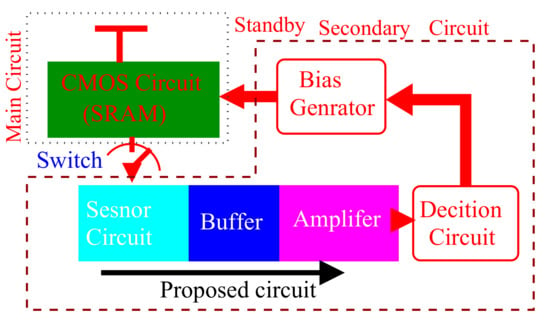

4. Proposed Compensation Circuit

The proposed circuit is tested on a 64X1KB butterfly architecture based SRAM where array size is 128B. The compensation circuit takes the input from the sensor circuit and generates a range of back gate voltages for different input voltages. The generator circuit which is used to compensate for the effect of NBTI in the test circuit is shown in Figure 13. The proposed compensation circuit consists of the decision circuit and the back gate/body () voltage generator. The body bias voltage-generator circuit can be designed by connecting the diode-connected MOSFETs in a series which act as series-connected resistances to generate different voltage levels. The sizing of the transistors in the body bias circuit is optimized as discussed in the previous section so that an equal voltage drop is achieved across each diode-connected MOSFET. The voltage drop across each diode-connected MOSFET depends on the output of the amplifier. The VB voltage control circuit is designed using pseudo NMOS logic where controls the gate of the transistor which is the weak transistor [22]. The body bias generator circuit can be also designed using an on-chip charge pump [23].

Figure 13.

Proposed Compensation SRAM architecture.

5. Results and Discussion

In this section, the simulation results are discussed under various stress conditions. Simulations were performed using cadence virtuoso and HSPICE tools at C, C and C temperatures. The technology used in the simulations is 45 nm technology PDK. MOS Reliability Analysis (MOSRA) model has already been discussed in section III, and is used for the HCI, NBTI, and PBTI induced stress analysis [24].

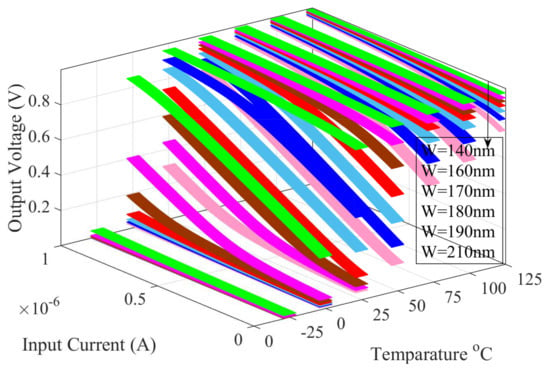

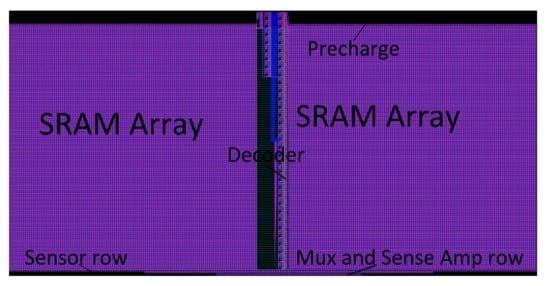

The mico-chip layout of the butterfly based SRAM architecture is shown in Figure 14 with precharge circuits on the top. SRAM array, decoder, and sensor circuits are connected with all the arrays where SRAM array depth is 128B. The multiplixer and sense amplifier are connected bellow the sensor circuits. The total area of the chip without pad is m and the area occupied by the sensor circuit is m which is of the total area.

Figure 14.

Butterfly architecture based without IO-pad SRAM microchip.

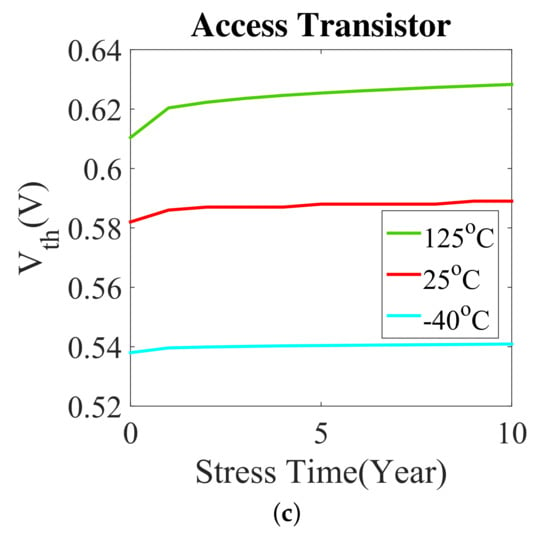

Usually in 6T SRAM, more reading are performed than writing operations. So, the change in the threshold voltage of the 6T SRAM transistors has been calculated in the reading mode as shown in Figure 15. It can be shown from the results that maximum stress is achieved on the driver transistor. Since the Access transistors are directly connected with the wordline and bitlines, they are also affected by the PBTI stress more than the drive transistor. The standby leakage current changes with a change in stress for the SRAM cell. Such a change of the leakage current is measured by a proposed NBTI sensor. The same sensor can be also used to mitigate the effects due to process variation. The read time (RT), write time (WT), and the leakage current for various process corners for 128B SRAM array are shown in Table 1. The minimum and maximum values of the leakage current are 27 nA and uA, respectively. Hence we tune the sensor for 3 nA current range as shown in Figure 8. In order to find the body biasing voltage which is required to shift back the threshold voltage to its normal value as in TT corner, write and read time simulations are performed for SS and FF to TT process corner using different body biasing voltages. Some of the simulation results for SS process corner are shown in Table 2 where it can be seen that the normal threshold voltage at the TT corner can be restored by applying the highlighted body voltages. Similarly, the desired voltages were found from the FF process corner simulations to be ( = V and = V). The range of the body biasing voltage can be generated using the proposed sensor and charge pump circuits since the range of the proposed sensor output voltage is V to 1 V.

Figure 15.

Degradation in

of SRAM cell transistors in 10 year NBTI & PBTI stress.

Table 1.

Process Corner and leakage currents.

Table 2.

Body biasing voltage.

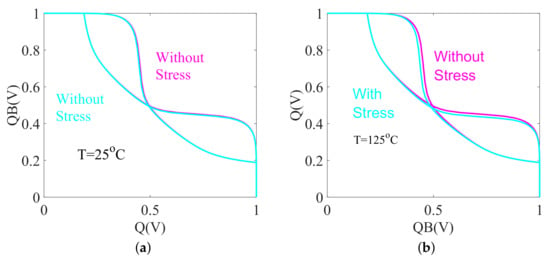

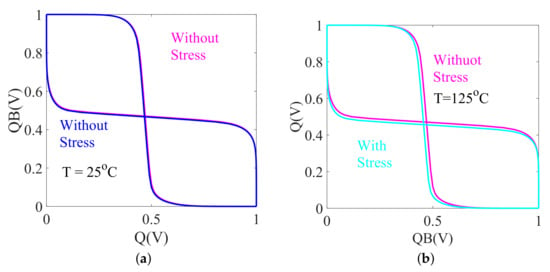

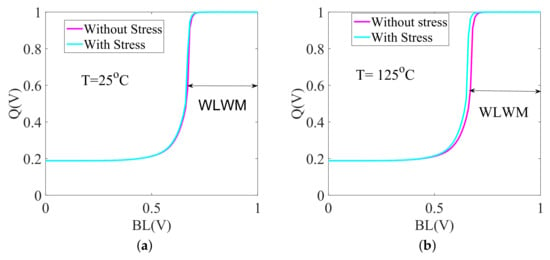

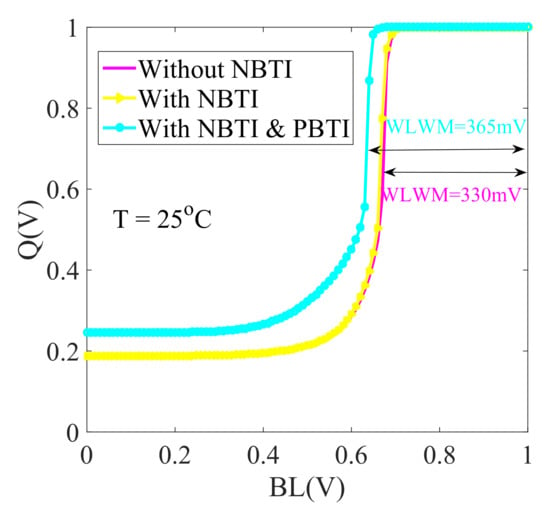

The standby leakage current of SRAM cell at 45 nm technology is known to be around a few nano-amperes [25,26,27]. RNM and SNM are the read and static noise margins, respectively, which are the parameters used to examine the stability of the SRAM cell. The performance of SRAM is examined using the word line write margin (WLWM) and read current parameters. Figure 16 and Figure 17 show the degradation of the RNM and SNM due to NBTI at C and C temperatures. The effect of NBTI further increases at higher temperatures where it further degrades the stability of the SRAM. Figure 18 shows the degradation of the WLWM under NBTI stress at C and C temperatures, respectively. It is clear that the WLWM is more degraded by the NBTI effect than the stability parameters. The amount of degradation of WLWM also increases at higher temperatures. NBTI is a more critical issue in PMOS than PBTI. However, a combination of NBTI and PBTI which exists in most of the real cases has a much bigger effect on the stability and performance of the SRAM cell than the effect due to NBTI only. In addition, the combined effect of NBTI and PBTI causes the change of the threshold voltage of the transistors. The high impact of the combined effect of NBTI and PBTI on the design is also demonstrated by the variation in WLWM as shown in Figure 19. The effects of NBTI, PBTI, and their combination on reading, writing, and the standby leakage current at C temperature are shown in Table 3.

Figure 16.

Degradation in RNM under 10 year NBTI stress at (a) T = C. (b) T = C.

Figure 17.

Degradation in SNM under 10 year NBTI stress at (a) T = C. (b) T = C.

Figure 18.

Degradation in WLWM under 10 year NBTI stress at (a) T = C. (b) T = C.

Figure 19.

Degradation in WLWM under 10 year NBTI and PBTI stress.

Table 3.

Degradation in SRAM stability and performance with 10 Year stress.

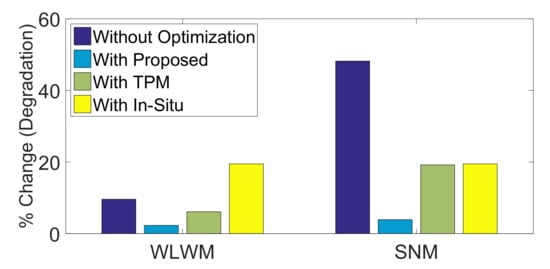

Figure 20 shows a comparison between the proposed sensor-based mitigation technique and that of the state-of-the-art under the combined NBT and PBTI stress. The effectiveness of the proposed O-ABB circuit based mitigation technique has been examined by comparing simulations performed for the SRAM cell with and without the use of the O-ABB circuit. The body-bias voltage generator circuit provides different output voltages with different stress value. The precision of this circuit depends on the input voltage provided by the sensor. Therefore, it is linear and sensitive towards a minimal change in the input current.

Figure 20.

Comparison of stability and write performance failure for proposed and existing techniques In-Situ [9] and (TPM) [28].

The proposed design has many advantages but every design also has limitations in terms of speed, area and stability. The proposed sensor can perfectly work for the temperature range C to C. However, sensor can be made work in a wider range of temperatures by increasing the six=ze of the transistors. The proposed design also requires larger design area and higher power budget. One of the key limitations of this circuit is that its required minimum working supply voltage is 1.1 V. The additional clock cycle needed for the proposed circuit causes delay and limits the performance. Therefore, Improving the circuit design to allow its operation at lower voltage levels without additional clock cycles will be our future research topic.

6. Conclusions

The process variation, BTI (NBTI and PBTI) are the most critical issues affecting the reliability of the circuit design. They become more critical for systems designed for defense and aerospace applications because these reliability degradation sources decrease the system’s stability and life. Mostly, SRAM is used as cache memory inside the microprocessor to bridge the gap between the logic and the main memory speed. The shift in the threshold voltages of SRAM cells due to BTI can cause degradation of the performance and stability. The proposed BTI mitigation technology not only detects small changes in the device threshold voltage and mitigates the consequent degradation, but also detects the change in the leakage current and converts it to voltage. Simulation results show that the proposed sensor provides 33% higher output voltage and 98% sensitivity at 1V supply voltage than other conventional state-of-the-art sensors. In addition, the proposed technology can mitigate up to 80% of the effects due to NBTI and PBTI in SRAM compared to conventional technologies. The output voltage has been calculated using the small-signal equivalent model of the sensor circuit and was compared with the simulation result. The simulation of the model also proved the efficiency of the proposed sensor. The area overhead of the proposed techniques can also be decreased by increasing the SRAM size. The proposed sensor circuit can be used with any analog and digital CMOS circuit.

Author Contributions

Conceptualization, N.Y.; Investigation, Writing-original draft, Writing-review and editing, Y.K.; Writing draft and editing, M.A.; Editing, K.K.C.; Funding acquisition and supervisor. All authors have read and agreed to the published version of the manuscript.

Funding

“This research was funded by the Industrial Core Technology Development Program of MOTIE/KEIT, KOREA grant number 10083639.”

Acknowledgments

We thank our colleagues from KETI and KEIT who provided insight and expertise that greatly assisted the research and greatly improved the manuscript. This work is also supported by the Industrial Core Technology Development Program of MOTIE/KEIT, KOREA [# 10083639.]

Conflicts of Interest

The authors declare no conflict of interest.

References

- Wang, Y.; Cotofana, S.; Fang, L. A unified aging model of NBTI and HCI degradation towards lifetime reliability management for nanoscale MOSFET circuits. In Proceedings of the IEEE/ACM International Symposium on Nanoscale Architectures, IEEE Computer Society, San Diego, CA, USA, 8–9 June 2011; pp. 175–180. [Google Scholar]

- Ahn, W.; Zhang, H.; Shen, T.; Christiansen, C.; Justison, P.; Shin, S.; Alam, M.A. A Predictive Model for IC Self-Heating Based on Effective Medium and Image Charge Theories and Its Implications for Interconnect and Transistor Reliability. IEEE Trans. Electron Devices 2017, 64, 3555–3562. [Google Scholar] [CrossRef]

- Igarashi, M.; Uchida, Y.; Takazawa, Y.; Yabuuchi, M.; Tsukamoto, Y.; Shibutani, K. Study of Local BTI Variation and its Impact on Logic Circuit and SRAM in 7 nm Fin-FET Process. In Proceedings of the IEEE International Reliability Physics Symposium (IRPS), Monterey, CA, USA, 31 March–4 April 2019; pp. 1–6. [Google Scholar]

- Dai, L.; Lü, W.; Lin, M. Random Dopant Fluctuation-Induced Variability in n-Type Junctionless Dual-Metal Gate FinFETs. Electronics 2019, 8, 282. [Google Scholar] [CrossRef]

- Zhang, R.; Liu, Z.; Yang, K.; Liu, T.; Cai, W.; Milor, L. Impact of front-end wearout mechanisms on FinFET SRAM soft error rate. Microelectron. Reliab. 2019, 100, 113487. [Google Scholar] [CrossRef]

- Zhang, L.; Liu, L.; Zhuang, Y.; Tang, H.; Xu, B.; Bao, J.; Wu, H. A novel sense amplifier to mitigate the impact of NBTI and PVT variations for STT-MRAM. IEICE Electron. Express 2019, 16, 20190238. [Google Scholar] [CrossRef]

- Singh, P.; Karl, E.; Blaauw, D.; Sylvester, D. Compact Degradation Sensors for Monitoring NBTI and Oxide Degradation. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2012, 20, 1645–1655. [Google Scholar] [CrossRef]

- Sai, G.; Halak, B.; Zwolinski, M. Multi-Path Aging Sensor for Cost-Efficient Delay Fault Prediction. IEEE Trans. Circuits Syst. II: Express Briefs 2018, 65, 491–495. [Google Scholar] [CrossRef]

- Yang, T.; Kim, D.; Li, J.; Kinget, P.R.; Seok, M. In Situ and In-Field Technique for Monitoring and Decelerating NBTI in 6T-SRAM Register Files. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2018, 26, 2241–2253. [Google Scholar] [CrossRef]

- Shah, A.P.; Yadav, N.; Beohar, A.; Vishvakarma, S.K. On-Chip Adaptive Body Bias for Reducing the Impact of NBTI on 6T SRAM Cells. IEEE Trans. Semicond. Manuf. 2018, 31, 242–249. [Google Scholar] [CrossRef]

- Jeppson, K.O.; Svensson, C.M. Negative bias stress of MOS devices at high electric fields and degradation of MNOS devices. Appl. Phys. 1977, 48, 2004–2014. [Google Scholar] [CrossRef]

- Kumar, S.V.; Kim, C.H.; Sapatnekar, S.S. An analytical model for negative bias temperature instability. In Proceedings of the IEEE/ACM international conference on Computer-aided design, San Jose, CA, USA, 5–9 November 2006; pp. 493–496. [Google Scholar]

- Tudor, B.; Wang, J.; Liu, W.; Elhak, H. MOS Device Aging Analysis with HSPICE and CustomSim. Synopsys White Pap. 2011. Available online: https://pdfs.semanticscholar.org/3f78/524f5c3e6d7da1b2f4c322031ad1f415da80.pdf (accessed on 3 February 2020).

- Habchi, R.; Salame, C.; Khoury, A.; Mialhe, P. Temperature dependence of a silicon power device switching parameters. Appl. Phys. Lett. 2006, 88, 153503. [Google Scholar] [CrossRef]

- Khan, S.; Hamdioui, S. Temperature dependence of NBTI induced delay. In Proceedings of the IEEE 16th International On-Line Testing Symposium, Corfu Island, Greece, 4–7 July 2010; pp. 15–20. [Google Scholar]

- Khan, M.; Hamdioui, S. Temperature impact on NBTI modeling in the framework of technology scaling. In Proceedings of the 2nd HiPEAC Workshop on Design for Reliability, Pisa, Italy, 25–27 January 2010; Volume 24. [Google Scholar]

- Fan, M.L.; Hu, V.P.H.; Chen, Y.N.; Su, P.C.; Chuang, C.T. Analysis of single-trap-induced random telegraph noise on FinFET devices, 6T SRAM cell, and logic circuits. IEEE Trans. Electron. Devices 2012, 59, 2227–2234. [Google Scholar] [CrossRef]

- Kang, K.; Kufluoglu, H.; Roy, K.; Alam, M.A. Impact of negative-bias temperature instability in nanoscale SRAM array: Modeling and analysis. IEEE Trans. Comput.-Aided Des. Integr. Syst. 2007, 26, 1770–1781. [Google Scholar] [CrossRef]

- Singh, H.; Mahmoodi, H. Analysis of SRAM reliability under combined effect of NBTI, process and temperature variations in nano-scale CMOS. In Proceedings of the IEEE International Conference on Future Information Technology, Changsha, Hunan, China, 14–15 December 2010; pp. 1–4. [Google Scholar]

- Shah, A.P.; Yadav, N.; Beohar, A.; Vishvakarma, S.K. SUBHDIP: Process variations tolerant subthreshold Darlington pair-based NBTI sensor circuit. IET Comput. Digit. Tech. 2018, 13, 243–249. [Google Scholar] [CrossRef]

- Razavi, B. Design of Analog CMOS Integrated Circuits; McGraw-Hill Education: New York, NY, USA, 2005. [Google Scholar]

- Lee, Z.C.; Leong, K.C.; Kong, Z.H.; Kim, T.T. NBTI/PBTI-Aware WWL Voltage Control for Half-Selected Cell Stability Improvement. IEEE Trans. Circuits Syst. II: Express Briefs 2013, 60, 602–606. [Google Scholar] [CrossRef]

- Chen, P.-H.; Ishida, K.; Zhang, X.; Okuma, Y.; Ryu, Y.; Takamiya, M.; Sakurai, T. 0.18-V input charge pump with forward body biasing in startup circuit using 65 nm CMOS. In Proceedings of the IEEE Custom Integrated Circuits Conference 2010, San Jose, CA, USA, 19–22 September 2010; pp. 1–4. [Google Scholar] [CrossRef]

- HPICE User Guide: Simulation and Analysis, Synopsys, Mountain View, CA, USA. 2018. Available online: https://www.synopsys.com/content/dam/synopsys/verification/datasheets/hspice-ds.pdf (accessed on 3 February 2020).

- Thomas, O.; Vinet, M.; Rozeau, O.; Batude, P.; Valentian, A. Compact 6T SRAM cell with robust read/write stabilizing design in 45nm Monolithic 3D IC technology. In Proceedings of the IEEE International Conference on IC Design and Technology, Austin, TX, USA, 18–20 May 2009; pp. 195–198. [Google Scholar] [CrossRef]

- Kim, N.S.; Austin, T.; Blaauw, D.; Mudge, T.; Hu, J.S.; Irwin, M.J.; Kandemir, M.; Narayanan, V. Leakage Current: Moore’s law meets static power. Computer 2003, 36, 68–75. [Google Scholar]

- Zhao, W.; Cao, Y. New Generation of Predictive Technology Model for Sub-45 nm Early Design Exploration. IEEE Trans. Electron. Devices 2006, 53, 2816–2823. [Google Scholar] [CrossRef]

- Yadav, N.; Jain, S.; Pattanaik, M.; Sharma, G. NBTI aware IG-FinFET based SRAM design using adaptable trip-point sensing technique. In Proceedings of the IEEE/ACM International Symposium on Nanoscale Architectures, Paris, France, 8–10 July 2014; pp. 122–128. [Google Scholar]

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).