An FPGA-Based Neuron Activity Extraction Unit for a Wireless Neural Interface

Abstract

1. Introduction

2. Methodology

3. System Architecture

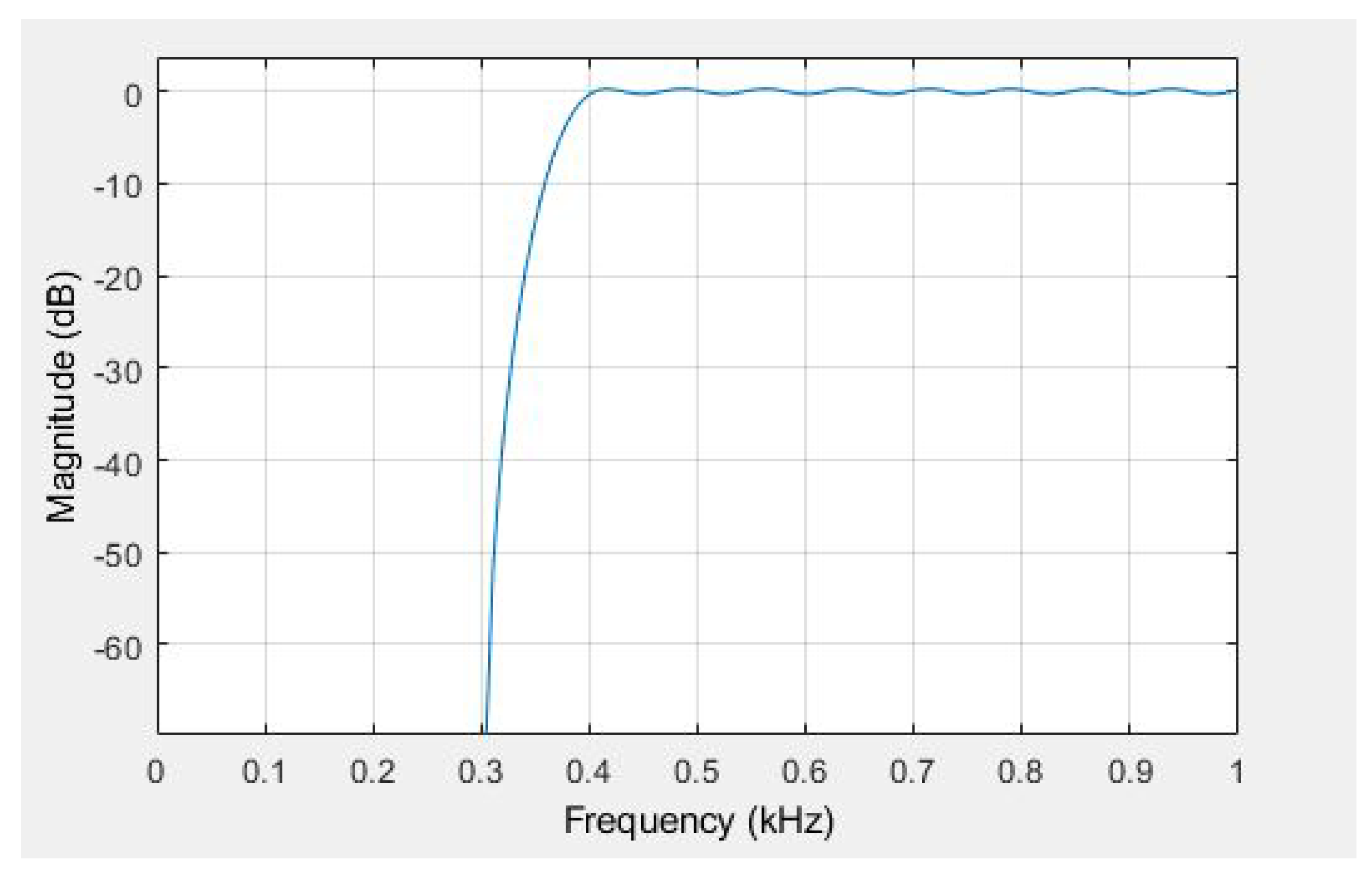

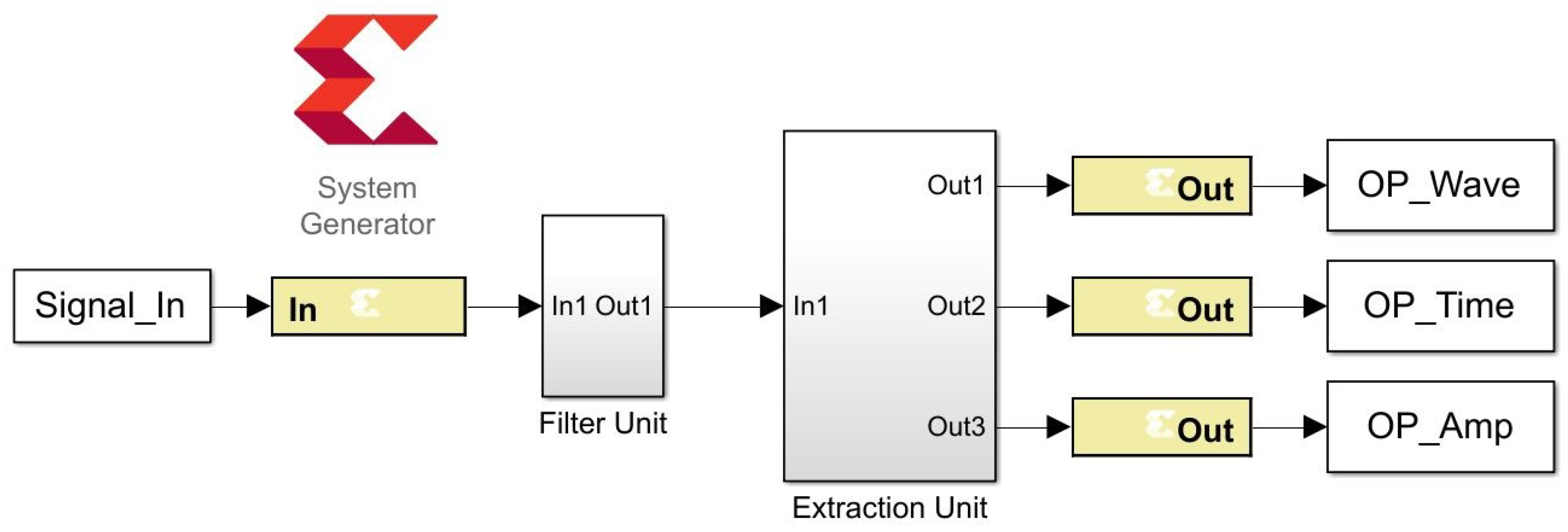

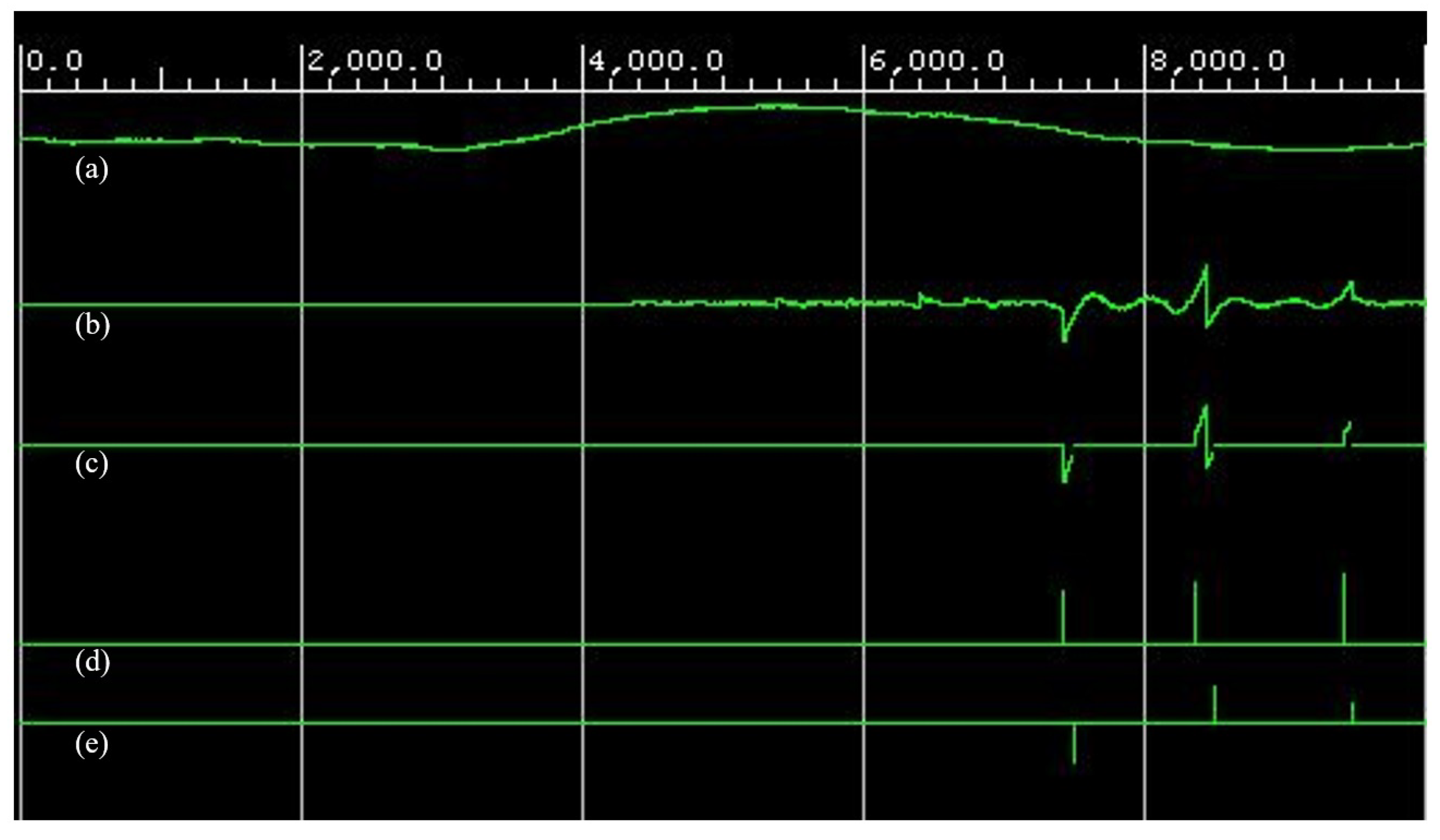

3.1. Neural Signal Filter Unit

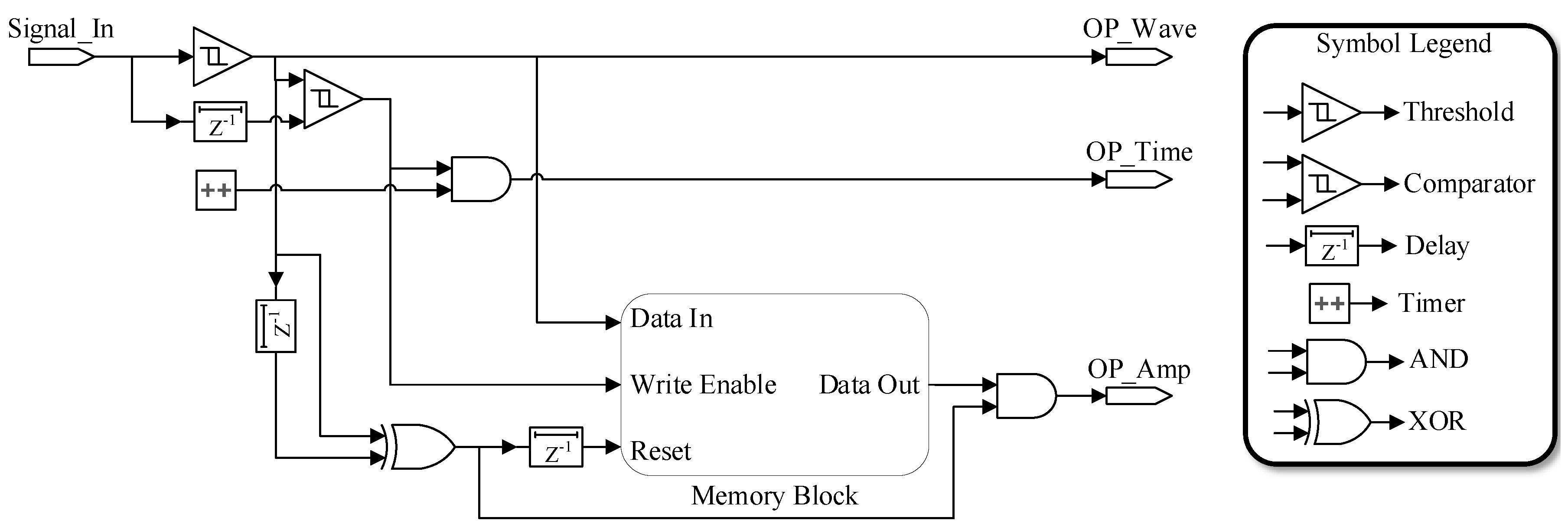

3.2. Neuron Activity Extraction Unit

| Algorithm 1: Neuron activity extraction. |

|

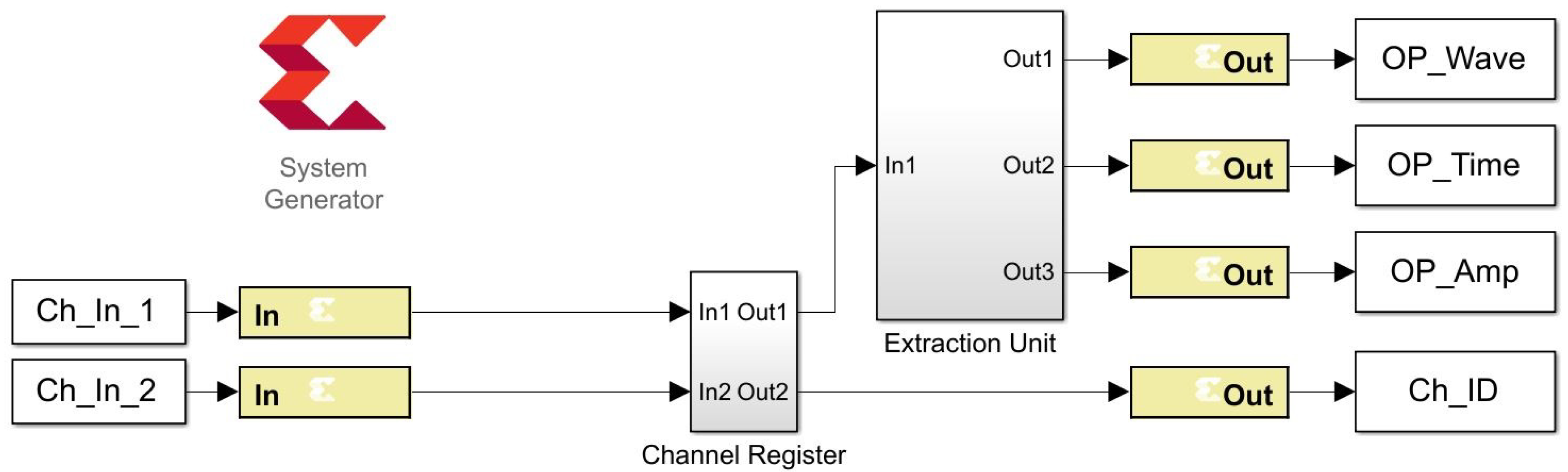

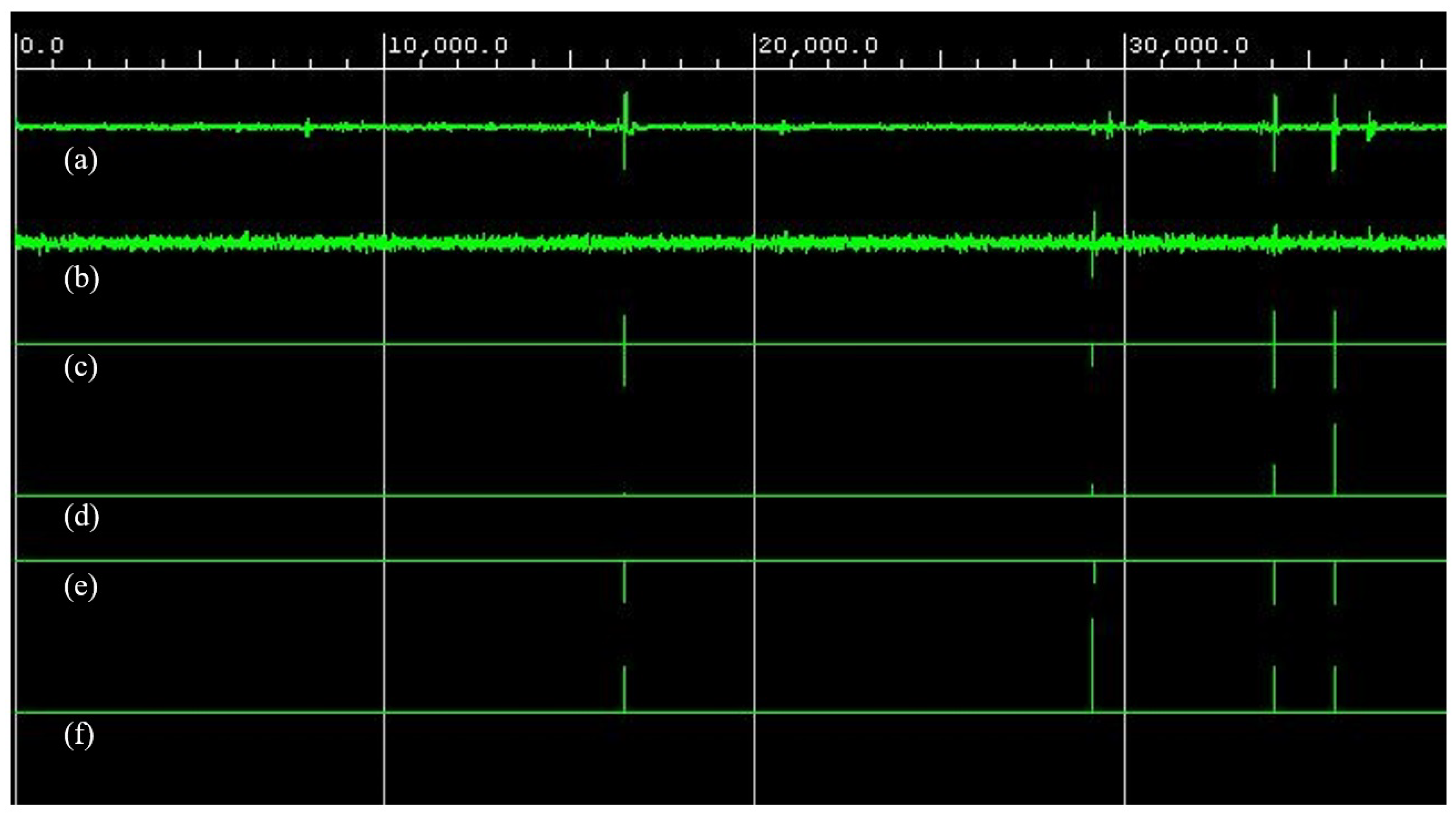

3.3. Channel Activity Register

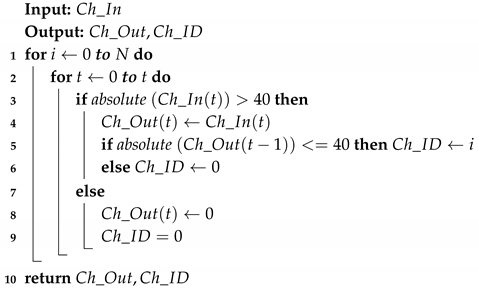

| Algorithm 2: Channel activation register. |

|

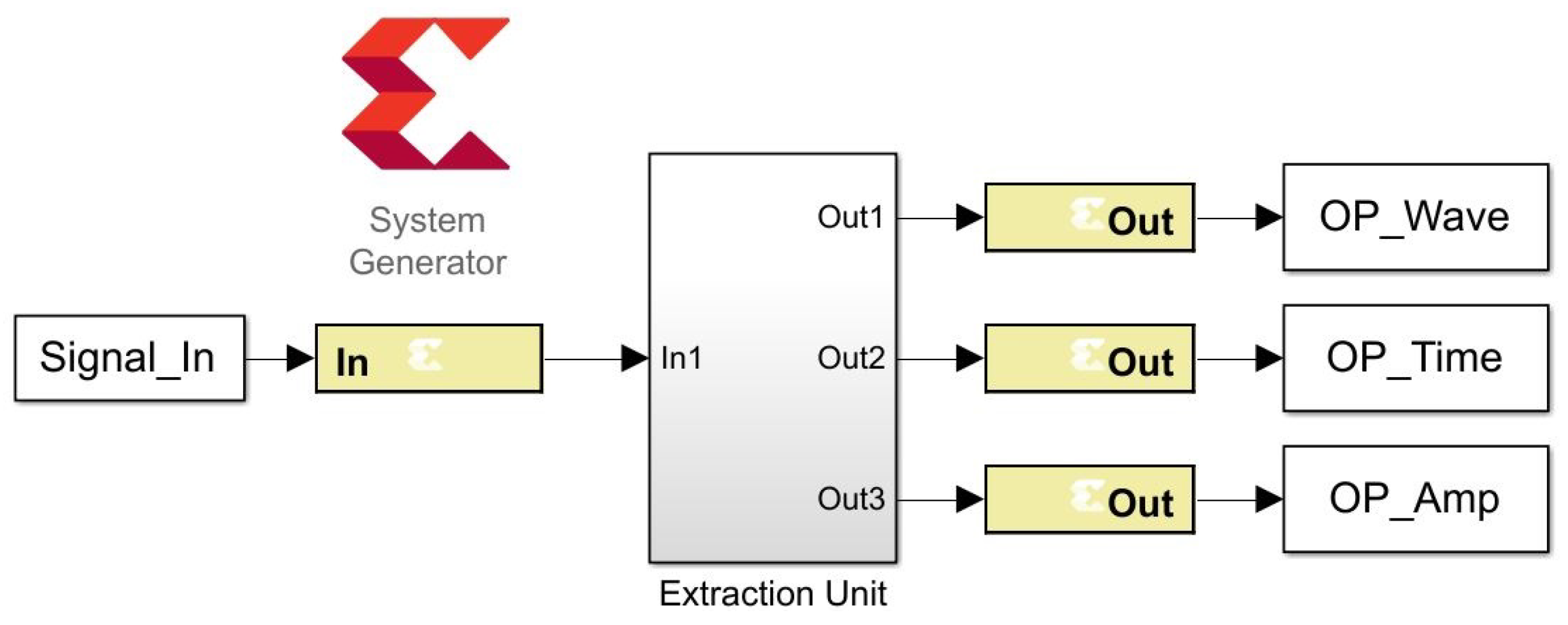

3.4. Complete Model

- Single-channel filtered (SCF) input;

- Single-channel unfiltered (SCUF) input;

- Multichannel filtered (MCF) input;

- Multichannel unfiltered (MCUF) input.

4. Implementation and Results

5. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Hatsopoulos, N.G.; Donoghue, J.P. The science of neural interface systems. Annu. Rev. Neurosci. 2010, 32, 249–266. [Google Scholar] [CrossRef]

- Yuan, H.; He, B. Brain-computer interfaces using sensorimotor rhythms: Current state and future perspectives. IEEE Trans. Biomed. Eng. 2014, 61, 1425–1435. [Google Scholar] [CrossRef]

- Elyahoodayan, S.; Jiang, W.; Xu, H.; Song, D. A Multi-Channel Asynchronous Neurostimulator with Artifact Suppression for Neural Code-Based Stimulations. Front. Neurosci. 2019, 13, 1011. [Google Scholar] [CrossRef]

- Grill, W.M.; Norman, S.E.; Bellamkonda, R.V. Implanted neural interfaces: Biochallenges and engineered solutions. Annu. Rev. Biomed. Eng. 2009, 11, 1–24. [Google Scholar] [CrossRef]

- Donoghue, J.P. Bridging the brain to the world: A perspective on neural interface systems. Neuron 2008, 60, 511–521. [Google Scholar] [CrossRef] [PubMed]

- Gao, H.; Walker, R.M.; Nuyujukian, P.; Makinwa, K.A.; Shenoy, K.V.; Murmann, B.; Meng, T.H. HermesE: A 96-channel full data rate direct neural interface in 0.13 μm CMOS. IEEE J. Solid State Circ. 2012, 47, 1043–1055. [Google Scholar] [CrossRef]

- Hampson, R.E.; Song, D.; Robinson, B.S.; Fetterhoff, D.; Dakos, A.S.; Roeder, B.M.; She, X.; Wicks, R.T.; Witcher, M.R.; Couture, D.E.; et al. Developing a hippocampal neural prosthetic to facilitate human memory encoding and recall. J. Neural Eng. 2018, 15, 36014. [Google Scholar] [CrossRef]

- Farshchi, S.; Nuyujukian, P.H.; Pesterev, A.; Mody, I.; Judy, J.W. A TinyOS-enabled MICA2-based wireless neural interface. IEEE Trans. Biomed. Eng. 2006, 53, 1416–1424. [Google Scholar] [CrossRef]

- Kueh, S.M.; Kazmierski, T.J. Low-Power and Low-Cost Dedicated Bit-Serial Hardware Neural Network for Epileptic Seizure Prediction System. IEEE J. Transl. Eng. Health Med. 2018, 6, 1–9. [Google Scholar] [CrossRef]

- Szuts, T.A.; Fadeyev, V.; Kachiguine, S.; Sher, A.; Grivich, M.V.; Agrochão, M.; Hottowy, P.; Dabrowski, W.; Lubenov, E.V.; Siapas, A.G.; et al. A wireless multi-channel neural amplifier for freely moving animals. Nat. Neurosci. 2011, 14, 263. [Google Scholar] [CrossRef]

- Lee, B.; Koripalli, M.K.; Jia, Y.; Acosta, J.; Sendi, M.S.; Choi, Y.; Ghovanloo, M. An Implantable Peripheral Nerve Recording and Stimulation System for Experiments on Freely Moving Animal Subjects. Sci. Rep. 2018, 8, 1–12. [Google Scholar] [CrossRef] [PubMed]

- Borton, D.A.; Yin, M.; Aceros, J.; Nurmikko, A. An implantable wireless neural interface for recording cortical circuit dynamics in moving primates. J. Neural Eng. 2013, 10. [Google Scholar] [CrossRef] [PubMed]

- Lee, B.; Jia, Y.; Abdollah Mirbozorgi, S.; Connolly, M.; Tong, X.; Zeng, Z.; Mahmoudi, B.; Ghovanloo, M. An Inductively-Powered Wireless Neural Recording and Stimulation System for Freely-Behaving Animals. IEEE Trans. Biomed. Circ. Syst. 2019, 13, 413–424. [Google Scholar] [CrossRef] [PubMed]

- Chowdhury, M.; Hossain, Q.; Azad Hossain, M.; Cheung, R. Single feed circularly polarized crescent-cut and extended corner square microstrip antennas for wireless biotelemetry. Int. J. Electr. Comput. Eng. 2019, 9, 1902–1909. [Google Scholar] [CrossRef]

- Mora Lopez, C.; Putzeys, J.; Raducanu, B.C.; Ballini, M.; Wang, S.; Andrei, A.; Rochus, V.; Vandebriel, R.; Severi, S.; Van Hoof, C.; et al. A Neural Probe with up to 966 Electrodes and up to 384 Configurable Channels in 0.13 μm SOI CMOS. IEEE Trans. Biomed. Circ. Syst. 2017, 11, 510–522. [Google Scholar] [CrossRef]

- Chen, D.; Li, X.; Wang, L.; Khan, S.U.; Wang, J.; Zeng, K.; Cai, C. Fast and Scalable Multi-Way Analysis of Massive Neural Data. IEEE Trans. Comput. 2015, 64, 707–719. [Google Scholar] [CrossRef]

- Shulyzki, R.; Abdelhalim, K.; Bagheri, A.; Salam, M.T.; Florez, C.M.; Velazquez, J.L.P.; Carlen, P.L.; Genov, R. 320-Channel Active Probe for High-Resolution Neuromonitoring and Responsive Neurostimulation. IEEE Trans. Biomed. Circuits Syst. 2015, 9, 34–49. [Google Scholar] [CrossRef]

- Sodagar, A.M.; Perlin, G.E.; Yao, Y.; Najafi, K.; Wise, K.D. An Implantable 64-Channel Wireless Microsystem for Single-Unit Neural Recording. IEEE J. Solid State Circuits 2009, 44, 2591–2604. [Google Scholar] [CrossRef]

- Chowdhury, M.H.; Cheung, R.C.C. Reconfigurable Computing and Hardware Acceleration in Health Informatics. In Signal Processing Techniques for Computational Health Informatics, 1st ed.; Ahad, M.A.R., Ahmed, M.U., Eds.; Springer International Publishing: New York, NY, USA, 2020; Chapter 9; pp. 209–229. [Google Scholar] [CrossRef]

- Chowdhury, M.H.; Cheung, R.C.C. Reconfigurable Architecture for Multi-lead ECG Signal Compression with High-frequency Noise Reduction. Sci. Rep. 2019, 9, 17233. [Google Scholar] [CrossRef] [PubMed]

- Chowdhury, M.H.; Cheung, R.C.C. Point-of-Care EMG Processor for the Differential Diagnosis of Neuropathy and Myopathy. In Proceedings of the IEEE EMB Special Topic Conference on Healthcare Innovations and Point-of-Care Technologies, Bethesda, MD, USA, 20–22 November 2019. [Google Scholar]

- Kim, C.; Park, J.; Ha, S.; Akinin, A.; Kubendran, R.; Mercier, P.P.; Cauwenberghs, G. A 3 mm × 3 mm Fully Integrated Wireless Power Receiver and Neural Interface System-on-Chip. IEEE Trans. Biomed. Circuits Syst. 2019, 13, 1736–1746. [Google Scholar] [CrossRef]

- Lo, Y.K.; Kuan, Y.C.; Culaclii, S.; Kim, B.; Wang, P.M.; Chang, C.W.; Massachi, J.A.; Zhu, M.; Chen, K.; Gad, P.; et al. A Fully Integrated Wireless SoC for Motor Function Recovery after Spinal Cord Injury. IEEE Trans. Biomed. Circuits Syst. 2017, 11, 497–509. [Google Scholar] [CrossRef]

- Kang, Y.N.; Chou, N.; Jang, J.; Byun, D.; Kang, H.; Moon, D.; Kim, J.; Kim, S. An Intrafascicular Neural Interface With Enhanced Interconnection for Recording of Peripheral Nerve Signals. IEEE Trans. Neural Syst. Rehabil. Eng. 2019, 27, 1312–1319. [Google Scholar] [CrossRef]

- Bonfanti, A.; Ceravolo, M.; Zambra, G.; Gusmeroli, R.; Borghi, T.; Spinelli, A.S.; Lacaita, A.L. A multi-channel low-power IC for neural spike recording with data compression and narrowband 400-MHz MC-FSK wireless transmission. In Proceedings of the ESSCIRC 2010 - 36th European Solid State Circuits Conference, Seville, Spain, 13–17 September 2010; pp. 330–333. [Google Scholar] [CrossRef]

- Chae, M.S.; Yang, Z.; Yuce, M.R.; Hoang, L.; Liu, W. A 128-channel 6 mW wireless neural recording IC with spike feature extraction and UWB transmitter. IEEE Trans. Neural Syst. Rehabil. Eng. 2009, 17, 312–321. [Google Scholar] [CrossRef]

- Harrison, R.R. A versatile integrated circuit for the acquisition of biopotentials. In Proceedings of the 2007 IEEE Custom Integrated Circuits Conference, San Jose, CA, USA, 16–19 September 2007; pp. 115–122. [Google Scholar]

- Xu, H.; Hirschberg, A.W.; Scholten, K.; Berger, T.W.; Song, D.; Meng, E. Acute in vivo testing of a conformal polymer microelectrode array for multi-region hippocampal recordings. J. Neural Eng. 2018, 15, 16017. [Google Scholar] [CrossRef]

- Liu, X.; Zhang, M.; Xiong, T.; Richardson, A.G.; Lucas, T.H.; Chin, P.S.; Etienne-Cummings, R.; Tran, T.D.; Van der Spiegel, J. A Fully Integrated Wireless Compressed Sensing Neural Signal Acquisition System for Chronic Recording and Brain Machine Interface. IEEE Trans. Biomed. Circuits Syst. 2016, 10, 874–883. [Google Scholar] [CrossRef]

- Versen, M.; Kipfelsberger, S.; Soekmen, F. Model-Based Reference Design Projects with MathWorks’ HDL Workflow Advisor for Custom-Specific Electronics with the Zedboard. In ANALOG 2016; 15. ITG/GMM-Symposium; VDE: Hong Kong, China, 2016; pp. 1–4. [Google Scholar]

- Kang, J.; Yoon, C.; Lee, J.; Kye, S.; Lee, Y.; Chang, J.H.; Kim, G.; Yoo, Y.; Song, T. A System-on-Chip Solution for Point-of-Care Ultrasound Imaging Systems: Architecture and ASIC Implementation. IEEE Trans. Biomed. Circuits Syst. 2016, 10, 412–423. [Google Scholar] [CrossRef]

- Rahane, S.B.; Kureshi, A.K.; Kharate, G.K. OTA-C Filters for Biomedical Signal Processing Applications using Hybrid CMOS-CNFET Technology. In Proceedings of the International Conference on Intelligent and Innovative Computing Applications (ICONIC), Tsim Sha Tsui, Kowloon, 6–7 December 2018; pp. 1–5. [Google Scholar]

- Smith, S.W. The Scientist and Engineer’s Guide to Digital Signal Processing; California Technical Pub.: San Diego, CA, USA, 1997. [Google Scholar]

- Greenberg, D.S.; Houweling, A.R.; Kerr, J.N. Population imaging of ongoing neuronal activity in the visual cortex of awake rats. Nat. Neurosci. 2008, 11, 749–751. [Google Scholar] [CrossRef]

- Shahrokhi, F.; Abdelhalim, K.; Serletis, D.; Carlen, P.L.; Genov, R. The 128-channel fully differential digital integrated neural recording and stimulation interface. IEEE Trans. Biomed. Circuits Syst. 2010, 4, 149–161. [Google Scholar] [CrossRef]

| Configuration | LUT | LUTRAM | FF | BRAM | DSP |

|---|---|---|---|---|---|

| SCF | 34 | 0 | 1 | 0.5 | 0 |

| SCUF | 778 | 465 | 1353 | 0.5 | 26 |

| MCF | 35 | 0 | 1 | 0.5 | 0 |

| MCUF | 1500 | 930 | 2703 | 0.5 | 52 |

| Reference | Primary Focus | Implement | Reconfigurability | Scalability | Channel Count | Transmission/ Data Rate | Power |

|---|---|---|---|---|---|---|---|

| Farshchi et al. [8] | Communication technique | PCB | No | No | 6 | 9.6 Kbps | 66 mW |

| Borton et al. [12] | Communication technique | PCB | No | No | 100 | 24 Mbps | 90.6 mW |

| Lee et al. [11] | Communication technique | ASIC | No | No | 32 | 9 Mbps | 18.9 mW |

| Kim et al. [22] | Wireless power transmission | ASIC | No | No | 16 | 15 Kbps | - |

| Lee et al. [13] | Wireless power transmission | ASIC | No | No | 32 | 9 Mbps | 35 mW |

| Lo et al. [23] | Electrode development | ASIC | No | No | 160 | 2 Mbps | 18 mW |

| Kang et al. [24] | Electrode development | PCB | No | No | 5 | 2 Mbps | - |

| Bonfanti et al. [25] | Data compression | ASIC | No | No | 64 | 1.25 Mbps | 16.6 mW |

| Shahrokhi et al. [35] | Signal conditioning | ASIC | No | No | 128 | - | 7 mW |

| Chae et al. [26] | Spike Sorting | ASIC | No | No | 128 | 90 Mbps | 6 mW |

| This work | Neuron activity extraction | FPGA | Yes | Yes | User Defined | 1.6 Kbps | 3 mW |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Chowdhury, M.H.; Elyahoodayan, S.; Song, D.; Cheung , R.C.C. An FPGA-Based Neuron Activity Extraction Unit for a Wireless Neural Interface. Electronics 2020, 9, 1834. https://doi.org/10.3390/electronics9111834

Chowdhury MH, Elyahoodayan S, Song D, Cheung RCC. An FPGA-Based Neuron Activity Extraction Unit for a Wireless Neural Interface. Electronics. 2020; 9(11):1834. https://doi.org/10.3390/electronics9111834

Chicago/Turabian StyleChowdhury, Mehdi Hasan, Sahar Elyahoodayan, Dong Song, and Ray C. C. Cheung . 2020. "An FPGA-Based Neuron Activity Extraction Unit for a Wireless Neural Interface" Electronics 9, no. 11: 1834. https://doi.org/10.3390/electronics9111834

APA StyleChowdhury, M. H., Elyahoodayan, S., Song, D., & Cheung , R. C. C. (2020). An FPGA-Based Neuron Activity Extraction Unit for a Wireless Neural Interface. Electronics, 9(11), 1834. https://doi.org/10.3390/electronics9111834