Abstract

In recent years number of Internet of Things (IoT) services and devices is growing and Internet of Vehicles (IoV) technologies are emerging. Multiband transceiver with high performance frequency synthesisers should be used to support a multitude of existing and developing wireless standards. In this paper noise sources of an all-digital frequency synthesiser are discussed through s-domain model of frequency synthesisers, and the impact of noise induced by main blocks of synthesisers to the overall phase noise of frequency synthesisers is analysed. Requirements for time to digital converter (TDC), digitally controlled oscillator (DCO) and digital filter suitable for all-digital frequency synthesiser for IoT and IoV applications are defined. The structure of frequency synthesisers, which allows us to meet defined requirements, is presented. Its main parts are 2D Vernier TDC based on gated ring oscillators, which can achieve resolution close to 1 ps; multi core LC-tank DCO, whose tuning range is 4.3–5.4 GHz when two cores are used and phase noise is −116.4 dBc/Hz at 1 MHz offset from 5.44 GHz carrier; digital filter made of proportional and integral gain stages and additional infinite impulse response filter stages. Such a structure allows us to achieve a synthesiser’s in-band phase noise lower than −100 dBc/Hz, out-of-band phase noise equal to −134.0 dBc/Hz and allows us to set a synthesiser to type-I or type-II and change its order from first to sixth.

1. Introduction

Wireless technologies and services based on these technologies have been spreading rapidly in recent years: coverage of 4G networks increases, 5G technologies are being developed, local area networks are advancing and wireless network at home, workplace and public places is a necessity. The number of Internet of Things (IoT) devices and personal wireless gadgets is rapidly growing. Also, Internet of Vehicles (IoV) and intelligent transport system technologies are emerging. As reports show, wireless standards for IoT and IoV applications, similarly to most of other current and developing wireless standards, are using frequency bands, which are spread from hundreds of megahertzes up to 6 GHz [1,2,3,4].

In order to support the multitude of these frequency bands and standards in a single device, integrated circuits (IC) of multiband wireless transceivers are used. Such transceivers are also used in software defined radio, which is becoming more popular in the light of fast developing wireless technologies due to one of its main ideas—the usage of the same hardware for the implementation of different wireless standards, which enables a fast adaptation of the existing equipment to new and developing technologies while reducing the price of the system [3].

One of the main blocks of a multiband transceiver is a high tuning range frequency synthesiser, used as local high frequency signal oscillator. Phase locked loop is usually used as a frequency synthesiser and there are two main classes of phase-locked loops: conventional (charge-pump) phase locked loop and all-digital phase-locked loop.

To save power, chip area and cost, newer integrated circuit manufacturing technologies are being used. But the implementation of the conventional frequency synthesiser, which is analog in most part, in nanometric technologies is becoming more complicated because it is difficult to ensure the parameters of the synthesiser for wireless applications (e.g. operating frequency, frequency tuning range, phase noise level) due to decreasing supply voltage, increasing leakage currents as complementary metal–oxide–semiconductor (CMOS) technology step decreases. Therefore, integrated circuits of all-digital frequency synthesisers are gaining more attention, because these synthesisers, due to their digital nature, don’t have the flaws typical of conventional synthesisers.

However, some of the currently most advanced integrated circuits of multiband transceivers are still using conventional frequency synthesisers [5,6,7,8] and are implemented in technologies no smaller than 65 nm. New commercial transceivers have been introduced in 28–7 nm technologies [9], but due to the small amount of publicly available technical data, it can only be concluded that they have a limited application scope and have a smaller frequency tuning range, compared to transceivers, which are implemented in more mature technology nodes. This shows that structures of the all-digital frequency synthesiser, their constituting blocks and their models are not sufficiently researched and described. Also, there is a lack of research regarding parameter estimations of all-digital frequency synthesisers and their main blocks, especially for applications in the fields of IoT and IoV.

Therefore, the aim of this work is to present a structure of the all-digital frequency synthesiser for multiband transceiver for IoT and IoV applications that is suitable for implementation in nanometric and submicron technology nodes: the model of s-domain all-digital synthesiser is discussed, noise sources of the frequency synthesiser and contribution of main blocks to overall phase noise level of the synthesiser are analysed, requirements for main blocks are defined and a structure of synthesisers, which meets defined requirements, is proposed.

2. Phase Noise in All-Digital Frequency Synthesisers

The main parameter of the frequency synthesiser is phase noise, which describes the spectral purity of an output signal. Therefore, requirements for main blocks of frequency synthesiser will be defined based on phase noise requirements. In this chapter noise sources of all-digital frequency synthesiser will be discussed through the s-domain model.

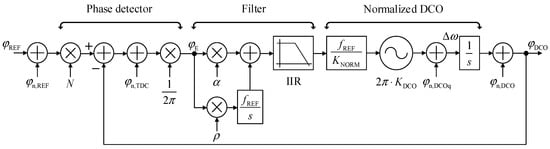

A model of an all-digital frequency synthesiser with included noise sources in the s-domain is shown in Figure 1 [10,11]. The main blocks are a phase detector, digitally controlled oscillator (DCO) and filter. The main part of phase detector is a time to digital converter (TDC), which measures time intervals between edges of reference and DCO signals.

Figure 1.

s-domain model of a higher order type-II all digital frequency synthesiser with noise sources.

There are two integrators (DCO and integrating path in the filter) and there are additional stages of infinite impulse response (IIR) filters in this model. Therefore, it is a type-II higher order frequency synthesiser. The main advantage of a type-II structure over type-I is better noise filtering capabilities, but it has worse dynamic characteristics than type-I. Therefore, there should be an ability to change the type of the synthesiser: type-I should be used for fast initial frequency acquisition and type-II is used for precise phase (and frequency) tracking. Type-I structure can be made by eliminating the integrator—setting the filter’s proportional gain coefficient ρ to 0.

There are three main phase noise sources: the noise of the reference signal (φn,REF in Figure 1), TDC (φn,TDC in Figure 1) and DCO. Noise induced by DCO has two components: quantisation noise (φn,DCOq in Figure 1) and oscillator’s noise (φn,DCO in Figure 1).

TDC creates quantization noise, which depends on the TDC’s resolution tres, DCO’s frequency fDCO and the frequency of reference signal fREF. Its single-sided power spectral density is shown in (1) equation [12].

Spectral density of noise of reference signal and oscillator’s component of DCO’s noise can be defined by the common equation of oscillator’s phase noise [13]:

where k0, k1, k2, k3, k4 are coefficients, describing the individual oscillator and f—frequency offset from carrier.

Quantization component of noise induced by DCO usually is reduced by using ΔΣ dithering and noise shaping techniques. Single sided power spectral density of DCO’s quantisation noise after ΔΣ shaping is [14]:

here q(f) is the quantization noise component, ΔΣs(f) is the ΔΣ noise shaping component, ΔfRES— the tuning step of DCO’s frequency, fREF—frequency of reference signal, fΔΣ—frequency of ΔΣ dithering, f—frequency offset from carrier, WΔΣ—bit count of ΔΣ modulator, and n—order of ΔΣ modulator.

As is seen from Equations (1) and (3), the quantization noise of TDC and DCO decreases with increased reference frequency and ΔΣ dithering frequency (in case of DCO). But increasing these frequencies will also increase power consumption of the system, which is undesirable in IoT and IoV applications. Therefore, there is present a classical task of searching for compromise between quantization noise and power consumption.

Total frequency synthesiser’s phase noise can be defined as [11]:

where Hcl,REF, Hcl,TDC, Hcl,DCO, are respectively closed-loop transfer functions of reference signal noise, TDC quantization noise and oscillator’s component of DCO noise, whose s-domain representations are shown in Equations (5)–(7) [15]. Expression of ΔΣ quantization noise, shown in Equation (3) takes into account its noise transfer function, therefore it is not multiplied by the power transfer function in Equation (4).

Hol in Equations (5)–(7) are open loop transfer functions of the type-II higher order frequency synthesiser. If four additional IIR filters are used in the structure of the synthesiser, it is defined by Equation (8).

here α and ρ are respectively proportional and integral gain of the synthesiser’s filter and λi is the transfer coefficient of each IIR filter stage.

Transition from s-domain to linear frequency can be made by using s = j2πf substitution.

3. Requirements for Blocks of All-Digital Multiband Frequency Synthesiser

In order to evaluate the impact of main blocks on noise performance of the frequency synthesiser, the total phase noise of the synthesiser will be calculated by using (4) equation.

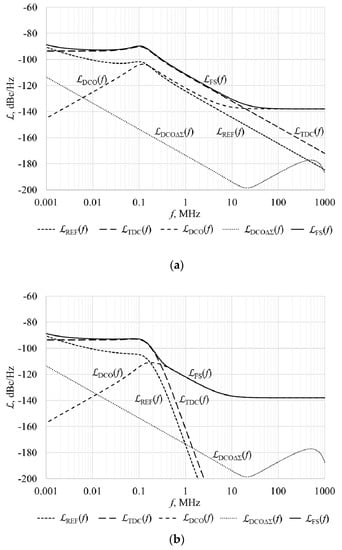

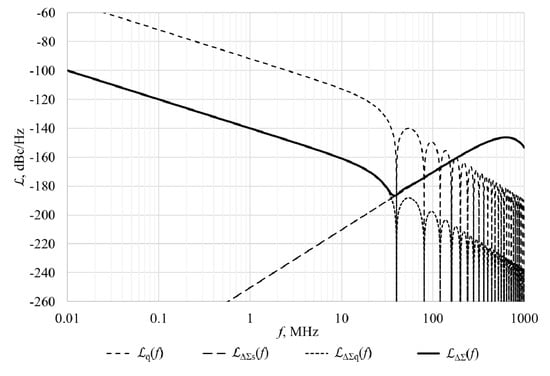

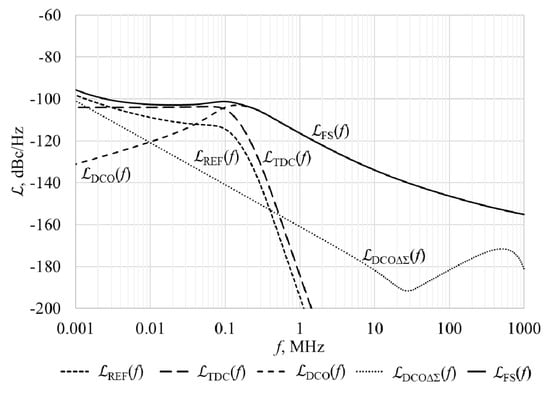

Calculation results of phase noise and its components of type-II frequency synthesiser are shown in Figure 2. Total phase noise of frequency synthesiser is marked as FS(f), phase noise induced by reference signal is marked as REF(f), phase noise induced by TDC is marked as TDC(f), the oscillator’s component of DCO’s phase noise is marked as DCO(f), DCO’s quantization and ΔΣ shaping noise is marked as DCOΔΣ(f). Parameters provided in references [16,17] were used to carry out these calculations: the operating frequency of the DCO is equal to 5.38 GHz, the frequency of the reference signal is 48 MHz, the frequency tuning step is 26 kHz, the ΔΣ modulator controls 9 bits. The ΔΣ dithering frequency and order of ΔΣ modulator are not provided, therefore we assume that the ΔΣ dithering frequency is equal to the DCO’s frequency divided by 4, and the order of the ΔΣ modulator is 2nd. Phase noise of the reference signal and oscillator’s component of DCO’s noise are approximated respectively by Equations (9) and (10).

Figure 2.

Calculated phase noise and its components of an all digital frequency synthesiser, when fDCO = 5.38 GHz, fREF = 48 MHz, fΔΣ = fDCO/4, ΔfRES = 26 kHz, W = 9, n = 2 with two filter configurations: (a) α = 2−6, ρ = 2−12; (b) α = 2−6, ρ = 2−10, λ1 = λ2 = λ3 = λ4 = 2−5.

Configuration of the filter is not provided in reference [16], therefore two configurations of the filter were considered. First configuration is made of only proportional and integral parts, with proportional and integral coefficients respectively set to α = 2−6 and ρ = 2−12. This corresponds to the filter’s configuration for a type-II frequency synthesiser. Results of calculations for this configuration are shown in Figure 2a. For the second configuration it is assumed that the filter is composed of proportional and integral gain paths and four first-order stages of IIR filter. Such configuration corresponds to filter’s structure for the type-II higher order frequency synthesiser. Coefficients of proportional and integral paths are set respectively to α = 2−6 and ρ = 2−10. Transfer coefficients of all stages of IIR filters are equal and set to λ1 = λ2 = λ3 = λ4 = 2−5. Results of calculations for the second configuration of the filter is shown in Figure 2b.

It is seen from both cases shown in Figure 2 that noise induced by TDC dominates at low frequency offsets from the carrier (in-band) and noise induced by DCO dominates at high frequency offsets from the carrier (out-of-band). Also, it is seen that the higher order synthesiser’s filter enables more precise control of the synthesiser’s passband and has better noise-filtering capabilities: in the case of the first configuration (Figure 2a), noise induced by TDC has a high impact on total phase noise up to 10 MHz frequency offset, while in the second configuration (Figure 2b), noise of reference signal and noise of TDC is highly attenuated outside of the synthesiser’s passband and DCO’s noise clearly dominates out-of-band. Therefore, it is important to have a reprogrammable filter, to control the synthesiser’s frequency response and noise filtering capabilities.

Since noise induced by TDC and DCO’s noise have separate dominance ranges, the requirements of phase noise performance for the frequency synthesiser can be transformed to the requirements for TDC and DCO.

As mentioned in the first chapter, reports and analysis of current and developing standards, which are used for IoT, IoV and other wireless applications, use frequency bands from hundreds of megahertz up to 6 GHz. Also, from the technical documentation of some of most the advanced multiband transceivers presently available [5,6,7,8], it is seen that in-band phase noise should be better than −90 dBc/Hz and out-of-band phase noise should be better than −120 dBc/Hz.

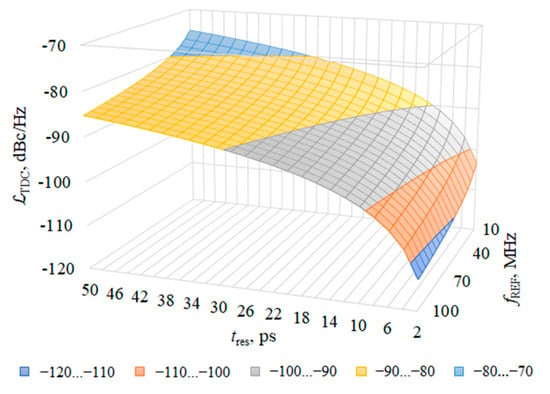

From Equation (1) it is seen that noise induced by TDC depends on the resolution of TDC, operating frequency of DCO and frequency of the reference signal. It deteriorates with a higher frequency of DCO, therefore, for theoretical calculations, the highest needed frequency should be used, i.e., 6 GHz. Calculated noise, induced by TDC, when frequency of digitally controlled oscillator is 6 GHz, frequency of reference signal ranges from 10 MHz to 100 MHz and resolution of TDC ranges from 2 ps to 50 ps is shown in Figure 3. As can be seen, the resolution of TDC has to be better than 12 ps to satisfy the in-band noise requirement of −90 dBc/Hz. If resolution of TDC is 4 ps, a better than −100 dBc/Hz in-band noise can be achieved.

Figure 3.

Calculated phase noise induced by time to digital converter, when frequency of digitally controlled oscillator’s output signal is 6 GHz, frequency of reference signal is 10–100 MHz, resolution of time to digital converter is 2–50 ps.

Oscillator’s component of the DCO’s noise depends on properties of the resonant tank. Usually LC tank oscillators are used to achieve low phase noise. LC tank DCOs and the oscillator’s component of DCO noise are widely researched and discussed [18,19,20], therefore, here the focus will be on the quantization component of DCO noise.

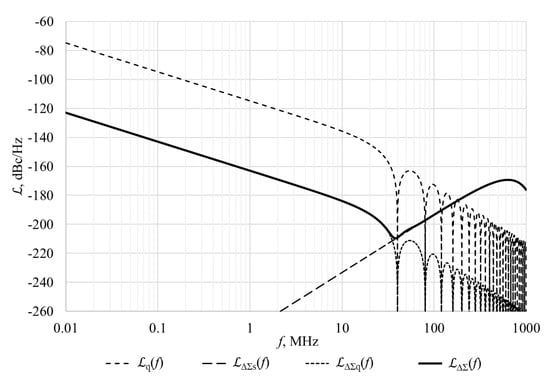

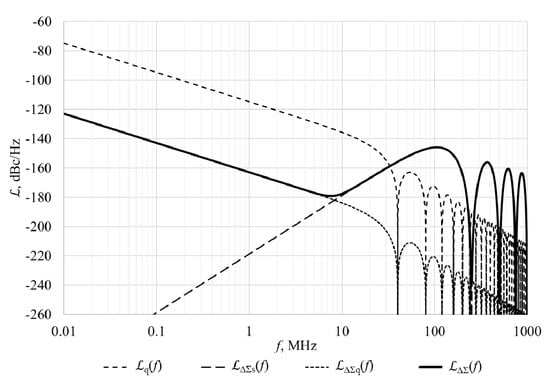

Figure 4 shows DCO’s quantization and ΔΣ shaping noise and its components, which are calculated by using Equation (3). The following parameters were used: DCO’s frequency fDCO is equal to 6 GHz, frequency of reference signal fREF is 40 MHz, ΔΣ dithering frequency fΔΣ is equal to divided-by-4 DCO’s frequency, DCO’s frequency tuning step ΔfRES is 50 kHz, ΔΣ modulator controls 8 bits and order of ΔΣ modulator is 3. Total DCO’s quantization and ΔΣ shaping noise is marked as ΔΣ(f), DCO’s quantization noise without ΔΣ modulator is marked as q(f), DCO’s quantization noise with ΔΣ modulator is marked as ΔΣq(f), and ΔΣ noise shaping component is marked as ΔΣs(f).

Figure 4.

Calculated phase noise and its components, induced by quantization of digitally controlled oscillator, when fDCO = 6 GHz, fREF = 40 MHz, fΔΣ = fDCO/4, ΔfRES = 40 kHz, W = 8, n = 3.

It can be seen from Figure 4 that ΔΣ quantization and noise shaping improves DCO’s quantization noise by more than 40 dBc/Hz at small frequency offsets from the carrier (in-band). In this range, according to Equation (3), noise depends on the frequency of the reference signal and ΔfRES/2W ratio. This ratio shows that increasing the ΔΣ modulator’s bit count by one bit corresponds to reduction of frequency tuning step by half. In-band DCO’s quantization noise will not be filtered by the synthesiser, therefore it should not exceed the noise induced by TDC. In order for DCO’s quantization noise to not exceed −100 dBc/Hz, when frequency of reference signal is 40 MHz, ratio of ΔfRES/2W should not exceed 2190 Hz, i.e., equivalent frequency tuning step after ΔΣ quantization should not exceed this value. Such a case, when the raw frequency tuning step (without ΔΣ dithering) is increased to 560.64 kHz and all other parameters are the same as in previous case, is shown in Figure 5. But it should be noted, that even in sub-micron technologies, a frequency tuning step close to 10 kHz is achievable [14,21,22,23]. Therefore, the requirement of ΔfRES/2W ratio is relatively easy to meet.

Figure 5.

Calculated phase noise and its components, induced by quantization of digitally controlled oscillator, when fDCO = 6 GHz, fREF = 40 MHz, fΔΣ = fDCO/4, ΔfRES = 560.64 kHz, W = 8, n = 3.

ΔΣ shaping noise dominates at high frequency offset from the carrier (out-of-band). This noise component increases when the frequency of DCO’s output signal decreases, because being together decreases ΔΣ dithering frequency. The case of ΔΣ quantization and shaping noise, when frequency of the DCO signal is decreased to 1 GHz and all other parameters are the same as in first case (shown in Figure 4) is shown in Figure 6. In this case the maximum of ΔΣ shaping noise increased by 23 dB/Hz and this maximum moved towards lower frequency offsets, but it is still out of frequency synthesiser’s passband. This noise component has to be lower than the oscillator’s component of DCO’s noise.

Figure 6.

Calculated phase noise and its components, induced by quantization of digitally controlled oscillator, when fDCO = 1 GHz, fREF = 40 MHz, fΔΣ = fDCO/4, ΔfRES = 40 kHz, W = 8, n = 3.

Another property of DCO for multiband frequency synthesiser for IoT and IoV applications, besides phase noise performance, is the tuning range. As mentioned above, the frequency of synthesisers output signal has to range from hundreds of megahertzes up to 6 GHz. But frequency of the DCO does not have to be tuneable in whole range—frequency range can be extended by using frequency dividers, such as in reference [24]. Therefore, we will assume that for multiband applications, the tuning range of DCO has to be at least 1 GHz.

According to the discussion in this and previous chapters, requirements for main blocks of an all-digital multiband frequency synthesiser for IoT and IoV applications can be defined:

- the resolution of TDC must be better than 12 ps to ensure a phase noise of less than −90 dBc/Hz when frequency of DCO’s signal is 6 GHz;

- the out-of-band phase noise of frequency synthesiser is dominated by noise induced by DCO, therefore its phase noise in this region has to be less than −120 dBc/Hz;

- total DCO’s quantization and ΔΣ shaping noise has to be lower than noise induced by TDC in synthesiser’s passband and oscillator’s component of DCO’s noise;

- the frequency tuning range of the DCO has to be wide (at least 1 GHz);

- the digital synthesiser’s filter should consist of a proportional and integral gain parts and additional IIR filters in order to change the type and order of the frequency synthesiser and be able to precisely control the bandwidth of the synthesiser.

4. All-Digital Frequency Synthesiser for Multiband Transceivers

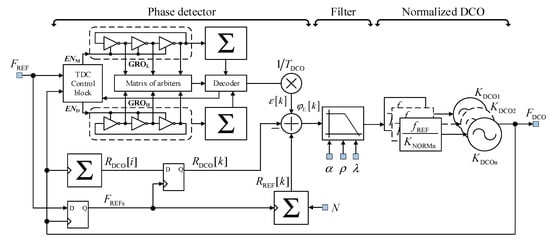

The structure of all-digital synthesiser for the multiband wireless transceiver, which meets the requirements defined in the previous chapter, is suitable for IoV and IoT applications shown in Figure 7. This structure is based on structure which is presented in reference [25], but is modified for a wide tuning range of output signal and ensures high resolution of TDC.

Figure 7.

Phase domain model of all digital frequency synthesiser for multiband transceiver.

Wide tuning range is achieved by using multicore DCO. In this structure it is shown as multiple parallel-connected DCOs, because in the general case, there can be n DCO cores used in synthesisers, but simultaneously only one core is operating. Each core has its own normalisation coefficient KDCOn, therefore, general DCO’s normalisation coefficient is a set of coefficients of each core KDCO = {KDCO1, KDCO2, ..., KDCOn}. Each core is normalised individually, therefore there are n normalisation blocks. The purpose of normalisation is to eliminate the transfer coefficient of the DCO (KDCO) and make a tuning of DCO linear—if transfer coefficient of the DCO is estimated correctly (i.e., normalisation transfer coefficient KNORM is equal to KDCO and ratio KDCO/KNORM = 1), due to normalisation, change of one bit of integer oscillator tuning word (LSB) changes the output frequency of DCO by fREF hertz.

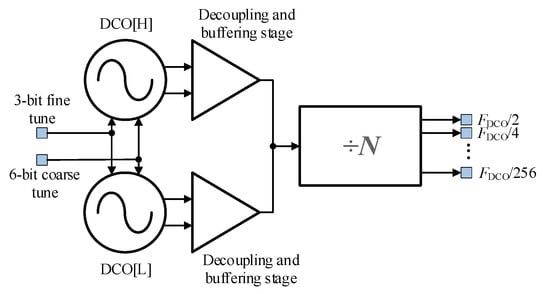

Physical implementation of multicore DCO in 0.18 μm CMOS technology is presented in our previous work [26] and shown in Figure 8. It made of two LC tank DCO cores, decoupling stage, differential to single ended converter, tri-state buffers and frequency divider. It is a partial case of a multicore oscillator, where two DCO cores are used, but this structure is scalable to use different a number of cores to satisfy operating frequency and tuning range requirements. However, the penalty of adding more cores is a rapidly increasing area of silicon.

Figure 8.

Structure of 5 GHz LC digitally controlled oscillator.

Both cores of LC DCO have the same configuration. Main components of the DCO are a high-quality factor inductor, negative impedance cross-coupled transistor pair and two switched-capacitor arrays. Frequency of DCO is tuned by using 6-bit coarse tuning and 3-bit fine tuning binary words. Together with DCO frequency divider it is used to increase available frequency values. A divider is made of eight divide-by-2 cells connected in a daisy chain, thus division values range from 2 to 256.

In this partial case 4.3–5.4 GHz frequency tuning range of DCO is achieved. When the highest operating frequency is set, phase noise at output of DCO is −116.4 dBc/Hz at 1 MHz offset from 5.44 GHz carrier and −134.0 dBc/Hz at 10 MHz offset from 5.44 GHz carrier. When working at the lowest frequency, phase noise at output of DCO is −117.6 dBc/Hz at 1 MHz offset from 4.3 GHz carrier and −138.0 dBc/Hz at 10 MHz offset from 5.44 GHz carrier.

Oscillator’s component of this DCO’s phase noise can be approximated by following equation:

Without tuning nonlinearity, mentioned above and alleviated by normalisation of DCO, there are capacitance mismatches in tuning banks, common to all DCOs. Ideally, all unit-weighted capacitors have same capacitance values. But in reality, these values will vary. If the synthesiser is in frequency tracking mode, these capacitors will be constantly switching on/off and due to variation of capacitance, output frequency will also vary—it will be slightly different from expected frequency and will degrade phase noise performance. One of the basic techniques to alleviate such mismatches is dynamic element matching (DEM) [14,15]. The main idea of DEM is to dynamically rearrange (e.g. cyclically shift within switched-capacitor bank) unit-weighted mismatched components, so that averaged in time equivalent values of these components would be equal.

From the discussion in chapters 2 and 3 it is seen that quantisation noise of the TDC depends on delay of the inverter. Actually, delay of the inverter is equal to the resolution of the commonly used TDC, which is based on the inverter delay line. This delay can be reduced by increasing its driving strength, together with increasing its power consumption. Table 1 shows modelling results of inverter’s delay (τinv) in 65 nm CMOS technology at different load capacitance (CL) and ratio of width and length (Wn/L) of used transistors. Length of all transistors was set to the minimum value in current technology (60 nm) and width of NMOS transistors (Wn) was set to 4, 8 and 16 μm. Width of PMOS transistor is always set to double of NMOS, i.e., Wp = 2Wn.

Table 1.

Modeling results of dependency of inverter’s delay time on load capacitance and ratio of width and length of transistors in 65 nm CMOS technology.

It is seen from Table 1 that even when greatly increasing the driving strength of an inverter, it remains challenging to achieve lower than 12 ps delay of an inverter. It is obvious that other negative results of such an approach are a rapidly increasing used area of silicon. Therefore, the more advanced structure of TDC should be used.

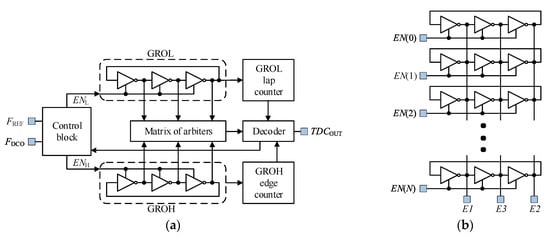

High resolution of TDC is achieved by using 2D Vernier TDC based on gated ring oscillators, which was presented in our previous works [27,28] and shown in Figure 9a. Such TDC allows us to measure the time interval, which is lower than delay of the inverter. Main blocks of this TDCs are two gated ring oscillators, which are used as infinite delay lines, lap and edge counters of both oscillators, matrix of arbiters, control block and output decoder. The resolution of such TDC is defined as difference of delay of stages from which two oscillators are made. To have the ability to control the resolution of TDC, stage delay of oscillator (and its corresponding oscillation frequency) should also be controllable. For this reason, each oscillator is made of parallel-connected oscillator sections, as shown in Figure 9b. Stage delay is decreasing when additional sections of the oscillator are enabled.

Figure 9.

(a) Structure of proposed 2D Vernier time to digital converter based on gated ring oscillators. GROL—lower frequency oscillator, GROH—higher frequency oscillator; (b) Structure of gated ring oscillators used in TDC.

At the beginning of the measurement, TDC is waiting for the rising edge of the reference signal. When it is received, the lower frequency gated ring oscillator and its lap counter are started. After that TDC is waiting for the rising edge of the DCO signal. When it is received, the state of lower frequency oscillator is saved, and the higher frequency oscillator and its edge counter are started. When both oscillators are started, the output signals of arbiters are monitored. When the output of any arbiter changes to a high level, it means that the higher frequency oscillator has caught up with the lower frequency oscillator. The position of that arbiter is located and depending on that position, the output signal of TDC is decoded. After that, all counters are reset and the TDC waits for another pair of the input signals for a new measurement.

As shown in reference [28], a TDC employing such a structure can be synthesised in various technology nodes. It was implemented in 65 nm and 0.13 µm CMOS technologies and resolutions close to 1 ps can be achieved in both technologies, which exceeds our requirements by 12 times. However, to achieve resolutions close to 1 ps, more stages of the gated ring oscillator should be turned on, which increases power consumption. Therefore, high resolution should be used only when it is needed.

Similar mismatches to those in the DCO’s tuning banks occur in the synthesised ring oscillators which are used in TDC. All delay cells (tri-state inverters), which are used to compose ring oscillators, are the same. However, due to their irregular location and wiring after automatic place and route, these cells have different effective driving strengths, which results in different stage delays.

However, despite the mismatch in stage delay, ring oscillator periods, which are utilized in calculations of the TDC’s output, are consistent during measurement. Also, the resolution of such TDC depends on the difference between stage-delay of higher and lower frequency oscillators and not on absolute value of stage delay (delay mismatch usually is much lower than stage-delay). Therefore, this structure is less susceptible to delay mismatch compared to TDC based on delay lines.

Although these mismatches in TDC stage delay are generally undesirable, they can be used to fine tune resolution of TDC based on ring oscillators. A TDC calibration technique which takes advantage of the place and route irregularity is presented in reference [29]. This mechanism sorts used delay elements by driving strength and uses this information to achieve a different oscillation frequency (and corresponding stage delay) with same number of enabled sections of ring oscillators, i.e., same number of the parallel-connected sections will result in a different stage delay, depending on the position in chip layout of the sections.

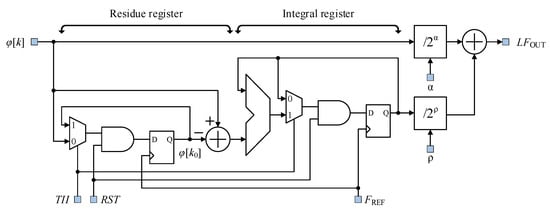

As mentioned earlier, the filter of frequency synthesiser has the important role of controlling the synthesiser’s dynamic characteristics and noise filtering. However, it gets little attention in publications related to frequency synthesisers [30,31,32]. Often it is only stated that there is a filter in the structure, without further elaboration. Filters, suitable for IoT and IoV applications in multiband frequency synthesisers can be based on structure from references [33,34]. Its main proportional-integral part is shown in Figure 10. Additional cascaded IIR filter stages can be used to form a higher order filter.

Figure 10.

Structure of filter for type-II frequency synthesiser.

Proportional and integral paths can be reconfigured by changing their gain coefficients, respectively α and ρ. Gain stages are implemented as right-shift registers. The type of synthesiser (from type-I to type-II and vice versa) that is controlled by signal TII—integral paths activates only when it is set to a high logic level. If four additional IIR filter stages are used, such a filter enables changing the synthesiser order from first to sixth.

The most power-hungry blocks in a proposed structure of frequency synthesiser are DCO and TDC. Power consumption of the presented DCO core is 18 mW, while the power consumption of TDC is 3,6 mW. All other circuitry is low-power and operates at a relatively low reference frequency. Therefore, we will estimate 50% of sum of DCO and TDC power consumption i.e., 10.8 mW. Total power consumption is 32.4 mW.

Calculated achievable phase noise and its components of all digital frequency synthesiser, when presented time to digital converter and digitally controlled oscillator are used is shown in Figure 11. The maximal frequency of designed DCO, which is equal to 5.44 GHz, was used for calculations. Also, it is assumed that frequency tuning step is 50 kHz, frequency of reference signal is 40 MHz, ΔΣ dithering frequency is equal to divided-by-4 DCO’s frequency, ΔΣ modulator controls 8 bits and order of ΔΣ modulator is 2. Also, the resolution of TDC is set to 4 ps and filter’s coefficients are α = 2−7, ρ = 2−10, λ0 = λ1 = λ2 = λ3 = 2−5.

Figure 11.

Calculated achievable phase noise and its components of frequency synthesiser, when presented time to digital converter, digitally controlled oscillator and synthesiser’s filter are used.

Noise of reference signal was approximated by following equation, derived from data of crystal oscillator [35]:

It is seen from Figure 11 that the synthesiser’s in-band phase noise is lower than −100 dBc/Hz. Out-of-band phase noise corresponds to the oscillator’s component of the DCO’s phase noise and is equal to −116.4 dBc/Hz and −134.0 dBc/Hz respectively at 1 MHz and 10 MHz offset from 5.44 GHz carrier. Out-of-band ΔΣ dithering noise is about 20 dBc/Hz lower than the DCO’s noise. As can be seen, the presented blocks of the synthesiser meet the defined requirements.

Comparison of calculated parameters of frequency synthesisers to other works is shown in Table 2. Here Fmin, Fmax—maximum and minimum operating frequency, Foff, Fc—frequency offset and carrier frequency at which phase noise is provided, {Foff}—phase noise, P—power consumption.

Table 2.

Comparison of calculated parameters of frequency synthesisers to other works.

5. Conclusions

There are three main phase noise sources in all-digital frequency synthesisers: noise of reference signal, TDC and DCO. Noise induced by DCO has two components: quantisation noise and oscillator’s noise.

Noise induced by TDC and DCO’s noise have separate dominance ranges—noise induced by TDC dominates at low frequency offsets from the carrier (in-band) and noise induced by DCO dominates at high frequency offsets from the carrier (out-of-band). Therefore, requirements of phase noise performance for frequency synthesisers can be transformed into the requirements for TDC and DCO.

The structure of the all-digital frequency synthesiser for wireless transceivers for IoT and IoV applications, suitable for implementation in nanometric and submicron CMOS technologies, has to be made of TDC whose resolution has to be lower than 12 ps to ensure a lower than −90 dBc/Hz in-band phase noise when the frequency of the DCO’s signal is 6 GHz; DCO whose frequency tuning range is at least 1 GHz and its out-of-band phase noise is lower than −120 dBc/Hz; and digital filter which enables to change the type and order of frequency synthesiser to be able to precisely control the bandwidth of the synthesiser.

A wide tuning range is achieved by using multicore DCO, which is made of multiple LC tank DCO cores, decoupling stages, differential to single ended converter, tri-state buffers and frequency dividers. Such a structure is scalable and different number of cores can be used to satisfy operating frequency and tuning range requirements. However, the penalty of adding more cores is a rapidly increasing area of silicon. With partial case in 0.18 μm CMOS technology, when only two DCO cores are used, the tuning range is 4.3–5.4 GHz and the phase noise is −116.4 dBc/Hz and −134 dBc/Hz at respectively 1 MHz and 10 MHz offset from the 5.44 GHz carrier.

High resolution of TDC is achieved by using 2D Vernier TDC based on gated ring oscillators, which can measure time interval, with a lower delay than inverters. The main blocks of this TDCs are two gated ring oscillators, which are used as infinite delay lines, lap and edge counters of both oscillators, matrix of arbiters, control block and output decoder. Close to 1 ps resolution of such TDC can be achieved when it is synthesised in 65 nm and 0.13 μm CMOS technologies.

Digital filters made of a proportional and integral gain parts and additional IIR filters should be used in multiband synthesisers for IoT and IoV applications. If four stages of IIR filter are used, such a filter allows us to set a synthesiser to type-I or type-II and change its order from first to sixth.

The proposed structure with presented blocks of frequency synthesiser allows us to achieve a synthesiser’s in-band phase noise of lower than −100 dBc/Hz, an out-of-band phase noise equal to −134.0 dBc/Hz, allows us to set a synthesiser to type-I or type-II, and to change its order from first to sixth.

Author Contributions

All authors contributed to the present paper with the same effort in finding available literature resources, conducting both simulations and measurements, as well as writing the paper.

Funding

This research was funded by the Research Council of Lithuania grant number DOTSUT-235, No. 01.2.2-LMT-K-718-01-0054 as a part of “Design and Research of Internet of Things (IoT) Framework Model and Tools for Intelligent Transport Systems” project. The APC was funded by Vilnius Gediminas technical university Faculty of Electronics.

Acknowledgments

The authors would like to thank the Research Council of Lithuania and the project “Design and Research of Internet of Things (IoT) Framework Model and Tools for Intelligent Transport Systems” team for support.

Conflicts of Interest

The authors declare no conflict of interest.

References

- Yole From Technologies to Market. 5G’s Impact on RF Front-End Industry: How Will Wireless Infrastructure and Cell Phone Terminals Change in the Next Decade? Available online: https://www.slideshare.net/Yole_Developpement/5gs-impact-on-rf-frontend-industry-how-will-wireless-infrastructure-and-cell-phone-terminals-change-in-the-next-decade-2017-report-by-yole-developpement (accessed on 7 May 2018).

- Nokia Pte Ltd Singapore; Thailand, E.; Vietnam, E.; Kong, Q.H. Status Update on 3GPP LTE V2X Standards and Proposed Modifications to the Working Document toward Revision of APT Report on “The Usage of its in APT Countries”. Available online: https://www.apt.int/sites/default/files/2017/03/AWG-21-INP-42_LTE_V2X_modification_to_AWG-20-TMP-44_ITS_USAGE_Nokia.docx (accessed on 16 May 2018).

- Kiela, K. Integrinių Analoginių Filtrų Belaidžio Ryšio Sistemoms Kūrimas. Ph.D. Thesis, Vilnius Gediminas Technical University, Vilnius, Lithuania, 2017. [Google Scholar]

- Vasjanov, A.; Barzdenas, V. A Review of Advanced CMOS RF Power Amplifier Architecture Trends for Low Power 5G Wireless Networks. Electronics 2018, 7, 271. [Google Scholar] [CrossRef]

- McLaurin, D.J.; Gard, K.G.; Schubert, R.P.; Manglani, M.J.; Zhu, H.; Alldred, D.; Li, Z.; Bal, S.R.; Fan, J.; Gysel, O.E.; et al. A highly reconfigurable 65 nm CMOS RF-to-bits transceiver for full-band multicarrier TDD/FDD 2G/3G/4G/5G macro basestations. In Proceedings of the 2018 IEEE International Solid - State Circuits Conference—(ISSCC), San Francisco, CA, USA, 11–15 February 2018; pp. 162–164. [Google Scholar]

- Analog Devices Integrated, Dual RF Transceiver with Observation Path AD9375. Available online: http://www.analog.com/en/products/rf-microwave/integrated-transceivers-transmitters-receivers/wideband-transceivers-ic/ad9375.html?doc=AD9375.pdf (accessed on 7 May 2018).

- Analog Devices RF Agile Transceiver AD9361. Available online: http://www.analog.com/media/en/technical-documentation/data-sheets/AD9361.pdf (accessed on 7 May 2018).

- Lime Microsystems FPRF MIMO Transceiver IC with Integrated Microcontroller LMS7002M. Available online: http://www.limemicro.com/wp-content/uploads/2015/09/LMS7002M-Data-Sheet-v2.8.0.pdf (accessed on 7 May 2018).

- Qualcomm Snapdragon LTE Modems. Available online: https://www.qualcomm.com/snapdragon/modems/comparison (accessed on 7 May 2018).

- Staszewski, R.B.; Waheed, K.; Vemulapalli, S.; Dulger, F.; Wallberg, J.; Hung, C.M.; Eliezer, O. Spur-free all-digital PLL in 65 nm for mobile phones. In Proceedings of the 2011 IEEE International Solid-State Circuits Conference 2011, San Francisco, CA, USA, 20–24 February 2011; pp. 52–53. [Google Scholar] [CrossRef]

- Mendel, S.; Vogel, C. A z-domain model and analysis of phase-domain all-digital phase-locked loops. In Proceedings of the 25th Norchip Conference, Aalborg, Denmark, 19–20 November 2007. [Google Scholar] [CrossRef]

- Staszewski, R.B.; Vemulapalli, S.; Vallur, P.; Wallberg, J.; Balsara, P.T. Time-to-digital converter for RF frequency synthesis in 90 nm CMOS. In Proceedings of the IEEE Radio Frequency integrated Circuits (RFIC) Symposium—Digest of Papers, Long Beach, CA, USA, 12–14 June 2005; pp. 473–476. [Google Scholar]

- Gardner, F. Phaselock Techniques, 3rd ed.; John Wiley & Sons: New York, NY, USA, 2005; ISBN 978-0-471-43063-6. [Google Scholar]

- Staszewski, R.B.; Hung, C.M.; Barton, N.; Lee, M.-C.; Leipold, D. A digitally controlled oscillator in a 90 nm digital CMOS process for mobile phones. IEEE J. Solid State Circuits 2005, 40, 2203–2211. [Google Scholar] [CrossRef]

- Staszewski, R.B.; Balsara, P.T. All-Digital Frequency Synthesizer in Deep-Submicron CMOS; John Wiley & Sons, Inc.: Hoboken, NJ, USA, 2006; Volume 2003, ISBN 9780470041956. [Google Scholar]

- Pavlovic, N.; Bergervoet, J. A 5.3GHz digital-to-time-converter-based fractional-N all-digital PLL. In Proceedings of the 2011 IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 20–24 February 2011; Volume 44, pp. 54–56. [Google Scholar]

- Jiang, B.; Xia, T. ADPLL design parameters determinations through noise modeling. Integration 2015, 48, 138–145. [Google Scholar] [CrossRef]

- Macaitis, V.; Navickas, R. CMOS technology based LC VCO review. In Proceedings of the 2015 Open Conference of Electrical, Electronic and Information Sciences (eStream), Vilnius, Lithuania, 21 April 2015; pp. 1–4. [Google Scholar]

- Devos, A.; Vigilante, M.; Reynaert, P. Multiphase digitally controlled oscillator for future 5G phased arrays in 90 nm CMOS. In Proceedings of the 2016 IEEE Nordic Circuits and Systems Conference (NORCAS), Copenhagen, Denmark, 1–2 November 2016; pp. 1–4. [Google Scholar]

- Macaitis, V.; Navickas, R. Comparison of LC-VCO and LC-DCO parameters in 65 nm CMOS technology. In Proceedings of the 2017 5th IEEE Workshop on Advances in Information, Electronic and Electrical Engineering (AIEEE), Riga, Latvia, 24–25 November 2017; pp. 5–8. [Google Scholar]

- Maurath, D.; Tavakoli, A.R.; Vehring, S.; Scholz, P.; Ding, Y.; Boeck, G.; Gerfers, F. A low-phase noise 12 GHz digitally controlled oscillator in 65 nm CMOS for a FMCW radar frequency synthesizer. In Proceedings of the 2017 12th European Microwave Integrated Circuits Conference (EuMIC), Nuremberg, Germany, 8–10 October 2017; pp. 232–235. [Google Scholar]

- Huang, Z.; Luong, H.C. Design and Analysis of Millimeter-Wave Digitally Controlled Oscillators With C-2C Exponentially Scaling Switched-Capacitor Ladder. IEEE Trans. Circuits Syst. I 2017, 64, 1299–1307. [Google Scholar] [CrossRef]

- Huang, Z.; Luong, H.C. A dithering-less 54.79-to-63.16GHz DCO with 4-Hz frequency resolution using an exponentially-scaling C-2C switched-capacitor ladder. In Proceedings of the 2015 Symposium on VLSI Circuits (VLSI Circuits), Kyoto, Japan, 17–19 June 2015; pp. 234–235. [Google Scholar]

- Jurgo, M.; Kiela, K.; Navickas, R. Design of Low Noise 10 GHz divide by 16…511 Frequency Divider. Electron. Electr. Eng. 2013, 19, 87–90. [Google Scholar] [CrossRef]

- Staszewski, R.B.; Waheed, K.; Dulger, F.; Eliezer, O.E. Spur-Free Multirate All-Digital PLL for Mobile Phones in 65 nm CMOS. IEEE J. Solid State Circuits 2011, 46, 2904–2919. [Google Scholar] [CrossRef]

- Jurgo, M.; Navickas, R. Design of Gigahertz Tuning Range 5 GHz LC Digitally Controlled Oscillator in 0.18 μm CMOS. J. Electr. Eng. 2016, 67, 143–148. [Google Scholar] [CrossRef]

- Jurgo, M.; Navickas, R. Synthesizable 2D Vernier TDC based on gated ring oscillators. Inf. MIDEM 2017, 47, 223–231. [Google Scholar]

- Jurgo, M.; Navickas, R. Comparison of TDC parameters in 65 nm and 0.13 μm CMOS. In Proceedings of the 2017 5th IEEE Workshop on Advances in Information, Electronic and Electrical Engineering (AIEEE), Riga, Latvia, 24–25 November 2017; pp. 1–4. [Google Scholar]

- Park, Y.; Wentzloff, D.D. A cyclic vernier TDC for ADPLLs synthesized from a standard cell library. IEEE Trans. Circuits Syst. I 2011, 58, 1511–1517. [Google Scholar] [CrossRef]

- Wu, W.; Staszewski, R.B.; Long, J.R. A 56.4-to-63.4 GHz multi-rate all-digital fractional-N PLL for FMCW radar applications in 65 nm CMOS. IEEE J. Solid State Circuits 2014, 49, 1081–1096. [Google Scholar] [CrossRef]

- Yang, S.Y.; Chen, W.Z.; Lu, T.Y. A 7.1 mW, 10 GHz all digital frequency synthesizer with dynamically reconfigured digital loop filter in 90 nm CMOS technology. IEEE J. Solid State Circuits 2010, 45, 578–586. [Google Scholar] [CrossRef]

- Yin, W.; Inti, R.; Elshazly, A.; Young, B.; Hanumolu, P.K. A 0.7-to-3.5 GHz 0.6-to-2.8 mW highly digital phase-locked loop with bandwidth tracking. IEEE J. Solid State Circuits 2011, 46, 1870–1880. [Google Scholar] [CrossRef]

- Staszewski, R.B. State-of-the-art and future directions of high-performance all-digital frequency synthesis in nanometer CMOS. IEEE Trans. Circuits Syst. I 2011, 58, 1497–1510. [Google Scholar] [CrossRef]

- Wu, W.; Staszewski, R.B.; Long, J. Millimeter-Wave Digitally Intensive Frequency Generation in CMOS; Academic Press: Cambridge, MA, USA, 2015; ISBN 9780128022078. [Google Scholar]

- Rakon SMD Temperature Compensated Crystal Oscillator: RTX5032A. Available online: http://www.rakon.com/component/docman/doc_download/43-rtx5032a?Itemid= (accessed on 7 May 2018).

- Kuo, F.W.; Chen, R.; Yen, K.; Liao, H.Y.; Jou, C.P.; Hsueh, F.L.; Babaie, M.; Staszewski, R.B. A 12mW all-digital PLL based on class-F DCO for 4G phones in 28nm CMOS. In Proceedings of the 2014 Symposium on VLSI Circuits Digest of Technical Papers, Honolulu, HI, USA, 10–13 June 2014; pp. 1–2. [Google Scholar]

- Liu, Y.C.; Chen, W.Z.; Chou, M.H.; Tsai, T.H.; Lee, Y.W.; Yuan, M.S. A 0.1-3GHz cell-based fractional-N all digital phase-locked loop using ΔΣ noise-shaped phase detector. In Proceedings of the IEEE 2013 Custom Integrated Circuits Conference, San Jose, CA, USA, 22–25 September 2013. [Google Scholar]

- Ueda, K.; Uozumi, T.; Endo, R.; Nakamura, T.; Heima, T.; Sato, H. A digital PLL with two-step closed-locking for multi-mode/multi-band SAW-less transmitter. In Proceedings of the IEEE 2012 Custom Integrated Circuits Conference, San Jose, CA, USA, 9–12 September 2012; pp. 4–7. [Google Scholar] [CrossRef]

- Weltin-Wu, C.; Zhao, G.; Galton, I. A 3.5 GHz Digital Fractional-N PLL Frequency Synthesizer Based on Ring Oscillator Frequency-to-Digital Conversion. IEEE J. Solid State Circuits 2015, 50, 2988–3002. [Google Scholar] [CrossRef]

- Hung, C.C.; Liu, S.I. A 40-GHz fast-locked all-digital phase-locked loop using a modified bang-bang algorithm. IEEE Trans. Circuits Syst. II 2011, 58, 321–325. [Google Scholar] [CrossRef]

- Pu, Y.G.; Park, A.S.; Park, J.S.; Lee, K.Y. Low-power, all digital phase-locked loop with a wide-range, high resolution TDC. ETRI J. 2011, 33, 366–373. [Google Scholar] [CrossRef]

© 2018 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).