Spatial Monitoring of I/O Interconnection Nets in Flip-Chip Packages

Abstract

1. Introduction

1.1. Spatial Monitoring in Microchips

1.2. Common Vulnerabilities and Failures in BGAs, Interconnects, and Pass Gate Transistors

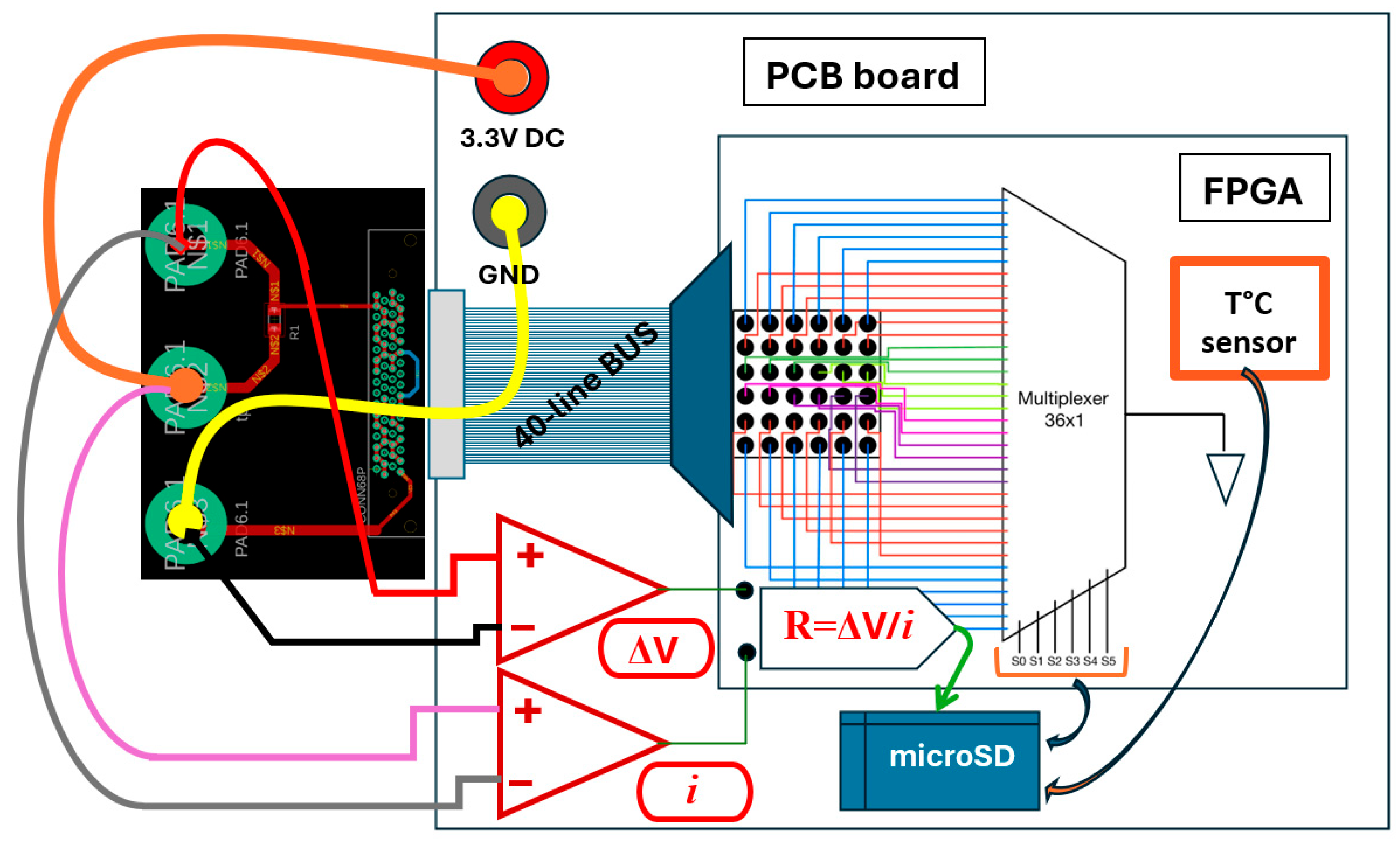

2. I/O Net Testing System and Data Acquisition

2.1. Testing System

- The device under test (DUT). The Packaged device used for the testing is the board (Atlys) with a Spartan-6 FPGA. The FPGA is programmed with a MUX 1 × 39 in System Verilog. The MUX transitions via a fixed counter of 3 s per I/O net. This value is used to ensure stable measurements. The DUT is stressed with a controlled high temperature as detailed in each test scenario.

- A complimentary board used to interface with the external instruments (power supply and DMMs). The board includes three ports:

- Input port for the supplied DC voltage of 5 V.

- Reference ground port.

- Inspection point port.

The board includes a resistor R250 of 250 Ω between the voltage input and inspection points. - Analog input and output instruments:

- REGOL DP832 power supply to supply a 5 V voltage input.

- REGOL M300 which serves as a multiple port DMM to measure the voltage, current, and temperature.

- PC using Labview 2024 Q3 to control and synchronize between the DUT and the instruments and to gather output data.

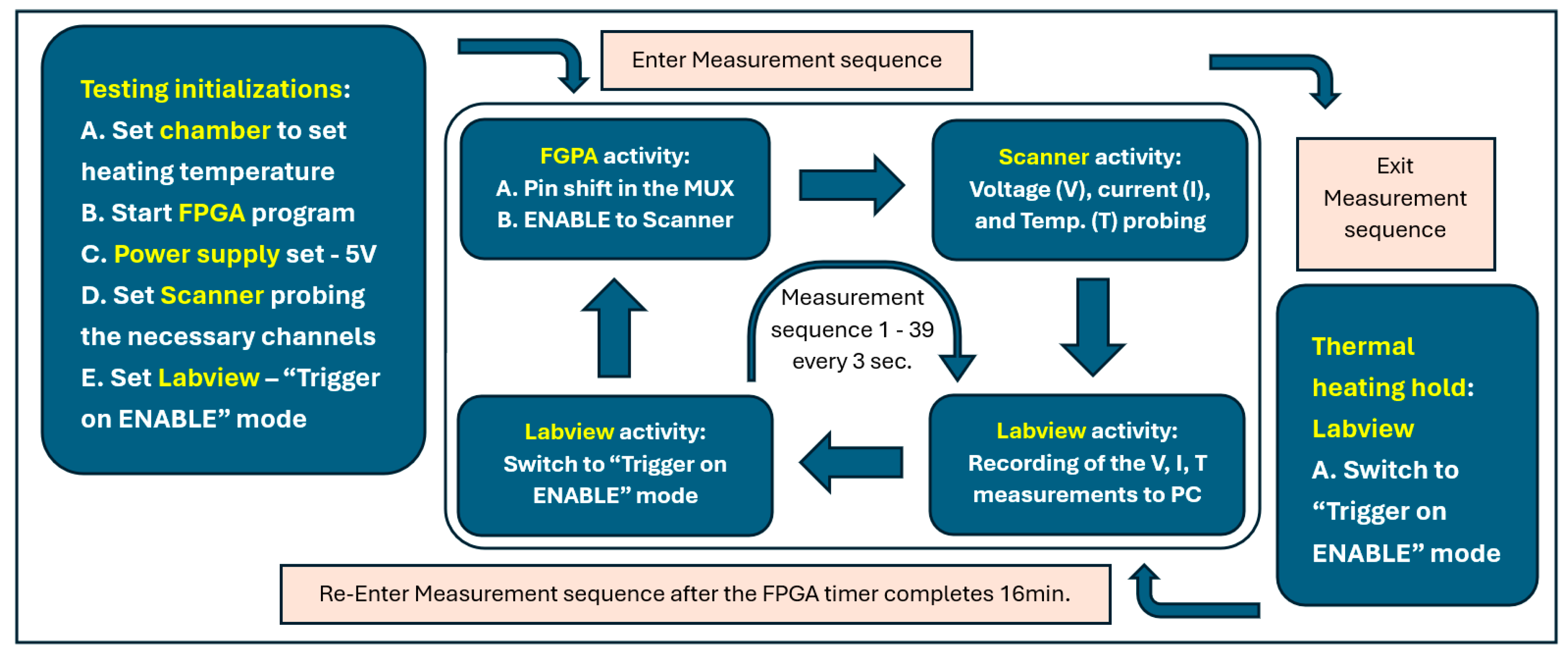

2.2. Testing Sequence

- Steps to initialize the system.

- The measurement sequence.

- System operation between sequences.

3. Experimental

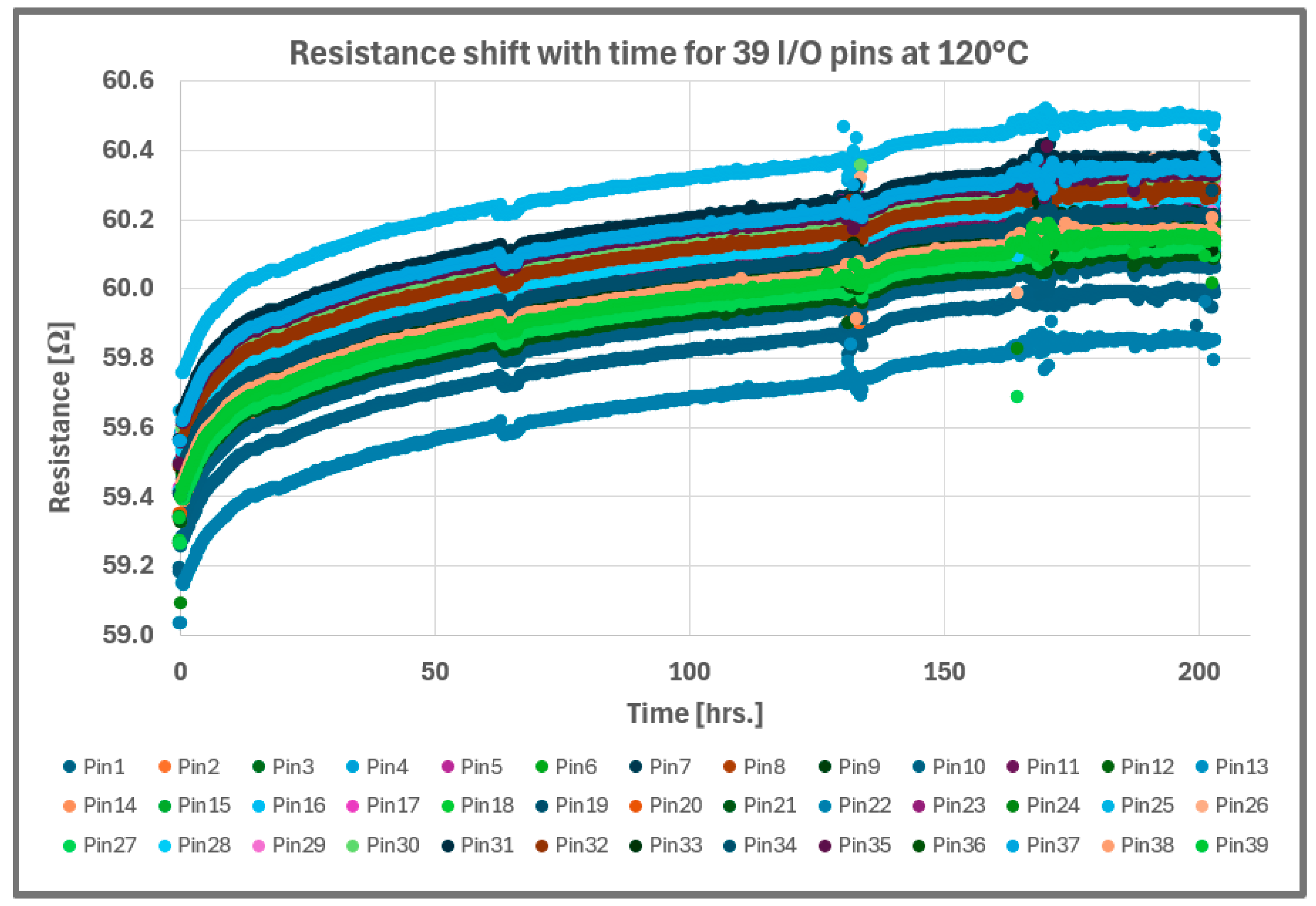

3.1. High Temperature Testing Results

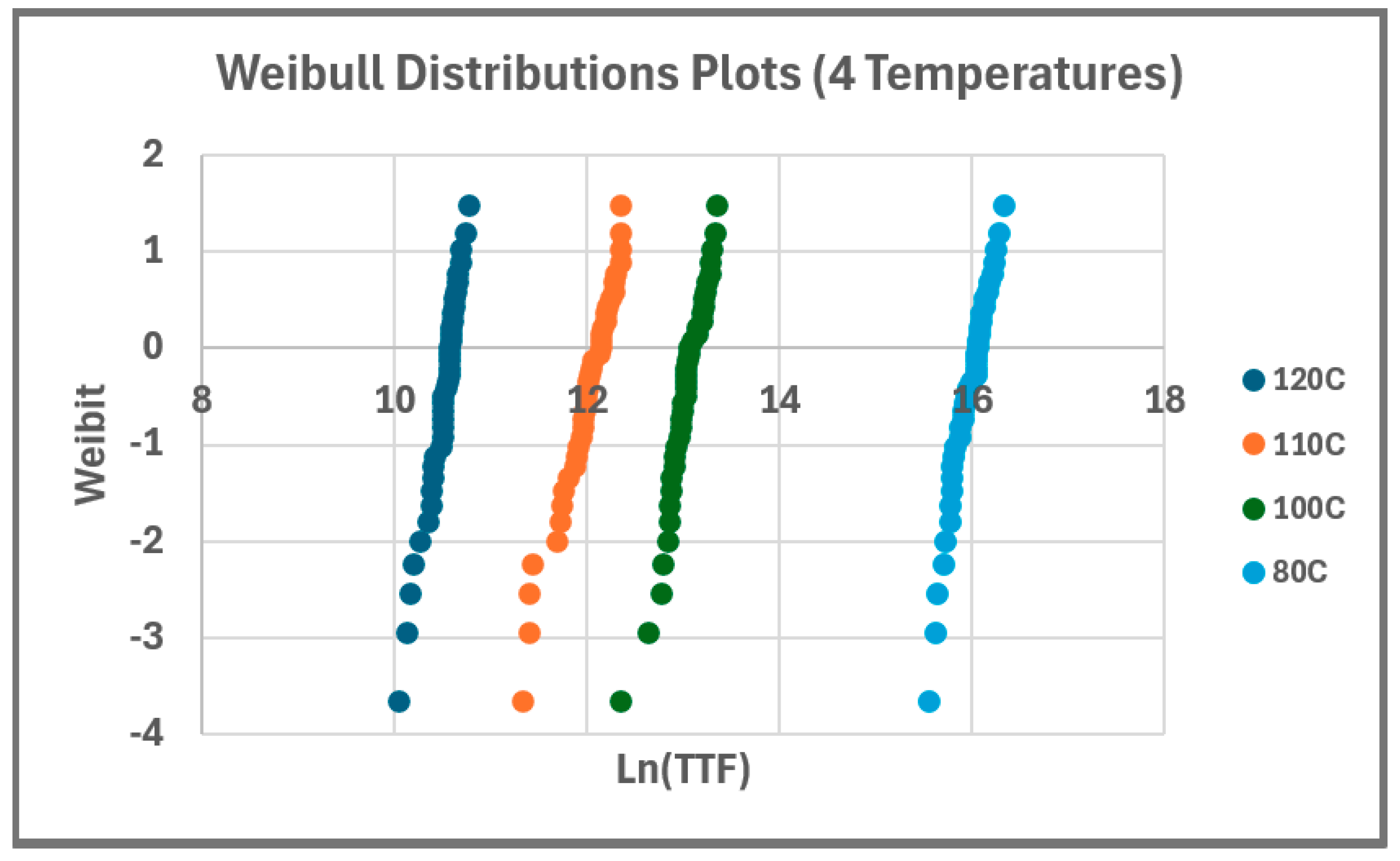

3.2. Estimating the N-Root Power Law to Calculate the TTF

- Standard deviation (SD): ≈0.1019

- 95% Confidence Interval (CI) for the mean: (2.6050, 2.6710)

- t-test (H0: mean = 0):

- ○

- t-statistic: ≈ 161.72

- ○

- p-value: ≈ 0

4. Packaging Spatial Profiles

5. Real-Time I/O Interconnection Net Monitor

6. Conclusions and Deductions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Alghassi, A.; Perinpanayagam, S.; Samie, M.; Sreenuch, T. Computationally Efficient, Real-Time, and Embeddable Prognostic Techniques for Power Electronics. IEEE Trans. Power Electron. 2015, 30, 2623–2634. [Google Scholar] [CrossRef]

- Ahsan, M.; Stoyanov, S.; Bailey, C. Prognostics of Automotive Electronics with Data Driven Approach: A Review. In Proceedings of the 39th International Spring Seminar on Electronics Technology (ISSE), Pilsen, Czech Republic, 18–22 May 2016; pp. 279–284. [Google Scholar] [CrossRef]

- Johnson, D.M. Review of fault management techniques used in safety-critical avionic systems. Prog. Aerosp. Sci. 1996, 32, 415–431. [Google Scholar] [CrossRef]

- Vichare, N.; Pecht, M. Prognostics and Health Management of Electronics. IEEE Trans. Compon. Packag. Technol. 2006, 29, 222–229. [Google Scholar] [CrossRef]

- Louen, C.; Ding, S.X.; Kandler, C. A new framework for remaining useful life estimation using support vector machine classifier. In Proceedings of the Control Fault-Tolerant Systems Conference, Nice, France, 9–11 October 2013; pp. 228–233. [Google Scholar] [CrossRef]

- Bender, E.; Bernstein, J.B. Microchip Health Monitoring System Using the FLL Circuit. Sensors 2021, 21, 2285. [Google Scholar] [CrossRef]

- Ghoshal, A.; Prosser, W.H.; Kim, H.S.; Chattopadhyay, A.; Copeland, B. Development of embedded piezoelectric acoustic sensor array architecture. Microelectron. Reliab. 2010, 50, 857–863. [Google Scholar] [CrossRef]

- Habib, F.; Martinez, M.; Artemev, A.; Brothers, M. Structural health monitoring of bonded composite repairs—A critical comparison between ultrasonic Lamb wave approach and surface mounted crack sensor approach. Compos. Part B Eng. 2013, 47, 26–34. [Google Scholar] [CrossRef]

- Lall, P.; Islam, N.; Suhling, J. Prognostication and health monitoring of leaded and lead free electronic and MEMS packages in harsh environments. In Proceedings of the 55th IEEE Electronic Components and Technology Conference (ECTC), Orlando, FL, USA, 1–3 June 2005; pp. 1305–1313. [Google Scholar] [CrossRef]

- Byttner, S.; Rögnvaldsson, T.; Svensson, M. Consensus Self-organized Models for Fault Detection (COSMO). Eng. Appl. Artif. Intell. 2011, 24, 833–839. [Google Scholar] [CrossRef]

- Bender, E.; Bernstein, J.B.; Boning, D.S. Modern Trends in Microelectronics Packaging Reliability Testing. Micromachines 2024, 15, 398. [Google Scholar] [CrossRef] [PubMed]

- Bhate, D.; Chan, D.; Subbarayan, G.; Chiu, T.C.; Gupta, V.; Edwards, D.R. Constitutive Behavior of Sn3.8Ag0.7Cu and Sn1.0Ag0.5Cu Alloys at Creep and Low Strain Rate Regimes. IEEE Trans. Compon. Packag. Technol. 2008, 31, 622–633. [Google Scholar] [CrossRef]

- Kumar, P.; Huang, Z.; Chavali, S.C.; Chan, D.K.; Dutta, I.; Subbarayan, G.; Gupta, V. Microstructurally Adaptive Model for Primary and Secondary Creep of Sn-Ag-Based Solders. IEEE Trans. Compon. Packag. Manuf. Technol. 2012, 2, 256–265. [Google Scholar] [CrossRef]

- Bernstein, J.B.; Bensoussan, A.; Bender, E. Reliability Prediction for Microelectronics, 1st ed.; Wiley Series in Quality & Reliability Engineering: Hoboken, NJ, USA, 2024; ISBN 978-1394210930. [Google Scholar]

- Ouyang, F.-Y.; Tu, K.; Lai, Y.-S. Effect of electromigration induced joule heating and strain on microstructural recrystallization in eutectic SnPb flip chip solder joints. Mater. Chem. Phys. 2012, 136, 210–218. [Google Scholar] [CrossRef]

- Dandu, P.; Fan, X.; Liu, Y.; Diao, C. Finite element modeling on electromigration of solder joints in wafer level packages. Microelectron. Reliab. 2010, 50, 547–555. [Google Scholar] [CrossRef]

- Clement, J.J.; Thompson, C.V. Modeling electromigration-induced stress evolution in confined metal lines. J. Appl. Phys. 1995, 78, 900–904. [Google Scholar] [CrossRef]

- Peng, J.; Huang, D.M.; Jiao, G.F.; Li, M.F. A Reliability Model for CMOS Circuit Based on Device Degradation. In Proceedings of the IEEE 11th International Conference on Solid-State and Integrated Circuit Technology, Xi’an, China, 29 October–1 November 2012; pp. 1–3. [Google Scholar] [CrossRef]

- Velamala, J.B.; Sutaria, K.B.; Ravi, V.S.; Cao, Y. Failure Analysis of Asymmetric Aging Under NBTI. IEEE Trans. Device Mater. Reliab. 2012, 13, 340–349. [Google Scholar] [CrossRef]

- Bernstein, J.B.; Bensoussan, A.; Bender, E. Reliability prediction with MTOL. Microelectron. Reliab. 2017, 68, 91–97. [Google Scholar] [CrossRef]

- Wu, X.; Yang, X.; Ye, J.; Liu, G. Novel Prognostics for IGBTs Using Wire-Bond Contact Degradation Model Considering On-Chip Temperature Distribution. IEEE Trans. Power Electron. 2025, 40, 4411–4424. [Google Scholar] [CrossRef]

| Test Case | N-Root | TTF (Averaged) | Parameter |

|---|---|---|---|

| 80 °C | 2.693 | 8,626,033 h. | 5.933 |

| 100 °C | 2.748 | 455,674 h. | 5.665 |

| 110 °C | 2.634 | 162,387 h. | 4.196 |

| 120 °C | 2.638 | 36,566 h. | 6.984 |

| Input# | Quadrant# | x-Distance | y-Distance |

|---|---|---|---|

| 0 | 4 | 7 | 8 |

| 1 | 4 | 6 | 8 |

| 2 | 4 | 4 | 8 |

| 3 | 4 | 2 | 3 |

| … | … | … | … |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Bender, E.; Sitbon, M.; Avraham, T.; Gerasimov, M. Spatial Monitoring of I/O Interconnection Nets in Flip-Chip Packages. Electronics 2025, 14, 3549. https://doi.org/10.3390/electronics14173549

Bender E, Sitbon M, Avraham T, Gerasimov M. Spatial Monitoring of I/O Interconnection Nets in Flip-Chip Packages. Electronics. 2025; 14(17):3549. https://doi.org/10.3390/electronics14173549

Chicago/Turabian StyleBender, Emmanuel, Moshe Sitbon, Tsuriel Avraham, and Michael Gerasimov. 2025. "Spatial Monitoring of I/O Interconnection Nets in Flip-Chip Packages" Electronics 14, no. 17: 3549. https://doi.org/10.3390/electronics14173549

APA StyleBender, E., Sitbon, M., Avraham, T., & Gerasimov, M. (2025). Spatial Monitoring of I/O Interconnection Nets in Flip-Chip Packages. Electronics, 14(17), 3549. https://doi.org/10.3390/electronics14173549