Bit Synchronization-Assisted Frequency Correction in Low-SNR Wireless Systems

Abstract

1. Introduction

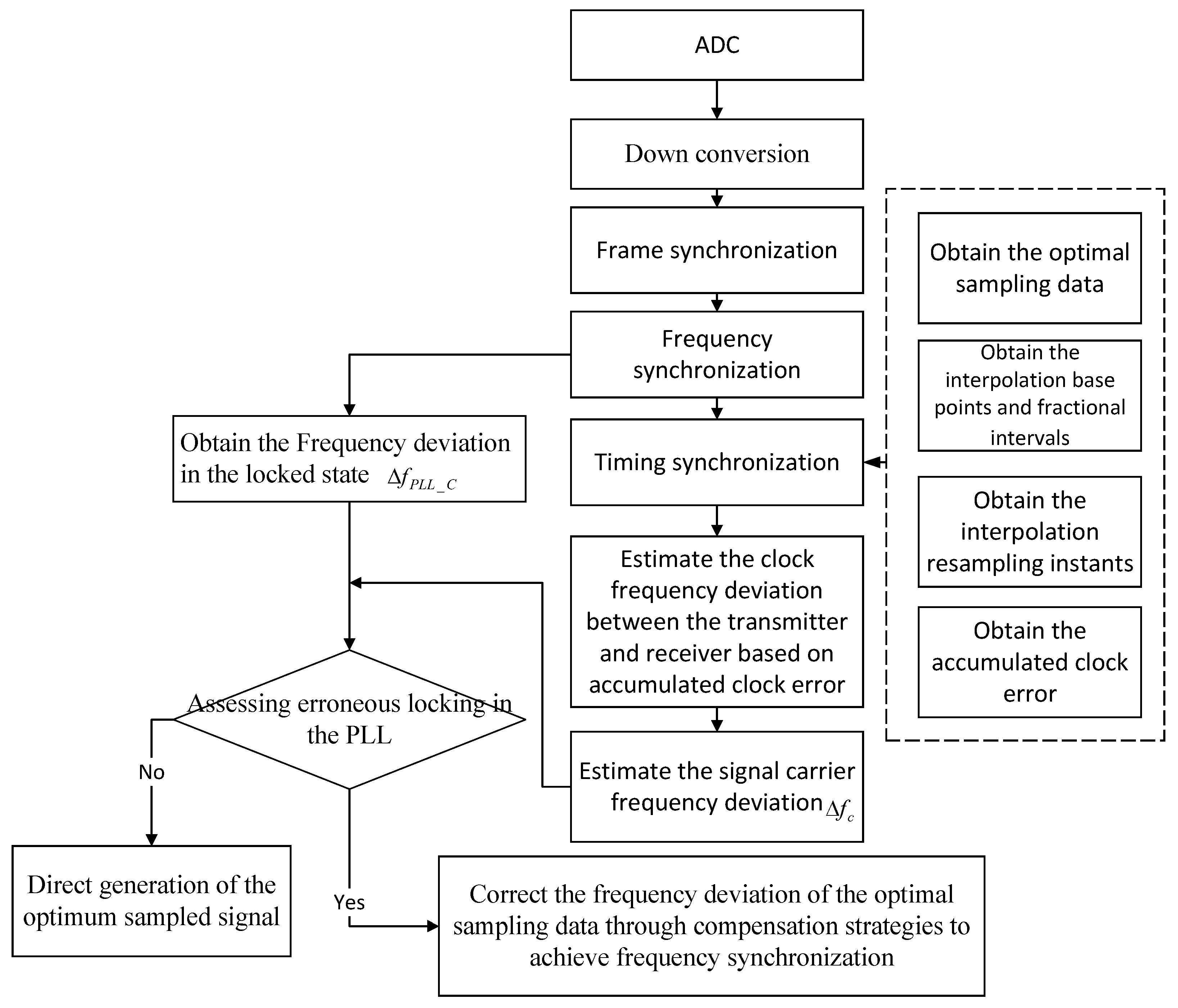

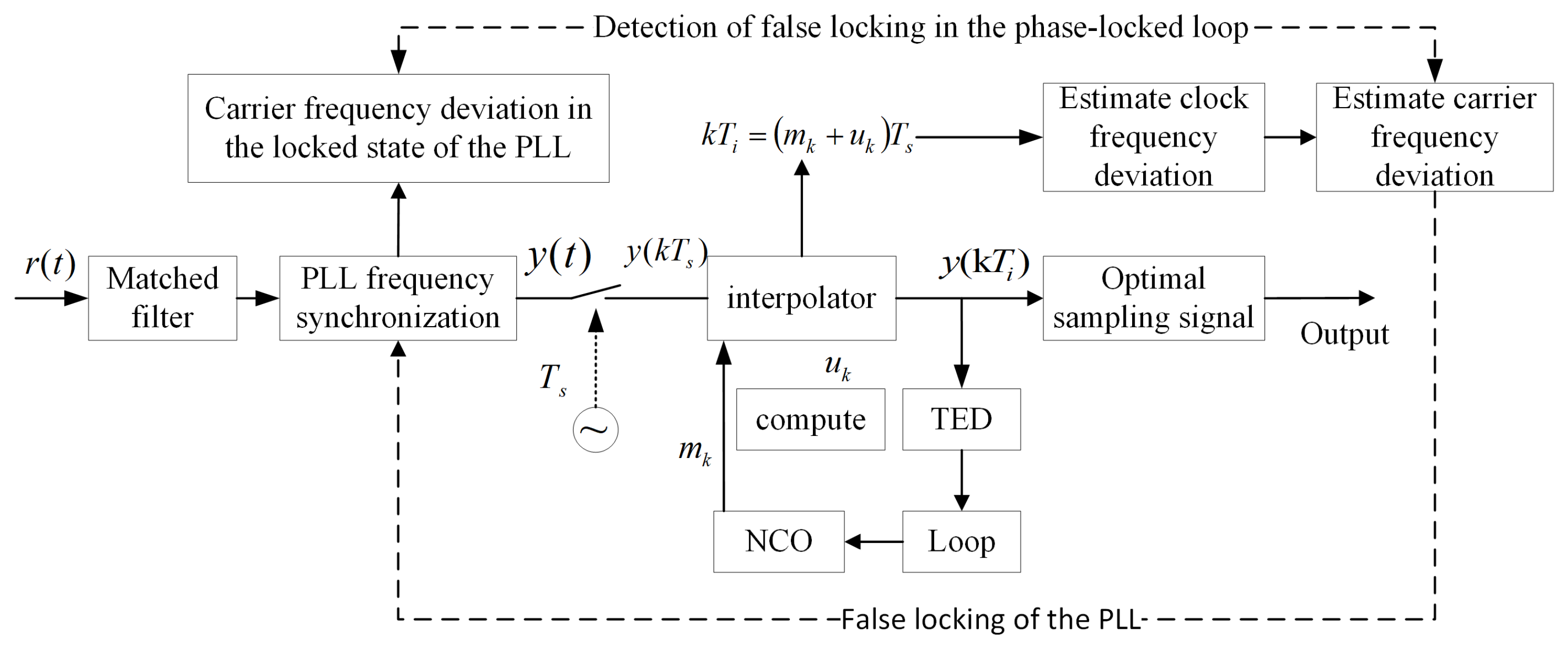

2. System Modeling

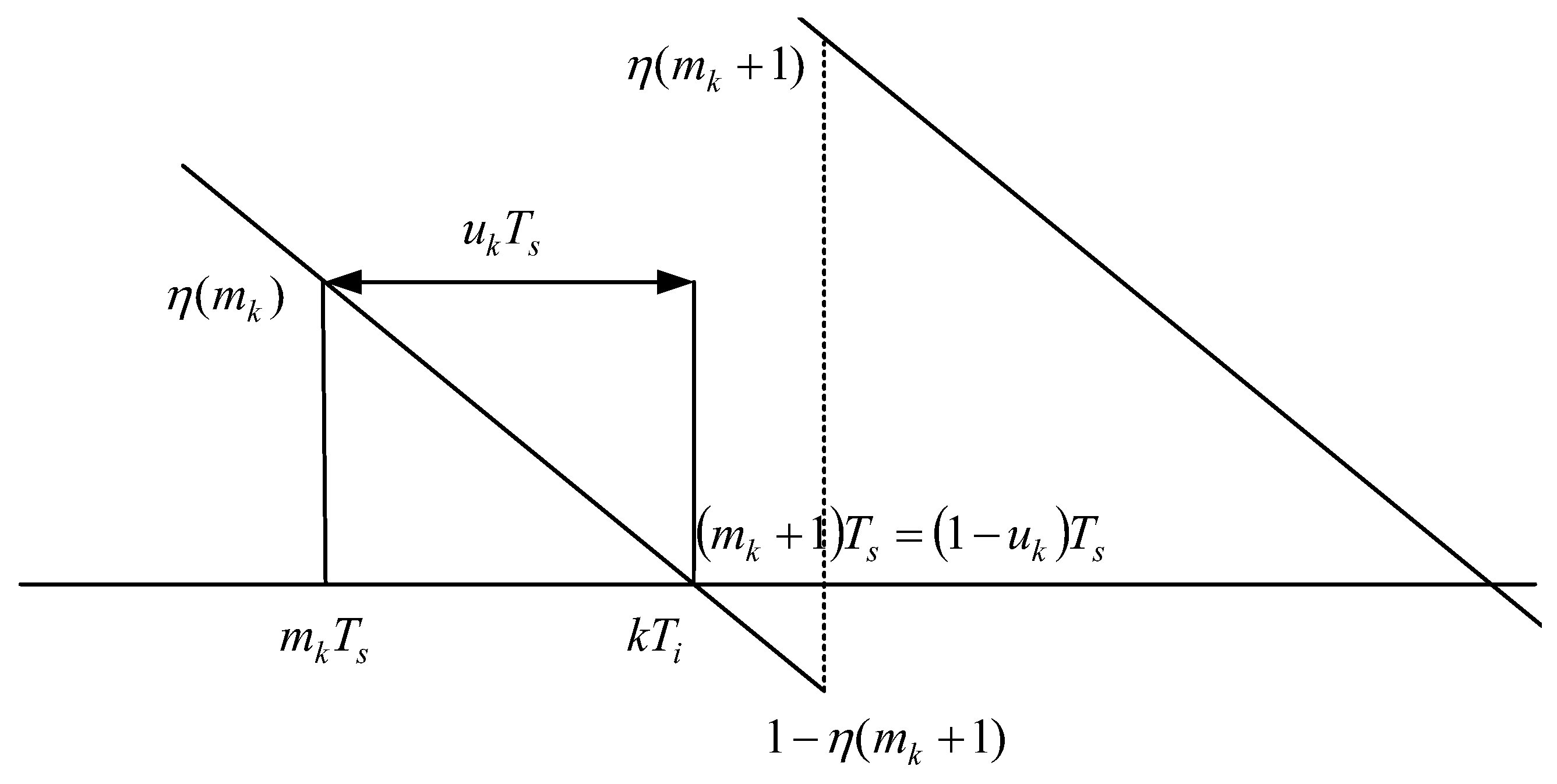

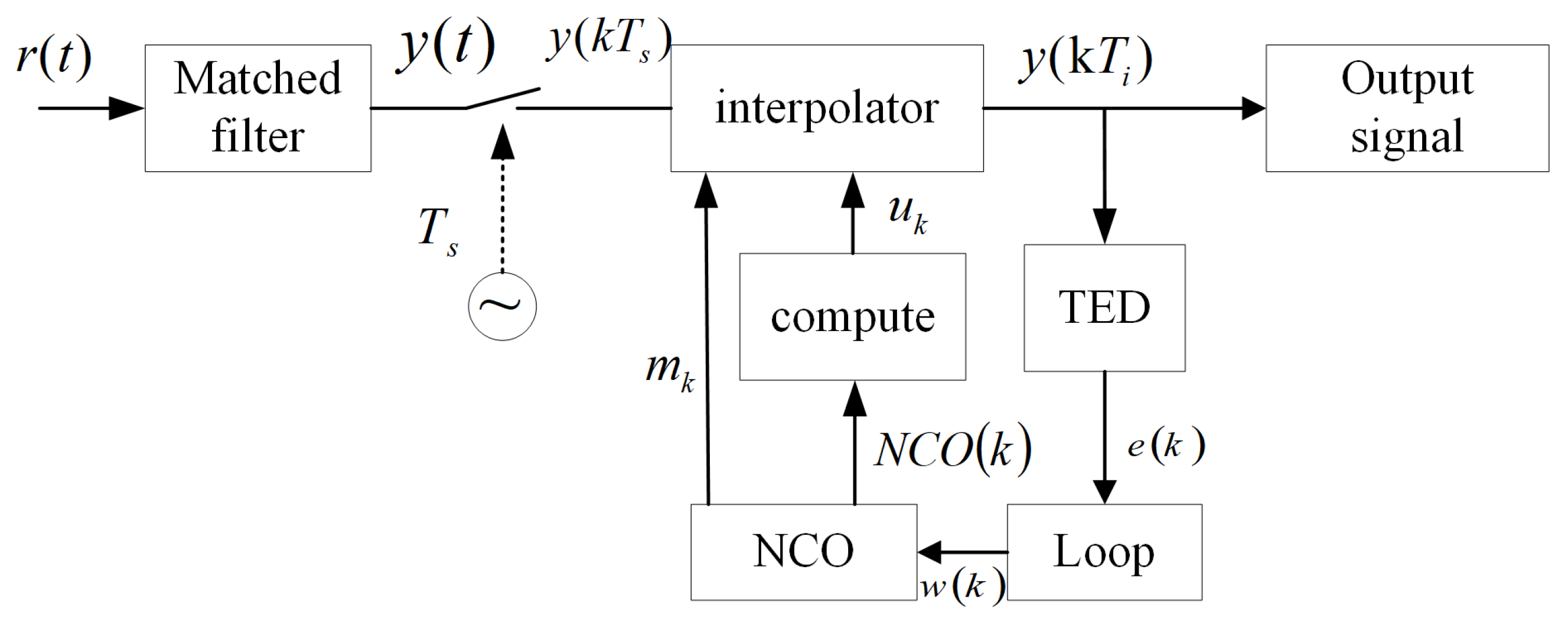

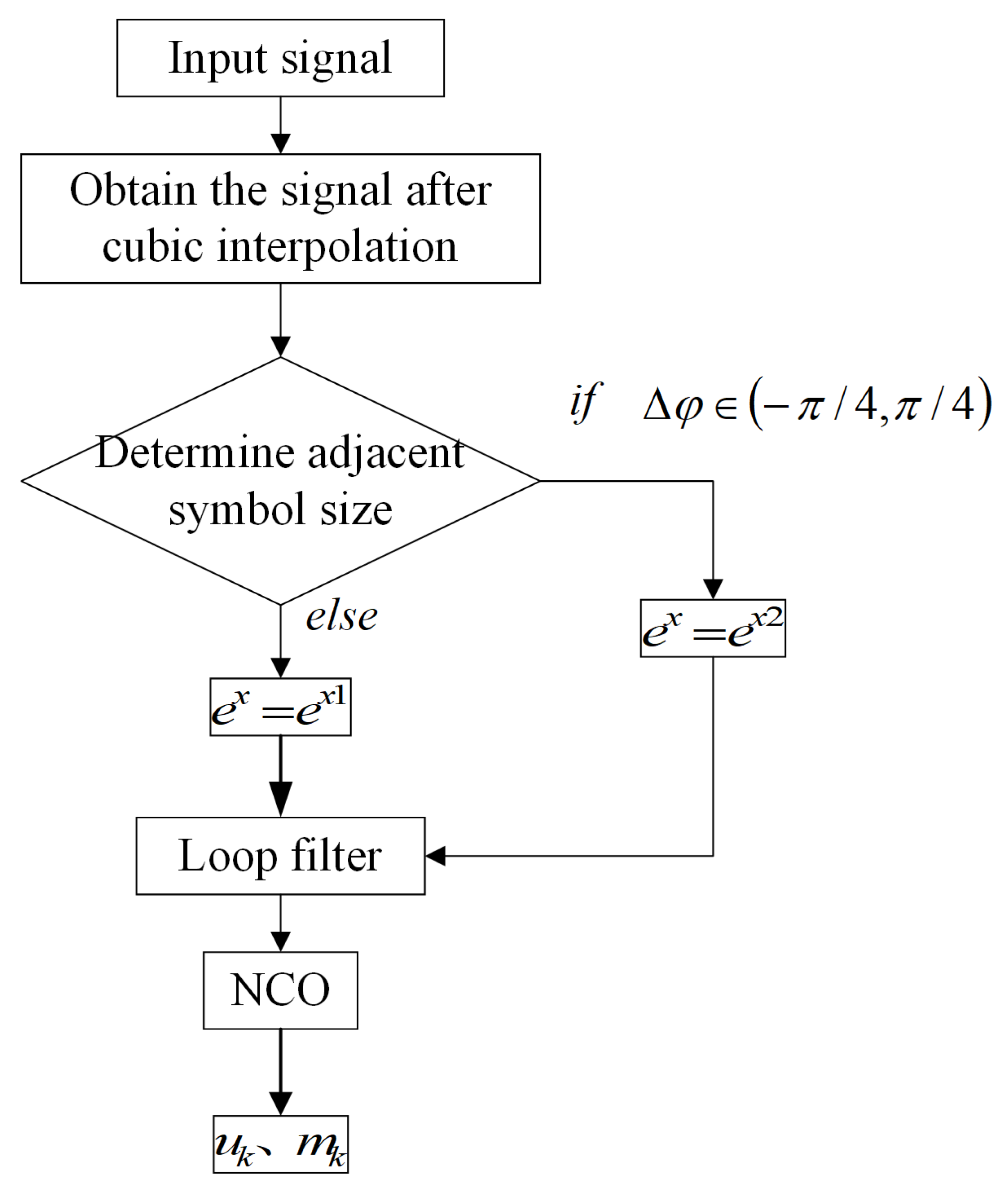

2.1. Timing Synchronization Feedback Model

2.2. Common Source Characteristics of Sampling and Carrier Clocks

2.2.1. Reference Clock Drift

2.2.2. Relative Offset Between Sampling and Carrier Clocks

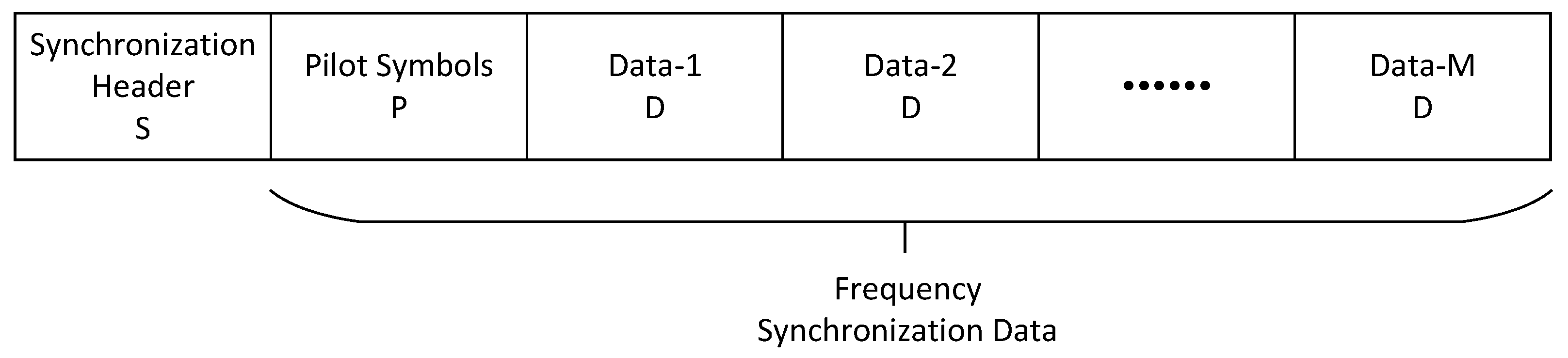

3. Carrier Frequency Offset Estimation

- : Receiver upsampling factor;

- : Ratio of carrier frequency to sampling clock frequency ();

- : Ratio of symbol rate to sampling rate ( where is symbol rate).

- : Interpolation basepoint index (integer part of timing offset);

- : Fractional interval ();

- : Ideal symbol-spaced sampling instant where k is the symbol index.

- Coarse Frequency Correction—The optimal sampled data undergoes frequency offset compensation using a digital down-conversion approach to obtain a coarsely corrected signal;

- Fine Frequency Correction via PLL—The coarse frequency-compensated signal is further refined using a PLL, which tracks and adjusts the residual frequency error;

- Phase Ambiguity Resolution—The fine frequency-compensated signal is further processed to resolve phase ambiguity, thereby completing the frequency synchronization process.

4. Modified Timing Synchronization Loop

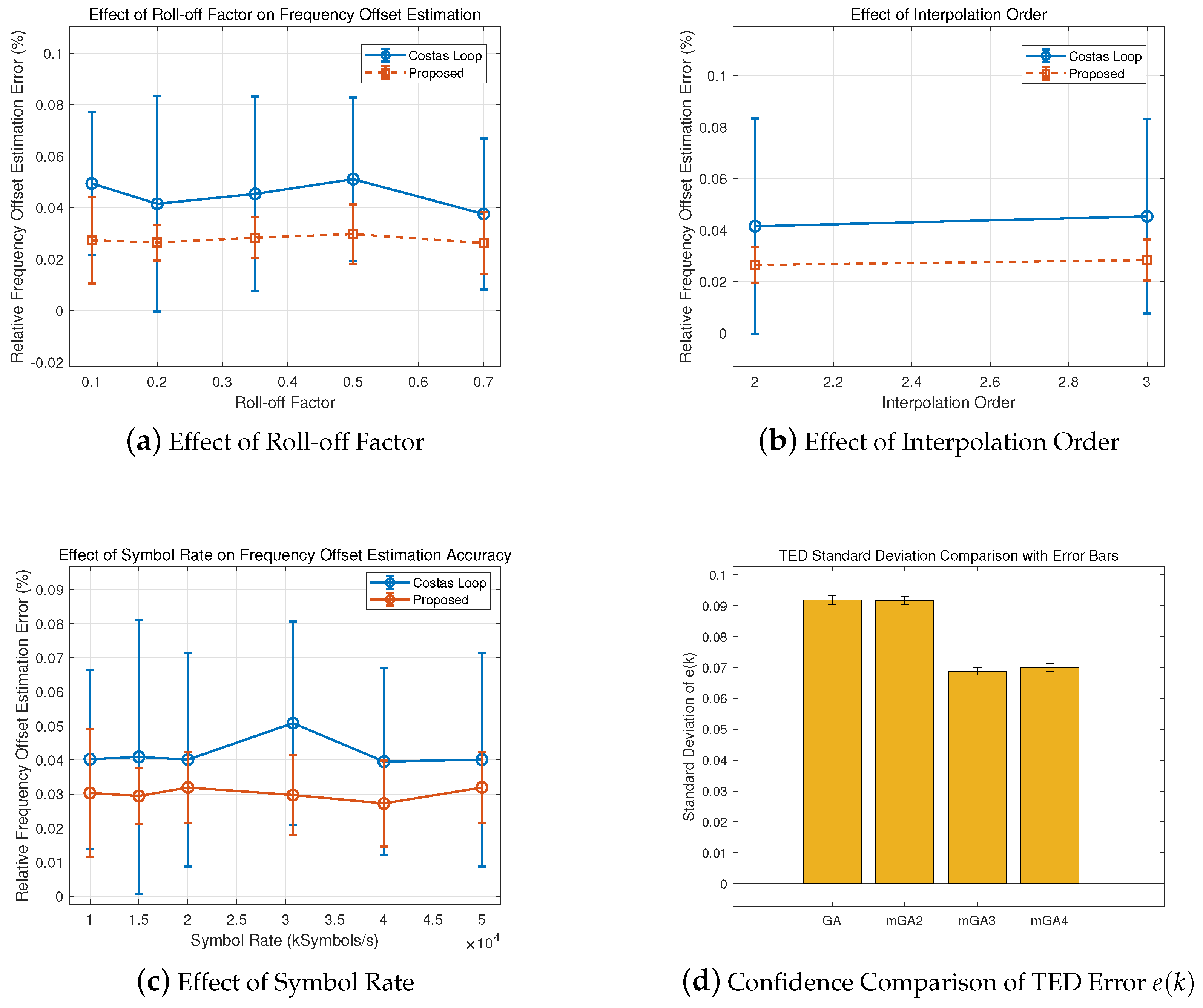

4.1. Self-Noise Suppression in Error Detection

4.2. Optimization of the Error Function

4.3. Final Expression of the mGA4 Algorithm

5. Simulation Results

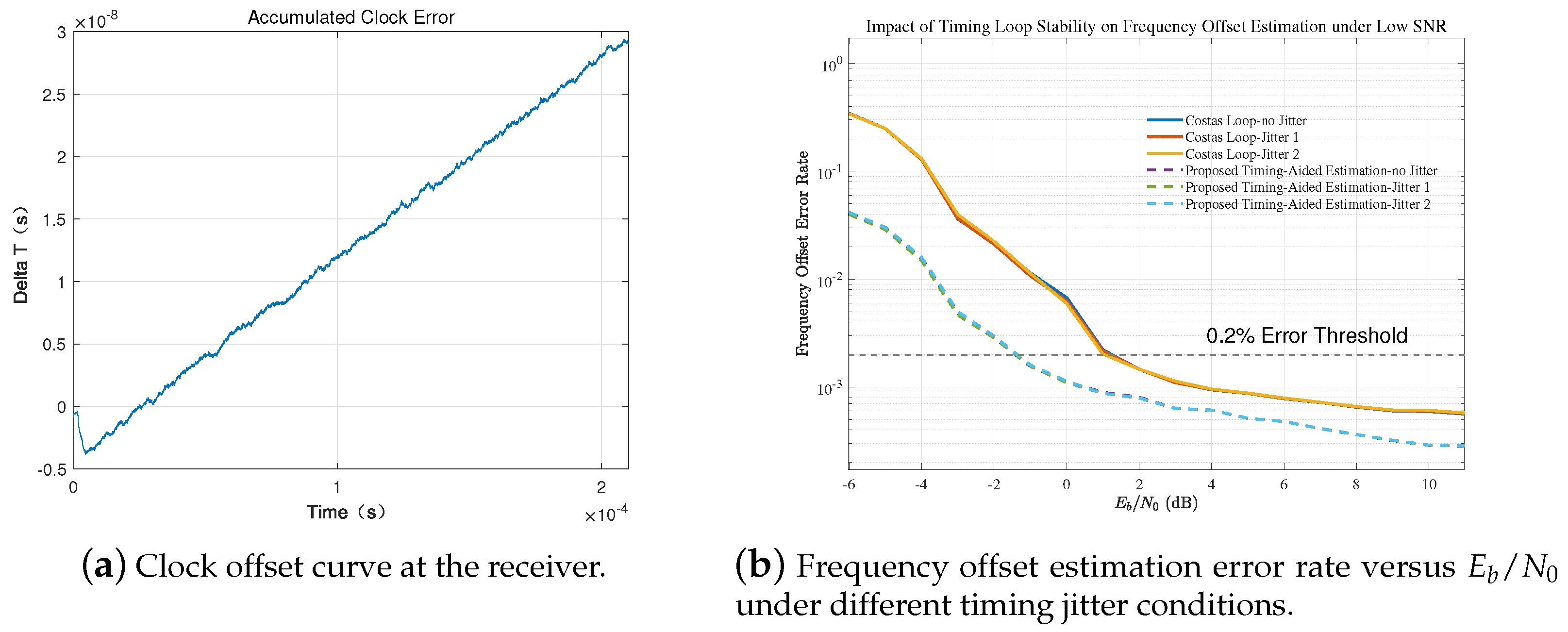

5.1. Carrier Phase Noise and Jitter Modeling

- Jitter1: Represents a typical high-performance oscillator (e.g., HMC830 PLL with 875 MHz output), with phase noise values:at frequency offsets Hz;

- Jitter2: Models a degraded oscillator, increasing the phase noise at all frequency offsets by approximately 10 dB compared to Jitter1, thus representing a more severe jitter condition.

5.2. Verification of Carrier Synchronization Performance

Statistical Analysis

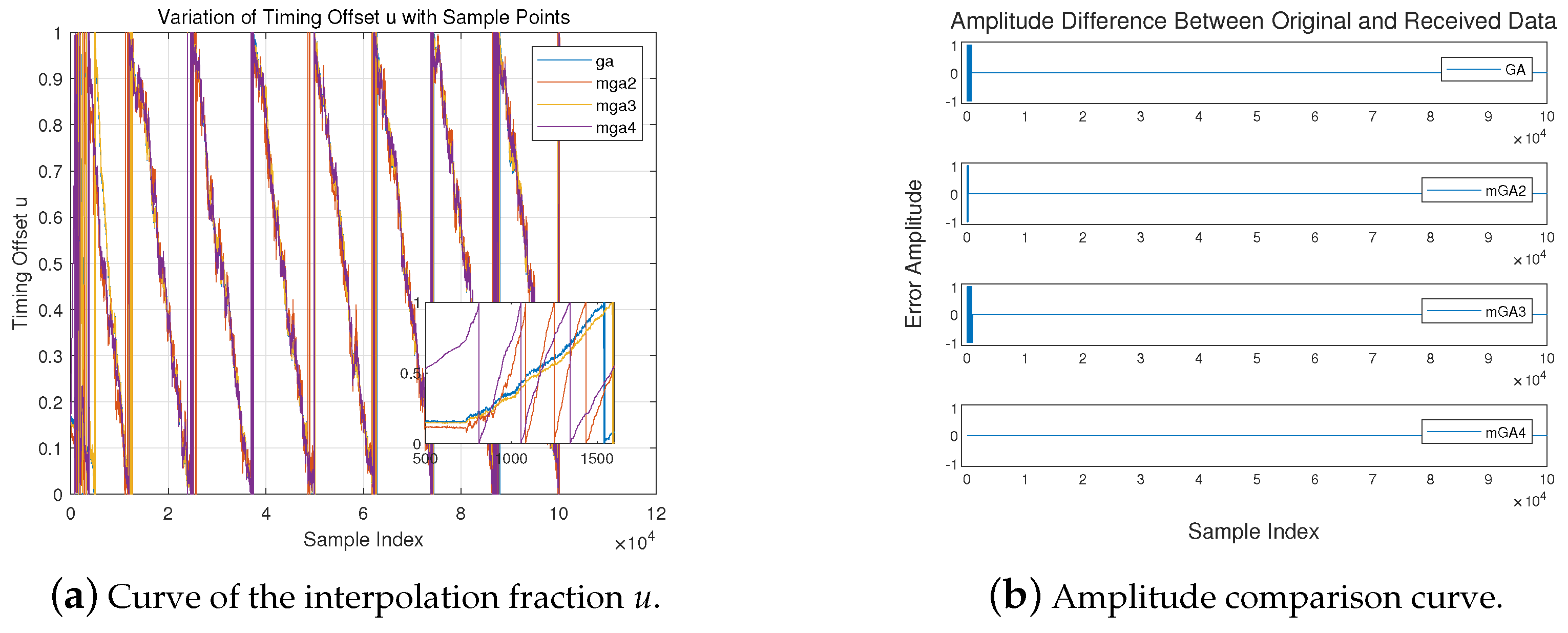

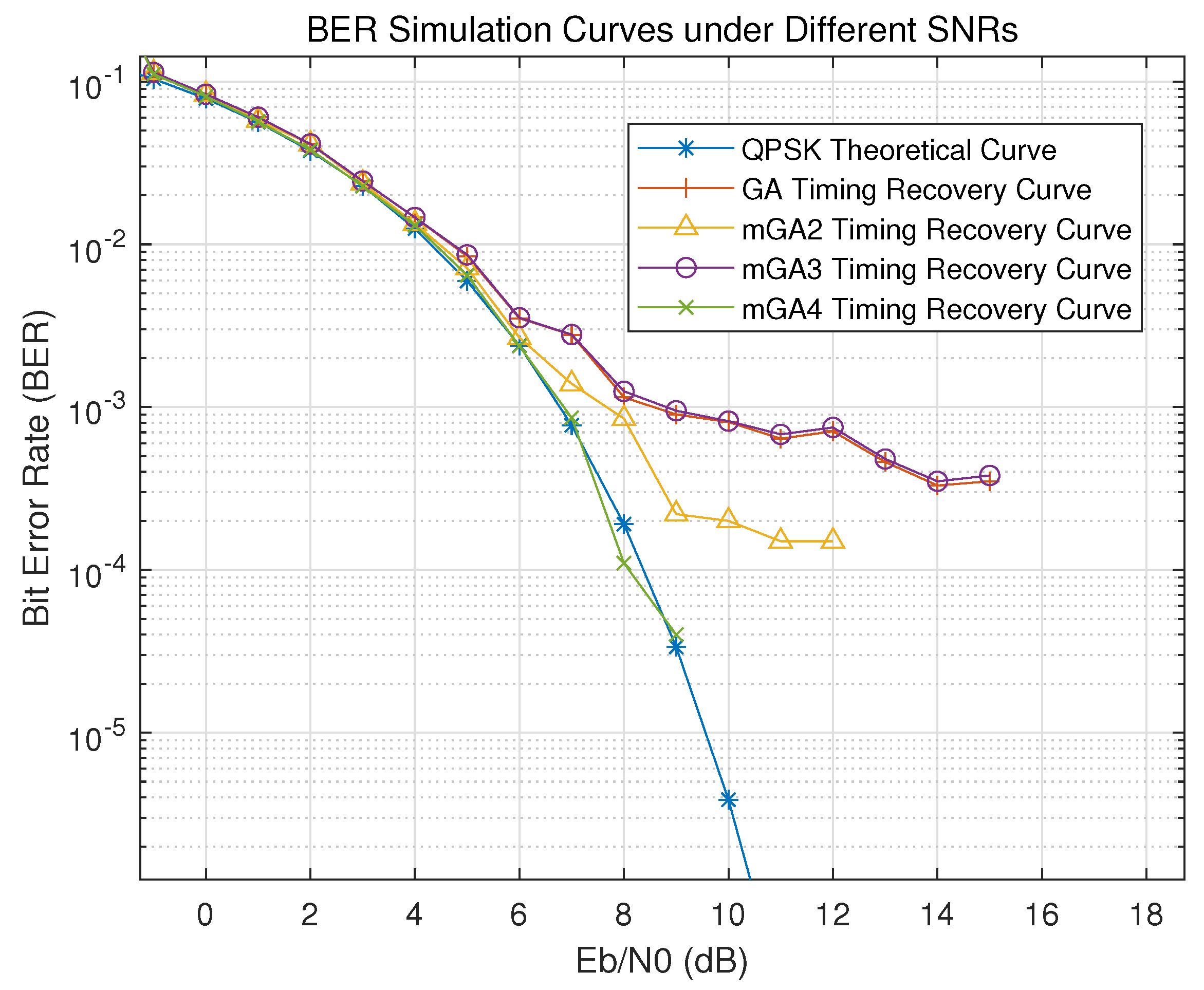

5.3. Validation of the Improved Timing Recovery Algorithm Performance

5.4. Evaluation of System Reliability and Efficiency

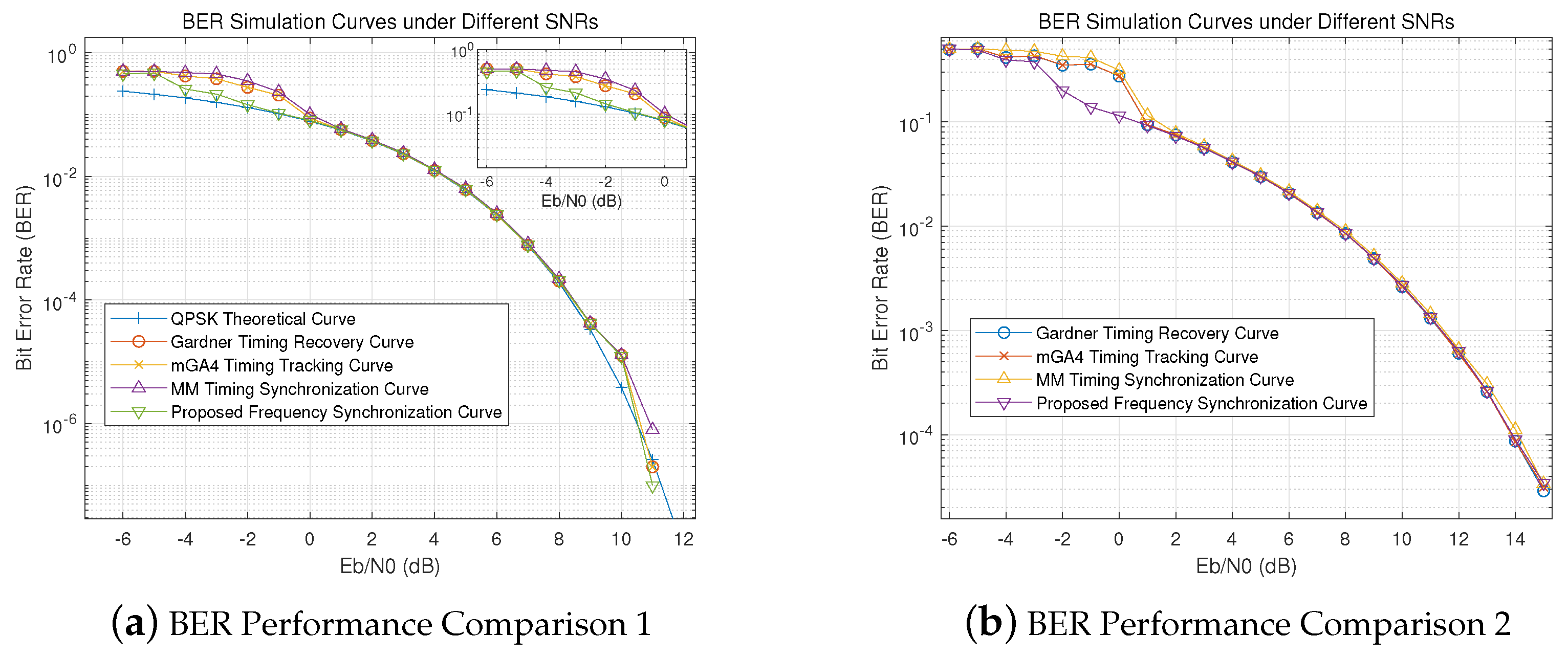

5.5. Bit Error Rate Optimization

5.6. Computational Complexity Analysis

- 4 sign evaluations (2 for in-phase and 2 for quadrature components);

- 2 XOR logical operations;

- 1 conditional timing error update.

- 2 subtractions (real and imaginary);

- 2 multiplications (for squaring);

- 1 addition (error accumulation);

- 1 comparison (minimum error selection).

- 6 multiplications;

- 6 additions.

- N multiplications;

- additions;

- 1 division.

6. Discussion

7. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Data Availability Statement

Conflicts of Interest

References

- Kay, S. A fast and accurate single frequency estimator. IEEE Trans. Acoust. Speech Signal Process. 1989, 37, 1987–1990. [Google Scholar] [CrossRef]

- Lovell, B.C.; Williamson, R.C. The Statistical Performance of Some Instantaneous Frequency Estimators. IEEE Trans. Signal Process. 1992, 40, 1708–1723. [Google Scholar] [CrossRef]

- Luise, M.; Reggiannini, R. Carrier frequency recovery in all-digital modems for burst-mode transmissions. IEEE Trans. Commun. 1995, 43, 1169–1178. [Google Scholar] [CrossRef]

- Liu, W.T.; Yang, T.; Chen, X.; You, J. Low-Complexity Frequency Offset Estimation for Probabilistically Shaped MQAM Coherent Optical Systems. IEEE Photonics J. 2022, 14, 7841911. [Google Scholar] [CrossRef]

- Tan, Q.; Yang, A.; Guo, P.; Zhao, Z. Blind frequency offset estimation based on phase rotation for coherent transceiver. IEEE Photonics J. 2020, 12, 7902212. [Google Scholar] [CrossRef]

- Roshna, T.R.; Nivin, R.; Joy, S.; Apren, T.J.; Alex, V. Design and implementation of digital Costas loop and Bit synchronizer in FPGA for BPSK demodulation. In Proceedings of the International Conference on Control Communication & Computing, Thiruvananthapuram, India, 13–15 December 2013; IEEE: Piscataway, NJ, USA, 2014; pp. 39–41. [Google Scholar]

- Guo, S.Y.; Qiao, D.H.; Zhao, H.M. Implementation of Costas Loop for BPSK Receivers Using FPGA. Appl. Mech. Mater. 2013, 263–266, 990–993. [Google Scholar] [CrossRef]

- Wu, L.L.; Wang, B.; Huang, Y.; Wang, H.; Tang, Q. A Blind Demodulation Algorithm for Underwater Acoustic MPSK Signal. IEEE Access 2021, 9, 147458–147470. [Google Scholar] [CrossRef]

- Kumar, S.; Majhi, S. Blind symbol timing offset estimation for offset-QPSK modulated signals. ETRI J. 2019, 42, 324–332. [Google Scholar] [CrossRef]

- Mueller, K.; Muller, M. Timing Recovery in Digital Synchronous Data Receivers. IEEE Trans. Commun. 1976, 24, 516–531. [Google Scholar] [CrossRef]

- Cerato, B.; Colazzo, L.; Martina, M.; Molino, A.; Vacca, F. Parametric FPGA early-late DLL implementation for a UMTS receiver. In Proceedings of the Conference Record of the Thirty-Sixth Asilomar Conference on Signals, Systems and Computers, Pacific Grove, CA, USA, 3–6 November 2002; IEEE: Piscataway, NJ, USA, 2002; pp. 1069–1072. [Google Scholar]

- Gardner, F. A BPSK/QPSK timing-error detector for sampled receivers. IEEE Trans. Commun. 1986, 34, 423–429. [Google Scholar] [CrossRef]

- Wang, Q.; Li, H.; Lu, C.Y. Design of interpolation filter in all-digital clock recovery scheme. J. Univ. Sci. Technol. Beijing 2008, 5, 576–580. [Google Scholar]

- Spalvieri, A.; Magarini, M. Minimum timing jitter in timing recovery based on pre-filtered square-law timing detection. In Proceedings of the 2009 Second International Conference on Communication Theory, Reliability, and Quality of Service, Colmar, France, 19–24 July 2009; IEEE: Piscataway, NJ, USA, 2009; pp. 46–51. [Google Scholar]

- D’Andrea, N.A.; Luise, M. Design and analysis of a jitter-free clock recovery scheme for QAM systems. IEEE Trans. Commun. 1993, 41, 1296–1299. [Google Scholar] [CrossRef]

- Lankl, B.; Sebald, G. Jitter-reduced digital timing recovery for multilevel PAM and QAM systems. In Proceedings of the ICC’93—IEEE International Conference on Communications, Geneva, Switzerland, 23–26 May 1993; IEEE: Piscataway, NJ, USA, 1993; pp. 804–810. [Google Scholar]

- Lim, D. A modified Gardner detector for symbol timing recovery of M-PSK signals. IEEE Trans. Commun. 2004, 52, 1643–1647. [Google Scholar] [CrossRef]

- Sciagura, E.; Zicari, P.; Perri, S.; Corsonello, P. An efficient and optimized FPGA feedback M-PSK symbol timing recovery architecture based on the gardner timing error detector. In Proceedings of the 10th Euromicro Conference on Digital System Design Architectures, Methods and Tools (DSD 2007), Lubeck, Germany, 29–31 August 2007; IEEE: Piscataway, NJ, USA, 2007; pp. 102–108. [Google Scholar]

- Cardenas, D.; Arevalo, G. Flag based all digital timing recovery. In Proceedings of the 2019 IEEE CHILEAN Conference on Electrical, Electronics Engineering, Information and Communication Technologies (CHILECON), Valparaiso, Chile, 13–27 November 2019; IEEE: Piscataway, NJ, USA, 2019; pp. 1–5. [Google Scholar]

- Yang, D.; Yan, C.; Wang, H.; Kuang, J.; Wu, N. Extension to Gardner timing error detector for QPSK signals. In Proceedings of the 2010 International Conference on Wireless Communications & Signal Processing (WCSP), Suzhou, China, 21–23 October 2010; IEEE: Piscataway, NJ, USA, 2010; pp. 1–5. [Google Scholar]

- Leng, W.; Zhang, Y.; Yang, Z. A modified gardner detector for multilevel PAM/QAM system. In Proceedings of the 2008 International Conference on Communications, Circuits and Systems, Xiamen, China, 25–27 May 2008; pp. 891–895. [Google Scholar]

| Scenario | RMS Phase Jitter (rad) | Jitter Percentage |

|---|---|---|

| Jitter1 | ∼0.0225 | ∼0.36% |

| Jitter2 | ∼0.0450 | ∼0.72% |

| Eb/N0 (dB) | Conventional Costas Loop | Proposed Method | ||||

|---|---|---|---|---|---|---|

| No Jitter | Jitter1 | Jitter2 | No Jitter | Jitter1 | Jitter2 | |

| −6 | 39.25 ± 0.12 | 39.35 ± 0.15 | 39.01 ± 0.18 | 4.77 ± 0.03 | 4.71 ± 0.04 | 4.81 ± 0.05 |

| −5 | 49.61 ± 0.21 | 49.19 ± 0.19 | 49.17 ± 0.22 | 5.41 ± 0.07 | 5.28 ± 0.06 | 5.50 ± 0.08 |

| −4 | 5.73 ± 0.09 | 5.94 ± 0.11 | 6.46 ± 0.13 | 0.72 ± 0.02 | 0.67 ± 0.02 | 0.75 ± 0.03 |

| −3 | 3.52 ± 0.07 | 3.42 ± 0.06 | 3.61 ± 0.08 | 0.49 ± 0.01 | 0.49 ± 0.01 | 0.51 ± 0.01 |

| −2 | 1.60 ± 0.05 | 1.55 ± 0.06 | 1.81 ± 0.07 | 0.23 ± 0.01 | 0.24 ± 0.01 | 0.24 ± 0.01 |

| −1 | 1.49 ± 0.04 | 1.36 ± 0.05 | 1.31 ± 0.05 | 0.13 ± 0.01 | 0.13 ± 0.01 | 0.14 ± 0.01 |

| 0 | 0.33 ± 0.03 | 0.32 ± 0.03 | 0.28 ± 0.03 | 0.10 ± 0.005 | 0.10 ± 0.005 | 0.10 ± 0.005 |

| 1 | 0.21 ± 0.02 | 0.21 ± 0.02 | 0.20 ± 0.02 | 0.10 ± 0.004 | 0.10 ± 0.004 | 0.10 ± 0.004 |

| 2 | 0.12 ± 0.02 | 0.12 ± 0.02 | 0.13 ± 0.02 | 0.06 ± 0.003 | 0.06 ± 0.003 | 0.06 ± 0.003 |

| 3 | 0.11 ± 0.02 | 0.11 ± 0.02 | 0.11 ± 0.02 | 0.07 ± 0.003 | 0.07 ± 0.003 | 0.07 ± 0.003 |

| 4 | 0.10 ± 0.01 | 0.10 ± 0.01 | 0.10 ± 0.01 | 0.05 ± 0.002 | 0.05 ± 0.002 | 0.05 ± 0.002 |

| 5 | 0.08 ± 0.01 | 0.08 ± 0.01 | 0.08 ± 0.01 | 0.06 ± 0.002 | 0.06 ± 0.002 | 0.06 ± 0.002 |

| 6 | 0.09 ± 0.01 | 0.09 ± 0.01 | 0.09 ± 0.01 | 0.04 ± 0.002 | 0.04 ± 0.002 | 0.04 ± 0.002 |

| 7 | 0.07 ± 0.01 | 0.07 ± 0.01 | 0.07 ± 0.01 | 0.04 ± 0.001 | 0.04 ± 0.001 | 0.04 ± 0.001 |

| 8 | 0.06 ± 0.01 | 0.06 ± 0.01 | 0.06 ± 0.01 | 0.04 ± 0.001 | 0.04 ± 0.001 | 0.04 ± 0.001 |

| 9 | 0.07 ± 0.01 | 0.07 ± 0.01 | 0.07 ± 0.01 | 0.03 ± 0.001 | 0.03 ± 0.001 | 0.03 ± 0.001 |

| 10 | 0.06 ± 0.01 | 0.06 ± 0.01 | 0.06 ± 0.01 | 0.03 ± 0.001 | 0.03 ± 0.001 | 0.03 ± 0.001 |

| 11 | 0.05 ± 0.01 | 0.06 ± 0.01 | 0.06 ± 0.01 | 0.03 ± 0.001 | 0.03 ± 0.001 | 0.03 ± 0.001 |

| Algorithm | Timing Convergence Symbols | BER (Initial 10 k) | BER (Full 500 k) | PER (%) | Throughput (Mbps) |

|---|---|---|---|---|---|

| GA | 198 | 2 | 60.21 | ||

| mGA2 | 135 | < | 1 | 60.85 | |

| mGA3 | 193 | 2 | 60.21 | ||

| mGA4 (proposed) | 102 | < | < | 0.6 | 61.44 |

| Module | Operation Type | Count | Complexity |

|---|---|---|---|

| Polarity-Based Gating | Sign, XOR, gating | 4 sign + 2 XOR | |

| Phase-Based Decision | Sub, Mul, Add, Min | 8 mult + 8 add + 4 cmp | |

| Lagrange Interpolation | Mult, Add | 6 mult + 6 add | |

| Drift Estimation (per frame) | Mult, Add, Div | N mult + add + 1 div |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Gao, J.; Yang, P.; Chen, S.; Luo, Z.; Zhang, Y.; Liu, T. Bit Synchronization-Assisted Frequency Correction in Low-SNR Wireless Systems. Electronics 2025, 14, 2319. https://doi.org/10.3390/electronics14122319

Gao J, Yang P, Chen S, Luo Z, Zhang Y, Liu T. Bit Synchronization-Assisted Frequency Correction in Low-SNR Wireless Systems. Electronics. 2025; 14(12):2319. https://doi.org/10.3390/electronics14122319

Chicago/Turabian StyleGao, Junfeng, Peiji Yang, Shaoxiang Chen, Zhenghua Luo, Yilin Zhang, and Tao Liu. 2025. "Bit Synchronization-Assisted Frequency Correction in Low-SNR Wireless Systems" Electronics 14, no. 12: 2319. https://doi.org/10.3390/electronics14122319

APA StyleGao, J., Yang, P., Chen, S., Luo, Z., Zhang, Y., & Liu, T. (2025). Bit Synchronization-Assisted Frequency Correction in Low-SNR Wireless Systems. Electronics, 14(12), 2319. https://doi.org/10.3390/electronics14122319