Design of Dual-Mode Multi-Band Doherty Power Amplifier Employing Impedance-and-Phase Constrained Optimization

Abstract

1. Introduction

2. Dual-Mode Multi-Band DPA Optimization Design Theory

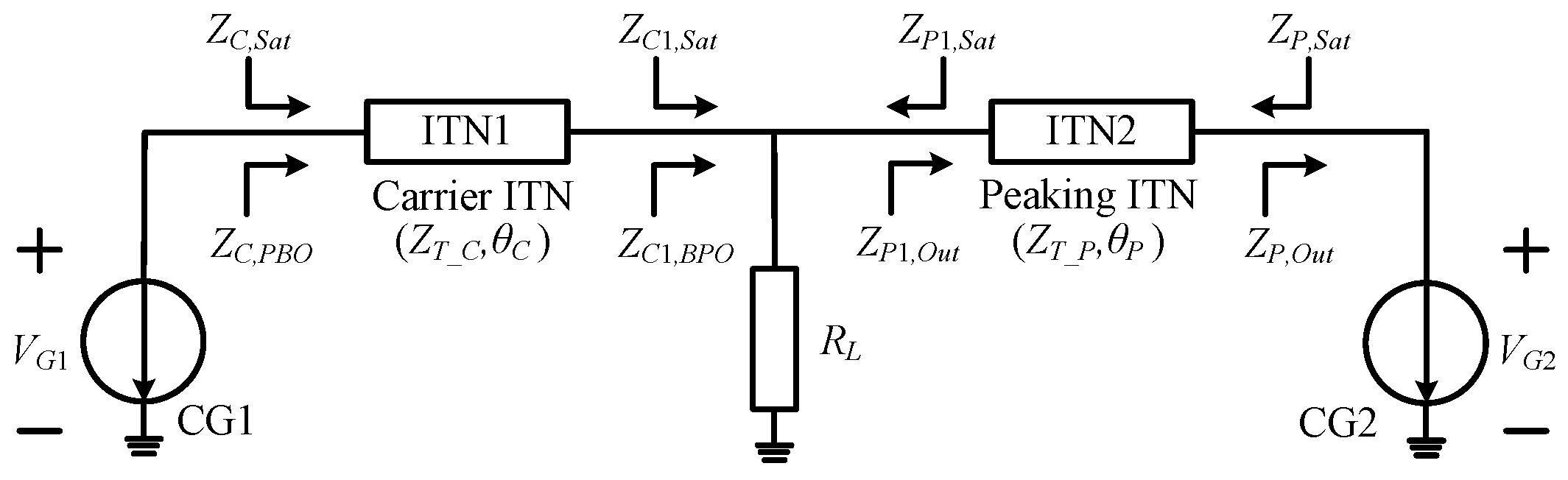

2.1. Dual-Mode DPA Architecture Based on Reciprocal Gate Bias

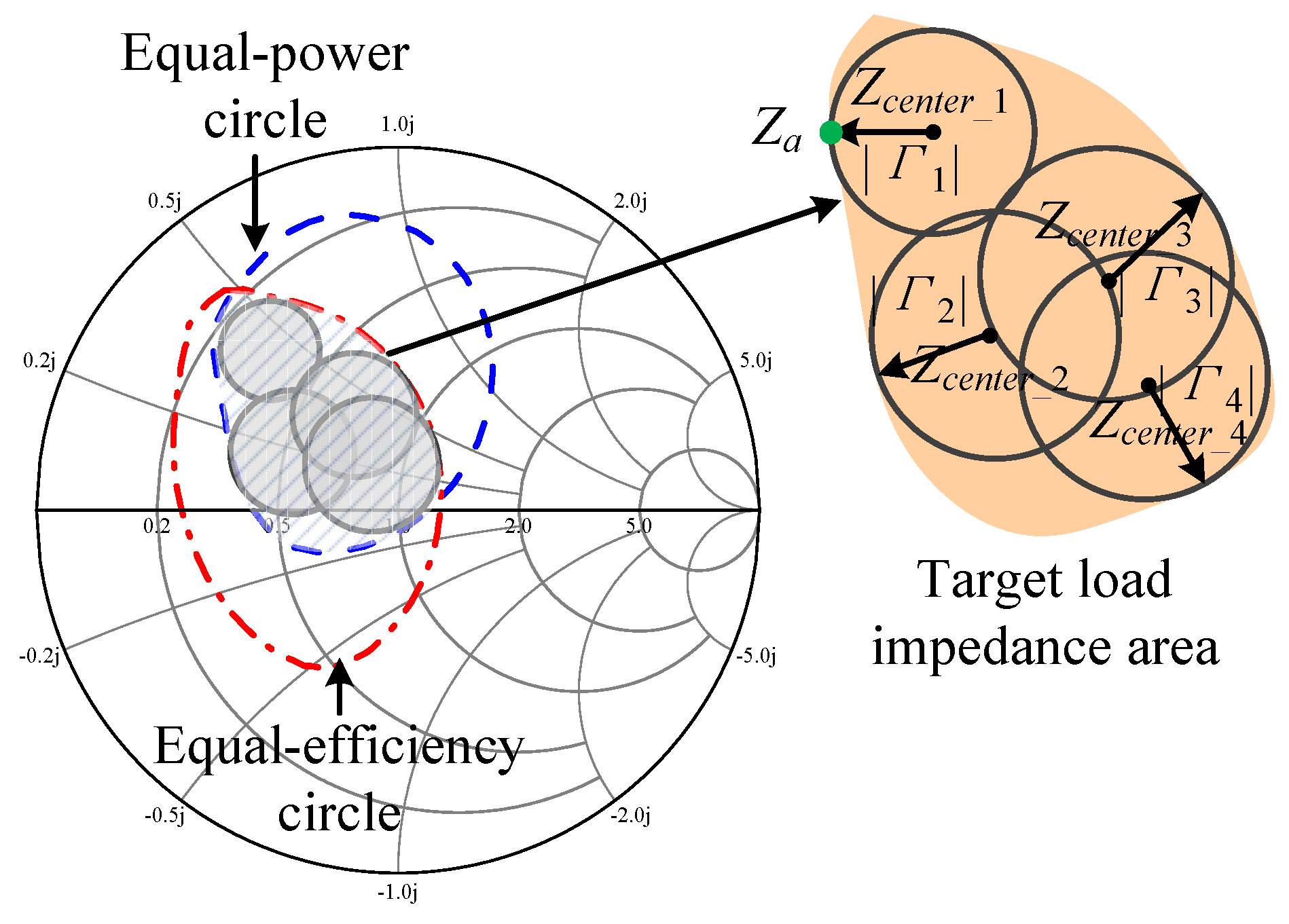

2.2. Load Impedance Region Determination Methods

2.3. Determination of ITN Phase Delay

2.4. Impedance-and-Phase Constrained Optimization

3. Design and Simulation of Dual-Mode Multi-Band DPA

3.1. Determination of the Impedance Constraint Region

3.2. Determination of Phase Delays of Carrier and Peaking ITNs

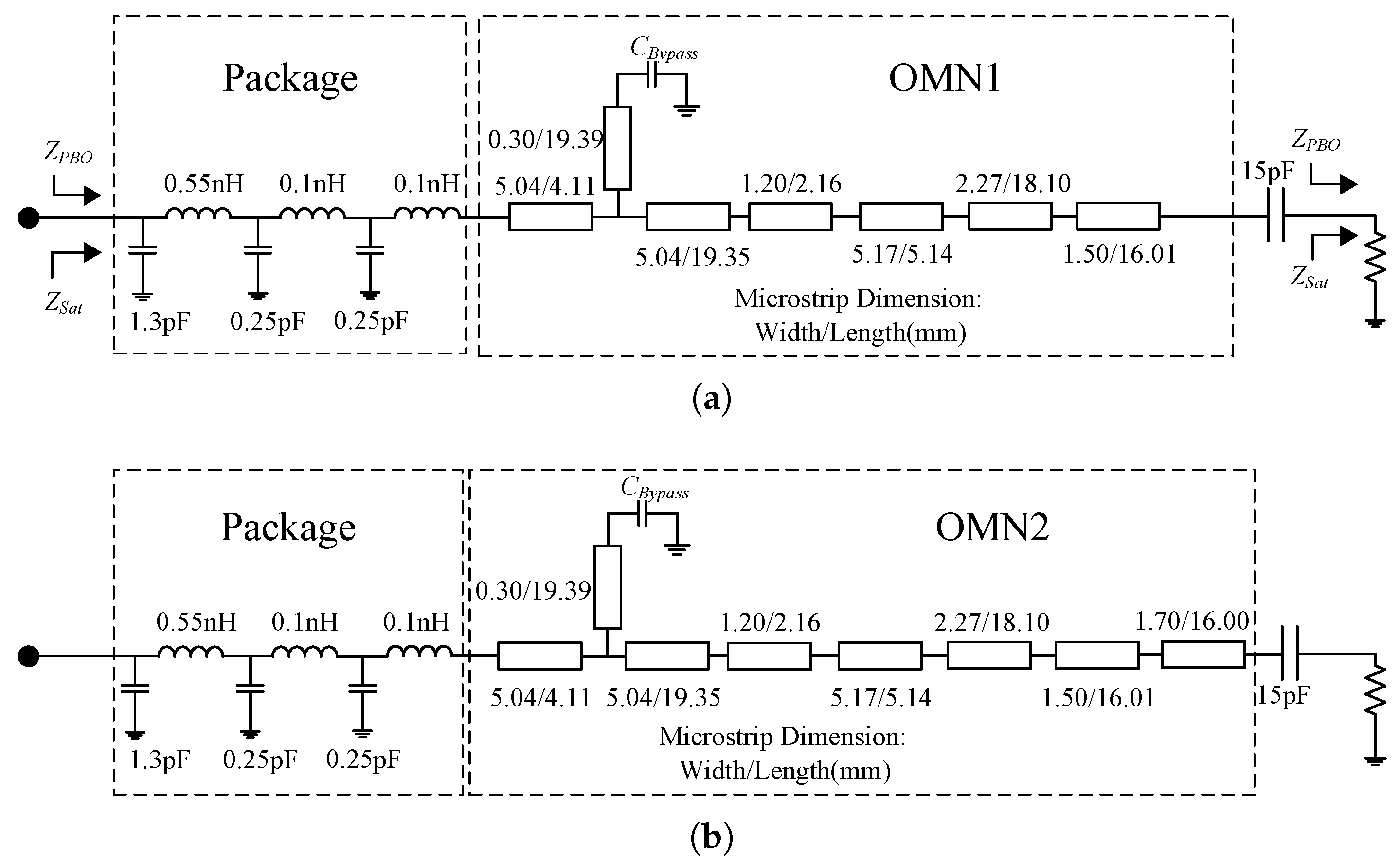

3.3. Design of ITNs

3.4. Simulation Results of Dual-Mode Multi-Band DPA

4. Fabrication and Measurement of Dual-Mode Multi-Band DPA

4.1. Continuous Wave Measurement

4.2. Modulated Signal Measurement

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

Abbreviations

| APSO | Adaptive particle swarm optimization |

| ADS | Advanced design system |

| CG | Current generator |

| DE | Drain efficiency |

| DPA | Doherty power amplifier |

| DPD | Digital predistortion |

| ITN | Impedance transformation network |

| LMN | Load modulation network |

| OMN | Output matching network |

| PA | Power amplifier |

| PAPR | Peak-to-average power ratio |

| PBO | Power back-off |

| PMN | Post-matching network |

Appendix A

| Variable Symbol | Definition |

|---|---|

| Target phase delay for the carrier ITN. | |

| Target phase delay for the peaking ITN. | |

| m | Phase delay parameter for the carrier ITN. |

| n | Phase delay parameter for the peaking ITN. |

| Design frequency of the low target band. | |

| Design frequency of the high target band. | |

| Target phase delay of the carrier ITN at . | |

| Target phase delay of the carrier ITN at . | |

| Target phase delay of the peaking ITN at . | |

| Target phase delay of the peaking ITN at . | |

| Phase delay parameter of the carrier ITN at . | |

| Phase delay parameter of the carrier ITN at . | |

| Phase delay parameter of the peaking ITN at . | |

| Phase delay parameter of the peaking ITN at . | |

| Phase delay optimization objective function. | |

| ITN phase delay at in Mode I. | |

| ITN phase delay at in Mode I. | |

| ITN phase delay at in Mode II. | |

| ITN phase delay at in Mode II. | |

| Target phase delay for the ITN at in Mode I. | |

| Target phase delay for the ITN at in Mode I. | |

| Target phase delay for the ITN at in Mode II. | |

| Target phase delay for the ITN at in Mode II. | |

| Load impedance of the ITN at a specific design frequency. | |

| Center impedance of the first impedance constraint circle. | |

| Radius of the first impedance constraint circle. | |

| Center impedance of the n-th impedance constraint circle. | |

| Radius of the n-th impedance constraint circle. | |

| Comprehensive impedance optimization objective function. | |

| F | Total optimization objective function. |

References

- Pitt, A.; Jindal, G.; Morris, K.; Cappello, T. A Broadband Asymmetrical Doherty Power Amplifier with Optimized Continuous Mode Harmonic Impedances. IEEE J. Microw. 2023, 3, 1120–1133. [Google Scholar] [CrossRef]

- Xia, J.; Yang, M.; Guo, Y.; Zhu, A. A Broadband High-Efficiency Doherty Power Amplifier with Integrated Compensating Reactance. IEEE Trans. Microw. Theory Tech. 2016, 64, 2014–2024. [Google Scholar] [CrossRef]

- Liu, T.; Wang, X.; Xin, Y.; Yang, X. PAPR Suppression for Angular-Domain-Based Massive Multiple-Input Multiple-Output Orthogonal Frequency Division Multiplexing System. Electronics 2023, 12, 4015. [Google Scholar] [CrossRef]

- Que, X.; Li, J.; Wang, Y. A Broadband Three-Way Series Doherty Power Amplifier with Deep Power Back-Off Efficiency Enhancement for 5G Application. Electronics 2024, 13, 1882. [Google Scholar] [CrossRef]

- Li, G.; Xu, W.; Nan, J.; Gao, M. Design of Efficient Concurrent Dual-Frequency Doherty Power Amplifier Based on Step Impedance Low-Pass Filter. Electronics 2023, 12, 4092. [Google Scholar] [CrossRef]

- Neveux, G.; Hallepee, C.; Passerieux, D.; Barataud, D. Non-Linear Simulation by Harmonic Balance Techniques of Load Modulated Power Amplifier Driven by Random Modulated Signals. Electronics 2024, 13, 947. [Google Scholar] [CrossRef]

- Kong, W.; Xia, J.; Zhou, X.; Zhang, T.; Zhang, W.; Bao, X. Bandwidth Extension of Three-Way Doherty Power Amplifier with Reactance Compensation Using Parallel Peaking Amplifiers. IEEE Access 2021, 9, 91661–91669. [Google Scholar] [CrossRef]

- Xia, J.; Xie, Z.; Kong, W.; Liu, R.; Zhao, Z.; Zhu, X.W. A 9 dB back-off dual-band asymmetric Doherty power amplifier using dual peaking amplifiers for reactance compensation. Microw. Opt. Technol. Lett. 2022, 64, 1145–1153. [Google Scholar] [CrossRef]

- Mehter, E.; Üçüncü, M. Radio Frequency (RF) Power Amplifier Design Providing High Power Efficiency in a Wide Dynamic Range. Electronics 2025, 14, 1435. [Google Scholar] [CrossRef]

- Moreno Rubio, J.J.; Noori, A. Doherty Power Amplifier Design via Differential Combining. Electronics 2024, 13, 3961. [Google Scholar] [CrossRef]

- Liu, H.Y.; Zhai, C.; Cheng, K.K.M. Novel Dual-Band Equal-Cell Doherty Amplifier Design with Extended Power Back-Off Range. IEEE Trans. Microw. Theory Tech. 2020, 68, 1012–1021. [Google Scholar] [CrossRef]

- Cui, H.; Leung, V.C.M.; Li, S.; Wang, X. LTE in the Unlicensed Band: Overview, Challenges, and Opportunities. IEEE Wirel. Commun. 2017, 24, 99–105. [Google Scholar] [CrossRef]

- Hussain, A.; Kildal, P.S.; Glazunov, A.A. Interpreting the Total Isotropic Sensitivity and Diversity Gain of LTE-Enabled Wireless Devices From Over-the-Air Throughput Measurements in Reverberation Chambers. IEEE Access 2015, 3, 131–145. [Google Scholar] [CrossRef]

- Shin, J.; Choi, W.; Chen, Y.; Jeon, H.; Bae, S.; Choi, Y.C.; Kang, H.; Koo, H.; Woo, Y.Y.; Lee, K.Y.; et al. Broadband Virtual-Stub Doherty Power Amplifier Using Asymmetric Structure. IEEE Access 2023, 11, 101425–101434. [Google Scholar] [CrossRef]

- Ahn, J.; Youn, Y.; Kim, B.; Lee, J.; Choi, N.; Lee, Y.; Kim, G.; Hong, W. Wideband 5G N77/N79 4 × 4 MIMO Antenna Featuring Open and Closed Stubs for Metal-Rimmed Smartphones with Four Slits. IEEE Antennas Wirel. Propag. Lett. 2023, 22, 2798–2802. [Google Scholar] [CrossRef]

- Sim, C.Y.D.; Liu, H.Y.; Huang, C.J. Wideband MIMO Antenna Array Design for Future Mobile Devices Operating in the 5G NR Frequency Bands n77/n78/n79 and LTE Band 46. IEEE Antennas Wirel. Propag. Lett. 2020, 19, 74–78. [Google Scholar] [CrossRef]

- Eid, M.A.E.; Abouelnaga, T.G.; Ibrahim, H.A.; Hamad, E.K.I.; Al-Gburi, A.J.A.; Alghamdi, T.A.H.; Alathbah, M. Highly Efficient GaN Doherty Power Amplifier for N78 Sub-6 GHz Band 5G Applications. Electronics 2023, 12, 4001. [Google Scholar] [CrossRef]

- Kong, W.; Zhong, Y.; Xia, J.; Zhou, X.Y.; Fu, H.; Dong, W.; Zhao, Z.M.; Zhu, X.W. Optimization Design of Broadband Doherty PA Using Fragment-Type Matching Network Based on Dual-State Impedance Objective Function. IEEE Trans. Circuits Syst. II Express Briefs 2024, 71, 1809–1813. [Google Scholar] [CrossRef]

- Nikandish, G.; Staszewski, R.B.; Zhu, A. Breaking the Bandwidth Limit: A Review of Broadband Doherty Power Amplifier Design for 5G. IEEE Microw. Mag. 2020, 21, 57–75. [Google Scholar] [CrossRef]

- Yang, Z.; Li, M.; Yao, Y.; Dai, Z.; Li, T.; Jin, Y. Design of Concurrent Dual-Band Continuous Class-J Mode Doherty Power Amplifier with Precise Impedance Terminations. IEEE Microw. Wirel. Compon. Lett. 2019, 29, 348–350. [Google Scholar] [CrossRef]

- Ren, M.; Gao, R.; Liu, S.; Li, M.; Shi, W.; Dai, Z.; Chen, S.; Pang, J. Design of Wideband Doherty Power Amplifier Using Inverse Continuous Class-F Mode. IEEE Trans. Circuits Syst. II Express Briefs 2024, 71, 4176–4180. [Google Scholar] [CrossRef]

- Abounemra, A.M.E.; Helaoui, M.; Ghannouchi, F.M. Design of an efficiency enhanced wideband Doherty power amplifier based on synthesising of a modified harmonic-control load modulation network. IET Microw. Antennas Propag. 2024, 18, 356–368. [Google Scholar] [CrossRef]

- Bai, G.; Dai, Z.; Wang, J.; Bi, C.; Shi, W.; Pang, J.; Li, M. Design of Broadband Doherty Power Amplifier Based on Single Loop Load Modulation Network. IEEE J. Emerg. Sel. Top. Circuits Syst. 2024, 14, 122–132. [Google Scholar] [CrossRef]

- Chen, Y.; Choi, W.; Shin, J.; Jeon, H.; Bae, S.; Bae, K.; Song, J.; Ju, Y.; Oh, H.; Kang, H.; et al. Comprehensive Analysis of Coupled Transmission Lines for Broadband High-Efficiency Doherty Power Amplifiers. IEEE Trans. Microw. Theory Tech. 2025; early access. [Google Scholar] [CrossRef]

- Alsulami, R.; Roblin, P.; Martinez-Lopez, J.I.; Hahn, Y.; Liang, C.; Popovic, Z.; Chen, V. A Novel 3-Way Dual-Band Doherty Power Amplifier for Enhanced Concurrent Operation. IEEE Trans. Microw. Theory Tech. 2021, 69, 4041–4058. [Google Scholar] [CrossRef]

- Guo, X.; Ye, J.; Wu, W. Dual-Band Class-X Doherty Power Amplifier with Large Frequency Ratio. IEEE Microw. Wirel. Technol. Lett. 2024, 34, 643–646. [Google Scholar] [CrossRef]

- Chen, X.; Chen, W.; Ghannouchi, F.M.; Feng, Z.; Liu, Y. A Broadband Doherty Power Amplifier Based on Continuous-Mode Technology. IEEE Trans. Microw. Theory Tech. 2016, 64, 4505–4517. [Google Scholar] [CrossRef]

- Chen, W.; Zhang, S.; Liu, Y.; Liu, Y.; Ghannouchi, F.M. A Concurrent Dual-Band Uneven Doherty Power Amplifier with Frequency-Dependent Input Power Division. IEEE Trans. Circuits Syst. I Regul. Pap. 2014, 61, 552–561. [Google Scholar] [CrossRef]

- Kalyan, R.; Rawat, K.; Koul, S.K. A Digitally Assisted Dual-Input Dual-Band Doherty Power Amplifier with Enhanced Efficiency and Linearity. IEEE Trans. Circuits Syst. II Express Briefs 2019, 66, 297–301. [Google Scholar] [CrossRef]

- Rawat, K.; Ghannouchi, F.M. Design Methodology for Dual-Band Doherty Power Amplifier with Performance Enhancement Using Dual-Band Offset Lines. IEEE Trans. Ind. Electron. 2012, 59, 4831–4842. [Google Scholar] [CrossRef]

- Jiang, S.; Liu, G.; You, M.; Wu, Y. A novel dual-band forward/inverse Doherty power amplifier. Int. J. Circuit Theory Appl. 2024, 52, 6073–6082. [Google Scholar] [CrossRef]

- Zhou, L.H.; Zhou, X.Y.; Chan, W.S. Compact Dual-Passband Doherty Power Amplifier Based on Stub-Loaded Stepped-Impedance Transformer. IEEE Trans. Circuits Syst. I Regul. Pap. 2024, 71, 99–109. [Google Scholar] [CrossRef]

- Kong, W.; Chen, Y.; Xia, J.; Ni, Z.; Ni, S.; Zhang, W.; Zhu, X.W. Design of Tri-Band Doherty Power Amplifier Using Phase and Impedance Constrained Optimization. Microw. Opt. Technol. Lett. 2025, 67, e70100. [Google Scholar] [CrossRef]

- Tang, Y.; Feng, W.; Zhou, X.; Wang, W.; Gu, L.; Xue, Q.; Che, W. Broadband High-Efficiency Dual-Mode Doherty Power Amplifier Using Hybrid F/F–1 Continuous-Mode Technology. IEEE Trans. Circuits Syst. I Regul. Pap. 2023, 70, 2651–2664. [Google Scholar] [CrossRef]

- Han, Y.; Gao, R.; Liu, S.; Li, M.; Shi, W.; Dai, Z.; Chen, S.; Pang, J. Enhanced Dual-Mode Reciprocal Doherty Power Amplifier Using Modified Combining Load and Parameter Sweeping Analysis. IEEE Trans. Circuits Syst. I Regul. Pap. 2024, 71, 3086–3097. [Google Scholar] [CrossRef]

- Liu, S.; Pang, J.; Gao, R.; Yao, T.; Cai, T.; Li, M.; Shi, W.; Dai, Z. Triple-Mode Reciprocal Doherty Power Amplifier with Multi-Band Operation and Extended High Efficiency Range. IEEE Trans. Circuits Syst. I Regul. Pap. 2023, 70, 1928–1939. [Google Scholar] [CrossRef]

- Qu, Y.; Crupi, G.; Cai, J. A Broadband PA Design Based on Bayesian Optimization Augmented by Dynamic Feasible Region Shrinkage. IEEE Microw. Wirel. Compon. Lett. 2022, 32, 1139–1142. [Google Scholar] [CrossRef]

- Chen, P.; Xia, J.; Merrick, B.M.; Brazil, T.J. Multiobjective Bayesian Optimization for Active Load Modulation in a Broadband 20-W GaN Doherty Power Amplifier Design. IEEE Trans. Microw. Theory Tech. 2017, 65, 860–871. [Google Scholar] [CrossRef]

- Mengozzi, M.; Gibiino, G.P.; Angelotti, A.M.; Santarelli, A.; Florian, C.; Colantonio, P. Automatic Optimization of Input Split and Bias Voltage in Digitally Controlled Dual-Input Doherty RF PAs. Energies 2022, 15, 4892. [Google Scholar] [CrossRef]

- Ni, Z.; Xia, J.; Zhou, X.; Kong, W.; Zhang, H.; Yu, C.; Zhu, X.W. Design and Analysis of Optimization Method for Ultra-Wideband PA Based on Improved MOEA/D Algorithm Using Mixed Objective Function. IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst. 2024; early access. [Google Scholar] [CrossRef]

- Hao, Z.; Qu, Y.; Huang, J.; Crupi, G.; Cai, J. Automatic multi-objective particle swarm optimization method for effective Doherty power amplifier design. Int. J. Numer. Model. Electron. Netw. Devices Fields 2024, 37, e3204. [Google Scholar] [CrossRef]

- Li, C.; You, F.; Yao, T.; Wang, J.; Shi, W.; Peng, J.; He, S. Simulated Annealing Particle Swarm Optimization for High-Efficiency Power Amplifier Design. IEEE Trans. Microw. Theory Tech. 2021, 69, 2494–2505. [Google Scholar] [CrossRef]

- Fan, Z.; Hao, Z.; Huang, J.; Cai, J. Design of RF-Input Sequential LMBA Using PSO Algorithm with Improved Linear Self-Adaptive Hyper-Parameters. IEEE Trans. Microw. Theory Tech. 2024, 72, 6414–6425. [Google Scholar] [CrossRef]

- Li, M.; Pang, J.; Li, Y.; Zhu, A. Ultra-Wideband Dual-Mode Doherty Power Amplifier Using Reciprocal Gate Bias for 5G Applications. IEEE Trans. Microw. Theory Tech. 2019, 67, 4246–4259. [Google Scholar] [CrossRef]

- Pang, J.; Dai, Z.; Li, Y.; Li, M.; Zhu, A. Multiband Dual-Mode Doherty Power Amplifier Employing Phase Periodic Matching Network and Reciprocal Gate Bias for 5G Applications. IEEE Trans. Microw. Theory Tech. 2020, 68, 2382–2397. [Google Scholar] [CrossRef]

- Jiang, H.; Xu, W.; Chen, Q. Evaluating aroma quality of black tea by an olfactory visualization system: Selection of feature sensor using particle swarm optimization. Food Res. Int. 2019, 126, 108605. [Google Scholar] [CrossRef] [PubMed]

- Bai, S.; Yang, Q.; Niu, K.; Zhao, B.; Zhou, L.; Yuan, Y. Discrete element-based optimization parameters of an experimental corn silage crushing and throwing device. Trans. ASABE 2021, 64, 1019–1026. [Google Scholar] [CrossRef]

- Pang, Y.; Li, H.; Tang, P.; Chen, C. Synchronization optimization of pipe diameter and operation frequency in a pressurized irrigation network based on the genetic algorithm. Agriculture 2022, 12, 673. [Google Scholar] [CrossRef]

- Li, Y.; Xu, L.; Gao, Z.; Lu, E.; Li, Y. Effect of vibration on rapeseed header loss and optimization of header frame. Am. Soc. Agric. Biol. Eng. 2021, 64, 1247–1258. [Google Scholar] [CrossRef]

- Yang, Q.; Cai, J.; Zhou, X.; Ahamd, I.; Hu, J.; Gu, J. The optimization of topological mechanism and dimension design of parallel transplanting machine in greenhouse. AMA Agric. Mech. Asia Afr. Lat. Am. 2021, 52, 61–66. Available online: https://www.cabidigitallibrary.org/doi/full/10.5555/20220472230 (accessed on 2 November 2022).

- Ayim, I.; Ma, H.; Alenyorege, E.A. Optimizing and predicting degree of hydrolysis of ultrasound assisted sodium hydroxide extraction of protein from tea (Camellia sinensis L.) residue using response surface methodology. J. Food Sci. Technol.-Mysore 2018, 55, 5166–5174. [Google Scholar] [CrossRef]

- Xu, F.; Wang, B.; Hong, C.; Telebielaigen, S.; Nsor-Atindana, J.; Duan, Y.; Zhong, F. Optimization of spiral continuous flow-through pulse light sterilization for Escherichia coli in red grape juice by response surface methodology. Food Control 2019, 105, 8–12. [Google Scholar] [CrossRef]

- Bonah, E.; Huan, X.; Yi, R.; Aheto, J.H.; Osae, R.; Golly, M. Electronic nose classification and differentiation of bacterial foodborne pathogens based on support vector machine optimized with particle swarm optimization algorithm. J. Food Process Eng. 2019, 42, e13236. [Google Scholar] [CrossRef]

- Tang, N.; Sun, J.; Yao, K.; Zhou, X.; Tian, Y.; Cao, Y.; Nirere, A. Identification of Lycium barbarum varieties based on hyperspectral imaging technique and competitive adaptive reweighted sampling-whale optimization algorithm-support vector machine. J. Food Process Eng. 2021, 44, e13603. [Google Scholar] [CrossRef]

- Xia, J.; Chen, W.; Meng, F.; Yu, C.; Zhu, X. Improved Three-Stage Doherty Amplifier Design with Impedance Compensation in Load Combiner for Broadband Applications. IEEE Trans. Microw. Theory Tech. 2019, 67, 778–786. [Google Scholar] [CrossRef]

- Kalyan, R.; Rawat, K.; Koul, S.K. Reconfigurable and Concurrent Dual-Band Doherty Power Amplifier for Multiband and Multistandard Applications. IEEE Trans. Microw. Theory Tech. 2017, 65, 198–208. [Google Scholar] [CrossRef]

- Li, X.; Helaoui, M.; Ghannouchi, F.; Chen, W. A Quad-Band Doherty Power Amplifier Based on T-Section Coupled Lines. IEEE Microw. Wirel. Compon. Lett. 2016, 26, 437–439. [Google Scholar] [CrossRef]

- Nghiem, X.A.; Negra, R. Design of a concurrent quad-band GaN-HEMT Doherty power amplifier for wireless applications. In Proceedings of the 2013 IEEE MTT-S International Microwave Symposium Digest (MTT), Seattle, WA, USA, 2–7 June 2013. [Google Scholar] [CrossRef]

| CG1 | CG2 | ITN1 | ITN2 | |

|---|---|---|---|---|

| Mode I | carrier PA | peaking PA | carrier ITN | peaking ITN |

| Mode II | peaking PA | carrier PA | peaking ITN | carrier ITN |

| Frequency (GHz) | 2.0 GHz | 2.8 GHz | 2.5 GHz | 3.3 GHz |

| 13.86 + j × 12.24 | 20.73 + j × 8.15 | 14.79 + j × 6.8 | 12.38 + j × 3.77 | |

| 0.198 | 0.22 | 0.2 | 0.104 | |

| 23.3 + j × 12.45 | 27.5 + j × 13.72 | 24.68 + j × 5.41 | 18.16 + j × 1.49 | |

| 0.208 | 0.148 | 0.098 | 0.154 | |

| 32.83 + j × 6.66 | 21.17 + j × 4.91 | 17.98 + j × 4.48 | 24.96 + j × 1.81 | |

| 0.139 | 0.145 | 0.144 | 0.078 | |

| 22.17 + j × 4.91 | 11.87 + j × 8.8 | 11.87 + j × 8.8 | 12.48 + j × 1.25 | |

| 0.139 | 0.188 | 0.181 | 0.109 |

| Mode I @ 2.0 GHz | Mode I @ 2.8 GHz | Mode II @ 2.5 GHz | Mode II @ 3.3 GHz | |||

|---|---|---|---|---|---|---|

| ITN1 | m | 1 | 2 * | n | 1 | 2 * |

| ITN2 | n | 1 | 2 * | m | 2 | 3 * |

| Width/Length (mm) | Value |

|---|---|

| 5.04/4.11 | |

| 5.04/19.35 | |

| 1.20/2.16 | |

| 5.17/5.14 | |

| 2.27/18.10 | |

| 1.50/16.01 | |

| 0.30/19.39 |

| Ref. | Freq. (GHz) | Pmax (dBm) | Gain (dB) | DEsat (%) | DE6dB (%) |

|---|---|---|---|---|---|

| R. Kalyan [56] | 1.50/2.14 & 1.85/2.55 | 43.2 | 10.0–13.0 | 62.0–70.0 | 52.0–56.0 |

| X. Li [57] | 0.73/1.65 2.67/3.57 | 42.5 | 9.0–14.0 | 52.7–73.1 | 44.6–58.9 |

| X. A. Nghiem [58] | 0.95/1.50 2.14/2.65 | 44.2 | 9.0–13.0 | 43.0–61.0 | 32.0–56.0 |

| T.W. | 2.00/2.80 & 2.50/3.30 | 44.1 | 9.5–14.7 | 53.7–68.6 | 49.4–55.7 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Tao, M.; Chen, Y.; Kong, W.; Ni, S.; Zheng, Z.; Xia, J. Design of Dual-Mode Multi-Band Doherty Power Amplifier Employing Impedance-and-Phase Constrained Optimization. Electronics 2025, 14, 2078. https://doi.org/10.3390/electronics14102078

Tao M, Chen Y, Kong W, Ni S, Zheng Z, Xia J. Design of Dual-Mode Multi-Band Doherty Power Amplifier Employing Impedance-and-Phase Constrained Optimization. Electronics. 2025; 14(10):2078. https://doi.org/10.3390/electronics14102078

Chicago/Turabian StyleTao, Meiyu, Yunqin Chen, Wa Kong, Shaohua Ni, Zhaowen Zheng, and Jing Xia. 2025. "Design of Dual-Mode Multi-Band Doherty Power Amplifier Employing Impedance-and-Phase Constrained Optimization" Electronics 14, no. 10: 2078. https://doi.org/10.3390/electronics14102078

APA StyleTao, M., Chen, Y., Kong, W., Ni, S., Zheng, Z., & Xia, J. (2025). Design of Dual-Mode Multi-Band Doherty Power Amplifier Employing Impedance-and-Phase Constrained Optimization. Electronics, 14(10), 2078. https://doi.org/10.3390/electronics14102078