Abstract

Dual-stage cascaded dc systems are some of the most widely applied power interfaces in dc distributed power systems. However, in some practical situations, these systems might be unstable, especially if they incorporate tightly regulated load converters that operate as constant power loads (CPLs), whose power fluctuations could exert a cascading impact on the operation of the systems. Existing studies tend to describe the instability phenomena using bifurcation diagram analysis and the loci of eigenvalue analysis. However, it is usually difficult to derive the explicit expressions of the stability criterion. This paper addresses the large-signal stability issue of the dual-stage cascaded dc systems from a standpoint of load power and obtains the explicit form large-signal stability boundary in terms of load power by using Lyapunov-type mixed potential theory. Moreover, the prototype dual-stage cascaded dc system, in which the control strategies for the feeder converter and the load converter are different, is used as an example in this study. According to the results, the system remains stable when the load power is in [5.8, 23.2] W. When load power is less than 5.8 W or increased to [23.2, 32.8] W, the system is in a period-2 subharmonic oscillation state. Moreover, when the load power exceeds 32.8 W, the system falls into a chaotic state. The deduced boundary is highly consistent with the analysis results of both a bifurcation diagram and Jacobian matrix based analysis. Finally, both circuit-level simulation and experimental results validate the effectiveness of the load power stability boundary.

1. Introduction

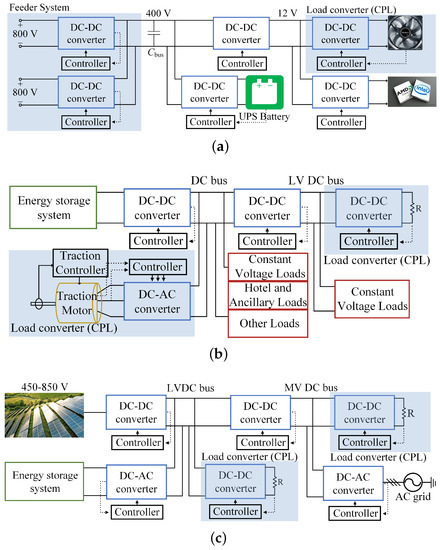

With the rapid growth of dc microgrids and distribution worldwide, dc distribution technology has become more popular than ever, and many innovations have been presented [1,2]. Among various power interfaces in dc distributed power systems, the cascaded dc system is one of the main application forms in practice [3,4]. However, this kind of system, such as two cascading dc–dc converters—as presented in Figure 1—may lose stability due to the load converter, which behaves as a CPL and presents itself as the negative impedance to the feeder converter. In order to address this problem, scholars have conducted numerous theoretical studies and practical investigations [5,6,7,8].

Figure 1.

Some typical dual-stage cascaded dc systems [7,8]: (a) Data center dc power supply system. (b) Plug-in hybrid vehicle power supply system. (c) PV-storage integrated grid connected power supply system [7,8].

In this field, Middlebrook’s impedance criterion and its improvements may be one of three current state-of-the-art analytical methods. The other two great methods are the state-space average model (SSA) and the discrete-mapping model (DMM) [8,9]. At the same time, each of these methods has its scope of applications and limitations. For instance, the impedance-based criteria have a wide range of applications but with limited accuracy [10]. Although the SSA-based approach can be applied to explore the slow-scale instability (Hopf bifurcation) of the systems, it cannot capture the fast-scale instability (period-doubling bifurcation). The DMM-based approach can be exploited to analyze both of the instability situations, but it has a bit complicated modeling process, which cannot obtain the explicit criterion in some occasions [4,7]. Based on these modeling methods, Nyquist plot, limit cycle analysis, bifurcation diagram analysis, Jacobian matrix, and the loci of eigenvalue analysis can be performed for the stability analysis of cascaded dc systems [4,5,7,8,9,10,11,12,13,14,15].

It is worth mentioning that in cascaded dc systems, both the control strategies and the switching frequencies of the dc-dc converters might be significantly different. Under this situation, modeling and analytical processes become more challenging [4]. Therefore, it is possible to model and analyze dual-stage cascaded dc systems in the form of feeder dc-dc converters with CPLs, which can simplify the complexity of the model to a certain extent.

From the above equivalent perspective, some research works have been carried out successively. For example, in [9], the authors describe function and Floquet theory in combination to model and quantify dc-dc converters with CPLs. In [10], low frequency oscillation phenomena were observed in such converters by the loci of eigenvalue and bifurcation diagram based techniques, even though the design of the converter satisfied Middlebrook’s impedance criterion. In [11], a fast-scale stability boundary was derived for such converters. In [12], the fast-scale instability phenomena were observed in such converters and captured by 3-D bifurcation diagrams, to name but a few.

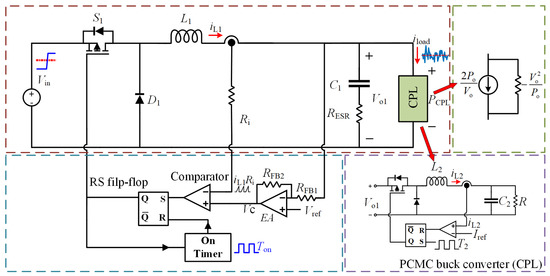

According to the existing achievements, it can be perceived that, in most modeling and stability analysis works of cascaded dc systems, the different switching frequencies of the feeder converter and the load converter are considered, but current studies tend to focus on the cases where the feeder converter and the load converter adopt the same control strategy possibly for the reason of simplicity. Moreover, it is usually difficult to derive the explicit expressions of the stability criterion based on the aforementioned analysis methods, especially when a bifurcation diagram and Jacobian matrix analyses are employed. Therefore, this work takes a dual-stage cascaded dc-dc converter as an example. The control strategies of the feeder and the load converters are different, where a current mode constant on-time controller (CMCOTC) is adopted for the feeder Buck converter and a peak-current mode controller (PCMC) is employed for the load Buck converter. Figure 2 shows the structure of the prototype system.

Figure 2.

The prototype dual-stage cascaded dc system.

Overall, the main contributions of this paper can be summarized as follows:

- (1)

- A large-signal model is constructed for a dual-stage cascaded dc system, in which two different control strategies are adopted for the feeder and the load stage.

- (2)

- A large-signal stability analysis is performed for the prototype system from the perspective of load power.

- (3)

- Lyapunov-type mixed potential theory is applied to obtain the explicit expression of the large-signal stability criterion of the system.

- (4)

- Circuit level simulation and an experimental prototype verify the correctness of the theoretical analysis.

The rest of the work can be organized as follows: In Section 2, the model of the prototype system is established based on the discrete-mapping model. In Section 3, large-signal stability analysis is performed by using the Lyapunov-type mixed potential theory, and a load power oriented explicit criterion is deduced. Moreover, a bifurcation diagram analysis and Jacobian matrix based analysis are conducted for comparison. The effectiveness of this work is validated by both simulation and experiments in Section 4. In Section 5, the conclusion is drawn.

2. Modeling of the Prototype Dual-Stage Cascaded dc System

As depicted in Figure 2, one can find that the prototype system can be deemed as a CMCOTC dc-dc buck converter with CPL, where is the input voltage, is the freewheeling diode, and and are the inductor and filtering capacitor, respectively. The power switching MOSFET is adopted to control the duty cycle according to the output of the R-S flip-flop, which is determined by the outputs of the comparator and the on timer. Two closed loops, the output voltage loop and the inductor current loop, appear as the inputs of the comparator, in which the output voltage loop employs the simple proportional compensation network by using an operational amplifier EA with two resistors and . The inductor current loop adopts a sensing resistor , the output of which is exploited to compare with the output of the operational amplifier EA. Consequently, when , the current signal acquired, is less than , the output of the voltage compensation network, the Q port of the RS flip-flop gives a turn-on instruction to the switch . After a predetermined time, , of the on timer, the switch, , is forced off.

2.1. CPL Modeling

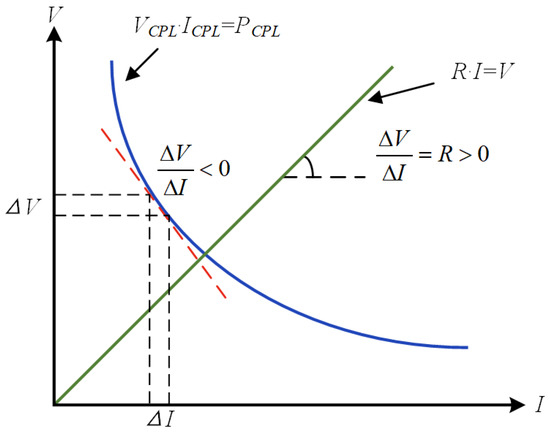

As discussed in Section 1, a tightly regulated load converter may behave as a CPL. The V-I characteristics of this kind of load presents an inverse proportional function of nonlinear relationship as Figure 3 shows. Therefore, many existing techniques for linear resistive loads are not able to be applied in such situations. To address this concern, this section tries to provide solutions from the perspective of mathematical operation.

Figure 3.

V-I characteristics of CPL and conventional resistive load [7].

It is known that the current drawn by a CPL increases/decreases with decrease/increase with the input voltage. Based on [11], a CPL can be described by

where is the current drawn by the CPL and is the input voltage of CPL. The variation of the current in Equation (1) can be governed by the following equation at the given operating point:

where and are the power and voltage of the given operating point, respectively. As a result, a CPL can be linearized around its operating point, and the V-I curve of a CPL can be approximated by its tangent line in a small range, as depicted in Figure 2 and Equation (3):

According to the above transformation, a CPL can be regarded as a current source in parallel with a dynamic negative resistance [7]:

where and are

respectively.

2.2. Modeling of the Prototype System

According to [4], the system in Figure 2 can be deemed a a piecewise nonlinear system, the state equations of the system can be expressed in the matrix form as

where x = [,]. and are the state matrices in operation state i. is the vector of the external inputs. Based on Figure 2, the corresponding state matrices and the input vector are written as follows

The switching boundary in different operation states is

where is the inductor current of the nth switching cycle. is the output of output voltage compensation network, which is given by

where F is the feedback coefficient, which is expressed as

Basically, the inductor current is assumed to rise and fall linearly. Thus, the duty cycle of the system can be obtained by

where is the inductor current at the time instant that the switching keeps on for . Assume that the duration of each operation state is , thus in one switching cycle, . If the system operates in continuous conduction mode (CCM), i = 2. Hence, the discrete-mapping function of each state can be described as

where I is an identity matrix, and the time interval depends on the time transient when Equation (8) holds. Let and be the first state and second state of each switching period, respectively, the discrete-mapping model can be obtained by

3. Load Power Oriented Large-Signal Stability Analysis

3.1. Derivation of Load Power Oriented Stability Boundary

Section 1 mentioned that bifurcation diagrams and eigenvalues of the Jacobian matrix are mainly utilized in existing studies to analyze the large signal stability. However, it is difficult to obtain explicit expressions for the stability boundary, in particular, the CPL of the discrete-mapping model exists as a non-linear form. Therefore, an analytical approach based on Brayton–Moser’s mixed potential function is introduced. First proposed in [16,17] and generalized in [18], Brayton–Moser’s mixed potential theory is the most used methodology in the stability of nonlinear RLC networks. In [19], the large-signal stability analysis of the dc distribution network with constant power loads via Brayton–Moser’s mixed potential theory is carried out, and a certain condition that the equilibrium is a local minimum is derived. In this part of the analysis, the analytical approach is based on developing a Lyapunov-type mixed potential function using the elements and topology of the studied circuit. This circuit may contain nonlinear resistances, inductances, or capacitors. Brayton and Moser propose five theorems for analyzing the circuit stability for large disturbances. To determine the explicit stability boundary, we have to construct a mixed potential function that satisfies one of Brayton–Moser’s theorems under certain conditions.

According to the third stability theorem of the mixed potential function, the algebraic expressions of the discrete-mapping model Equation (12) can be equivalently substituted by the constant voltage [20,21] source, controlled sources and resistances. Hence, the current potential function of non-energy storage elements in the circuit can be expressed by

where k = 1 + . The power stored in output filtering capacitor of the system is

Summing and simplifying Equations (14) and (15), the mixed potential function of the system can be written as

In terms of Equation (16) and the unified form of the mixed potential function, the current potential function matrix of the system can be obtained by

The voltage potential function matrix of the system is

The second-order partial derivative of the current potential function matrix with respect to the current is

where = . Then the second-order partial derivative of the voltage potential function matrix with respect to the voltage is

Under the assumption of ≥ 0, according to the third stability theorem of mixed potential function, the minimum eigenvalues and are defined by

When and in the circuit satisfy , and if , it yields

that means when t , all the solutions of the model converge to the equilibrium point, i.e., the system reaches stable state even if there are large signal disturbances. Thus, one can deduce the load power related stability boundary by

where = . Likewise, when choosing the parameters of the system, the condition also needs to be considered, which satisfies ≥ 0.

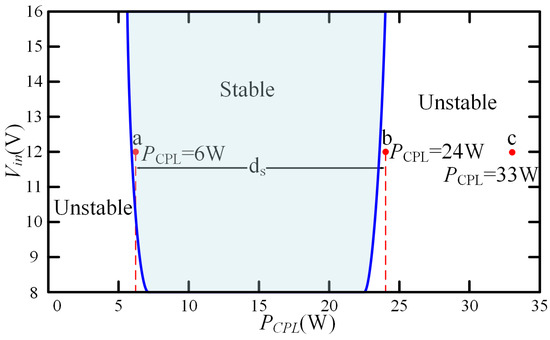

By introducing the parameters in Table 1 to the criterion formula Equation (23), one can paint the full picture of the stable region of the system Equation (13) on the plane of (), as depicted in Figure 4. From Figure 4, it can be seen that as decreases, the system has a lower tolerance for the stability operation range, and the system will lose stability when the load power exceeds a certain range. Based on the analytical form stability criterion Equation (23), engineers can determine the load power range when the system remains stable under diverse dynamics conditions. This stability criterion derived produces more straightforward guidance for the design of cascaded dc systems from the load power perspective.

Table 1.

Parameters of the system.

Figure 4.

Stability boundary of the system as varies from 8 to 16 V and varies from 0 W to 35 W.

To verify the effectiveness of the stability criterion, the bifurcation diagram and the eigenvalues trajectory of Jacobian matrix are, respectively, obtained in Section 3.2 and Section 3.3.

3.2. Bifurcation Diagram Based Analysis

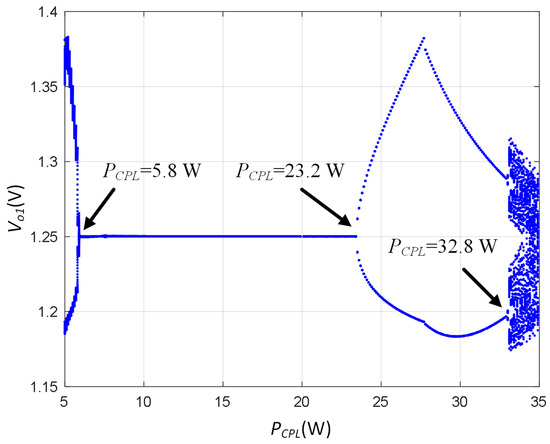

Introduce the parameters of the system listed in Table 1 to the model. By setting output voltage as the sampled parameter and varying the power of the load from 5 to 35 W, Figure 5 shows the bifurcation diagram of the output voltage with the load power. The last 80 points of the discrete-mapping model are adopted at the corresponding point of each load power value of the bifurcation diagram.

Figure 5.

Bifurcation diagram of from 5 to 35 W.

From Figure 5, it can be seen that the system keeps stable when is from 5.8 to 23.2 W. When is less than 5.8 W, the system goes into a period-2 subharmonic oscillation state. When is between 23.2 and 32.8 W, the system is in a period-2 subharmonic oscillation state with a wider sampled voltage. When is further increased to 32.8 W, the system falls into chaotic state. In Figure 4, the term is the stability interval at = 12 V depicted by the bifurcation diagram. Within a reasonable margin of error, the explicit operational boundary and the stability interval reveal a good relevance.

3.3. Jacobian Matrix Based Analysis

A Lyapunov-stability theory based analysis is offered in this part. The dynamics of the system in a small neighborhood of the equilibrium point or orbit can be inspected by determining the eigenvalues of the Jacobian of the system. By varying the system parameters and tracking the loci of the eigenvalues trajectory in relation to the unit circle, the stability information such as the classifications of bifurcations and the boundaries of the stable operating regions can be identified [22,23,24].

Defining x = is the state variable vector of Jacobian matrix of the system [10]. Based on Equations (1), (6), (7) and (9), the equilibrium point of the system can be expressed as

The Jacobian matrix can be obtained by the partial derivative of perturbing the state equation near the equilibrium point [25], given by

Supposing that

Then, the Jacobian matrix can be written in terms of Equation (25), (26) and linearized CPL, as shown Equation (27).

Then, the eigenvalues can be calculated by solving of the characteristic equation as

where I is an 4 × 4 identity matrix. If all eigenvalues are inside the unit circle, the system is stable. If a pair of complex eigenvalues move out of the unit circle smoothly while all other eigenvalues stay inside the unit circle, the system undergoes a slow-scale bifurcation. If a negative real eigenvalue moves out of the unit circle at (−1, 0), a fast-scale bifurcation occurs. If any eigenvalue jumps across the unit circle, a nonsmooth (border collision) bifurcation occurs [10].

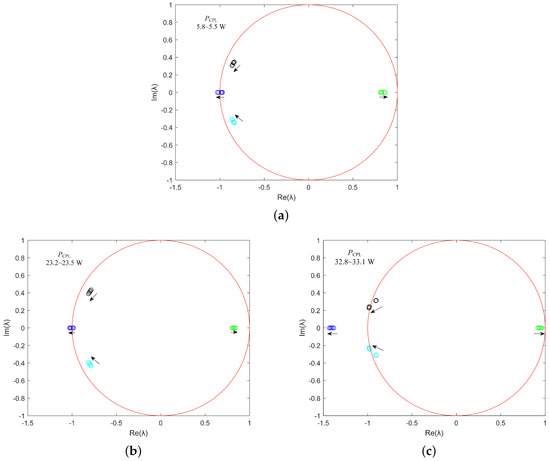

After combining Equation (28) and the parameters listed in Table 1, several typical eigenvalues are shown in Table 2, and the loci of the eigenvalues is shown in Figure 6.

Table 2.

Eigenvalues at typical load power.

Figure 6.

Loci of eigenvalues: (a) varies from 5.8 to 5.5 W. (b) varies from 23.2 to 23.5 W. (c) varies from 32.8 to 33.1 W.

In Figure 6a, there are eigenvalues crossing the unit circle from right to left at the negative real axis (−1, 0) when decreases from 5.8 to 5.5 W, and the rest of eigenvalues are within the unit circle, indicating that a period-doubling bifurcation emerges in the system, which is stable at the beginning. When increases from 23.2 to 23.5 W, a phenomenon from steady state to period-doubling bifurcation can be observed shown in Figure 6b. In Figure 6c, when increases from 32.8 to 33.1 W, there are eigenvalues keeping away from the boundary of the unit circle (−1, 0) with pairs of complex eigenvalues jumping cross the unit circle, indicating that a border collision bifurcation occurs after period-doubling bifurcation. Under the border collision bifurcation, the nonlinear dynamical behaviors of the system may change dramatically such as a direct jump from a periodic orbit to a chaotic orbit. The essential cause of this phenomenon is the bounded duty cycle of the switching converter [26].

4. Circuit-Level Simulation and Experimental Validations

4.1. Circuit-Level Realization and Simulation

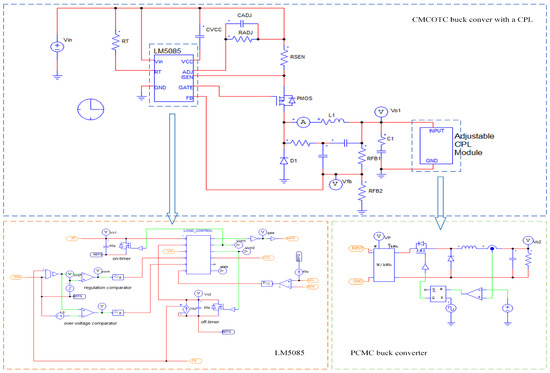

The simulation of the prototype cascaded dc system is constructed in PSIM in Figure 7. The commercial chip LM5085 is used in the subsequent experiment to implement the CMCOTC function, which allows 100% duty cycle operation to achieve low dropout and a wide input voltage range. Hence, an imitation LM5085 chip is established as Figure 7 shows.

Figure 7.

Schematic of CMCOTC buck converter with CPL in simulation.

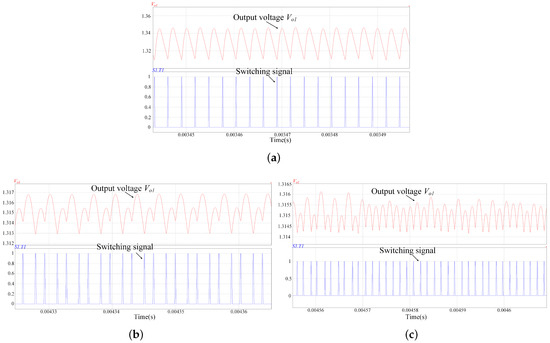

Owing to a tightly-regulated power converter behaves as a CPL, which may not behave as an ideal CPL in all situations and this does not present worst situation from a stability point of view [27,28,29]. Thus, a PCMC buck converter with 100kHz switching frequency is regulated to the feeder converter as a CPL in Figure 7. The parameters of the system refer to Table 1. With selected points a, b, and c—shown in Figure 4—as the sample points, the output voltage waveforms are shown in Figure 8 at = 6 W, 24 W, and 33.1 W, respectively. When = 6 W, the system is stable. When = 24 W, the system works in a period-2 subharmonic oscillation state. When increases to 33.1 W, the system is in a chaotic state.

Figure 8.

Simulation waveforms of the system with varying: (a) = 6 W. (b) = 24 W. (c) = 33.1 W.

4.2. Experimental Results

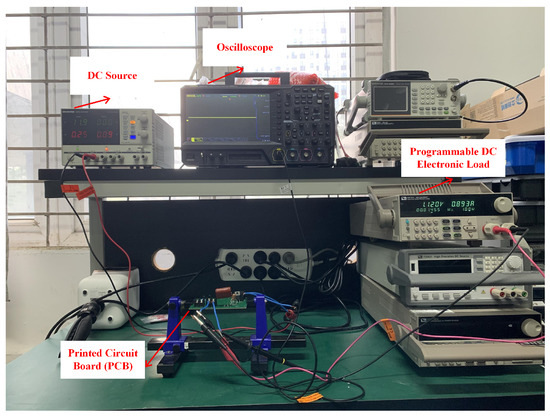

In order to further verify the analysis and simulation, an experimental platform is constructed, as shown in Figure 9, in which a CMCOTC Buck converter is connected with a programmable dc electronic load. While this load works in a constant current mode and the input current is 0∼12 A, the rise rate of the sink current is more than 0.001 A/S but no more than 0.2 A/S, and the fall rate remains between 0.01 A/S and 1.6 A/S. Obviously, in practice, the programmable dc electronic load meets the requirements of the dynamical characteristic of an ideal CPL. The parameters are the same as Table 1 and the simulation. Figure 10 shows the experimental output voltage waveforms of the system.

Figure 9.

Experimental platform of the system.

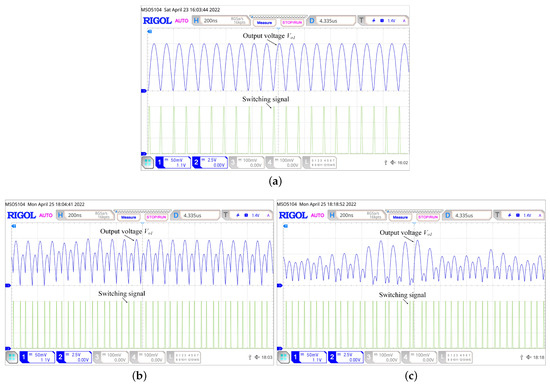

Figure 10.

Experimental waveforms of the system with varying: (a) = 6 W. (b) = 24 W. (c) = 33.1 W.

5. Conclusions

This work discusses a large-signal stability analysis of a dual-stage cascaded dc system from the perspective of load power. In this cascaded system, the control strategies of the feeder and the load converters are different, where a CMCOTC is adopted for the feeder buck converter and a PCMC is employed for the load buck converter. During the modeling process, the load buck converter is equivalent to a CPL for obtaining the discrete-mapping model. Through the use of Lyapunov-type mixed potential theory, an explicit analytical discriminant condition for the stability criterion is deduced, and the full picture of the stable region is depicted in order to guide the design of such systems. According to the results, the system remains stable when the load power is approximately maintained at [6, 24] W. In order to validate the proposed approximation of the region of attraction, the full picture of the discrete-mapping model-based large signal analysis is painted as a reference, in which both a bifurcation diagram and the loci of eigenvalue are contained. Meanwhile, both circuit-level simulations in PSIM and laboratory experiments are carried out to validate the specific boundary conditions.

Author Contributions

Writing—original draft, Z.C.; Conceptualization, Supervision, X.C.; Data curation, F.Z.; Writing—review & editing, B.Z.; Writing—review & editing, H.M. All authors have read and agreed to the published version of the manuscript.

Funding

The work was partly supported by the Natural Science Project of Yichang, China (A20-3-014).

Conflicts of Interest

The authors declare no conflict of interest.

References

- Cuzner, R. Does DC Distribution Make Sense? [About This Issue]. IEEE Electrif. Mag. 2016, 4, 2–3. [Google Scholar] [CrossRef]

- Nordman, B.; Christensen, K. DC Local Power Distribution: Technology, Deployment, and Pathways to Success. IEEE Electrif. Mag. 2016, 4, 29–36. [Google Scholar] [CrossRef]

- Luo, S. A review of distributed power systems part I: DC distributed power system. IEEE Aerosp. Electron. Syst. Mag. 2005, 20, 5–16. [Google Scholar] [CrossRef]

- Ji, H.; Xie, F.; Chen, Y.; Zhang, B. Small-Step Discretization Method for Modeling and Stability Analysis of Cascaded dc–dc Converters With Considering Different Switching Frequencies. IEEE Trans. Power Electron. 2022, 37, 8855–8872. [Google Scholar] [CrossRef]

- Mukherjee, N.; Strickland, D. Control of Cascaded DC–DC Converter-Based Hybrid Battery Energy Storage Systems—Part I: Stability Issue. IEEE Trans. Ind. Electron. 2016, 63, 2340–2349. [Google Scholar] [CrossRef]

- Mukherjee, N.; Strickland, D. Control of Cascaded DC–DC Converter-Based Hybrid Battery Energy Storage Systems—Part II: Lyapunov Approach. IEEE Trans. Ind. Electron. 2016, 63, 3050–3059. [Google Scholar] [CrossRef]

- Singh, S.; Gautam, A.R.; Fulwani, D. Constant power loads and their effects in DC distributed power systems: A review. Renew. Sustain. Energy Rev. 2017, 72, 407–421. [Google Scholar] [CrossRef]

- He, B.; Chen, W.; Mu, H.; Zhan, D.; Zhang, C. Small-Signal Stability Analysis and Criterion of Triple-Stage Cascaded DC System. IEEE J. Emerg. Sel. Top. Power Electron. 2022, 10, 2576–2586. [Google Scholar] [CrossRef]

- Li, H.; Zhang, Z.; Zhou, Z.; Chu, Z.; Zeng, Y.; Qiu, Z. A Floquet Theory-Based Stability Analysis Method for Cascaded DC-DC Converters by Combining with the Describing Function of PWM Link. In Proceedings of the 2021 IEEE Energy Conversion Congress and Exposition (ECCE), Vancouver, BC, Canada, 10–14 October 2021; pp. 2841–2846. [Google Scholar] [CrossRef]

- Ding, L.; Wong, S.-C.; Tse, C.K. Bifurcation Analysis of a Current-Mode-Controlled DC Cascaded System and Applications to Design. IEEE J. Emerg. Sel. Top. Power Electron. 2020, 8, 3214–3224. [Google Scholar] [CrossRef]

- El Aroudi, A.; Haroun, R.; Al-Numay, M.S.; Calvente, J.; Giral, R. Fast-Scale Stability Analysis of a DC–DC Boost Converter With a Constant Power Load. IEEE J. Emerg. Sel. Top. Power Electron. 2021, 9, 549–558. [Google Scholar] [CrossRef]

- Wu, H.; Pickert, V.; Ma, M.; Ji, B.; Zhang, C. Stability Study and Nonlinear Analysis of DC–DC Power Converters With Constant Power Loads at the Fast Timescale. IEEE J. Emerg. Sel. Top. Power Electron. 2020, 8, 3225–3236. [Google Scholar] [CrossRef]

- Hu, W.; Yang, R.; Wang, X.; Zhang, F. Stability Analysis of Voltage Controlled Buck Converter Feed From a Periodic Input. IEEE Trans. Ind. Electron. 2021, 68, 3079–3089. [Google Scholar] [CrossRef]

- Rahimi, A.M.; Emadi, A. An Analytical Investigation of DC/DC Power Electronic Converters With Constant Power Loads in Vehicular Power Systems. IEEE Trans. Veh. Technol. 2009, 58, 2689–2702. [Google Scholar] [CrossRef]

- Wang, B.; Chen, D.; Chen, C.-J.; Hsiao, S.-F. Stability Prediction of Integrated-Circuit Based Constant ON-Time Controlled Buck Converters. IEEE Trans. Power Electron. 2021, 36, 6838–6849. [Google Scholar] [CrossRef]

- Brayton, R.K.; Moser, J.K. A theory of nonlinear networks. I. Quart. Appl. Math. 1964, 22, 1–33. [Google Scholar] [CrossRef]

- Brayton, R.K.; Moser, J.K. A theory of nonlinear networks. II. Quart. Appl. Math. 1964, 22, 81–104. [Google Scholar] [CrossRef]

- Weiss, L.; Mathis, W.; Trajkovic, L.L. A generalization of Brayton-Moser’s mixed potential function. IEEE Trans. Circuits Syst. I 1998, 45, 423–427. [Google Scholar] [CrossRef]

- Liu, Z.; Ge, X.; Su, M.; Han, H.; Xiong, W.; Gui, Y. Complete Large-signal Stability Analysis of DC Distribution Network via Brayton-Moser’s Mixed Potential Theory. IEEE Trans. Smart Grid 2022, 2022, 1. [Google Scholar] [CrossRef]

- Ahmed, M.S.; Fayed, A.A. A Current-Mode Delay-Based Hysteretic Buck Regulator With Enhanced Efficiency at Ultra-Light Loads for Low-Power Microcontrollers. IEEE Trans. Power Electron. 2020, 35, 471–483. [Google Scholar] [CrossRef]

- Hsu, S.; Chen, C.; Tsai, C. A High Frequency Power and Area Efficienct Charge-Pump-Constant-On-Time Controlled DC-DC Converter Based on Dynamic-Biased Comparator with 50mV Droop and 2us 1% Settling Time for 1.15A/1ns Load Step. In Proceedings of the 2019 IEEE Applied Power Electronics Conference and Exposition (APEC), Anaheim, CA, USA, 17–21 March 2019; pp. 2980–2983. [Google Scholar] [CrossRef]

- Ming, X.; Xin, Y.; Li, T.; Liang, H.; Li, Z.; Zhang, B. A Constant On-Time Control With Internal Active Ripple Compensation Strategy for Buck Converter With Ceramic Capacitors. IEEE Trans. Power Electron. 2019, 34, 9263–9278. [Google Scholar] [CrossRef]

- Bizzarri, F.; Nora, P.; Brambilla, A. Closed-Form Operational Boundaries for Buck Converters With Constant On-Time Control. IEEE Trans. Circuits Syst. II Express Briefs 2021, 68, 3331–3335. [Google Scholar] [CrossRef]

- Tsai, C.; Chen, B.; Li, H. Switching Frequency Stabilization Techniques for Adaptive On-Time Controlled Buck Converter With Adaptive Voltage Positioning Mechanism. IEEE Trans. Power Electron. 2016, 31, 443–451. [Google Scholar] [CrossRef]

- Li, X.; Zhang, X.; Jiang, W.; Wang, J.; Wang, P.; Wu, X. A Novel Assorted Nonlinear Stabilizer for DC–DC Multilevel Boost Converter With Constant Power Load in DC Microgrid. IEEE Trans. Power Electron. 2020, 35, 11181–11192. [Google Scholar] [CrossRef]

- Hariharan, K.; Kapat, S.; Mukhopadhyay, S. Constant On-Time Multi-Mode Digital Control with Superior Performance and Programmable Frequency. In Proceedings of the 2019 IEEE Applied Power Electronics Conference and Exposition (APEC), Anaheim, CA, USA, 17–21 March 2019; pp. 1344–1350. [Google Scholar] [CrossRef]

- Olsson, E. Constant-power rectifiers for constant-power telecom loads. In Proceedings of the 24th Annual International Telecommunications Energy Conference, Montréal, QC, Canada, 29 September–3 October 2002; pp. 591–595. [Google Scholar] [CrossRef]

- Cupelli, M.; Zhu, L.; Monti, A. Why Ideal Constant Power Loads Are Not the Worst Case Condition From a Control Standpoint. IEEE Trans. Smart Grid 2015, 6, 2596–2606. [Google Scholar] [CrossRef]

- Lin, G.-Y.; Chen, D.; Chen, Y.-J. The DCM stability issue of voltage regulators using a current-mode constant on-time controller control. In Proceedings of the 2013 IEEE Energy Conversion Congress and Exposition, Denver, CO, USA, 15–19 September 2013; pp. 813–816. [Google Scholar] [CrossRef]

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).