The Effects of Total Ionizing Dose on the SEU Cross-Section of SOI SRAMs

Abstract

1. Introduction

2. Test Circuit and Experimental Setup

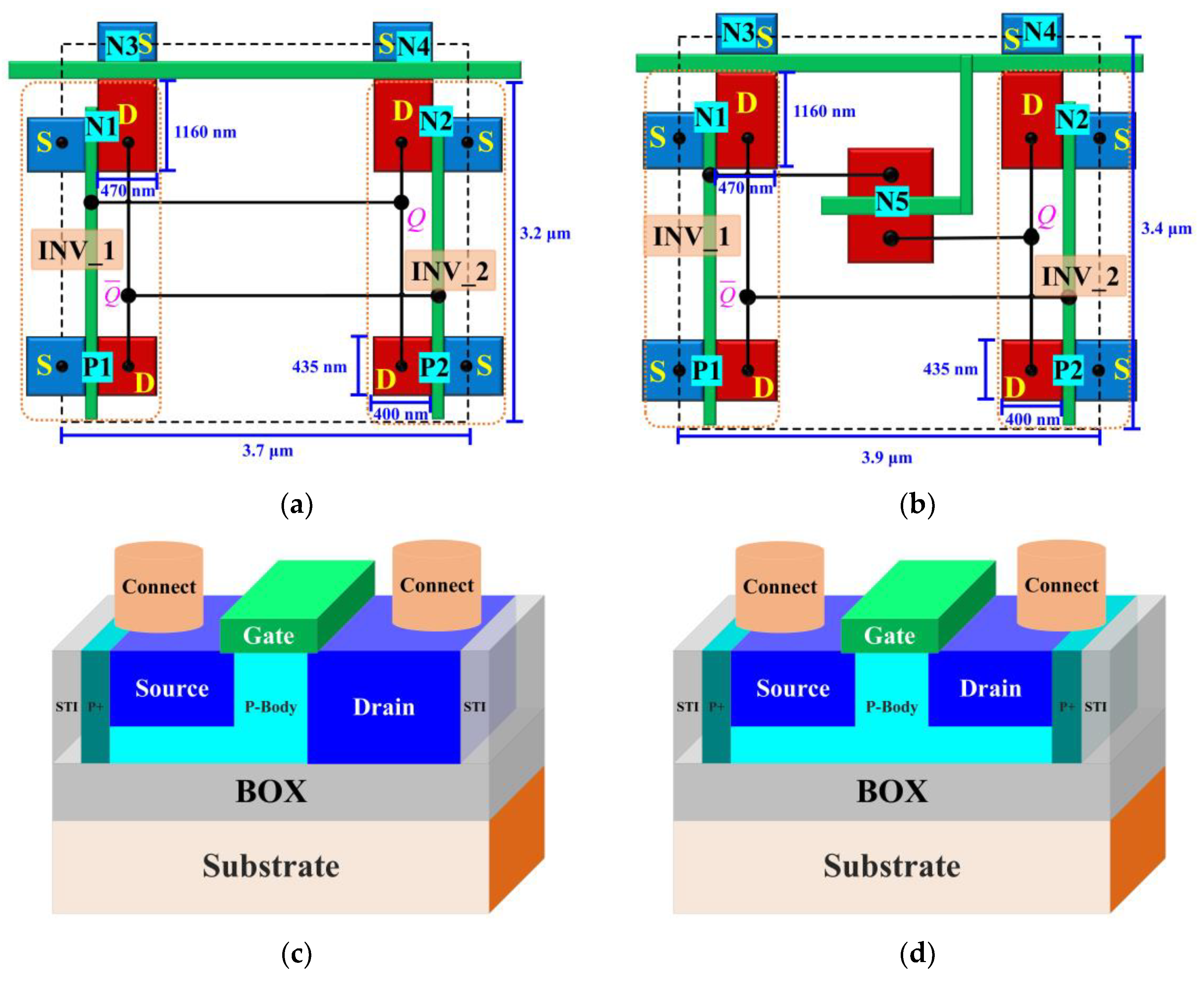

2.1. Test Circuit

2.2. TID Experiment

2.3. Heavy Ion Irradiation

3. Experimental Results

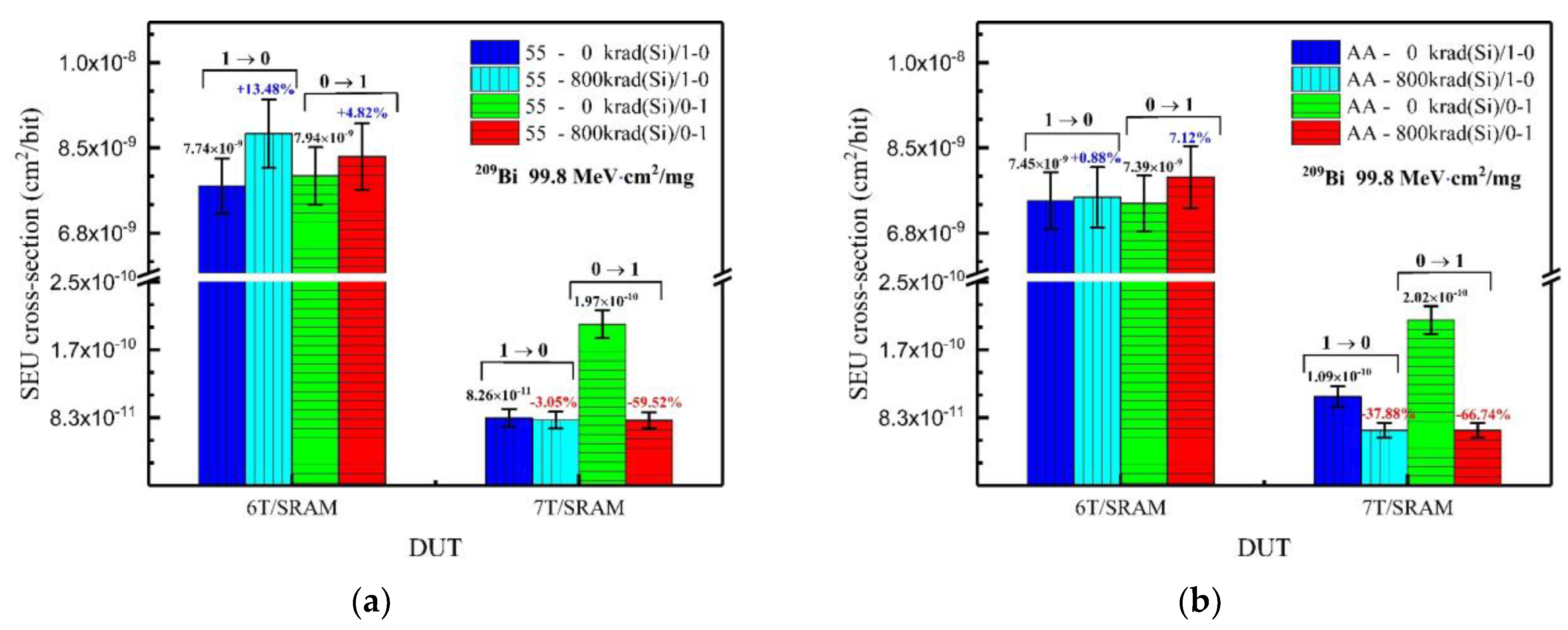

3.1. Effect of TID on the 6T SRAM SEU cross-section

3.2. Effect of Data Pattern on the 6T SRAM SEU cross-section

3.3. Effect of TID on the 7T SRAM SEU cross-section

4. Discussion

4.1. Transient Propagation Circuit Analysis for 7T SRAM

4.2. Effect of TID on the OFF-State Equivalent Resistance of Delay Transistor N5

4.3. The Advantages of Suppressing SEU with TID

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Barth, J.L.; Dyer, C.S.; Stassinopoulos, E.G. Space, atmospheric, and terrestrial radiation environments. IEEE Trans. Nucl. Sci. 2003, 50, 466–482. [Google Scholar] [CrossRef]

- Xapsos, M. A Brief History of Space Climatology: From the Big Bang to the Present. IEEE Trans. Nucl. Sci. 2019, 66, 17–37. [Google Scholar] [CrossRef]

- Dodd, P.E.; Massengill, L.W. Basic mechanisms and modeling of single-event upset in digital microelectronics. IEEE Trans. Nucl. Sci. 2003, 50, 583–602. [Google Scholar] [CrossRef]

- Baumann, R.C. Radiation-induced soft errors in advanced semiconductor technologies. IEEE Trans. Device Mater. Reliab. 2005, 5, 305–316. [Google Scholar] [CrossRef]

- Dodd, P.E.; Shaneyfelt, M.R.; Schwank, J.R.; Felix, J.A. Current and Future Challenges in Radiation Effects on CMOS Electronics. IEEE Trans. Nucl. Sci. 2010, 57, 1747–1763. [Google Scholar] [CrossRef]

- Kobayashi, D. Scaling Trends of Digital Single-Event Effects: A Survey of SEU and SET Parameters and Comparison With Transistor Performance. IEEE Trans. Nucl. Sci. 2021, 68, 124–148. [Google Scholar] [CrossRef]

- Binder, D.; Smith, E.C.; Holman, A.B. Satellite Anomalies from Galactic Cosmic Rays. IEEE Trans. Nucl. Sci. 1975, 22, 2675–2680. [Google Scholar] [CrossRef]

- Barillot, C.; Calvel, P. Review of commercial spacecraft anomalies and single-event-effect occurrences. IEEE Trans. Nucl. Sci. 1996, 43, 453–460. [Google Scholar] [CrossRef]

- Normand, E. Single-event effects in avionics. IEEE Trans. Nucl. Sci. 1996, 43, 461–474. [Google Scholar] [CrossRef]

- Harboe-Sorensen, R.; Poivey, C.; Zadeh, A.; Keating, A.; Fleurinck, N.; Puimege, K.; Guerre, F.X.; Lochon, F.; Kaddour, M.; Li, L.; et al. PROBA-II Technology Demonstration Module In-Flight Data Analysis. IEEE Trans. Nucl. Sci. 2012, 59, 1086–1091. [Google Scholar] [CrossRef]

- Ecoffet, R. Overview of In-Orbit Radiation Induced Spacecraft Anomalies. IEEE Trans. Nucl. Sci. 2013, 60, 1791–1815. [Google Scholar] [CrossRef]

- Bessot, D.; Velazco, R. Design of SEU-hardened CMOS memory cells: The HIT cell. In Proceedings of the RADECS 93—Second European Conference on Radiation and its Effects on Components and Systems, St. Malo, France, 13–16 September 1993; pp. 563–570. [Google Scholar] [CrossRef]

- Calin, T.; Nicolaidis, M.; Velazco, R. Upset hardened memory design for submicron CMOS technology. IEEE Trans. Nucl. Sci. 1996, 43, 2874–2878. [Google Scholar] [CrossRef]

- Schwank, J.R.; Shaneyfelt, M.R.; Dodd, P.E. Radiation Hardness Assurance Testing of Microelectronic Devices and Integrated Circuits: Radiation Environments, Physical Mechanisms, and Foundations for Hardness Assurance. IEEE Trans. Nucl. Sci. 2013, 60, 2074–2100. [Google Scholar] [CrossRef]

- Hughes, H.L.; Benedetto, J.M. Radiation effects and hardening of MOS technology: Devices and circuits. IEEE Trans. Nucl. Sci. 2003, 50, 500–521. [Google Scholar] [CrossRef]

- Narasimham, B.; Gambles, J.W.; Shuler, R.L.; Bhuva, B.L.; Massengill, L.W. Quantifying the Effect of Guard Rings and Guard Drains in Mitigating Charge Collection and Charge Spread. IEEE Trans. Nucl. Sci. 2008, 55, 3456–3460. [Google Scholar] [CrossRef]

- Liu, X.; Cai, L.; Liu, B.; Yang, X.; Cui, H.; Li, C. Total Ionizing Dose Hardening of 45 nm FD-SOI MOSFETs Using Body-Tie Biasing. IEEE Access 2019, 7, 51276–51283. [Google Scholar] [CrossRef]

- Soliman, K.; Nichols, D.K. Latchup in CMOS Devices from Heavy Ions. IEEE Trans. Nucl. Sci. 1983, 30, 4514–4519. [Google Scholar] [CrossRef]

- Bruguier, G.; Palau, J.M. Single particle-induced latchup. IEEE Trans. Nucl. Sci. 1996, 43, 522–532. [Google Scholar] [CrossRef]

- Hsieh, C.M.; Murley, P.C.; Brien, R.R.O. Dynamics of Charge Collection from Alpha-Particle Tracks in Integrated Circuits. In Proceedings of the 1981 International Reliability Physics Symposium, Orlando, FL, USA, 7–9 April 1981; pp. 38–42. [Google Scholar]

- Schwank, J.R.; Ferlet-Cavrois, V.; Shaneyfelt, M.R.; Paillet, P.; Dodd, P.E. Radiation effects in SOI technologies. IEEE Trans. Nucl. Sci. 2003, 50, 522–538. [Google Scholar] [CrossRef]

- Barnaby, H.J. Total-Ionizing-Dose Effects in Modern CMOS Technologies. IEEE Trans. Nucl. Sci. 2006, 53, 3103–3121. [Google Scholar] [CrossRef]

- Schwank, J.R.; Shaneyfelt, M.R.; Fleetwood, D.M.; Felix, J.A.; Dodd, P.E.; Paillet, P.; Ferlet-Cavrois, V. Radiation Effects in MOS Oxides. IEEE Trans. Nucl. Sci. 2008, 55, 1833–1853. [Google Scholar] [CrossRef]

- Raine, M.; Hubert, G.; Gaillardin, M.; Paillet, P.; Bournel, A. Monte Carlo Prediction of Heavy Ion Induced MBU Sensitivity for SOI SRAMs Using Radial Ionization Profile. IEEE Trans. Nucl. Sci. 2011, 58, 2607–2613. [Google Scholar] [CrossRef]

- Raine, M.; Gaillardin, M.; Lagutere, T.; Duhamel, O.; Paillet, P. Estimation of the Single-Event Upset Sensitivity of Advanced SOI SRAMs. IEEE Trans. Nucl. Sci. 2018, 65, 339–345. [Google Scholar] [CrossRef]

- Liu, M.S.; Liu, H.Y.; Brewster, N.; Nelson, D.; Golke, K.W.; Kirchner, G.; Hughes, H.L.; Campbell, A.; Ziegler, J.F. Limiting Upset Cross Sections of SEU Hardened SOI SRAMs. IEEE Trans. Nucl. Sci. 2006, 53, 3487–3493. [Google Scholar] [CrossRef]

- Schwank, J.R.; Shaneyfelt, M.R.; Felix, J.A.; Dodd, P.E.; Baggio, J.; Ferlet-Cavrois, V.; Paillet, P.; Hash, G.L.; Flores, R.S.; Massengill, L.W.; et al. Effects of Total Dose Irradiation on Single-Event Upset Hardness. IEEE Trans. Nucl. Sci. 2006, 53, 1772–1778. [Google Scholar] [CrossRef]

- Pereira, E.C.F.; Gonçalez, O.L.; Vaz, R.G.; Federico, C.A.; Both, T.H.; Wirth, G.I. The effects of total ionizing dose on the neutron SEU cross section of a 130 nm 4 Mb SRAM memory. In Proceedings of the 2014 15th Latin American Test Workshop—LATW, Fortaleza, Brazil, 12–15 March 2014; pp. 1–4. [Google Scholar]

- Xiao, Y.; Guo, H.-X.; Zhang, F.-Q.; Zhao, W.; Wang, Y.-P.; Zhang, K.-Y.; Ding, L.-L.; Fan, X.; Luo, Y.-H.; Wang, Y.-M. Synergistic effects of total ionizing dose on single event upset sensitivity in static random access memory under proton irradiation. Chin. Phys. B 2014, 23, 118503. [Google Scholar] [CrossRef]

- Artola, L.; Gaillardin, M.; Hubert, G.; Raine, M.; Paillet, P. Modeling Single Event Transients in Advanced Devices and ICs. IEEE Trans. Nucl. Sci. 2015, 62, 1528–1539. [Google Scholar] [CrossRef]

- Zheng, Q.; Cui, J.; Liu, M.; Zhou, H.; Liu, M.; Wei, Y.; Su, D.; Ma, T.; Lu, W.; Yu, X.; et al. Total Ionizing Dose Influence on the Single-Event Upset Sensitivity of 130-nm PD SOI SRAMs. IEEE Trans. Nucl. Sci. 2017, 64, 1897–1904. [Google Scholar] [CrossRef]

- Zheng, Q.; Cui, J.; Lu, W.; Guo, H.; Liu, J.; Yu, X.; Wei, Y.; Wang, L.; Liu, J.; He, C.; et al. The Increased Single-Event Upset Sensitivity of 65-nm DICE SRAM Induced by Total Ionizing Dose. IEEE Trans. Nucl. Sci. 2018, 65, 1920–1927. [Google Scholar] [CrossRef]

- Schwank, J.R.; Shaneyfelt, M.R.; Draper, B.L.; Dodd, P.E. BUSFET-a radiation-hardened SOI transistor. IEEE Trans. Nucl. Sci. 1999, 46, 1809–1816. [Google Scholar] [CrossRef]

- Ziegler, J.F.; Ziegler, M.D.; Biersack, J.P. SRIM—The stopping and range of ions in matter. Nucl. Instrum. Methods Phys. Res. Sect. B Beam Interact. Mater. At. 2010, 268, 1818–1823. [Google Scholar] [CrossRef]

- Schwank, J.R.; Dodd, P.E.; Shaneyfelt, M.R.; Feli, J.A.; Hash, G.L.; Ferlet-Cavrois, V.; Paillet, P.; Baggio, J.; Tangyunyong, P.; Blackmore, E. Issues for single-event proton testing of SRAMs. IEEE Trans. Nucl. Sci. 2004, 51, 3692–3700. [Google Scholar] [CrossRef]

- Faccio, F.; Cervelli, G. Radiation-induced edge effects in deep submicron CMOS transistors. IEEE Trans. Nucl. Sci. 2005, 52, 2413–2420. [Google Scholar] [CrossRef]

- Faccio, F.; Michelis, S.; Cornale, D.; Paccagnella, A.; Gerardin, S. Radiation-Induced Short Channel (RISCE) and Narrow Channel (RINCE) Effects in 65 and 130 nm MOSFETs. IEEE Trans. Nucl. Sci. 2015, 62, 2933–2940. [Google Scholar] [CrossRef]

- Wu, X.; Lu, W.; Wang, X.; Xi, S.-B.; Guo, Q.; Li, Y.-D. Total ionizing dose effect on 0.18 μm narrow-channel NMOS transistors. Acta Phys. Sin. 2013, 62, 136101. [Google Scholar] [CrossRef]

- Zhou, H.; Cui, J.-W.; Zheng, Q.-W.; Guo, Q.; Ren, D.-Y.; Yu, X.-F. Reliability of partially-depleted silicon-on-insulator n-channel metal-oxide-semiconductor field-effect transistor under the ionizing radiation environment. Acta Phys. Sin. 2015, 64, 086101. [Google Scholar] [CrossRef]

- Zhang, H.; Bi, J.; Wang, H.; Hu, H.; Li, J.; Ji, L.; Liu, M. Study of total ionizing dose induced read bit errors in magneto-resistive random access memory. Microelectr. Reliab. 2016, 67, 104–110. [Google Scholar] [CrossRef]

| Ion Species | Air/Al-Foil (mm)/(μm) | Energy at Device Surface (MeV) | LET at Device Surface (MeV·cm2/mg) | Ion Range (μm) |

|---|---|---|---|---|

| 86Kr | 30/0 | 1841 | 20.5 | 274 |

| 50/100 | 1154 | 27.2 | 150 | |

| 50/180 | 480 | 37.6 | 59 | |

| 209Bi | 30/0 | 923 | 99.8 | 54 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Zhao, P.; Li, B.; Liu, H.; Yang, J.; Jiao, Y.; Chen, Q.; Sun, Y.; Liu, J. The Effects of Total Ionizing Dose on the SEU Cross-Section of SOI SRAMs. Electronics 2022, 11, 3188. https://doi.org/10.3390/electronics11193188

Zhao P, Li B, Liu H, Yang J, Jiao Y, Chen Q, Sun Y, Liu J. The Effects of Total Ionizing Dose on the SEU Cross-Section of SOI SRAMs. Electronics. 2022; 11(19):3188. https://doi.org/10.3390/electronics11193188

Chicago/Turabian StyleZhao, Peixiong, Bo Li, Hainan Liu, Jinhu Yang, Yang Jiao, Qiyu Chen, Youmei Sun, and Jie Liu. 2022. "The Effects of Total Ionizing Dose on the SEU Cross-Section of SOI SRAMs" Electronics 11, no. 19: 3188. https://doi.org/10.3390/electronics11193188

APA StyleZhao, P., Li, B., Liu, H., Yang, J., Jiao, Y., Chen, Q., Sun, Y., & Liu, J. (2022). The Effects of Total Ionizing Dose on the SEU Cross-Section of SOI SRAMs. Electronics, 11(19), 3188. https://doi.org/10.3390/electronics11193188