Ultralow Voltage FinFET- Versus TFET-Based STT-MRAM Cells for IoT Applications

Abstract

:1. Introduction

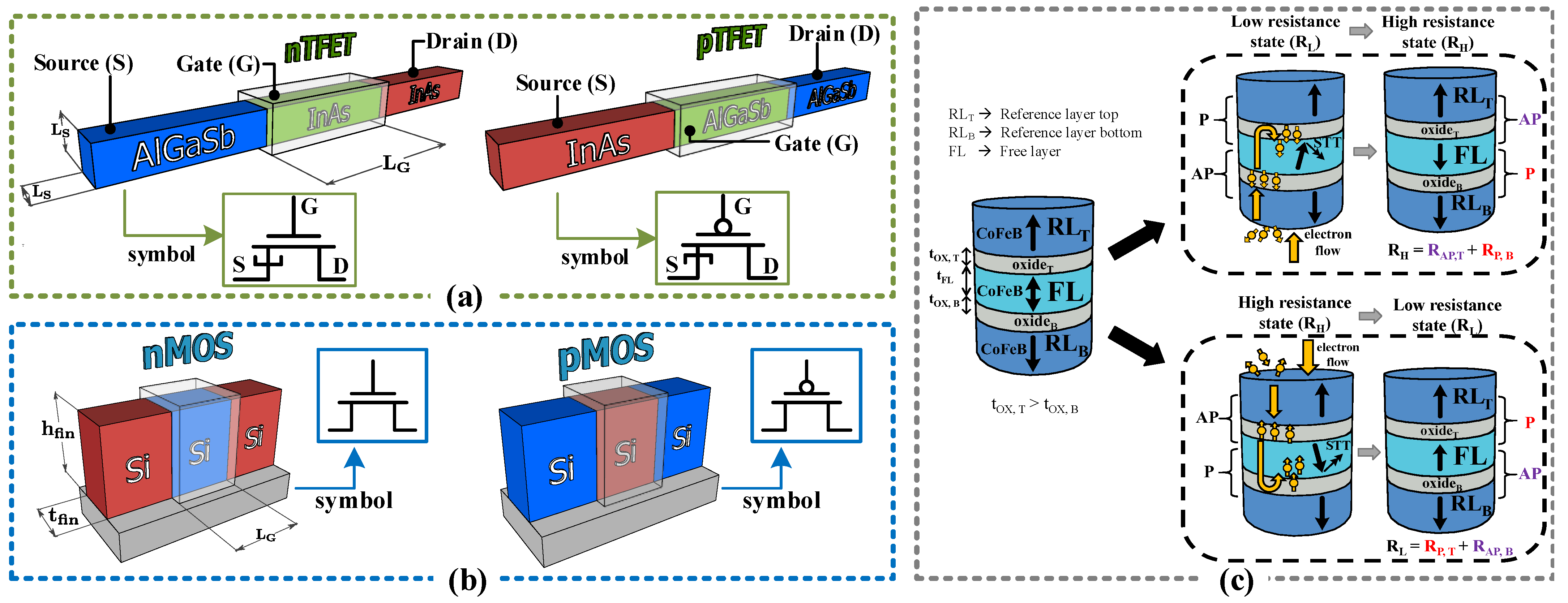

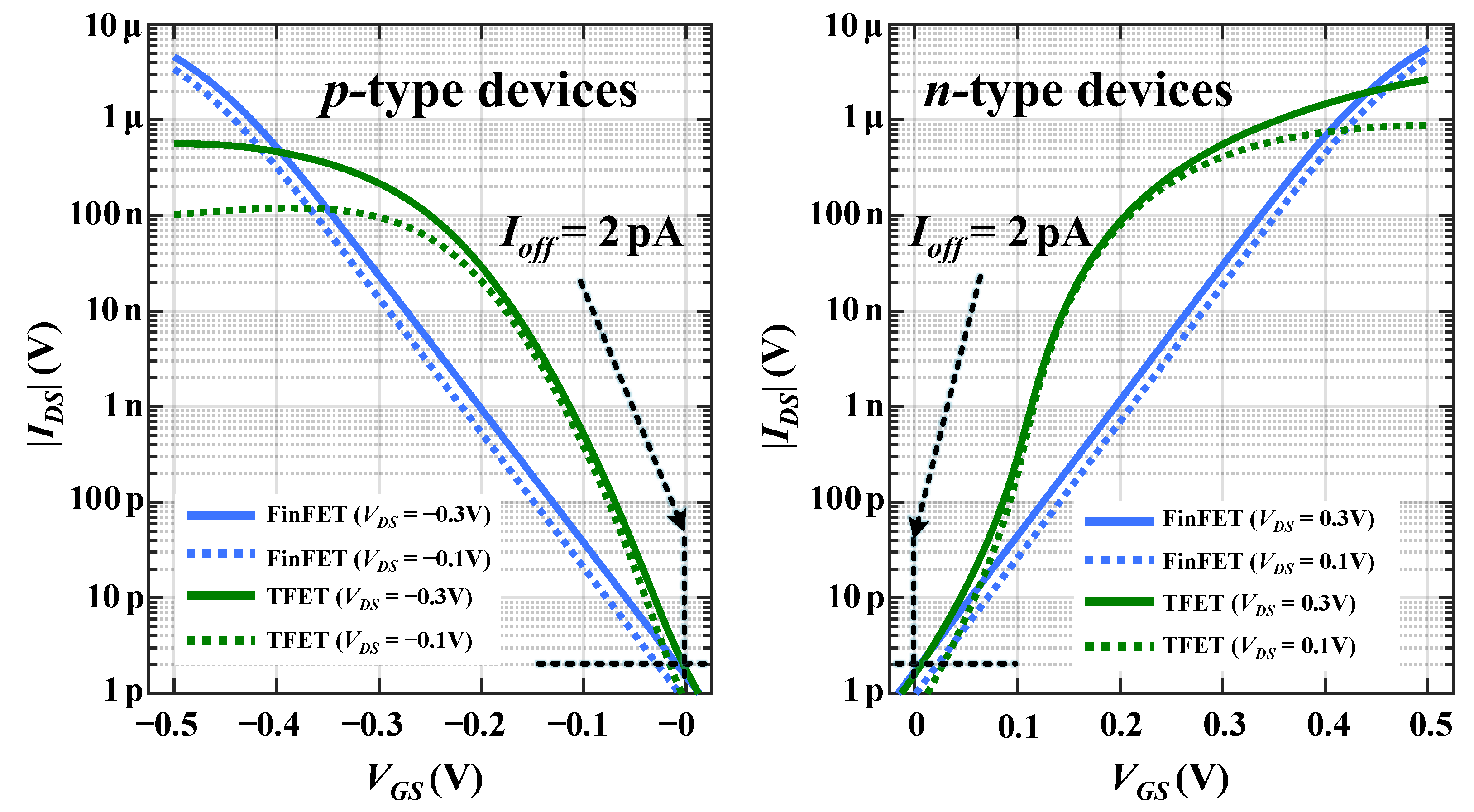

2. Ultralow Voltage Transistors and STT-DMTJ

2.1. Tunnel-FET (TFET) and FinFET Structures

2.2. Double-Barrier Magnetic Tunnel Junction (DMTJ)

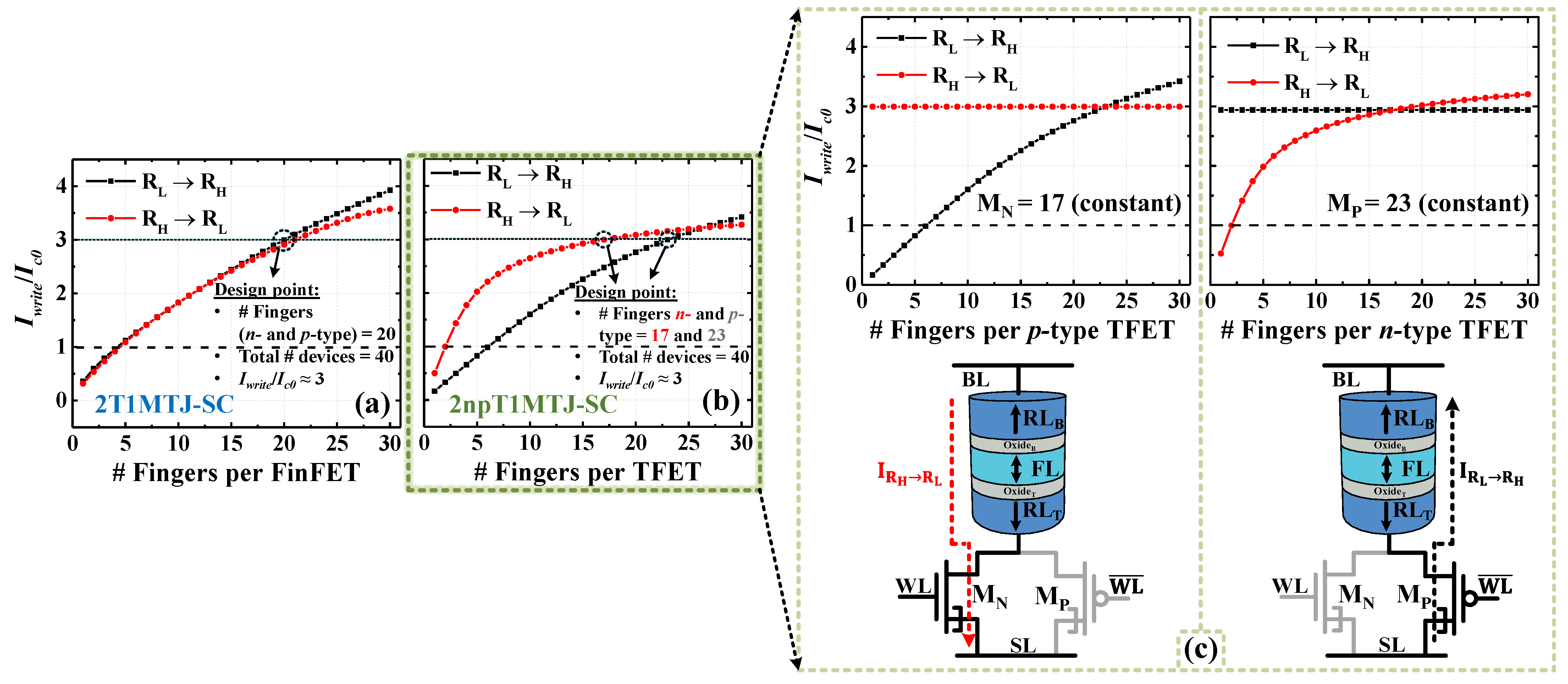

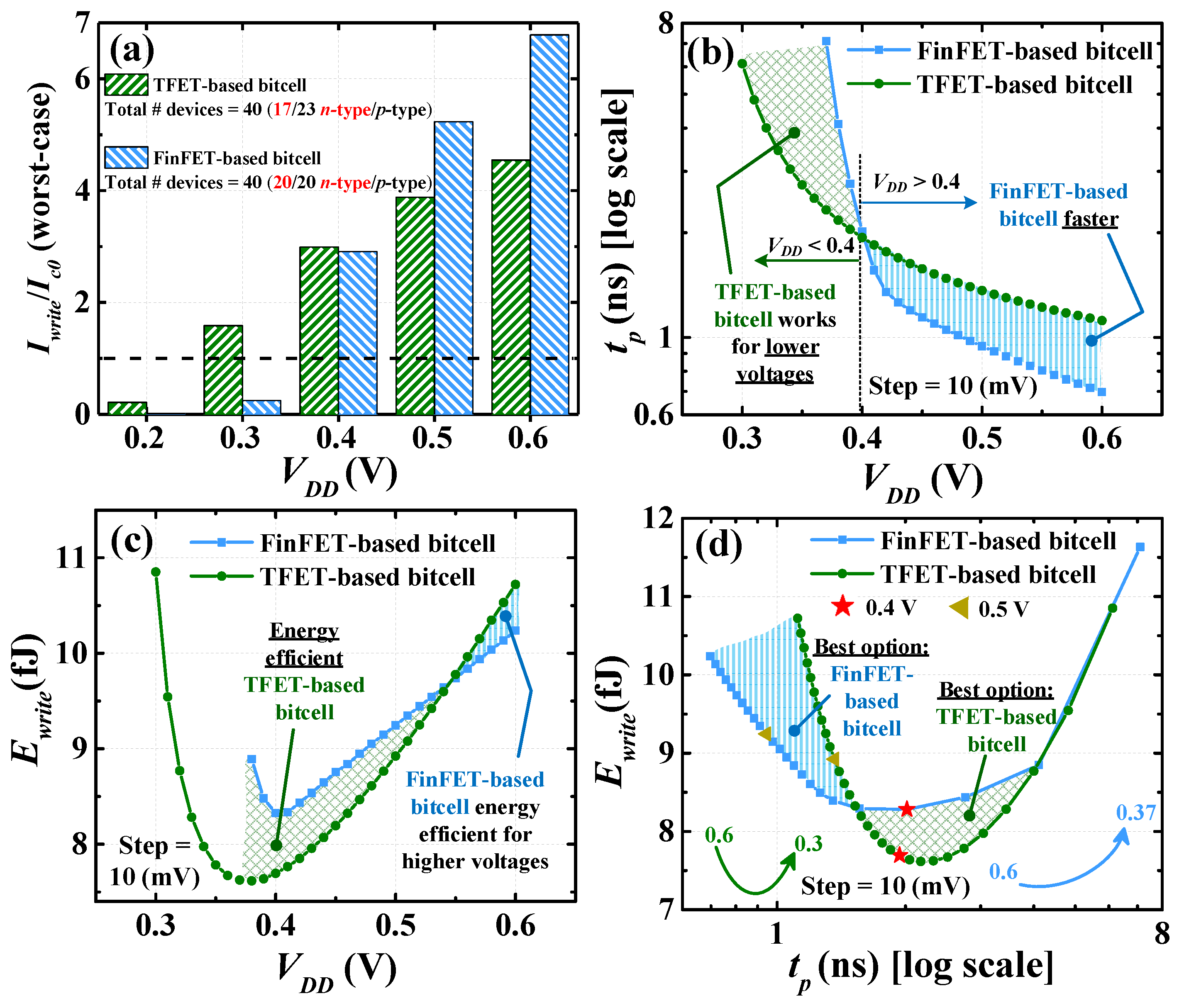

3. STT-MRAM BitCell Simulation and Benchmark

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Fong, X.; Kim, Y.; Venkatesan, R.; Choday, S.H.; Raghunathan, A.; Roy, K. Spin-Transfer Torque Memories: Devices, Circuits, and Systems. Proc. IEEE 2016, 104, 1449–1488. [Google Scholar] [CrossRef]

- De Rose, R.; Lanuzza, M.; d’Aquino, M.; Carangelo, G.; Finocchio, G.; Crupi, F.; Carpentieri, M. A compact model with spin-polarization asymmetry for nanoscaled perpendicular MTJs. IEEE Trans. Electron Devices 2017, 64, 4346–4353. [Google Scholar] [CrossRef]

- Wolf, S.A.; Lu, J.; Stan, M.R.; Chen, E.; Treger, D.M. The Promise of Nanomagnetics and Spintronics for Future Logic and Universal Memory. Proc. IEEE 2010, 98, 2155–2168. [Google Scholar] [CrossRef]

- Garzón, E.; De Rose, R.; Crupi, F.; Trojman, L.; Finocchio, G.; Carpentieri, M.; Lanuzza, M. Assessment of STT-MRAMs based on double-barrier MTJs for cache applications by means of a device-to-system level simulation framework. Integr. VLSI J. 2020, 71, 56–69. [Google Scholar] [CrossRef]

- Garzón, E.; De Rose, R.; Crupi, F.; Carpentieri, M.; Teman, A.; Lanuzza, M. Simulation Analysis of DMTJ-Based STT-MRAM Operating at Cryogenic Temperatures. IEEE Trans. Magn. 2021, 57, 1–6. [Google Scholar] [CrossRef]

- Garzón, E.; De Rose, R.; Crupi, F.; Teman, A.; Lanuzza, M. Exploiting STT-MRAMs for Cryogenic Non-Volatile Cache Applications. IEEE Trans. Nanotechnol. 2021, 20, 123–128. [Google Scholar] [CrossRef]

- Apalkov, D.; Khvalkovskiy, A.; Watts, S.; Nikitin, V.; Tang, X.; Lottis, D.; Moon, K.; Luo, X.; Chen, E.; Ong, A.; et al. Spin-Transfer Torque Magnetic Random Access Memory (STT-MRAM). J. Emerg. Technol. Comput. Syst. 2013, 9, 1–35. [Google Scholar] [CrossRef]

- Alioto, M. Enabling the Internet of Things: From Integrated Circuits to Integrated Systems; Springer: Cham, Switzerland, 2017. [Google Scholar]

- Fassio, L.; Lin, L.; De Rose, R.; Lanuzza, M.; Crupi, F.; Alioto, M. Trimming-Less Voltage Reference for Highly Uncertain Harvesting Down to 0.25 V, 5.4 pW. IEEE J. Solid State Circuits 2021. [Google Scholar] [CrossRef]

- Fassio, L.; Lin, L.; De Rose, R.; Lanuzza, M.; Crupi, F.; Alioto, M. A 0.6-to-1.8 V CMOS Current Reference with Near-100% Power Utilization. IEEE Trans. Circuits Syst. II Express Briefs 2021. [Google Scholar] [CrossRef]

- Hu, G.; Lee, J.H.; Nowak, J.J.; Sun, J.Z.; Harms, J.; Annunziata, A.; Brown, S.; Chen, W.; Kim, Y.H.; Lauer, G.; et al. STT-MRAM with double magnetic tunnel junctions. In Proceedings of the 2015 IEEE International Electron Devices Meeting (IEDM), Washington, DC, USA, 7–9 December 2015; pp. 26.3.1–26.3.4. [Google Scholar] [CrossRef]

- Yamani, S.V.; Rani, N.U.; Vaddi, R. An Energy-Efficient Hybrid Tunnel FET based STT-MRAM Memory Cell Design at Low VDD. Int. J. Electron. 2021, 1–16. [Google Scholar] [CrossRef]

- Kuhn, K.J. Considerations for Ultimate CMOS Scaling. IEEE Trans. Electron Devices 2012, 59, 1813–1828. [Google Scholar] [CrossRef]

- ASU. Predictive Technology Model (PTM). Available online: http://ptm.asu.edu (accessed on 17 June 2021).

- Ionescu, A.; Riel, H. Tunnel field-effect transistors as energy-efficient electronic switches. Nature 2011, 479, 329–337. [Google Scholar] [CrossRef] [PubMed]

- Convertino, C.; Zota, C.B.; Schmid, H.; Caimi, D.; Czornomaz, L.; Ionescu, A.M.; Moselund, K.E. A hybrid III–V tunnel FET and MOSFET technology platform. Nat. Electron. 2021, 4, 162–170. [Google Scholar] [CrossRef]

- Strangio, S.; Settino, F.; Palestri, P.; Lanuzza, M.; Crupi, F.; Esseni, D.; Selmi, L. Digital and analog TFET circuits: Design and benchmark. Solid State Electron. 2018, 146, 50–65. [Google Scholar] [CrossRef] [Green Version]

- Garzón, E.; De Rose, R.; Crupi, F.; Trojman, L.; Lanuzza, M. Assessment of STT-MRAM performance at nanoscaled technology nodes using a device-to-memory simulation framework. Microelectron. Eng. 2019, 215, 111009. [Google Scholar] [CrossRef]

- Bhattacharya, A.; Pal, S.; Islam, A. Implementation of FinFET based STT-MRAM bitcell. In Proceedings of the 2014 IEEE International Conference on Advanced Communications, Control and Computing Technologies, Ramanathapuram, India, 8–10 May 2014; pp. 435–439. [Google Scholar] [CrossRef]

- Xu, C.; Zheng, Y.; Niu, D.; Zhu, X.; Kang, S.H.; Xie, Y. Impact of Write Pulse and Process Variation on 22 nm FinFET-Based STT-RAM Design: A Device-Architecture Co-Optimization Approach. IEEE Trans. Multi Scale Comput. Syst. 2015, 1, 195–206. [Google Scholar] [CrossRef]

- Shafaei, A.; Wang, Y.; Pedram, M. Low write-energy STT-MRAMs using FinFET-based access transistors. In Proceedings of the 2014 IEEE 32nd International Conference on Computer Design (ICCD), Seoul, Korea, 19–22 October 2014; pp. 374–379. [Google Scholar] [CrossRef]

- Vani, Y.S.; Rani, N.U.; Vaddi, R. Low Write Energy STT-MRAM Cell Using 2T-Hybrid Tunnel FETs Exploiting the Steep Slope and Ambipolar Characteristics. In Proceedings of the 21st International Symposium, VDAT 2017, Roorkee, India, 29 June–2 July 2017; pp. 398–405. [Google Scholar]

- Wang, Z.; Ye, L.; Huang, Q.; Du, K.; Tan, Z.; Wang, Y.; Huang, R. Ultra-Low-Power and Performance-Improved Logic Circuit Using Hybrid TFET-MOSFET Standard Cells Topologies and Optimized Digital Front-End Process. IEEE Trans. Circuits Syst. I Regul. Pap. 2021, 68, 1160–1170. [Google Scholar] [CrossRef]

- Strangio, S.; Palestri, P.; Lanuzza, M.; Esseni, D.; Crupi, F.; Selmi, L. Benchmarks of a III-V TFET technology platform against the 10-nm CMOS FinFET technology node considering basic arithmetic circuits. Solid State Electron. 2017, 128, 37–42. [Google Scholar] [CrossRef]

- Settino, F.; Lanuzza, M.; Strangio, S.; Crupi, F.; Palestri, P.; Esseni, D.; Selmi, L. Understanding the potential and limitations of tunnel FETs for low-voltage analog/mixed-signal circuits. IEEE Trans. Electron Devices 2017, 64, 2736–2743. [Google Scholar] [CrossRef]

- Nogueira, A.D.M.; Agopian, P.G.D.; Simoen, E.; Rooyackers, R.; Claeys, C.; Collaert, N.; Martino, J.A. Impact of gate current on the operational transconductance amplifier designed with nanowire TFETs. Solid State Electron. 2021, 186, 108099. [Google Scholar] [CrossRef]

- Lin, Z.; Li, L.; Wu, X.; Peng, C.; Lu, W.; Zhao, Q. Half-Select Disturb-Free 10T Tunnel FET SRAM Cell With Improved Noise Margin and Low Power Consumption. IEEE Trans. Circuits Syst. II Express Briefs 2021, 68, 2628–2632. [Google Scholar] [CrossRef]

- Chen, Y.N.; Fan, M.L.; Hu, V.P.H.; Su, P.; Chuang, C.T. Evaluation of Stability, Performance of Ultra-Low Voltage MOSFET, TFET, and Mixed TFET-MOSFET SRAM Cell With Write-Assist Circuits. IEEE J. Emerg. Sel. Top. Circuits Syst. 2014, 4, 389–399. [Google Scholar] [CrossRef]

- De Rose, R.; d’Aquino, M.; Finocchio, G.; Crupi, F.; Carpentieri, M.; Lanuzza, M. Compact Modeling of Perpendicular STT-MTJs With Double Reference Layers. IEEE Trans. Nanotechnol. 2019, 18, 1063–1070. [Google Scholar] [CrossRef]

- Baravelli, E.; Gnani, E.; Gnudi, A.; Reggiani, S.; Baccarani, G. TFET Inverters With n-/p-Devices on the Same Technology Platform for Low-Voltage/Low-Power Applications. IEEE Trans. Electron Devices 2014, 61, 473–478. [Google Scholar] [CrossRef]

- Memisevic, E.; Svensson, J.; Hellenbrand, M.; Lind, E.; Wernersson, L.E. Vertical InAs/GaAsSb/GaSb tunneling field-effect transistor on Si with S = 48 mV/decade and Ion = 10 μA/ μm for Ioff = 1 nA/ μm at Vds = 0.3 V. In Proceedings of the 2016 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 3–7 December 2016; pp. 19.1.1–19.1.4. [Google Scholar] [CrossRef] [Green Version]

- Morris, D.H.; Vaidyanathan, K.; Avci, U.E.; Liu, H.; Karnik, T.; Young, I.A. Enabling high-performance heterogeneous TFET/CMOS logic with novel circuits using TFET unidirectionality and low-VDD operation. In Proceedings of the 2016 IEEE Symposium on VLSI Technology, Honolulu, HI, USA, 14–16 June 2016; pp. 1–2. [Google Scholar] [CrossRef]

- Alioto, M. Ultra-Low Power VLSI Circuit Design Demystified and Explained: A Tutorial. IEEE Trans. Circuits Syst. I Regul. Pap. 2012, 59, 3–29. [Google Scholar] [CrossRef]

- Wang, X.; Cheng, B.; Brown, A.R.; Millar, C.; Kuang, J.B.; Nassif, S.; Asenov, A. Interplay Between Process-Induced and Statistical Variability in 14-nm CMOS Technology Double-Gate SOI FinFETs. IEEE Trans. Electron Devices 2013, 60, 2485–2492. [Google Scholar] [CrossRef]

- Pelgrom, M.; Duinmaijer, A.; Welbers, A. Matching properties of MOS transistors. IEEE J. Solid State Circuits 1989, 24, 1433–1439. [Google Scholar] [CrossRef]

- Huang, Q.; Jia, R.; Chen, C.; Zhu, H.; Guo, L.; Wang, J.; Wang, J.; Wu, C.; Wang, R.; Bu, W.; et al. First foundry platform of complementary tunnel-FETs in CMOS baseline technology for ultralow-power IoT applications: Manufacturability, variability and technology roadmap. In Proceedings of the 2015 IEEE International Electron Devices Meeting (IEDM), Washington, DC, USA, 7–9 December 2015; pp. 22.2.1–22.2.4. [Google Scholar] [CrossRef]

- Garzón, E.; de Rose, R.; Crupi, F.; Trojman, L.; Teman, A.; Lanuzza, M. Relaxing Non-Volatility for Energy-Efficient DMTJ Based Cryogenic STT-MRAM. Solid-State Electron. 2021, 184, 108090. [Google Scholar] [CrossRef]

- Ohashi, T.; Yamaguchi, A.; Hasumi, K.; Inoue, O.; Ikota, M.; Lorusso, G.; Donadio, G.L.; Yasin, F.; Rao, S.; Kar, G.S. Variability study with CD-SEM metrology for STT-MRAM: Correlation analysis between physical dimensions and electrical property of the memory element. In Metrology, Inspection, and Process Control for Microlithography XXXI; SPIE Advanced Lithography: San Jose, CA, USA, 2017; Volume 10145, p. 101450H. [Google Scholar] [CrossRef]

- Ho, C.H.; Panagopoulos, G.D.; Kim, S.Y.; Kim, Y.; Lee, D.; Roy, K. A physics-based statistical model for reliability of STT-MRAM considering oxide variability. In Proceedings of the 2013 International Conference on Simulation of Semiconductor Processes and Devices (SISPAD), Glasgow, UK, 3–5 September 2013; pp. 29–32. [Google Scholar] [CrossRef]

- Trinh, Q.K.; Ruocco, S.; Alioto, M. Dynamic Reference Voltage Sensing Scheme for Read Margin Improvement in STT-MRAMs. IEEE Trans. Circuits Syst. I Regul. Pap. 2018, 65, 1269–1278. [Google Scholar] [CrossRef]

- Trinh, Q.K.; Ruocco, S.; Alioto, M. Novel Boosted-Voltage Sensing Scheme for Variation-Resilient STT-MRAM Read. IEEE Trans. Circuits Syst. I Regul. Pap. 2016, 63, 1652–1660. [Google Scholar] [CrossRef]

| Parameter | Description | Value |

|---|---|---|

| TFET | ||

| Gate length | 20 | |

| Length of nanowire square cross-section | 7 | |

| Physical oxide thickness (EOT) | 2.3 (1 ) | |

| FinFET | ||

| hfin | Fin height | 21 |

| tfin | Fin width | 8 |

| Gate length | 14 | |

| Physical oxide thickness (EOT) | 1.2 (0.88 ) | |

| DMTJ | ||

| d | MTJ diameter | 22 |

| FL thickness | 1 | |

| Top barrier thickness | 0.85 | |

| Bottom barrier thickness | 0.4 | |

| RA | Resistance-area product | ∼7 |

| Gilbert damping factor | 0.025 | |

| TMR | Tunnel magnetoresistance ratio at 0 V | 150% |

| High resistance state at 0 V | 44.6 k | |

| Low resistance state | 20 k | |

| Critical switching current | ∼3 | |

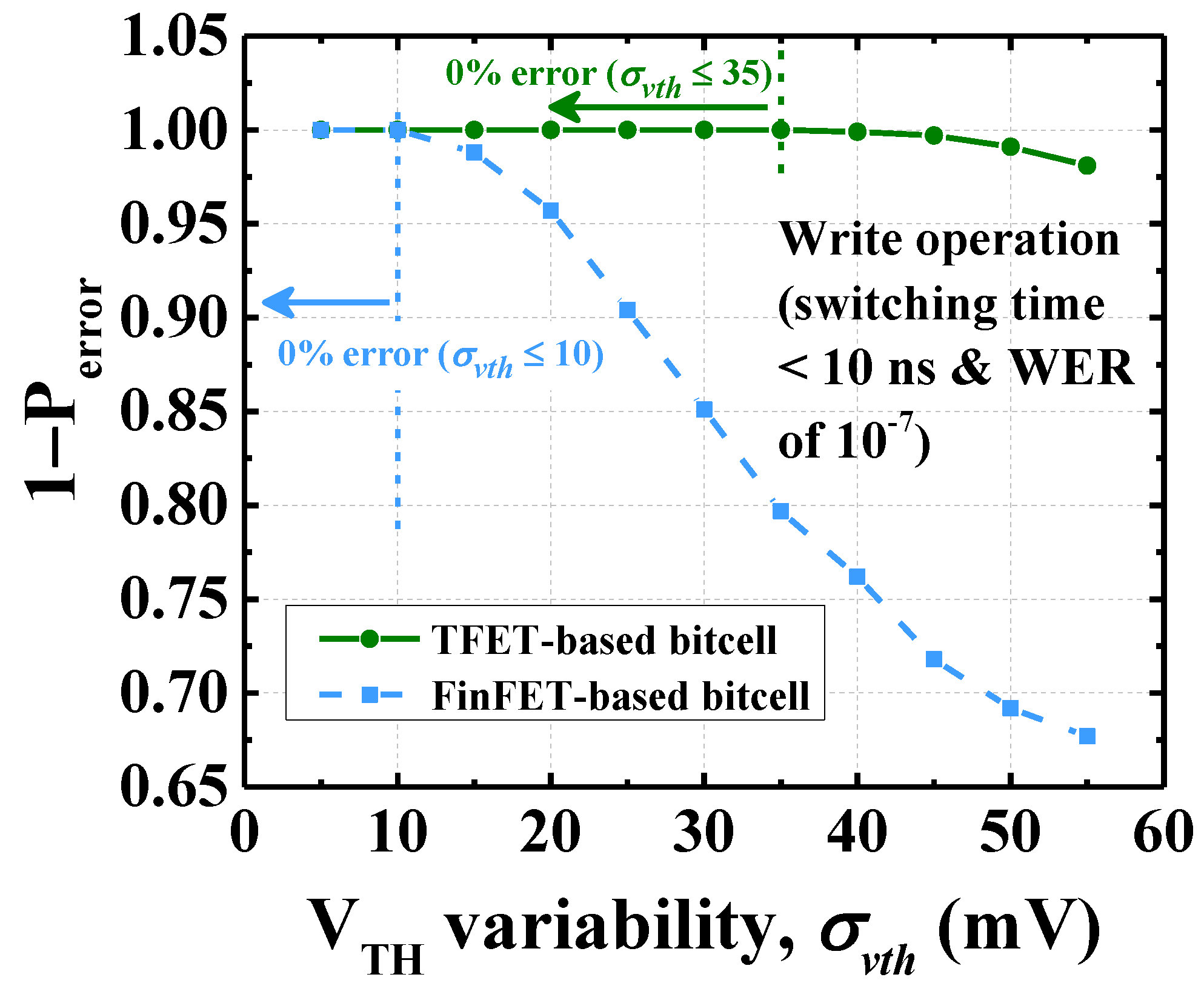

| Parameter | TFET-Based Bitcell | FinFET-Based Bitcell | ||

|---|---|---|---|---|

| Variation () | Variation () | Variation () | Variation () | |

| ( ) | 0.4 | |||

| Area () | 6000 | |||

| ( ) | 2.77 | 4.36 | 6.89 | Cell does not work * |

| ( ) | 11.3 | 17.44 | 22.7 | |

| ( ) | 1.68 | |||

| ( ) | 1 | |||

| ( ) | 0.67 | |||

| ( ) | 40 | |||

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Garzón, E.; Lanuzza, M.; Taco, R.; Strangio, S. Ultralow Voltage FinFET- Versus TFET-Based STT-MRAM Cells for IoT Applications. Electronics 2021, 10, 1756. https://doi.org/10.3390/electronics10151756

Garzón E, Lanuzza M, Taco R, Strangio S. Ultralow Voltage FinFET- Versus TFET-Based STT-MRAM Cells for IoT Applications. Electronics. 2021; 10(15):1756. https://doi.org/10.3390/electronics10151756

Chicago/Turabian StyleGarzón, Esteban, Marco Lanuzza, Ramiro Taco, and Sebastiano Strangio. 2021. "Ultralow Voltage FinFET- Versus TFET-Based STT-MRAM Cells for IoT Applications" Electronics 10, no. 15: 1756. https://doi.org/10.3390/electronics10151756

APA StyleGarzón, E., Lanuzza, M., Taco, R., & Strangio, S. (2021). Ultralow Voltage FinFET- Versus TFET-Based STT-MRAM Cells for IoT Applications. Electronics, 10(15), 1756. https://doi.org/10.3390/electronics10151756