Abstract

Multiple-output converters have been widely used where individual outputs are required. Compared with conventional separate converters, the advantage of multiple outputs is to have a lower number of active and passive components. In this paper, first, a pulse-width-modulation (PWM)-pulse-frequency-modulation (PFM) method is used for two-output converters that have only one coil and one active switch. Secondly, three-output converter topologies are proposed where the third output is controlled by phase delay (PD). These converters need only two coils and two active switches to regulate three outputs. How to obtain PD at different switching frequencies is discussed next, and a PWM-PFM-PD controlled five-output buck converter is presented. The proposed solution uses only two active switches and two magnetic cores to adjust five-output voltages independently. A modeling and digital control method are proposed in order to regulate the five output voltages. A prototype circuit with independent 15 V/1.5 A, 12 V/1.5 A, 5 V/0.8 A, −5 V/0.6 A and 3.3 V/0.45 A outputs is assembled to validate the analysis, and it was proved that it regulates the output voltages at different loads.

1. Introduction

The size and cost of a multiple output converter can be less than that of separate converters. However, one of the main drawbacks of a multiple output converter is its cross regulation. One way to obtain multiple outputs is to have a single power converter such as a flyback or forward converter with multiple secondary windings. Usually, these converters regulate only the output that is defined as the master one; the other outputs depend on the load conditions [1]. If there are no conduction losses and no leakage inductance, closed-loop regulation of the master output will regulates all the outputs in continuous conduction mode (CCM) [1]. However, perfect cross-regulation in real life may not be easy to achieve. Therefore, post regulators are applied to adjust the additional outputs [2,3].

The single-switch pulse-width modulation (PWM)-pulse-frequency modulation (PFM) converter uses PFM in order to regulate the second output voltage [4,5]. This converter has two separate inductors. One of the output circuits operates in CCM, while the other operates in discontinuous conduction mode (DCM). Both outputs can be controlled independently by orthogonally modulating both the duty cycle and the switching frequency of the single active switch. The work described in [6] is based on such a PWM-PFM method, however, instead of DCM, the second output is controlled in zero-current-switching (ZCS) quasi-resonant (QR) mode. A further PWM-phase delay (PD) control method produces a regulated third output [7,8]. In this case, two active switches are required. The active switches are operated at the same switching frequency, which is a requirement for implementing PD, and the PD then makes it easy to adjust the third-output voltage. Some researchers have used the PWM-PFM and PWM-PD methods with isolated dc-dc converters [9,10,11,12]. However, extra active switches are required to implement these converters. The study reported in [13] outlines a PWM-PFM-PD control method, but the converter can adjust only three-output voltages.

Firstly, the PWM-PFM method for two-output converters that have only one coupled inductor and one active switch is described. Next, a three-output converter topology is proposed in which the third output is controlled by PD. Subsequently, PWM-PFM and PWM-PD methods are merged, and a PWM-PFM-PD method is proposed to control a five-output converter [14]. Finally, alternative PWM-PFM-PD controlled five-output converter topologies are proposed. The proposed solutions use only two active switches and two magnetic cores to adjust five-output voltages independently. Two active switches have five independent control parameters, i.e., duty cycle and switching frequency of the first gate signal, duty cycle and switching frequency of the second gate signal, and finally phase delay between the first and the second gate signals. Two of the outputs are adjusted using PWM in CCM, while the other two use PFM in DCM, and the fifth load is regulated by PD. Using “burst mode” in one of the two switches enables the use of PD operation for signals that do not have the same frequency. This technique creates the opportunity to regulate five outputs with a significantly reduced number of active and passive components.

Section 2 presents PWM-PFM controlled two-output converters. Then, Section 3 describes PWM-PD controlled three-output converters and Section 4 shows PWM-PFM-PD controlled five-output converters. Each section has design criteria and experimental results of the converters. Also, Section 4 has a comparison between the proposed five-output converter and other multiple converters. Section 5 explains how to model the five-output converter and Section 6 presents a control method to regulate five output voltages and its experimental results. Conclusions are given in Section 7.

2. PWM-PFM Controlled Two-Output Converters

The PWM-PFM method for two-output dc-dc converters with one active switch is introduced in [4]. In the paper, one output is controlled by PWM and the other by PFM. One of the inductors is designed for CCM, and the other for DCM. While the duty cycle of the switch determines both output voltages, its switching frequency only adjusts the output voltage in DCM. Hence both output voltages can be regulated independently, subject to DCM constraints.

Another way to obtain auxiliary outputs without using additional active switches is to place multiple windings onto the inductor of a buck converter [15,16]. The primary of the coupled inductor is used for the first output, and the secondary voltage is rectified and filtered to create a second output. This second output depends on the turns ratio of the coupled inductor, n. The polarity of the coupled inductor determines whether energy is transferred to the secondary in flyback or forward mode.

The first output is regulated by the PWM of the active switch, while a zener diode or a linear regulator is often included on the secondary side to regulate the second output voltage [2,3]. These methods reduce the efficiency of the converter.

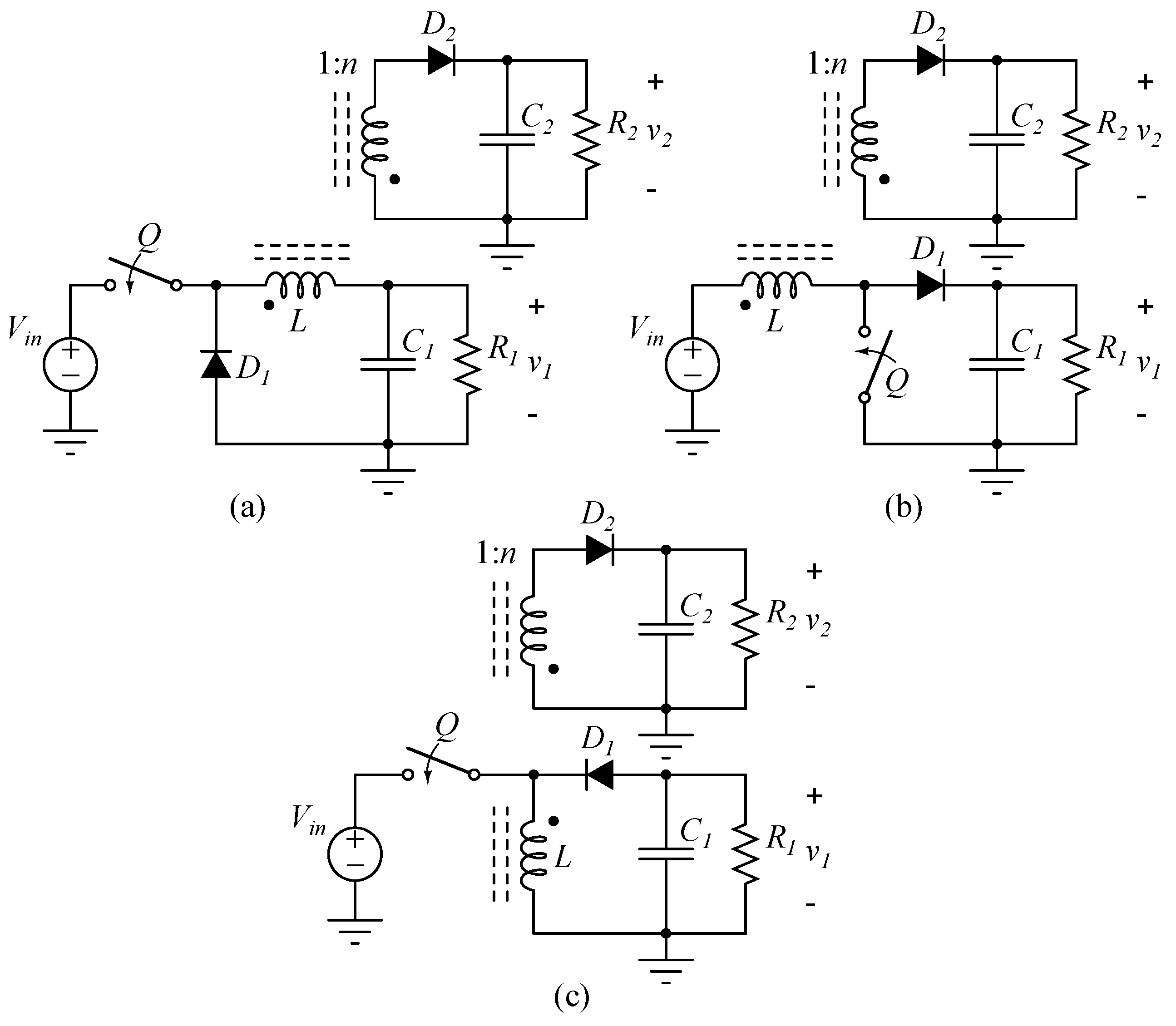

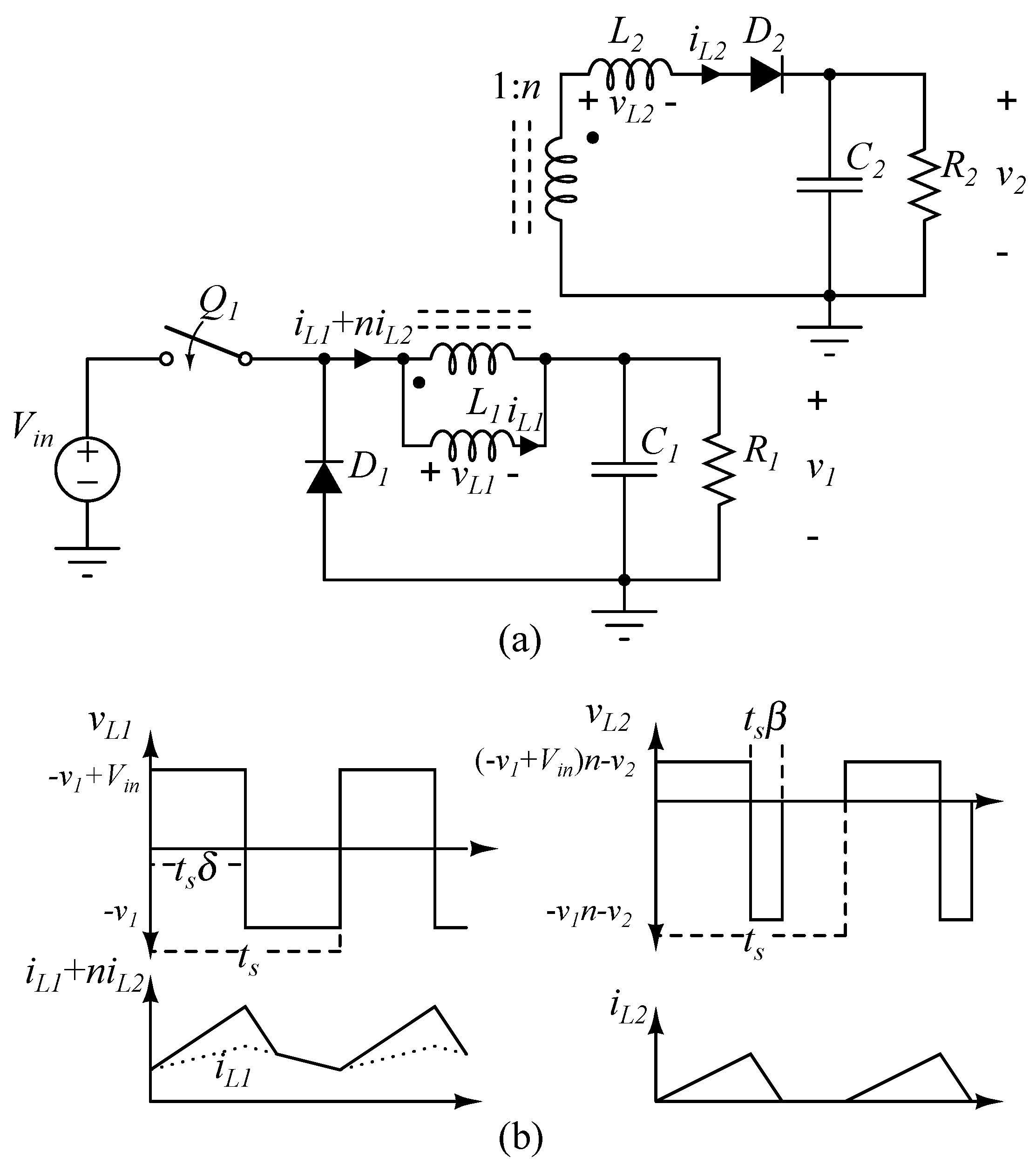

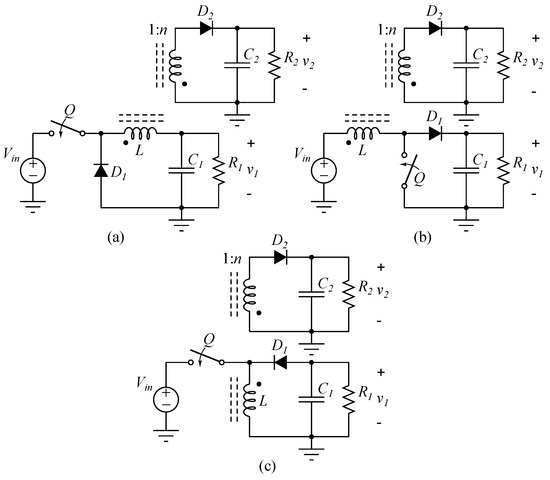

PFM can be used as a control parameter to regulate the second output when it is operated in DCM. The magnetizing inductance of the coupled inductor is used for the PWM output, and the leakage inductance is used for the PFM output. The two-output buck converters that are shown in Figure 1a are explained in this chapter. Note that the exact same approach is possible for other dc-dc converters, e.g., the boost and buck-boost converters that are depicted in Figure 1b,c.

Figure 1.

(a) A two-output buck converter. (b) A potential two-output boost converter; (c) A potential two-output buck-boost converter.

2.1. Two-Output Fly-Buck Converter

Using a fly-buck converter (Figure 1a) as a simple two-output converter is proposed in [17,18]. Only one of the outputs is controlled, causing severe cross-regulation issues for the second output. In order to remediate the cross-regulation problem, adding an active switch to the secondary of the coupled inductor was proposed in [19].

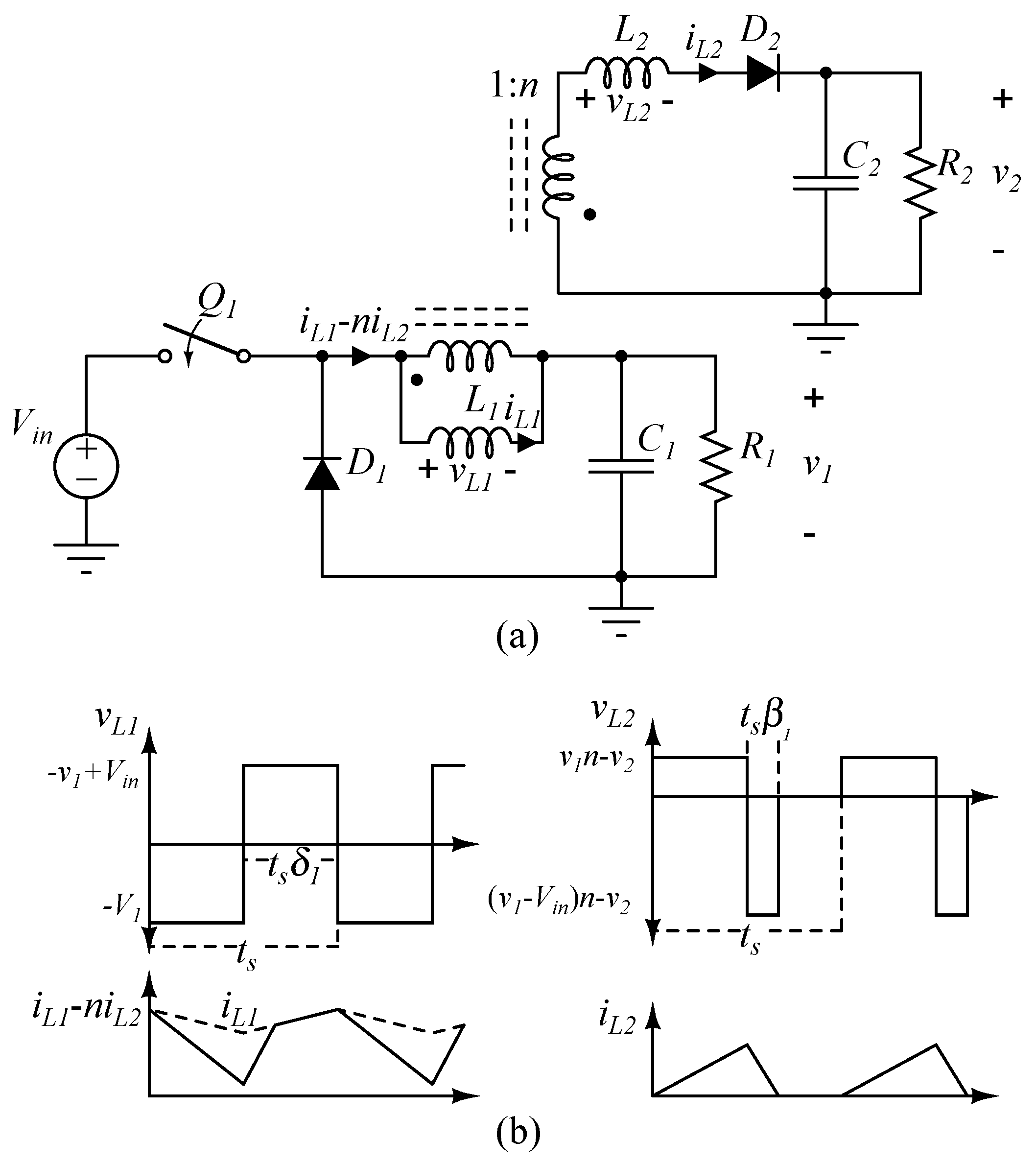

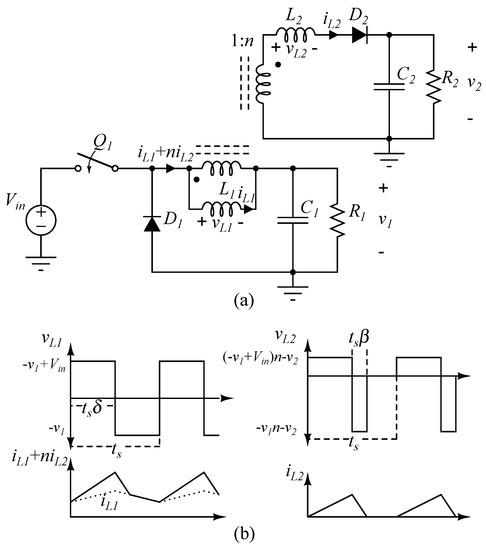

As an alternative to the conventional uncontrolled fly-buck converter, Figure 2a shows a two-output buck converter whose second output is obtained from a flyback type coupled inductor with magnetizing inductance L and substantial leakage inductance L. The steady-state equation of the first output voltage v is the same as for the conventional buck converter. When the first switch Q is off, energy is transferred to the secondary switch. The steady-state equation of the second output voltage v is:

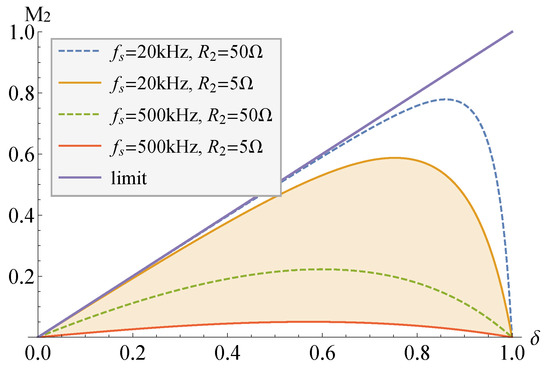

where n is the turns ratio of the coupled inductor, V is the input voltage, is the duty cycle of the switch Q, and is the normalized (t) demagnetizing interval of the leakage inductor L (see Figure 2b). As shown in (1), the switching period t is a possible control parameter of V. This explains why the switching frequency, f = 1/t, can be used to restrain the cross-regulation problem without adding additional components. Figure 3 is constructed from (1) to show the regulation that is possible with the switching frequency.

Figure 2.

(a) A fly-buck type two-output buck converter; (b) Voltage and current waveforms of the magnetizing and leakage inductances of the coupled inductor v, i-ni, v and i, respectively.

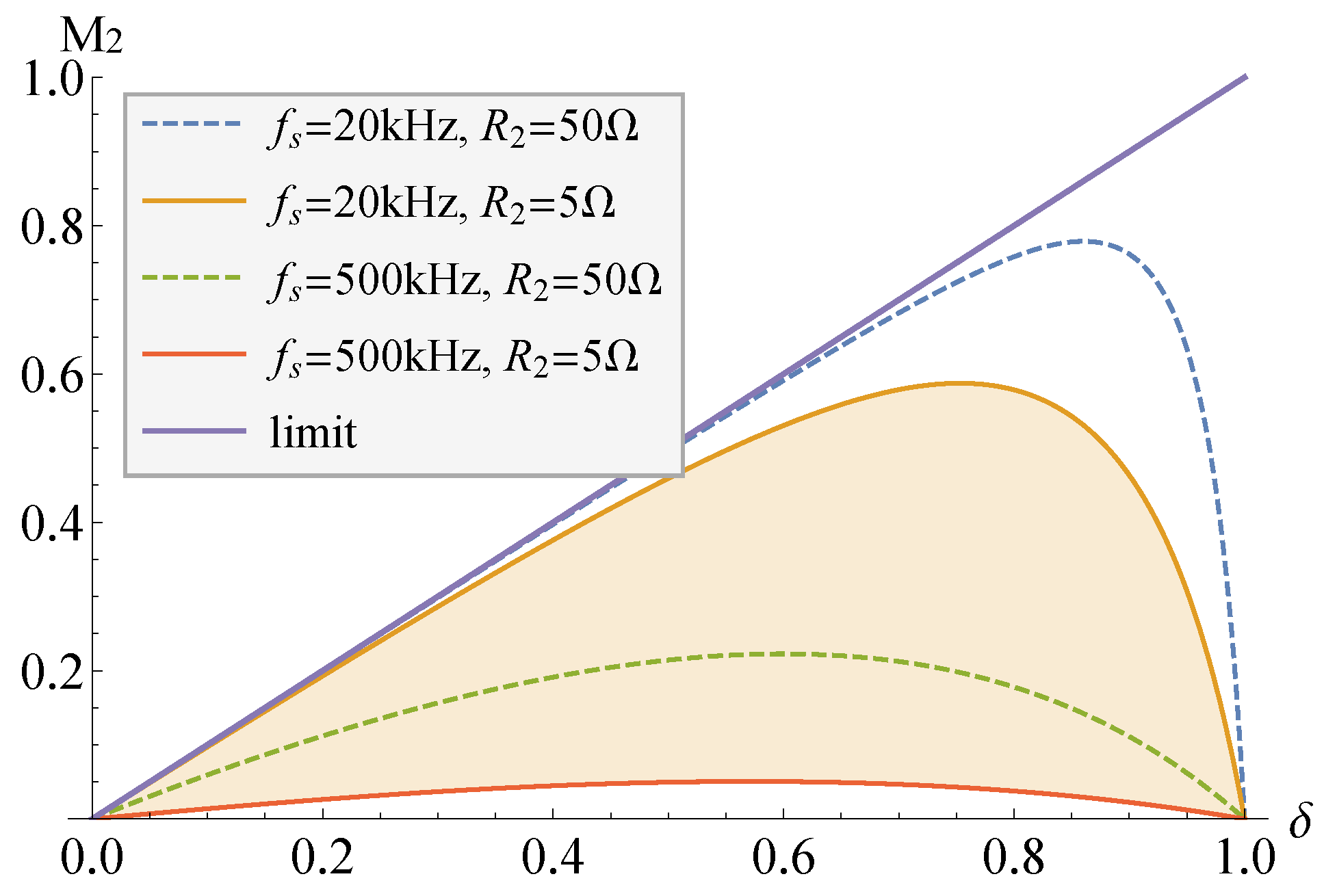

Figure 3.

Conversion ratio of the second output, M = v/V, versus the duty cycle at different switching frequencies f combined with the second load R of the fly-buck converter when the turns ratio of the coupled inductor n is 1. For the other components, see Table 1. Results are obtained by using (1).

From Figure 3 it can be deduced that it is preferable to adjust the second output in the fly-buck mode when the duty cycle is higher than 50%. This is because more energy can be transferred during the switch-off period to support a wider range of load conditions.

2.1.1. Design Criteria

L’s value depends on the turns ratio of the coupled inductor, n. However, n needs to be known to calculate L. The minimum value of n is:

and so n can be calculated from (1) by numerical iteration. If a higher L inductance is needed, it can be increased by additional inverse windings [20] or by changing the overlap ratio of the secondary winding [21].

Inductor L is needed to adjust the second output v. L’s inductance should be relatively small compared to the magnetizing inductance in order to correctly operate this second output in DCM. Moreover, L is also used to restrict the peak value of the inductor current i. It follows that

For the fly-buck converter, the peak current of ni should be lower than the minimum current of i if a conventional buck converter is used:

where Δi is ripple of i, as i-ni cannot be negative because of the diode D. When this condition is false, i decreases and the first output voltage drops. Instead of a diode, a MOSFET can be used to allow i-ni to become negative.

2.1.2. Experimental Results

A fly-buck converter whose output voltages are 15 V/1.5 A and 5 V/0.8 A was built. The parameters of the prototype are shown in Table 1. The 15 V output was chosen as the reference output because the available power from the reference output is higher than that from the second output.

Table 1.

Components of the fly-buck and forward-buck two-output prototypes.

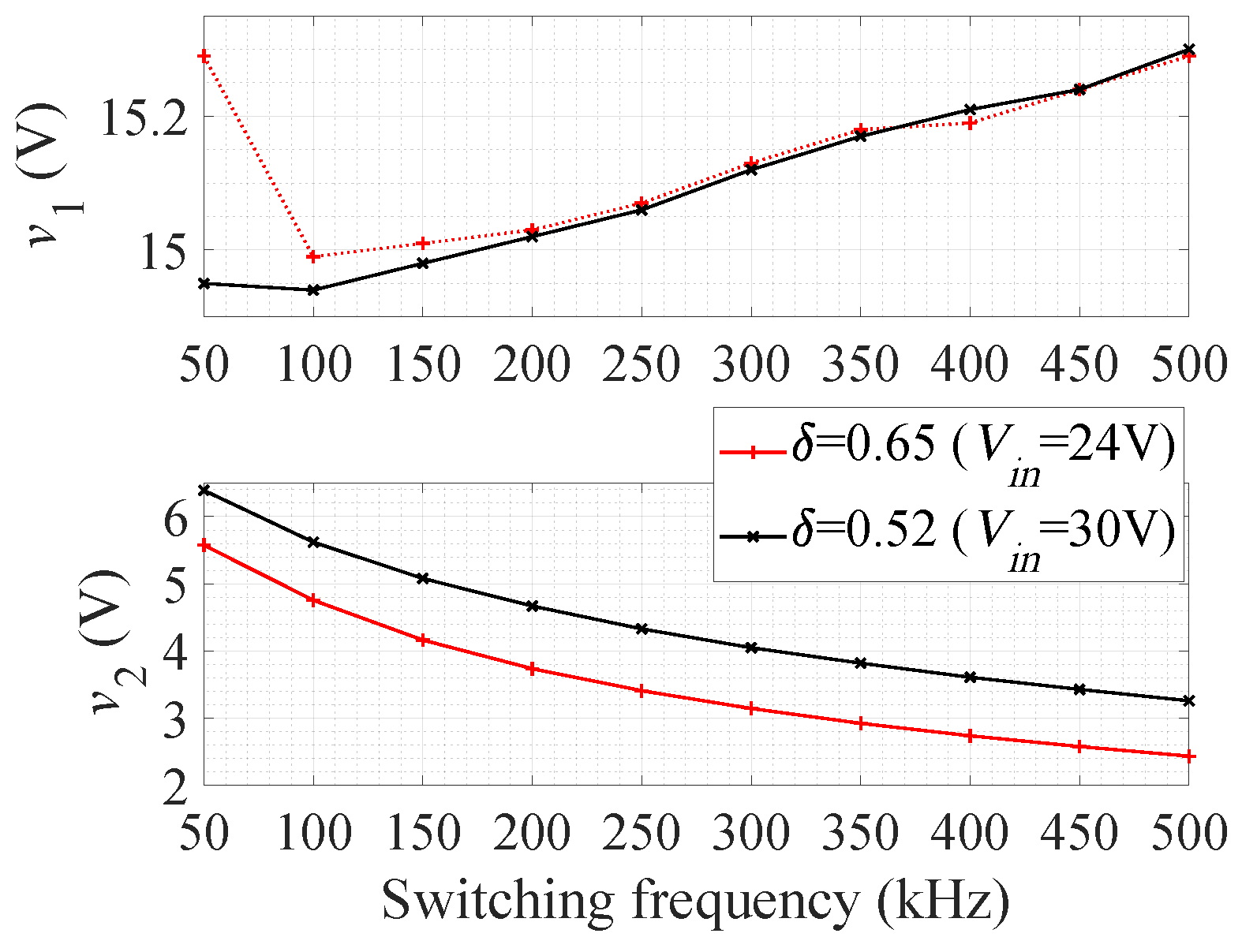

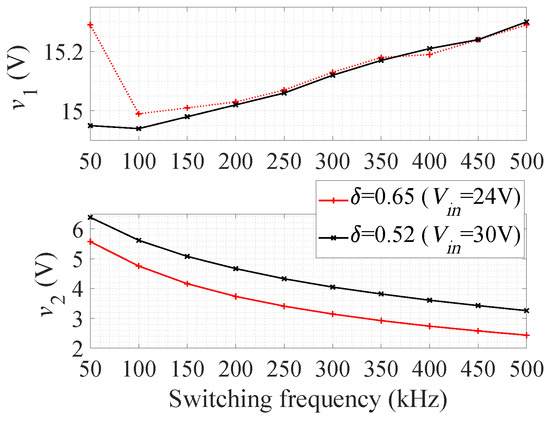

Figure 4 shows that v changes for different switching frequencies. The duty cycle is kept the same for both these plots. There is a small change in v when f changes because of cross-regulation. Figure 4 shows that the voltage range of the second output is slightly larger when is higher.

Figure 4.

Experimentally measured output voltages of the proposed fly-buck two-output converter for different f (R = 10 and R = 6.25 ).

In Table 2, the control values and efficiencies of the circuit at different loads are given. When the first output current i is changed from 0.75 A to 1.5 A, must be increased from 58.7% to 64.5%. Note that is the control parameter of v. Therefore, it is possible to increase f from 27 kHz to 84 kHz to keep v at 5 V. Even if f is not a control parameter of v, is slightly changed from 64.5% to 64.2% when the second output current i is changed from 0.8 A to 0.2 A. The reason for this slight change is again due to cross-regulation issue. An appropriate PWM-PFM method can keep the output voltages the same at both operating points.

Table 2.

Experimental results of the fly-buck converter (V = 24 V).

As shown in Table 2, the minimum efficiency of the circuit is 91.4% when i is at the minimum operating point. The more i increases, the more the efficiency increases. The efficiency at the lower switching frequencies is generally lower than the efficiency at the higher switching frequencies. This is because the ripple of i decreases when f increases. The conduction losses also decrease because of this reason.

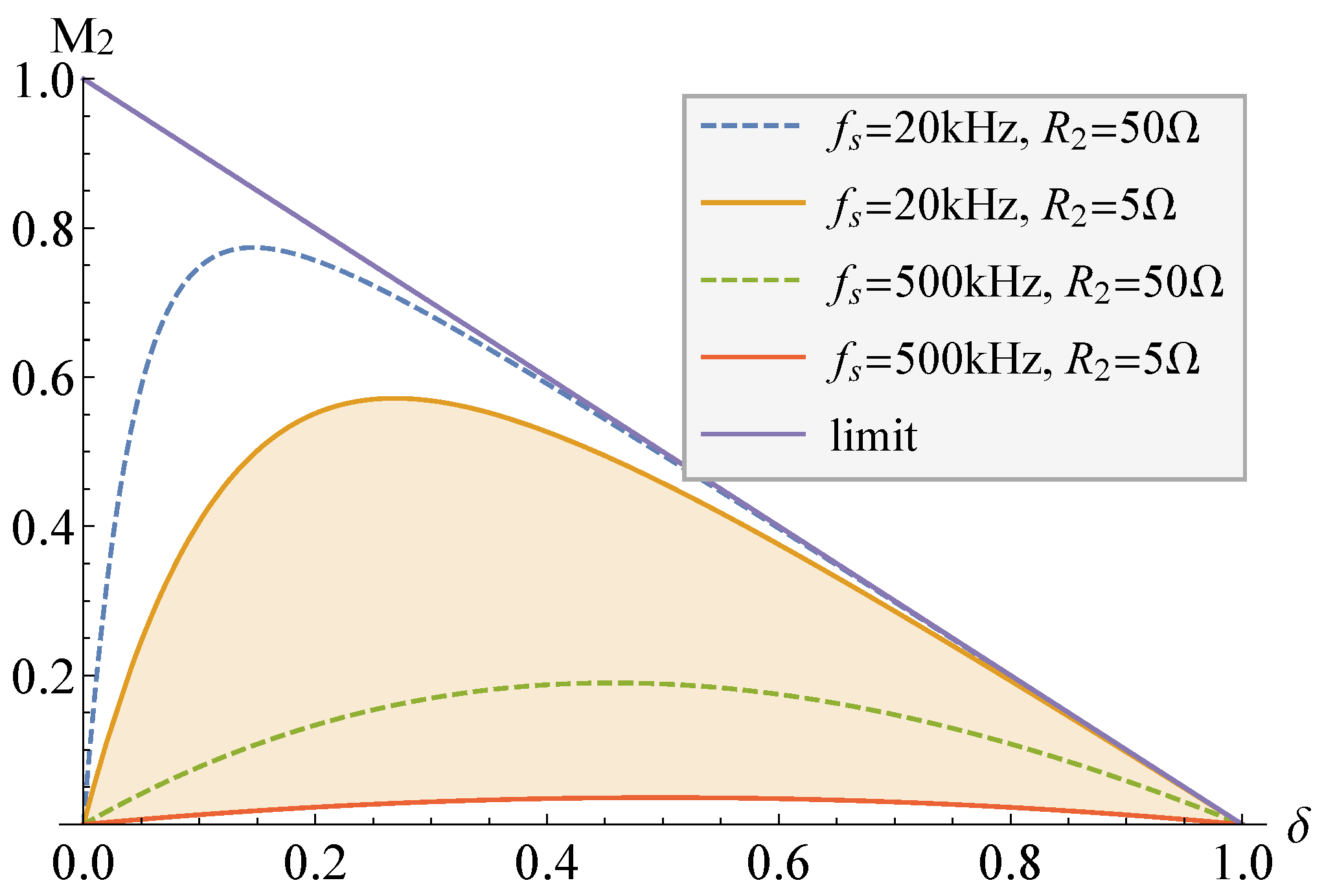

2.2. Two-Output Forward-Buck Converter

Figure 5a shows a two-output forward-buck converter where the second output is obtained by introducing a forward-mode coupled inductor. The circuit is the same as for the fly-buck circuit, except that the polarity of the coupled inductor is reversed. When Q is switched on, energy stored in magnetizing inductor is transferred to the secondary. The conversion ratio of the first output voltage M is the same as for the conventional buck converter. The value for the second output voltage v can be calculated by the following equation:

Figure 5.

(a) Forward-buck type two-output buck converter; (b) Voltage and current waveforms of the magnetizing and leakage inductances of the coupled inductor v, i + ni, v and i, respectively.

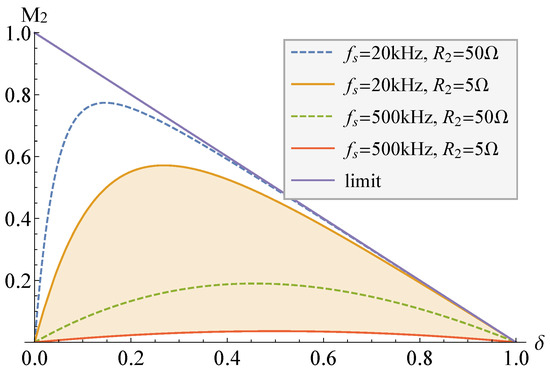

As shown in Figure 6 and (5), the switching frequency t = 1/f can be used to adjust the second output voltage. Also, Figure 6 shows that the conversion ratio range increases when the duty cycle decreases. This is the opposite situation to that of the fly-buck converter (see Figure 3 and Figure 6). The polarity of the transformer can be selected, depending on as required by the application, to create the widest possible voltage range for the second output. In particular, if is less than 0.5, the forward-buck topology is selected, otherwise the fly-buck topology is more appropriate.

2.2.1. Design Criteria

The minimum value of the turns ratio n is:

The initial n-value can be computed from (5) by using numerical procedures.

A leakage inductance L is needed to adjust the second output v. The peak value of the inductor current i is required for the selection process:

For the forward-buck type, the average of the current i must be lower than the minimum current of i:

This is because i + ni cannot be negative because of the diode D. This is the same reasoning as applies to the fly-buck type.

2.2.2. Experimental Results

A forward-buck converter with outputs of 12 V/1.5 A and 5 V/0.6 A was designed and built. The parameters of the prototype, which were the same as for the fly-buck converter, are shown in Table 1. Figure 7 shows the experimental results of the change in v versus f, same as for the fly-buck converter. The change in f from 50 kHz to 500 kHz causes (approximately) a 3.5 V drop in v when = 0.42. v changes only +0.4 V from 50 kHz to 500 kHz, because of cross-regulation issues. This is enough to control the two-outputs independently, as Table 3 shows. The control values and efficiency of the forward-buck converter under different load conditions are also shown in Table 3. The efficiency at lower switching frequencies is generally lower than that at higher switching frequencies, matching the behavior of the fly-buck converter.

Figure 7.

Experimentally measured output voltages of the proposed forward-buck two-output converter depending on f (R = 12 and R = 8.3 ).

Table 3.

Experimental results of the forward-buck converter (V = 24 V).

3. PWM-PD Controlled Three-Output Converters

The PWM-PD method for non-isolated three-output dc-dc converters with two active switches is presented in [7,8]. It requires two square wave voltages and builds a third square voltage from them. The first and the second output voltage are controlled by and , respectively. The third output is adjusted by the duty cycle , which is equal to the total of and in [7,8]. This is why a third switch is not needed to obtain a third output; however, additional diodes and an extra magnetic core must be added [7,8].

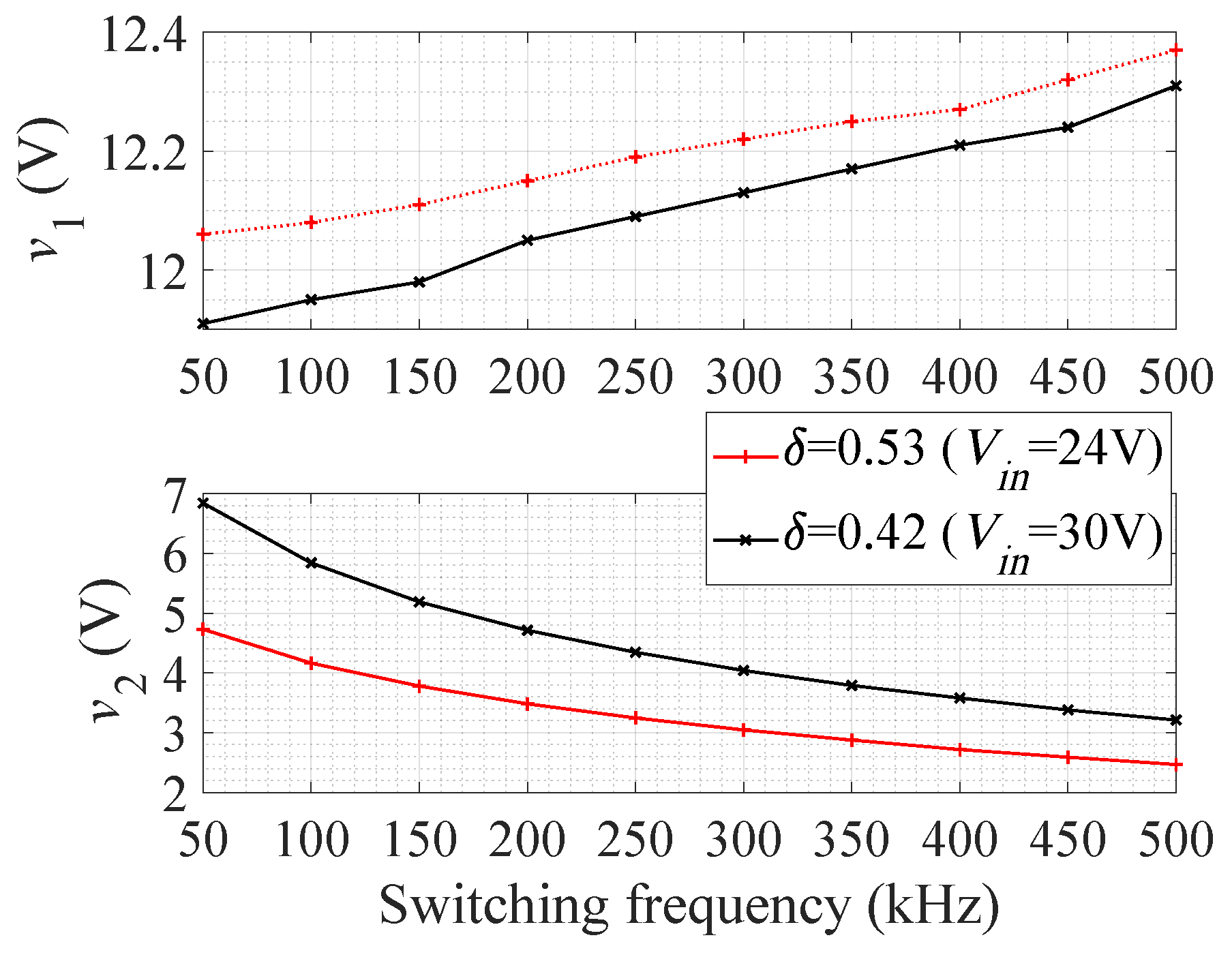

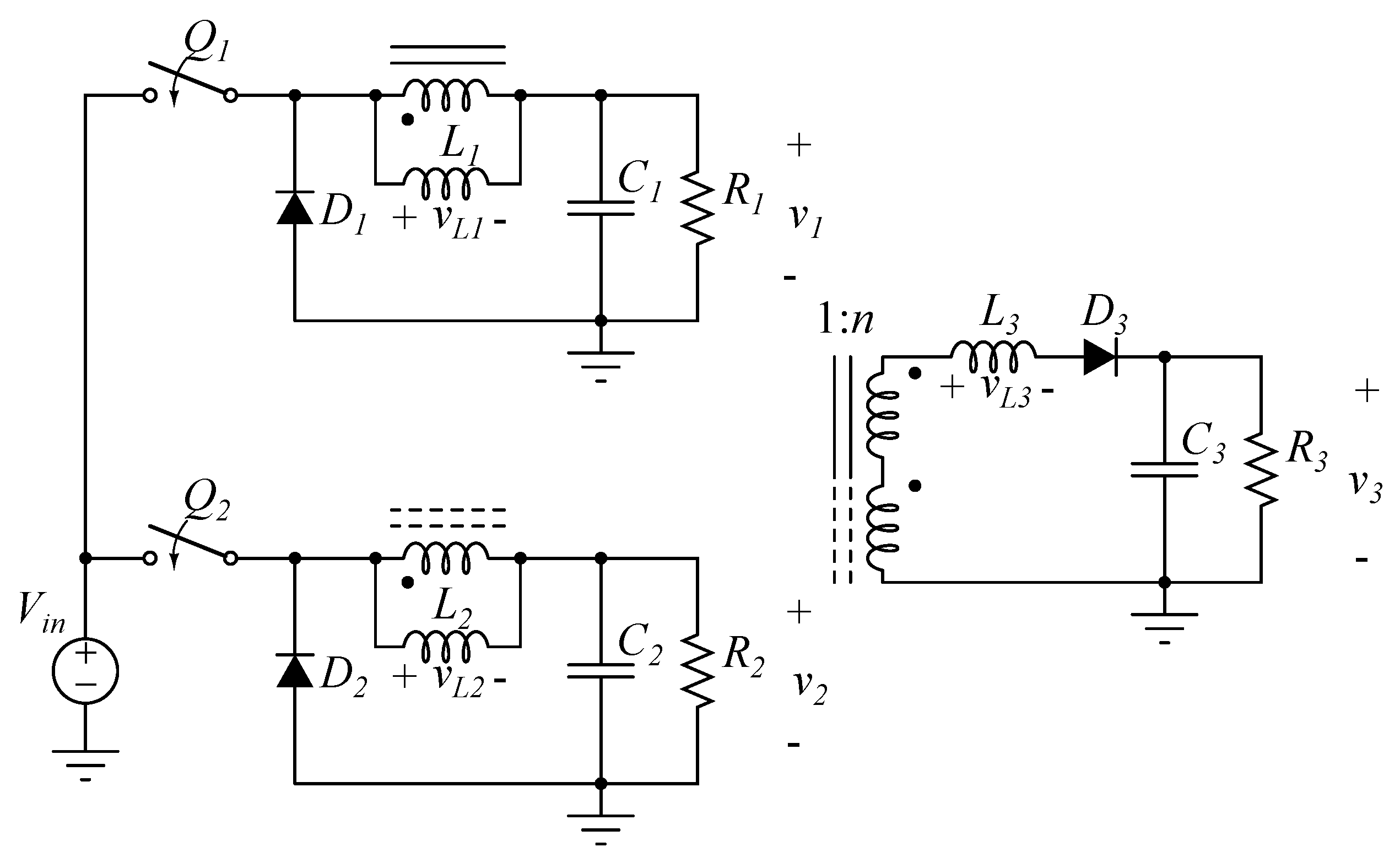

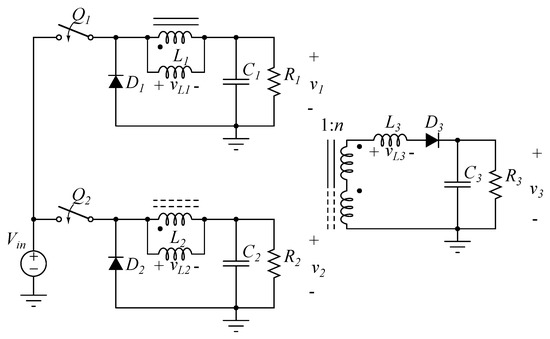

A PWM-PD controlled three-output converter which needs only two inductors is shown in Figure 8. In order to obtain the third adjustable output, additional windings are added to the inductors L and L of the buck converters. To use this method, the switching frequencies of the active switches should be the same. The polarity of the windings can be chosen in two ways, and boost or buck-boost converters may be used instead of buck converters. The secondaries of the coupled inductors are connected in series so that the combined leakage inductance of the coupled inductors, L, can be used to adjust the third output. This third output is adjusted by the duty cycle , which is a function of the phase delay between the gate signals of Q and Q.

Figure 8.

PWM-PD controlled three-output forward-type buck converter.

3.1. A PWM-PD Controlled Fly-Buck Type Three-Output Converter

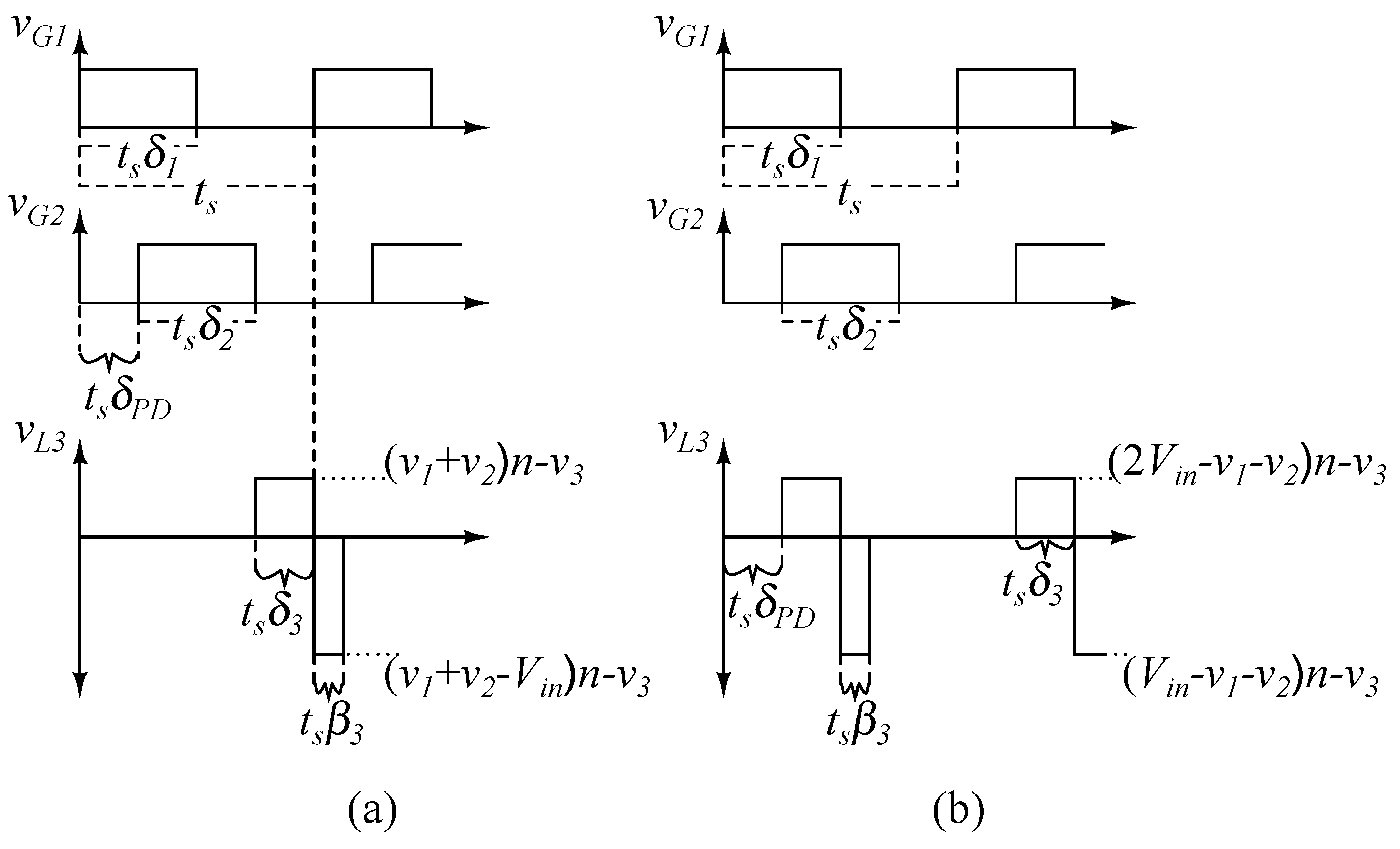

The secondary windings of the coupled inductors of the two buck converters are connected in series. L is equal to the total leakage inductance of the first and second coupled inductors. The polarity of the secondaries is similar to that of a flyback converter. When the voltage across both magnetizing inductors is negative, the energy is transferred to the secondary. The duty cycle of this third output square wave is

as shown in Figure 9a. The third output voltage v of the fly-buck type converter can thus be calculated as:

Figure 9.

The gate voltage of the switches v and v, and the voltage waveform of the tertiary inductor, v of (a) a fly-buck type converter and (b) a forward-buck type three-output converter.

3.1.1. Design Criteria

The minimum value of n is:

The current passing through L, i, is formulated as:

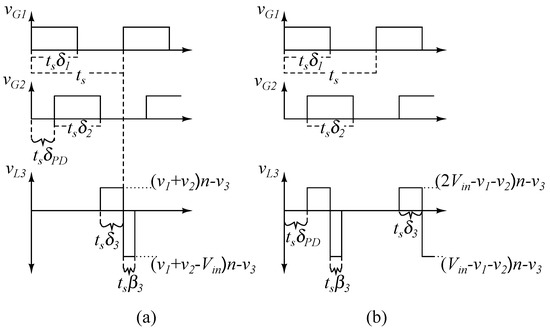

3.1.2. Experimental Results

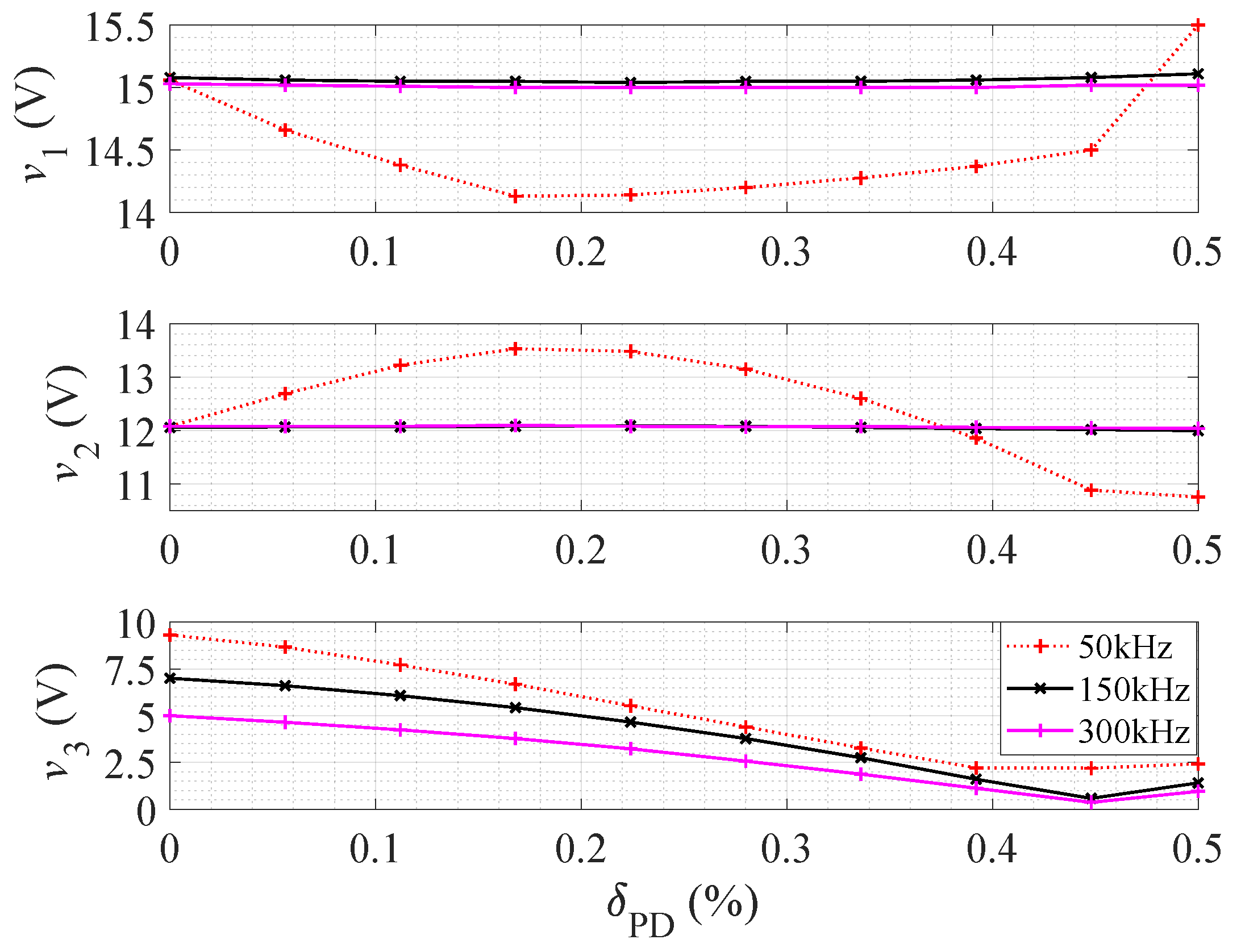

A fly-buck three-output converter was built to verify the preceding analysis. The parameters of the prototype were the same as for the two-output converters and are shown in Table 1. Figure 10 shows the experimental results for v and how they change as a function of the phase delay. The first output, 15 V/1.5 A, and the second, 12 V/1.5 A, are kept the same for different third-output voltages. The cross-regulation at 50 kHz is 2–3 V for v and v as shown in Figure 10. Note that the change in v and v is only 0.2 V at higher frequencies.

Figure 10.

Experimentally measured output voltages of the proposed fly-buck three-output converter, depending on different phase delays ( = 24 V, = 10 , = 8 and = 7.5 ).

Table 4 shows the operating points, control parameters and efficiencies of the converter for different loads. When or is chosen as the control parameter for the third output, the output voltages can be kept the same at different loads. For example, when only the third load is changed in the first four rows, then the related control parameter, the phase delay, is able to keep the third output constant, i.e., 3.3 V.

Table 4.

Experimental results with a fly-buck type three-output converter (V = 24 V and f = 150 kHz).

The efficiency of the converter is 94.4% at the rated load, and it can be even higher for other loads, as shown in Table 4.

3.2. A PWM-PD Controlled Forward-Buck Type Three-Output Converter

The forward-buck type three-output converter is the same as a fly-buck type three-output converter, except for the polarity of the secondary windings. The polarity of the secondaries is similar to that of a forward converter. When the voltage across both magnetizing inductors is positive, energy is transferred to the secondary.

The of the forward-buck circuit is:

as shown in Figure 9b. The third-output voltage v can be calculated as:

3.2.1. Design Criteria

The minimum value of n is:

The current of L, i, is formulated as:

3.2.2. Experimental Results

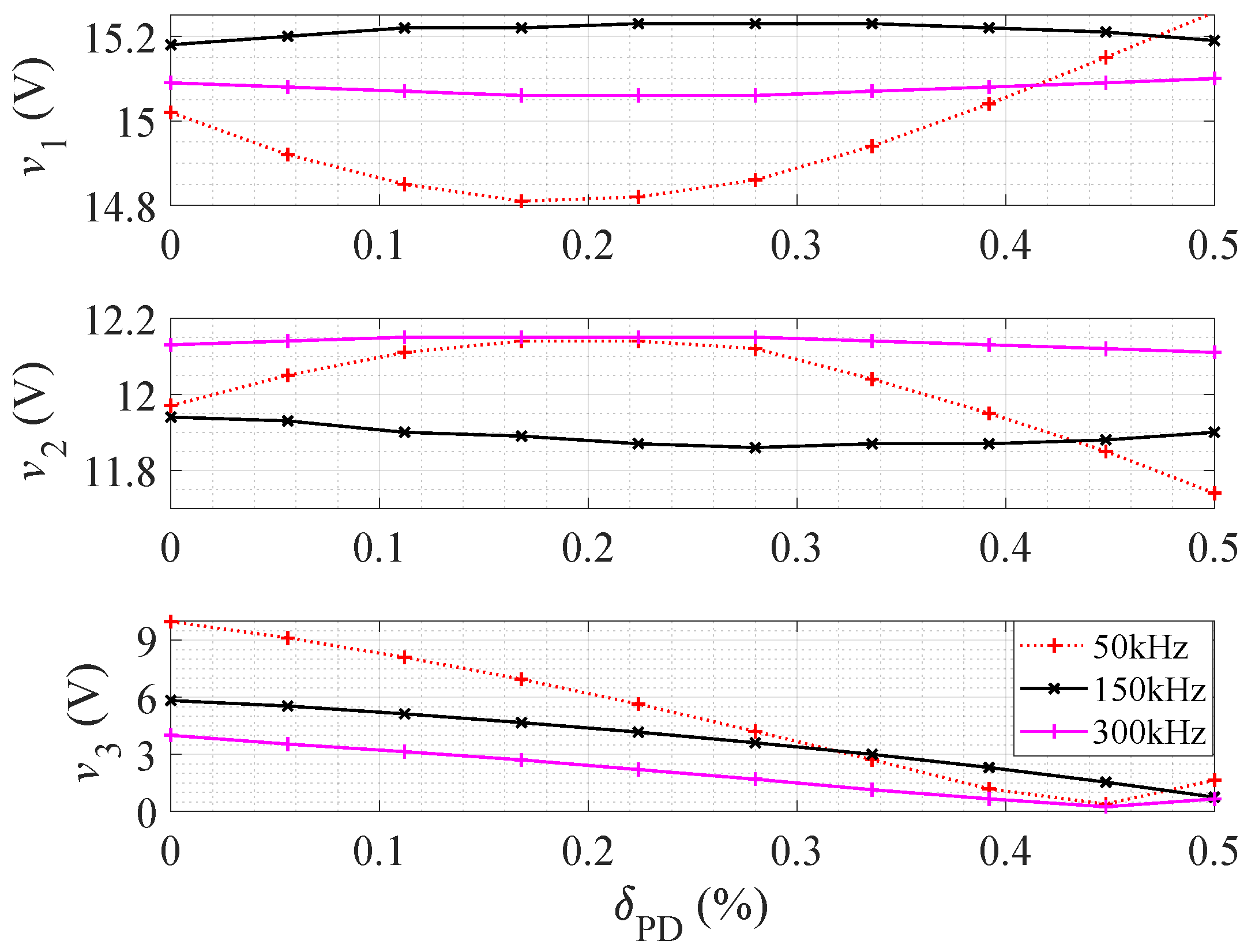

The same components used for the fly-buck type were used to build a forward-buck three-output converter. Figure 11 shows the experimental results of v, as a function of . Figure 11 shows that cross-regulation for the forward-buck converter at 50kHz is appreciably worse than at the other switching frequencies.

Figure 11.

Experimentally measured output voltages of the proposed forward-buck three-output converter depending on different phase delays ( = 24 V, = 10 , = 8 and = 7.5 ).

Table 5 shows the operating points, control parameters, and efficiencies of the forward-buck type converter for different loads. It can be seen that or is a valid control parameter of the third output. The efficiency of the converter is 94.4% at the rated load. The efficiency values of the converter are similar to those for the fly-buck type.

Table 5.

Experimental results for a forward-buck type three-output converter (V = 24 V and f = 150 kHz).

4. PWM-PFM-PD Controlled Five-Output Converters

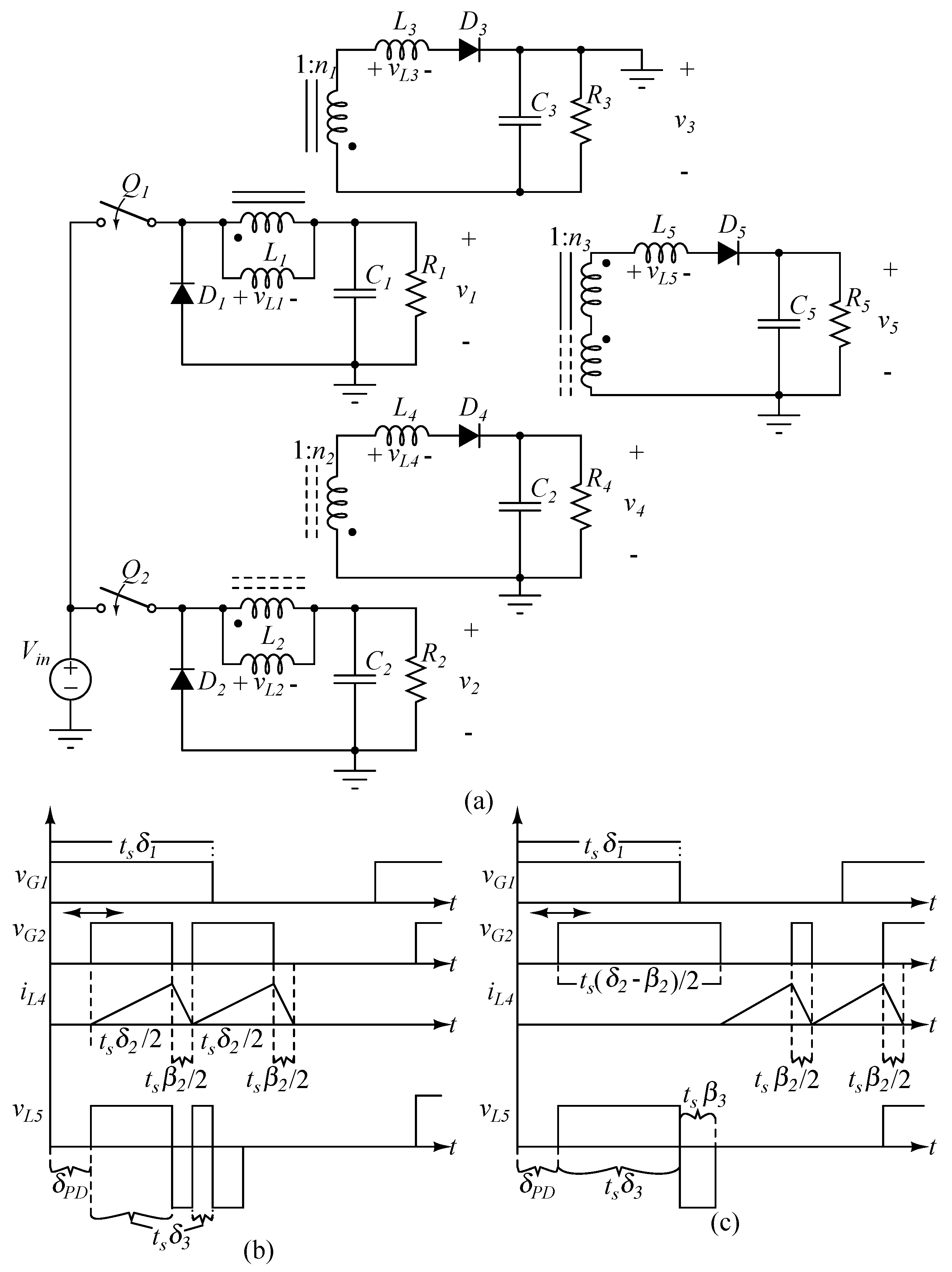

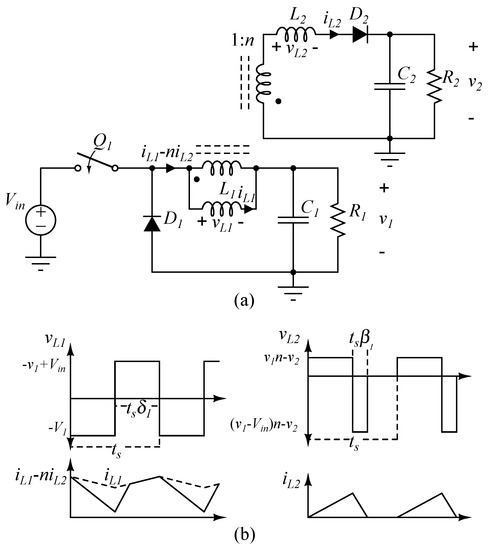

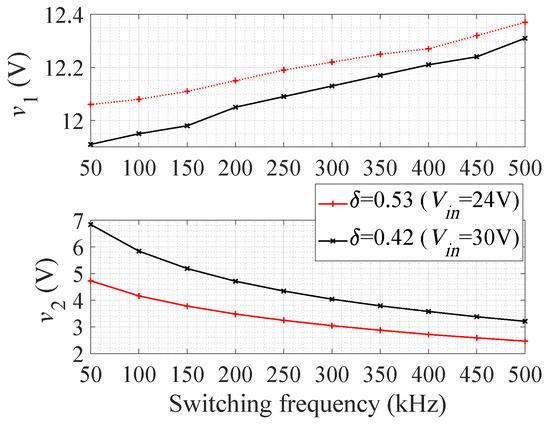

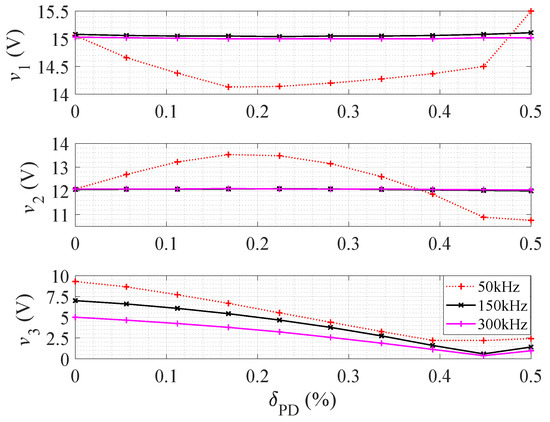

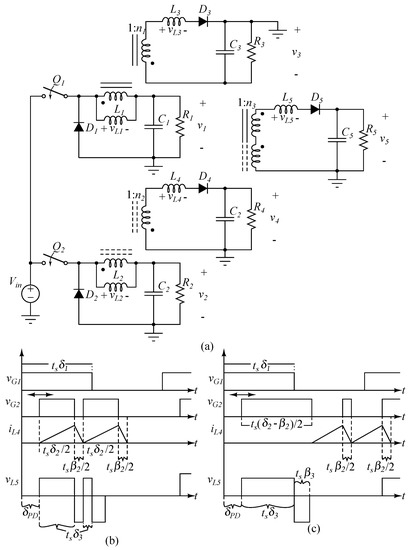

In this section, the PWM-PFM controlled two-output and the PWM-PD controlled three-output converters are merged to obtain five independently controlled outputs. The resulting PWM-PFM-PD controlled five-output converter, which has only two coils and two active switches, is shown in Figure 12a. In order to obtain the extra three adjustable outputs, two additional windings are added to the inductors of the buck converters and flyback diodes are then connected to the secondaries of these coupled inductors to construct the third and the fourth output. The leakage inductors L and L are designed to control the third and the fourth output voltage in DCM. Therefore, the total of the leakage inductance of the coupled inductors L, which is obtained by connecting the tertiaries of the coupled inductors in series with diodes, can be used to adjust the fifth output by PD.

Figure 12.

(a) PWM-PFM-PD controlled five-output converter. Waveforms of gate voltages, current through the fourth inductor and the voltage across the fifth inductor when the fifth output is connected in (b) a fly-buck type and (c) forward-buck type converter.

In order to use the PD method with non-equal frequency waveforms, it is proposed that the second switch operates in “burst” mode. The second switching frequency is synchronized to the first switching frequency, = 1/. It is then possible to insert a PD between the starting points of the signals as shown in Figure 12b,c. Frequency can be represented by:

The PWM signal is divided into segments depending on the required number of pulses, k. In burst mode, the turn-on time of the second signal is affected by the demagnetizing ratio of the fourth inductor as can be seen in Figure 12b,c. When the inductor current drops to zero, the next segment is triggered. The inductor voltage waveform of the fifth output for the fly-buck type converter is divided into k pulses as shown in Figure 12b. in burst mode is:

The range of in burst mode is reduced by k and for the fly-buck type’s fifth output. As shown in Figure 12c, instead of dividing the PWM signal into equal sub-pulses, there is a gap between the pulses in the case of a forward-buck type converter. This gap is needed for the demagnetizing duration of i to operate the fourth output in DCM. In other words, the demagnetizing duration does not affect the range of , and (13) can be used for the forward-buck type converter in burst mode. The forward-buck type converter for the fifth output is preferable to the burst mode as it has a wider effective range and operates with less adverse effects.

4.1. Topology Comparison

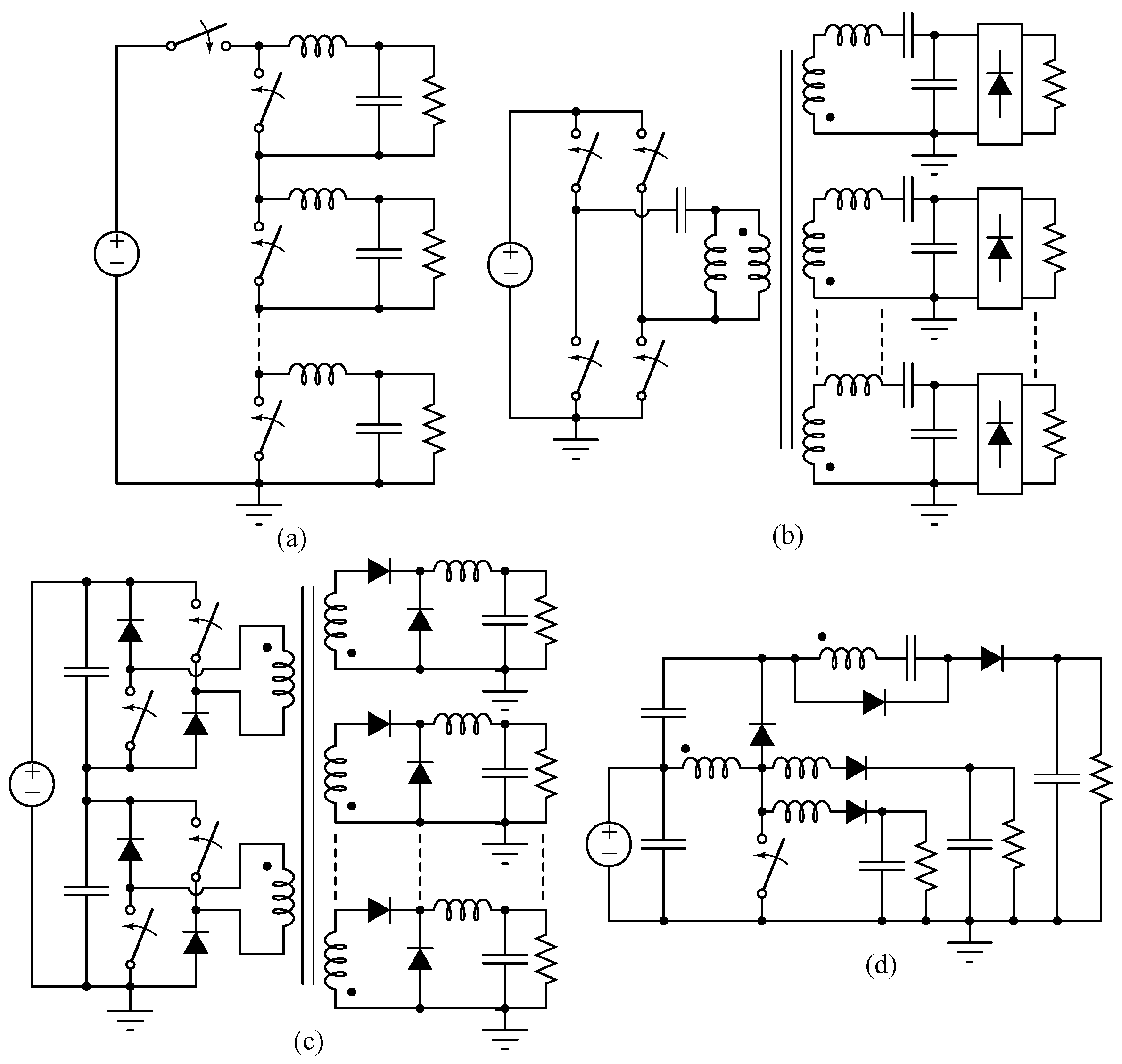

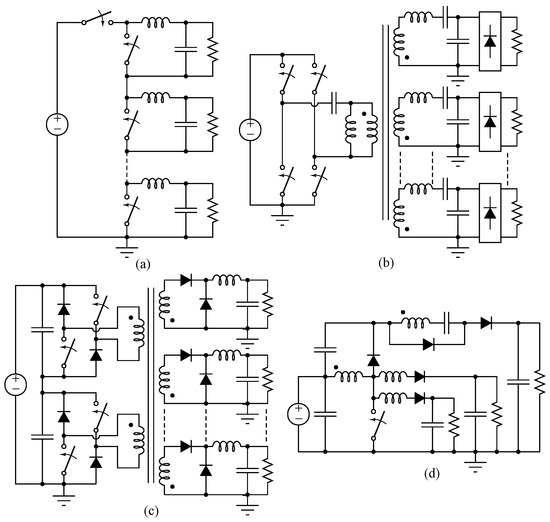

One method to reduce the size of a converter is to reduce the total number of components, e.g., by sharing common functionality as mentioned in the previous sections. Comparisons in this respect for the proposed five-output converter with similar research in [22,23,24,25] are summarized in Table 6. Figure 13 shows the reviewed multiple-output dc-dc converters, i.e., (a) the integrated multiple-output synchronous buck converter (IMOSBC) from [22]; (b) the multiple-output narrow-band resonant converter (MONBRC) from [23]; (c) the multiple-output two-transistor forward converter (MOTTFC) from [24] and (d) the single-input multiple-output dc-dc converter (SIMOC) from [25].

Table 6.

Comparison of multiple-output converters.

Figure 13.

Multiple-output dc-dc converters from the literature: which are (a) an integrated multiple-output synchronous buck converter (IMOSBC) in [22]; (b) a multiple-output narrow-band resonant converter (MONBRC) in [23]; (c) a multiple-output two-transistor forward converter (MOTTFC) in [24] and (d) a single-input multiple-output dc-dc converter (SIMOC) in [25].

The IMOSBC uses fewer switches and diodes than those of its individual converters, but Figure 13a shows that it does not have less magnetic components. The MOTTFC from [24] and SIMOC from [25] are conceived to minimize cross-regulation, because the converters can not regulate all their outputs independently. Although the MONBRC regulates all outputs independently, it has more components than those of five individual converters, as shown in Figure 13b. As can be seen in Table 6, the proposed converter has the least number of components per output when compared to the others.

TMONBRC, MOTTFC and SIMOC are designed for high conversion ratios. However, the proposed topology can use forward converters instead of the buck converters for its first and second outputs, thereby also achieving high gain.

4.2. Design Criteria

The design rules for the PWM-PFM and PWM-PD converters can also be used for PWM-PFM-PD converters. As an example, the design of a five-output converter is shown in this subsection. The input voltage V is 24 V, and the outputs are 15 V/1.5 A, 12/1.5 A, −5 V/0.8 A, 5 V/0.6 A and 3.3 V/0.45 A, respectively.

The first and second outputs are operated in CCM. Therefore, the heaviest loads, 15 V/1.5 A, 12/1–1.5 A, are selected for these outputs. The topology can be selected to be buck, boost or buck-boost depending on the input voltage. Moreover, and should be close to 0.5, depending on the and values, in order to ensure a wide . In this chapter, the requirement is a buck converter; and so only the buck converter is analyzed.

The third and fourth outputs are operated in DCM, and a fly-buck or forward-buck type is selected according to the and values, because how the range of the fly-buck and forward-buck type converters changes depends on the and values.

Given these considerations, the 5 V and +5 V outputs are chosen for these outputs and the fly-buck topology is used because ≥ 0.5. Accordingly, the turn ratios of the coupled inductors n and n are chosen to be 0.707.

The fifth output voltage is 3.3V. The forward-buck type in burst mode is selected to control this output by PD, as discussed before.

The design of this output is similar to that of the third and fourth output. The turns ratio of the coupled inductor’s n is calculated from (13), depending on the maximum and minimum load values. n is selected to have the same value, 0.707, as n.

The parameters of the five-output converter prototype are the same as for the two-output converter, and can be found in Table 7.

Table 7.

Components of the five-output converter prototypes.

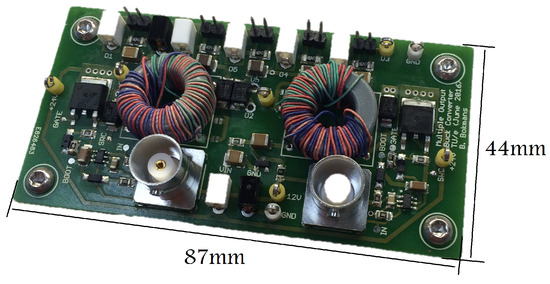

4.3. Experimental Results with the Open-Loop Five-Output Prototype

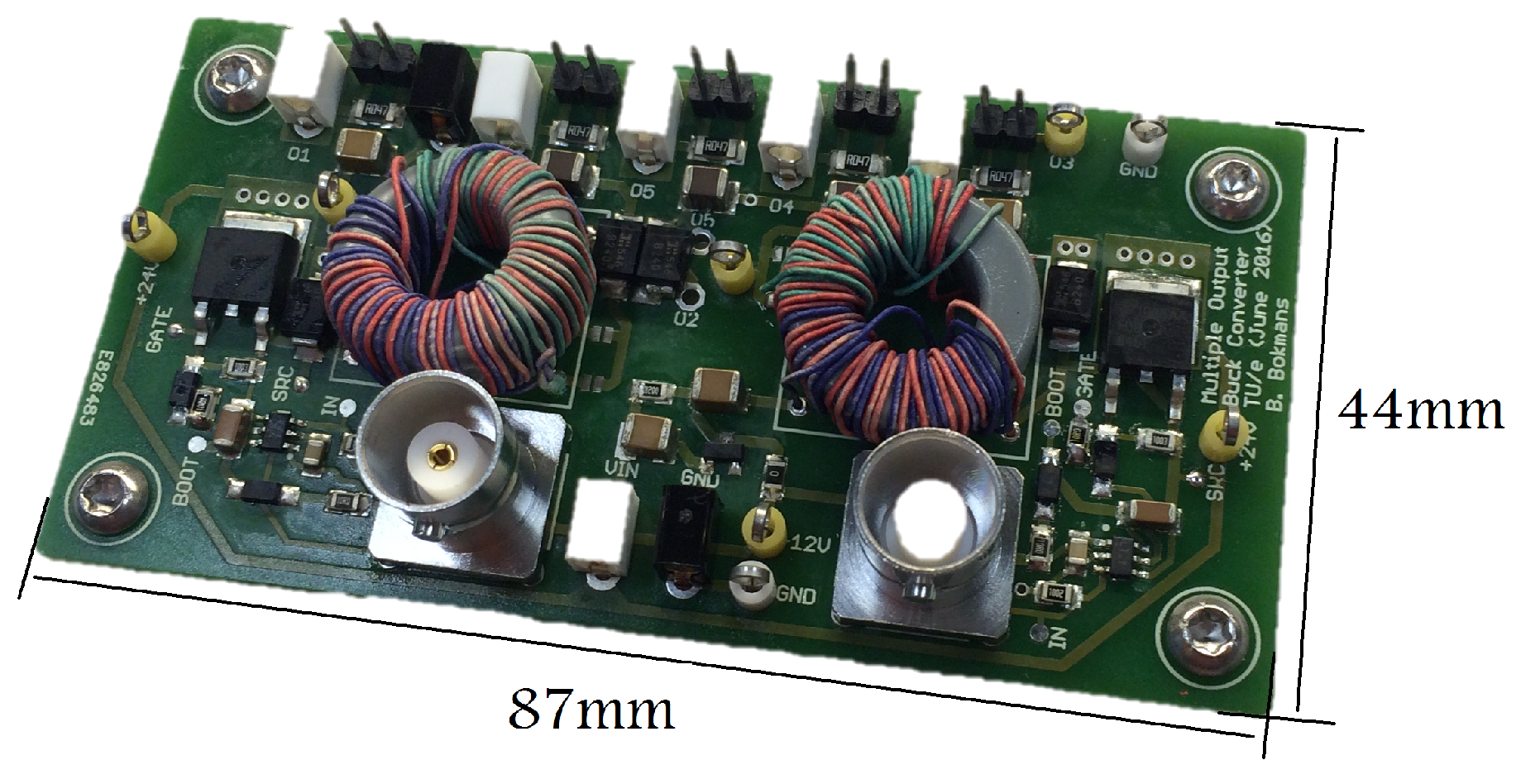

After the design and the simulation were complete, a hardware prototype was built as shown in Figure 14, and tested in order to verify the analysis.

Figure 14.

Five output converter prototype.

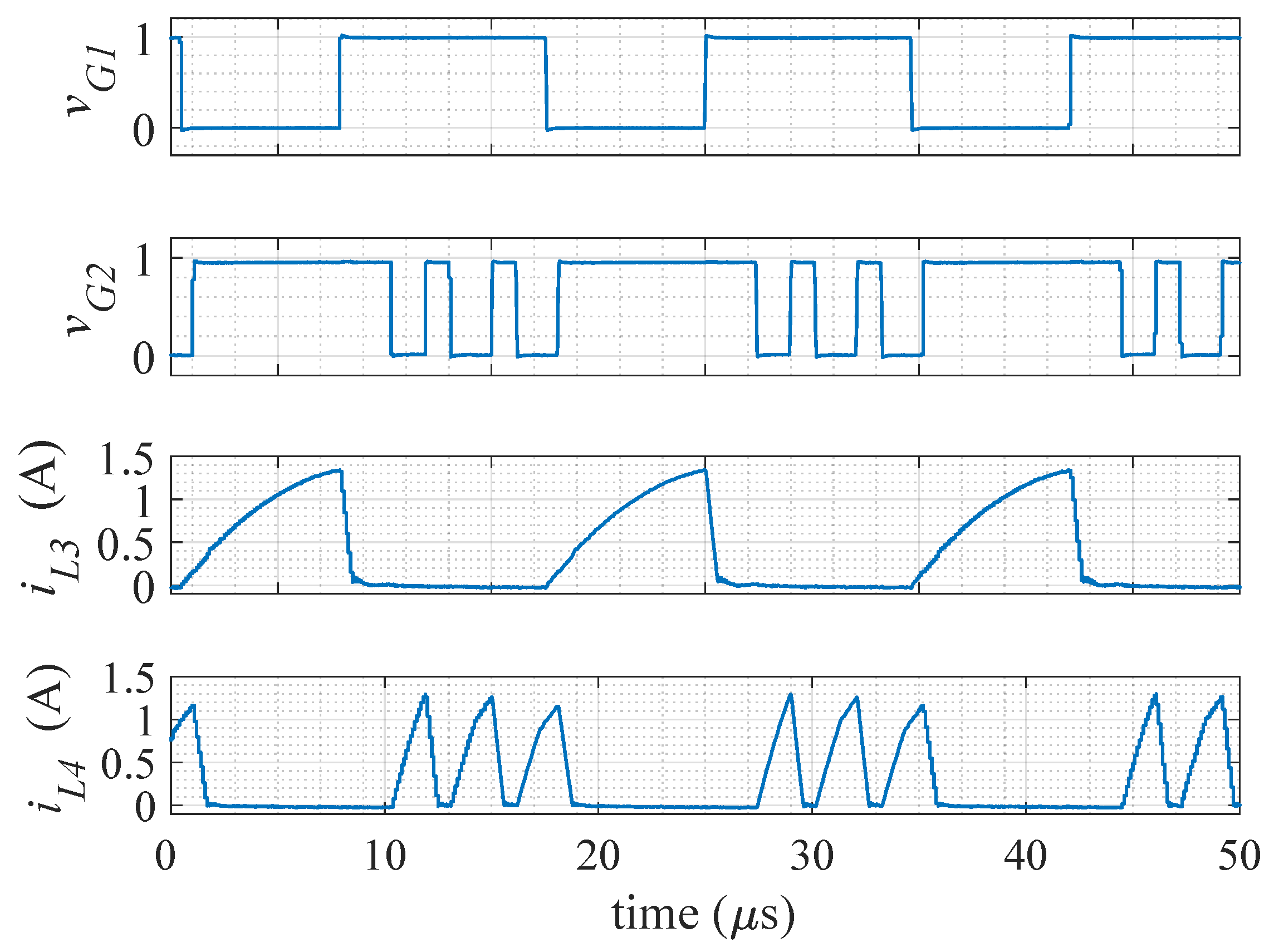

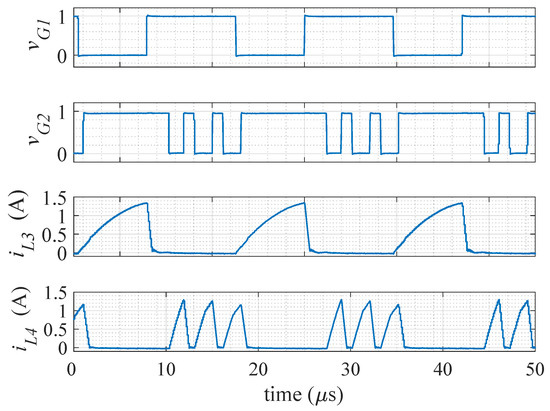

A two-channel waveform generator was used to generate all PWM signals. The second output of the waveform generator is a single signal, of which the duty cycle, phase delay, and number of pulses can be controlled independently, as shown in Figure 15.

Figure 15.

Experimental waveforms of the gate voltages and , and current through the third and fourth leakage inductors when = 56.4%, = 57.3%, = 16%, f = 58.5 kHz and k = 3.

Table 8 and Table 9 show the operating points, control parameters and efficiencies of the five-output converter for a number of different loads. The efficiency varied between 92.5% and 93.5%.

Table 8.

Experimental results for a five-output converter (V = 24 V).

Table 9.

The control parameters of a five-output converter at the operating points shown in Table 8.

5. Modeling

Models of dc-dc converters are required to design the controller. Therefore, many modeling researches for PWM converters, which are given either continuous or discrete-time modeling, have been made. However, the sequence of state variables to each other is important for discrete-time modeling. For instance, the demagnetizing time of , can be higher than the total of the phase shift time and the demagnetizing time of , at the five-output converter. Therefore, at least two models, with and , are required for this condition when using discrete-time modeling. In addition, the sequence of the state variables is independent to each other with state-space averaging. Moreover, the work in [26] shows that asymptotic stability of the averaged system model implies asymptotic stability of the actual system. Therefore, the controllers can replicate the design of these models.

In this section, two PWM signals are used in order to describe the PWM-PFM-PD control scheme. Therefore, five-output voltages can be regulated independently. First, state-space average (SSA) model is used for the multiple output converter. The large-signal models are nonlinear, and the models are linearized around a desired operating point by Taylor-expansion. After obtaining large and small models of the five-output converter, the models are compared by simulation to verify them. Depending on the small signal model, the dominant poles of the system are placed in the desired points at close-loop. Then, to decrease the steady-state error of the system, error cancellation algorithm is proposed. In the end, the experimental results of the prototype are given to verify the analyses.

All components of the converter are considered ideal. There are ten state variables, , , , , , , , , and , to model the converter. When burst mode is on (k > 1), the frequency of is different than the main frequency, . The state variables at the different switching frequencies for SSA is then explained. One of the advantages of SSA is that the state variables can be averaged independently from each other.

5.1. Averaging and Correcting

Suppose the dynamics of a state variable of a dc-dc converter can be described by a piecewise-linear state-space model as:

where is the number of state variables, is the switching function, is the number of the switching stage (the sub-circuit), and are the state coefficients. Then state-space averaging (SSA) technique can be applied to a state variable that has multiple switching functions according to the following average model:

Generalizing this procedure, it was taken into account that a state variable may depend on all other state variables. For instance, state variable has two stages and each state equation is multiplied by the related switching interval in SSA. When these two stages are multiplied by the related switching interval and , they become:

And, after simplification:

Now consider that all state variables (, , , , , , , , , ) and input(s) () in Figure 12a are subjected to this averaging, then the differential equations that describe the multiple-output converter can be defined in vector notation as:

in which the state vector x and coefficient matrix are:

where

PWM converters that are operated in CCM have two switching intervals: the active switch is either on () or off (). In CCM, the average of the derivatives of the inductor current is the same as the product of the averages; and SSA is equal to explicit averaging of the circuit equations. Contrary to CCM, DCM operation involves an additional interval where the inductor currents and therefore its average is zero, and the average of this third interval is zero. In addition, in DCM the average of the product terms is not the same as the averaged product of the individual waveforms. The studies described in [27,28] explain this situation and offer a correction matrix. The difference between the actual average and SSA charging currents is shown, based on [27] in Table 10. The matrix corrects mismatch of the inductor currents in DCM as follows:

Table 10.

Charging capacitors over the entire period using an inductor operating in DCM.

With this correction matrix, the modified SSA model in (25) becomes:

5.2. Full-Order Averaged Models

It is possible to calculate what the average of the inductor currents is from the peak value of the inductor currents without requiring the demagnetizing duration ratios , and . The peak current of the inductor currents is defined as:

The average of the inductor currents can then be written as:

The demagnetizing duration ratios of the inductors operated in DCM can be found from the average value of the inductor currents, (36)–(38). Hence, the new demagnetizing constraints for the multiple output converter are:

Substituting these magnetizing durations, (39)–(41), into (32) gives the following full-order averaged model for the converter:

with

where

The state matrix includes switching frequency information, as shown in (43)–(46). Therefore, the model is able to predict correctly even when the frequencies are different and the burst mode is active. In fact, the frequency information of is defined as in (45), and, depending on the value of , the state variable changes correspondingly.

5.3. Linearization

The large-signal model is nonlinear since the state matrix in (43) changes for each operating point. The matrix can be rewritten in the following form:

where the state variable and the input vectors are:

The function in (49) is linearized by taking the first-order Taylor approximation around the operating point , according to:

where is the Jacobian matrix of with respect to the vector, and is the Jacobian matrix of with respect to the vector.

5.4. Discretization

The obtained SSA models in (49) are continuous, and they need to be discretized to be applicable to digital control. The discrete model can be described as:

where

where is the identity matrix, and is the sampling time of the discrete model. As is equal to the switching period of the converter, it is a variable.

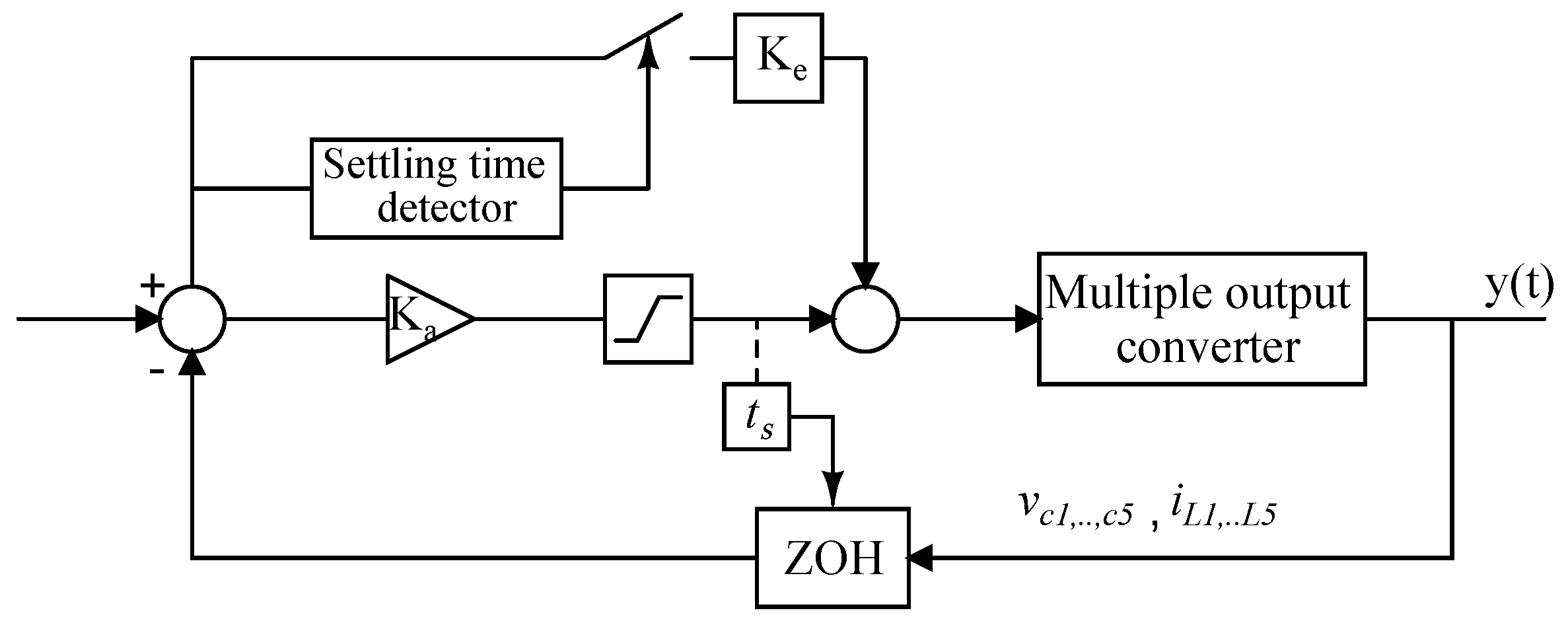

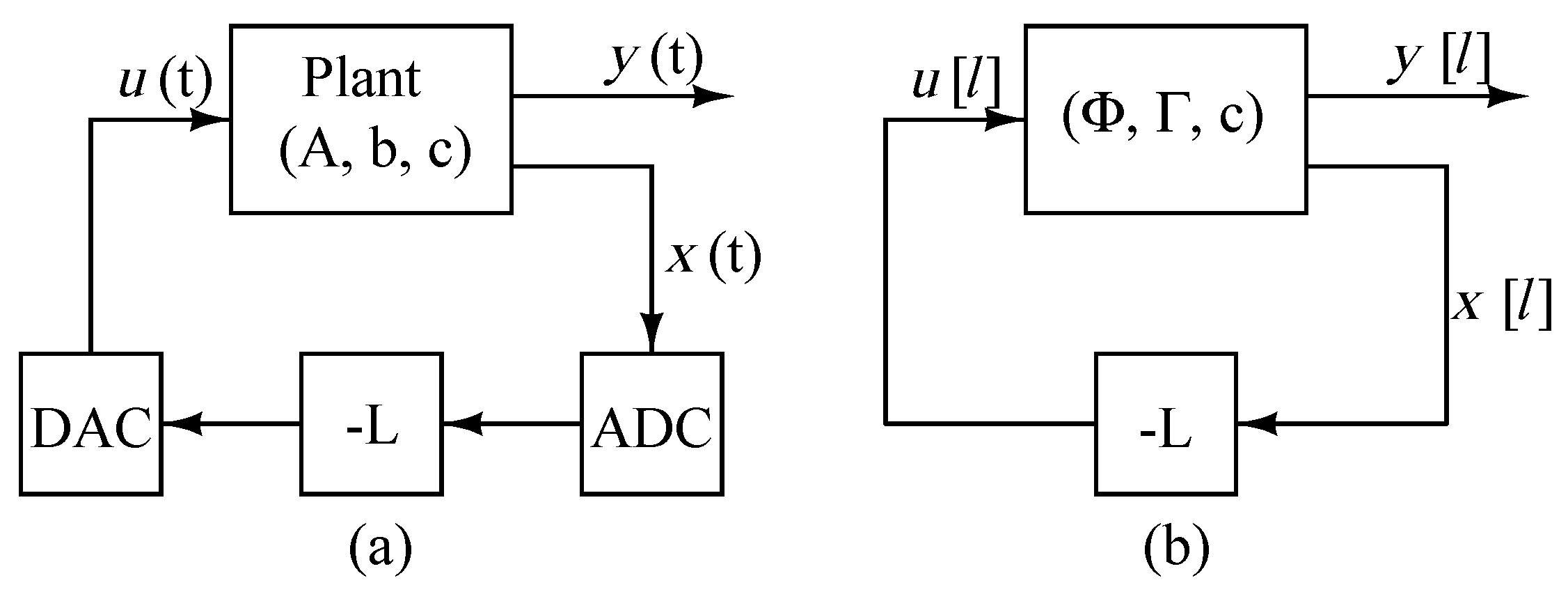

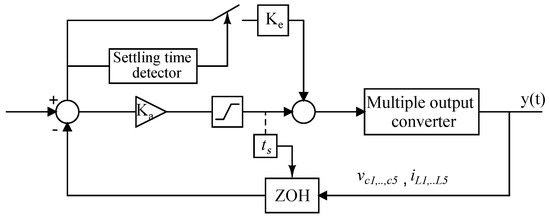

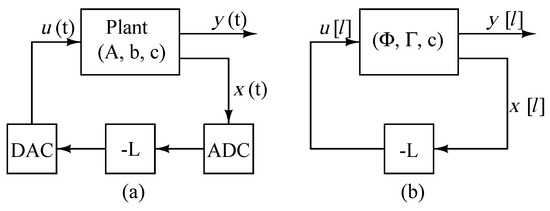

The analog-to-digital converter (ADC) of the system microcontroller is triggered by this variable switching period, as depicted in Figure 16. The microcontroller captures the inputs with a sample-hold circuit, and the data is kept constant until the next sample. The microcontroller also holds the outputs after the starting point of the PWM sequence.

Figure 16.

Closed-loop block diagram of a state-feedback controller with error cancelation function.

6. Digital Control of Multiple-Output Converters

In this section, the output voltage regulation of a multiple-output converter is studied.

PID (proportional-integral-derivative) controllers are still very popular in many control applications thanks to their simple structure and performance. Integral action, which indicates infinite loop gain at steady-state, guarantees zero steady-state tracking error, and zero steady-state effect of constant output disturbances. In general, the excessive integral gain yields closed-loop instability. As state variables of multiple input-multiple output (MIMO) affect each other, oscillation is caused more critical than for single input-single output (SISO) systems [29]. This is the reason why regulating a multiple-output converter is complicated: there are interdependencies between the different outputs. To solve this kind of regulation problem, digital control provides many options. Sophisticated algorithms and accurate calculation can be implemented in microcontrollers or even field programmable gate arrays (FPGAs).

6.1. Pole Placement by Digital State Feedback

According to [30], the poles of a closed-loop system can be placed in any desired location by manipulating the state feedback gains. These techniques can be applied to a system of any order.

A multiple-output converter system controlled by a discrete-time control platform and having variable switching frequency is shown in Figure 16. A system which is regulated by a feedback vector - is depicted in Figure 17a. All of the state variables are sampled by ADCs, and these variables are weighted by the state-feedback gains to result in the plant input vector []. Next, these variables are transformed back to the analog domain using digital-to-analog converters (DACs). The ZOH equivalent of the plant is shown in Figure 17b, and it is described with (53). The equation for the feedback gain is:

Figure 17.

(a) A regulation system using digital state feedback; (b) A zero-order hold (ZOH) design model for digital state feedback.

The vector of feedback gains is calculated from (58), and the eigenvalues of the closed system set to their the desired values. The Matlab function “place” is used to calculate [31].

Choosing the Settling Interval

The speed of the controller is desired to be as fast as possible. The deadbeat control is one of the most popular control methods, as the steady-state error goes to zero in a finite number of switching periods [30]. This approach supplies a faster dynamic response than other control techniques.

If the poles of a continuous-time closed-loop system are moved far left in the s domain, the system response becomes faster. Using the fact that from the formula it follows that s = −∞ maps to z = 0, the z-domain poles should be moved to the origin of the z plane in order to make the system as fast as possible. This method is called deadbeat control. According to the Cayley-Hamilton Theorem, “deadbeat" means that the eigenvalues of the matrix are made zero when:

where d is the dimension of the system. Therefore,

It follows from (60) that the regulator moves the poles to zero in order to settle time steps. In theory, the settling time of the regulator therefore becomes seconds. If the feedback gain is made higher than described by (60), a damped oscillation is observed at half the sampling frequency [32]. Moreover, parameter mismatches of the model, model uncertainties, and noise from the measurement signals can cause a steady-state error and reduce the settling time. One of the disadvantages of deadbeat controllers is that measurements are needed to adjust the feedback gains, using trial and error [33]. The component values of the converters, such as inductance, capacitance, and resistance, will vary, e.g., because of temperature effects and aging.

This causes variation in and and thus in the pole locations. Another drawback of the deadbeat technique is that, because the processor forces the control signal to match the state variables to the reference in seconds, the control signal can saturate, and then the settling time becomes much longer than the expected seconds.

As the settling time of buck converters operated at CCM (the 1st and 2nd outputs) is higher than those at DCM (the 3rd, 4th and 5th outputs), the maximum settling time can be analyzed depending on these CCM outputs.

A buck converter with an appropriate deadbeat controller was simulated in LTspice IV. The parameters of the buck converter are: inductor 150 H, capacitor 40 F, load 10 , switching frequency 150 kHz, feedback gains 0.9 (for current) and 1.05 (for voltage). The duty cycle settles in 2 when the input voltage is changed from 23 V to 24 V. The maximum duty cycle settles at 0.9, and the duty cycle saturates, when the change of input voltage is increased substantially, such as from 19 V to 24 V. The settling time becomes 7 instead of 2.

The settling time was chosen as 10 to make the results robust against component variations and saturation effects. was chosen depending on the settling time, and Bessel polynomials were used for the controller prototype [30].

6.2. Error Cancelation

6.2.1. Settling Time Detector

In Section 6.1, the steady-state error problem is mentioned. In order to detect this steady-state error, the system under control first needs to settle. Accordingly, a settling time detector is used to detect whether the system is in the steady-state, as shown in Figure 16a.

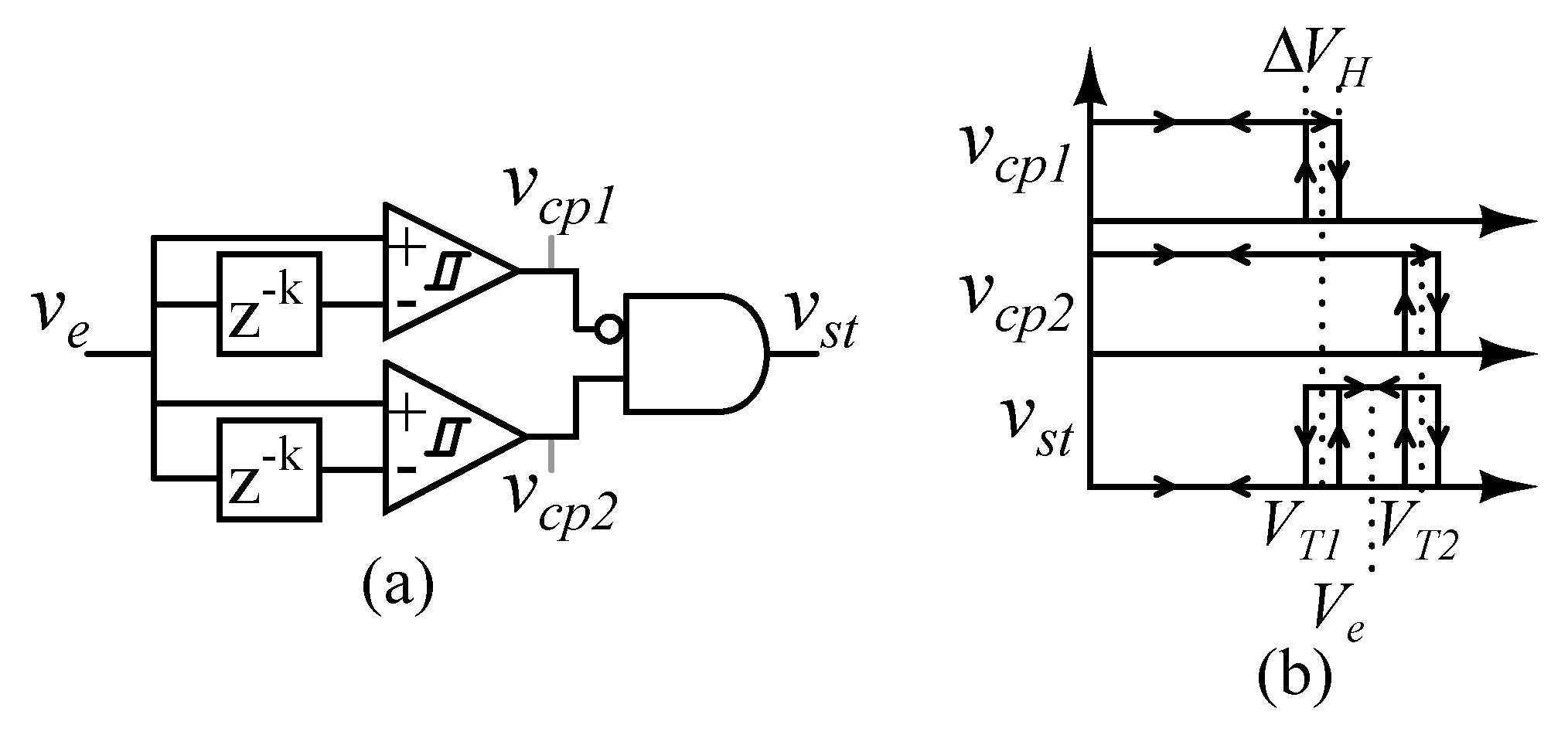

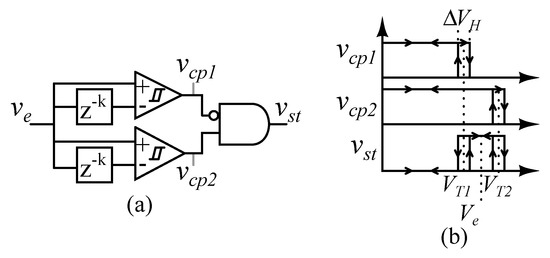

After the system reaches the steady-state, the change in the error is approximately zero. Following reference [34], an analog circuit is used to detect the settling time of a signal. To detect its change, a signal can be compared to a delayed copy of itself. The input signal and the delayed signal are therefore connected to two hysteresis comparators, as shown in Figure 18a.

Figure 18.

(a) The block diagram of the detection circuit; (b) Output signals of the comparators and “and” gate as function of the delayed input signal.

The delayed error signal can be smaller or greater than the error signal during the transient. Therefore, two hysteresis comparators are used to cover both cases, as shown in Figure 18b. The threshold voltages and are selected to be close to the expected error signal , which is zero, as shown in Figure 18b. The comparators are designed with hysteresis to avoid oscillations at the comparator outputs [34].

6.2.2. Cancelation Algorithm

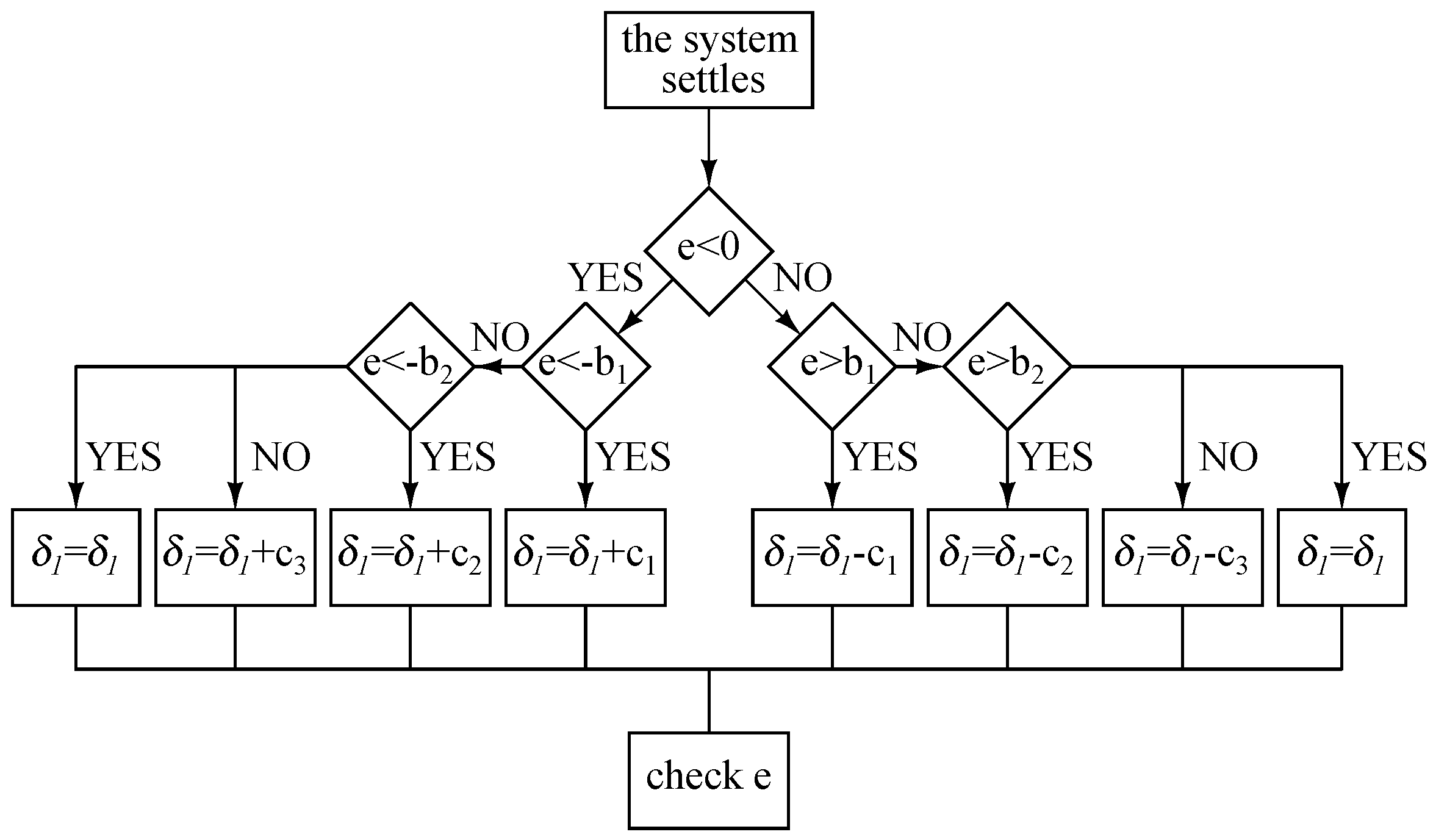

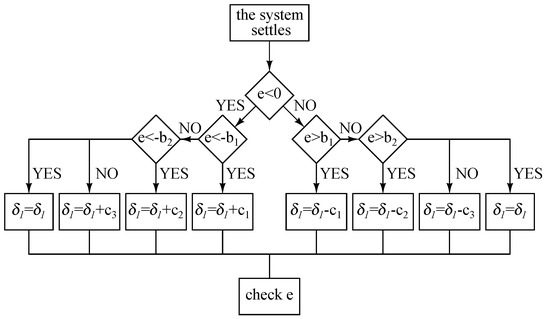

The system is modeled without considering the voltage drop of diodes, the losses caused by parasitic components or the uncertainties- and the nonlinear characteristics-of components. Therefore, the required control effort could be larger than the predicted one. In each period, errors are made in the control parameter calculations, and these ultimately cause a steady-state error. In order to compensate for this, an error cancelation scheme is introduced. This circuit becomes active when the controller error signal stops changing.

The required control parameters are calculated using the small-signal model. Because the calculation depends on ideal components, in practice cross-regulation issues cause offsets from the desired output values. This procedure is therefore repeated until such time that the output voltages are inside the requested tolerance band.

Figure 19 shows the steady-state error cancelation algorithm for the first output voltage . As is the control parameter of , is decreased or increased, depending on the amount of error. The same algorithm is issued for the other output voltages.

Figure 19.

Steady-state error(e) cancelation algorithm for the control parameter.

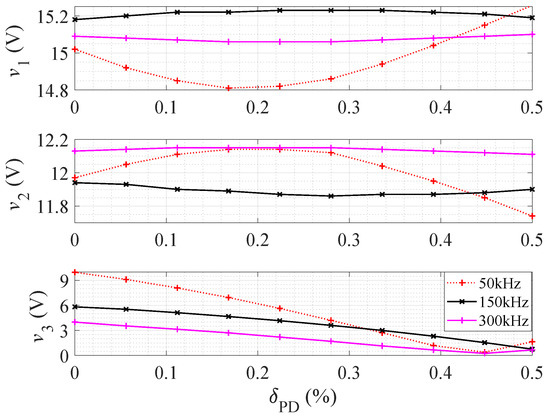

6.3. Experimental Results with the Close-Loop Five-Output Prototype

As proof of concept, a five-output closed-loop converter was built. The schematic of the converter is depicted in Figure 12a. The same power circuit was used as in the previous chapter. A C2000 Delfino F28379D microcontroller functioned as a controller to measure the state variables and to generate all gate signals. A PWM module of the microcontroller was used for each pulse of the burst mode PWM signal. In total, five PWM modules were used and these five signals were connected to an OR gate. Measurements circuits were used between the microcontroller and the output voltages and .

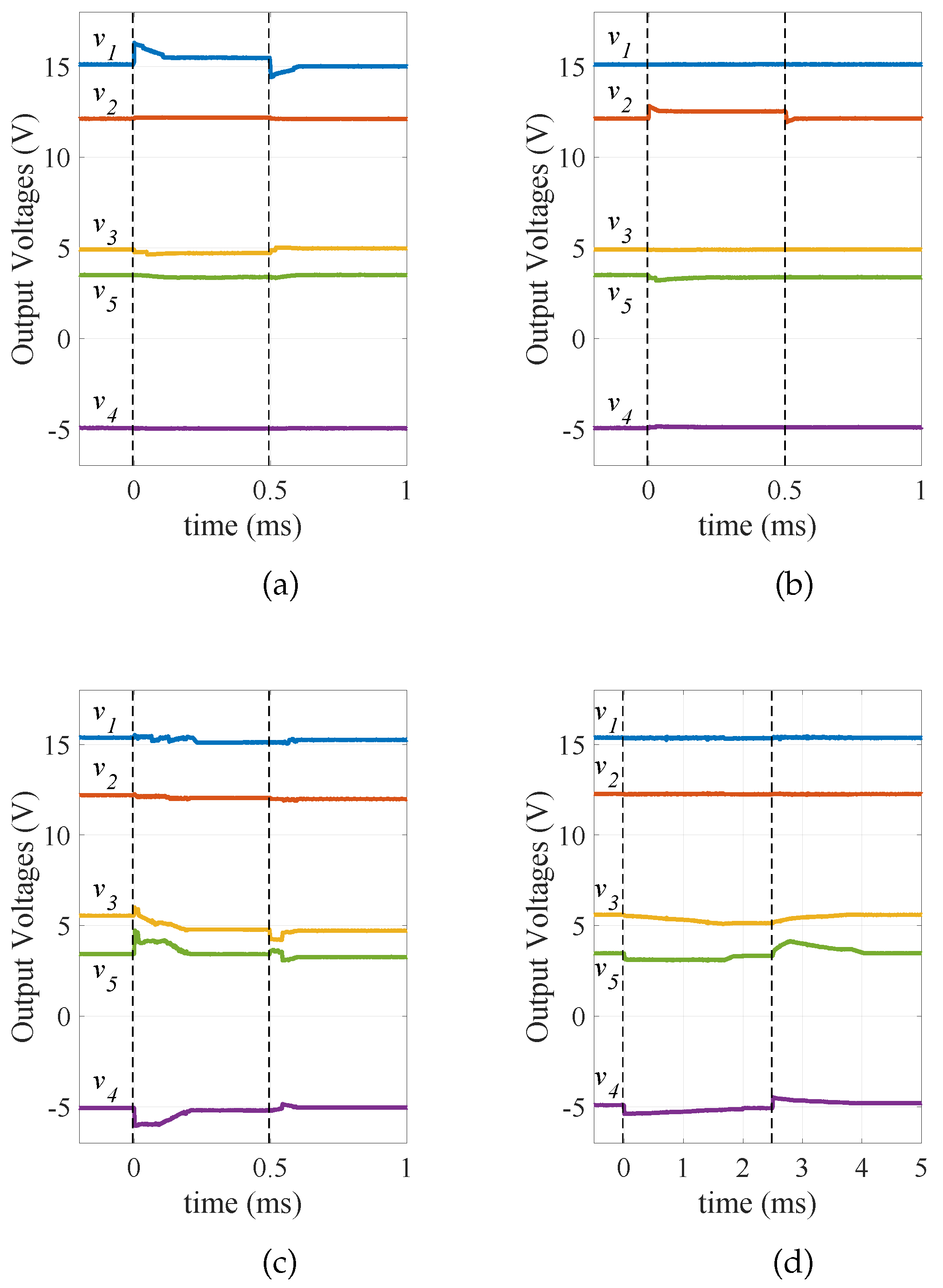

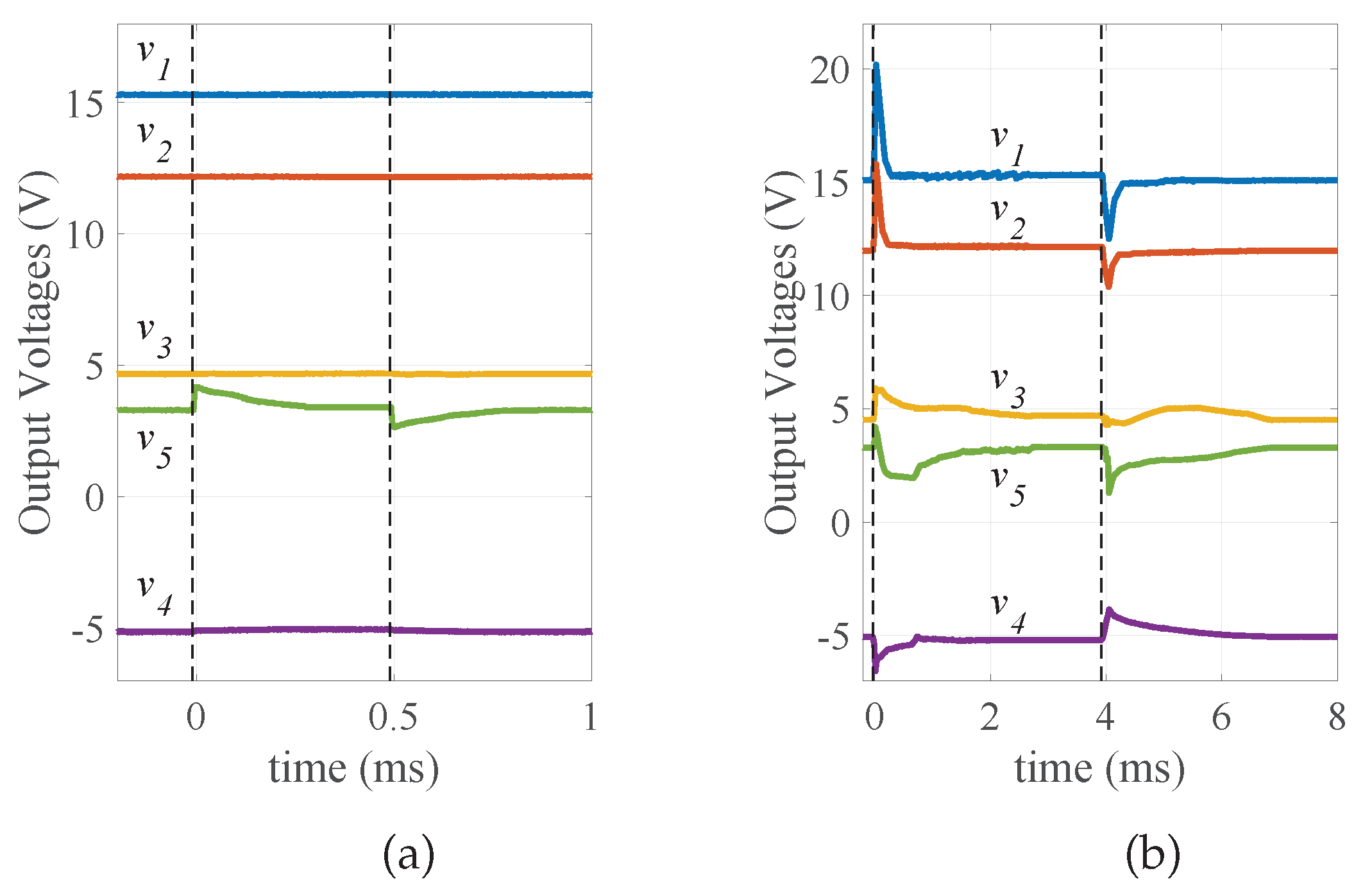

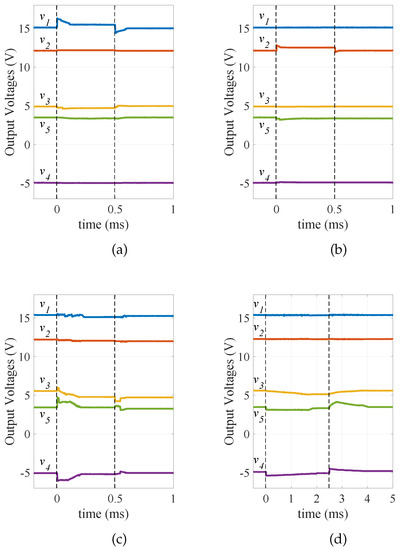

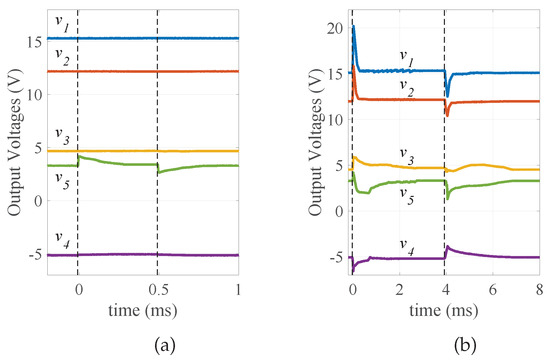

Experimental results for load and input voltage changes are shown in Figure 20 and Figure 21. Initially the five-output converter is in steady-state. Each output current is changed one at a time, keeping the the other output currents constant. Finally, the input voltage is changed.

Figure 20.

Experimental results from the closed-loop five-output prototype: Output voltage responses (a) when the first output current changes from 1.5 A to 0.75 A, and from 0.75 A to 1.5 A; (b) when the second output current changes from 1.5 A to 1 A, and from 1 A to 1.5 A; (c) when the third output current changes from 0.8 A to 0.5 A, and from 0.5 A to 0.8 A; (d) when the fourth output current changes from 0.6 A to 0.4 A, and from 0.4 A to 0.6 A.

Figure 21.

Experimental results from the closed-loop five-output prototype: Output voltage responses (a) when the fifth output current changes from 0.45 A to 0.3 A, and from 0.3 A to 0.45 A; (b) when the input voltage changes from 21 A to 30 V, and from 30 V to 21 V.

As shown in Figure 20a, at t = 0 s, the first output current is stepped down from 1.5 A to 0.75 A, and at t = 0.5 ms, is stepped up from 0.75 A to 1.5 A. The change at affects , because is also a control parameter of . The controller adjusts from 82.4 kHz to 66.3 kHz in order to keep at the desired voltage.

Likewise, at t = 0 s, the second output current is stepped down from 1.5 A to 1 A, and at t = 0.5 ms, is stepped back up to 1.5 A, as shown in Figure 20b. The controller reduces from 67.3% to 66.3% to keep at 12 V after the change at t = 0 s. Since is a control parameter of , increases from 3 to 5.

Furthermore, at t = 0 s, the third-output current is stepped down from 0.8 A to 0.5 A, and at t = 0.5 ms, is stepped back to 0.8 A, as shown in Figure 20c. As the main control parameter of is , the change of affects and . This happens because they are operated in DCM and are synchronized to . There is some hunting around of and , because of cross-regulation issues. However, the system eventually finds the steady-state operating points.

Next, at t = 0 s, the fourth output current is stepped down from 0.6 A to 0.4 A, and at t = 2.5 ms, is stepped back to 0.6 A as shown in Figure 20d. is changed from 3 to 5 after the change at t = 0 s. This change affects other outputs, and accordingly decreases from 85.5 kHz to 69.7 kHz. This is why the settling time needed for the system to recover from this change is longer than for the previous changes.

The fifth output current is stepped down from 0.45 A to 0.33 A at t = 0 s, and is stepped back to 0.45 A as seen in Figure 21a at t = 0.5 ms. The phase delay ratio is the only control parameter of . Therefore, changes of only are observed, as shown Figure 21a, when is increased from 33.5% to 42.0%.

Lastly, the input voltage is changed from 21 V to 30 V at t = 0 s, and from 30 V to 21 V at t = 4 ms. This change affects all the outputs, so regulation is apparent at every output in Figure 21b.

7. Conclusions

This paper introduces methods to obtain additional outputs without increasing the number of switches and coils. After proposing new multiple output converters, modeling and a digital controller for multiple output converters are presented.

First, multiple output dc-dc converters with reduced number of active and passive components are presented. Two PWM-PFM controlled two-output topologies, fly-buck and forward-buck, are shown. These two-output converters have only one switch and one coupled inductor to regulate two outputs independently. Then, two topologies controlled by PWM-PD are shown. These three-output converters need only two switches and two coupled inductors to regulate three-outputs independently. The two-output and three-output converters were implemented, and experimental results were obtained to validate the analysis and design procedure. The procedure to obtain PD at the different frequencies is discussed, and then a PWM-PFM-PD method is shown that exploits the full control potential of the two signals. Also, this signal pattern is applied to a five-output converter which has only two switches and two coupled inductors to control five-outputs. The design criteria for this five-output converter are presented, and the analysis is verified experimentally.

Next, a discrete converter model and corresponding control method are proposed for multiple output converters. First, the SSA technique is used to describe the multiple output converter. The application of SSA modeling to a multiple output converter, wherein state variables operate at different frequencies, is also explained.

To verify the regulation, a pole-placement feedback method is applied to the small signal model of the converter after this model is discretized by variable sampling time ZOH. A tuning method is presented to reduce the steady-state error of all the independently regulated outputs.

Finally, a prototype of the close loop system is presented. The controller is implemented with a F28379D microcontroller, and the measurement results of the five-output converter show that the analyses are valid.

Author Contributions

Conceptualization, M.T., M.A.M.H. and J.L.D.; Methodology, M.T.; Validation, M.T. and J.C.C.; Writing-original draft preparation, M.T.; Writing—review, M.A.M.H. and J.L.D.; Writing-final editing: M.T.; Funding acquisition, E.A.L.

Funding

This work is part of the research programme ASLS with project number 12759, which is partly financed by the Netherlands Organisation for Scientific Research (NWO). The authors also acknowledge the financial support of Philips Lighting (Signify, now).

Conflicts of Interest

The authors declare no conflict of interest.

References

- Maksimovic, D.; Erickson, R. Modeling of cross-regulation in multiple-output flyback converters. In Proceedings of the 1999 IEEE Applied Power Electronics Conference and Exposition (APEC), Dallas, TX, USA, 14–18 March 1999; pp. 1066–1072. [Google Scholar]

- Levin, G. A new secondary side post regulator (SSPR) PWM controller for multiple output power supplies. In Proceedings of the 1999 IEEE Applied Power Electronics Conference and Exposition (APEC), Dallas, TX, USA, 14–18 March 1999; pp. 736–742. [Google Scholar]

- Ferreres, A.; Carrasco, J.; Maset, E.; Ejea, J. Small-signal modeling of a controlled transformer parallel regulator as a multiple output converter high efficient post-regulator. IEEE Trans. Power Electron. 2004, 19, 183–191. [Google Scholar] [CrossRef]

- Sebastian, J.; Uceda, J. The double converter: A fully regulated two-output DC-DC converter. IEEE Trans. Power Electron. 1987, 2, 239–246. [Google Scholar] [CrossRef]

- Tacca, H. Single-switch two-output flyback-forward converter operation. IEEE Trans. Power Electron. 1998, 13, 903–911. [Google Scholar] [CrossRef]

- Sebastian, J.; Uceda, J.; Perez, M.; Rico, M.; Aldana, F. A very simple method to obtain one additional fully regulated output in zero-current-switched quasi resonant converters. In Proceedings of the 21st Annual IEEE Conference on Power Electronics Specialists, San Antonio, TX, USA, 11–14 June 1990; pp. 536–542. [Google Scholar]

- Barrado, A.; Olias, E.; Roldan, A.; Vazquez, R.; Pleite, J. Multiple output DC/DC converters based on PWM-pulse delay control (PWM-PD). In Proceedings of the 30th Annual IEEE Power Electronics Specialists Conference, Charleston, SC, USA, 1 July 1999; pp. 1141–1145. [Google Scholar]

- Barrado, A.; Olias, E.; Lazaro, A.; Pleite, J.; Vazquez, R. PWM-PD multiple output DC/DC converters: Operation and control-loop modeling. IEEE Trans. Power Electron. 2004, 19, 140–149. [Google Scholar] [CrossRef]

- Cho, S.-H.; Kim, C.-S.; Han, S.-K. High-efficiency and low-cost tightly regulated dual-output LLC resonant converter. IEEE Trans. Ind. Electron. 2012, 59, 2982–2991. [Google Scholar] [CrossRef]

- Liu, C.; Gu, B.; Lai, J.-S.; Wang, M.; Ji, Y.; Cai, G.; Zhao, Z.; Chen, C.-L.; Zheng, C.; Sun, P. High-efficiency hybrid full bridge-half bridge converter with shared ZVS lagging leg and dual outputs in series. IEEE Trans. Power Electron. 2013, 28, 849–861. [Google Scholar] [CrossRef]

- Seong, H.; Kim, D.; Cho, G.-H. A new ZVS DC/DC converter with fully regulated dual outputs. In Proceedings of the IEEE Power Electronics Specialist Conference, Seattle, WA, USA, 20–24 June 1993; pp. 351–356. [Google Scholar]

- Zhang, Y.; Xu, D. Design and implementation of an accurately regulated multiple output zvs dc-dc converter. IEEE Trans. Power Electron. 2007, 22, 1731–1742. [Google Scholar] [CrossRef]

- Hyeon, B.-C.; Cho, B.-H. A tightly regulated triple output asymmetrical half bridge flyback converter. J. Power Electron. 2010, 10, 14–20. [Google Scholar] [CrossRef]

- Turhan, M.; Hendrix, M.A.M.; Duarte, J.L.; Castellanos, J.C.; Delos, J. A tightly regulated PWM-PFM-PD multiple output DC-DC converter. In Proceedings of the 2016 IEEE 8th International Power Electronics and Motion Control Conference (IPEMC-ECCE Asia) Asia, Hefei, China, 22–26 May 2016; pp. 616–620. [Google Scholar]

- Designing Low-Cost, Multiple Output DC-DC Converters Using 1:1 Coupled Inductors with Buck Regulators. Available online: https://www.we-online.com/web/en/electronic_components/produkte_pb/application_notes/multiple_output_converters.php (accessed on 17 September 2019).

- An-2292 Designing an Isolated Buck (Flybuck) Converter. Available online: http://www.ti.com/lit/an/snva674b/snva674b.pdf (accessed on 17 September 2019).

- Karlsson, M.; Persson, O. Isolated Fly-Buck Converter, Switched Mode Power Supply, and Method of Measuring a Voltage on a Secondary Side of an Isolated Fly-Buck Converter. International Patent 137852, 17 September 2015. [Google Scholar]

- Fang, X.; Meng, Y. Isolated bias power supply for IGBT gate drives using the fly-buck converter. In Proceedings of the 2015 IEEE Applied Power Electronics Conference and Exposition (APEC), Charlotte, NC, USA, 15–19 March 2015; pp. 2373–2379. [Google Scholar]

- Wang, W.; Lu, D.; Chai, Q.; Lin, Q.; Cai, F. Analysis of fly-buck converter with emphasis on its cross-regulation. IET Power Electron. 2017, 10, 292–301. [Google Scholar] [CrossRef]

- Raets, H.; Albach, M. High Leakage Inductance Transformer. Patent 6100781, 8 August 2000. [Google Scholar]

- De Leon, F.; Purushothaman, S.; Qaseer, L. Leakage inductance design of toroidal transformers by sector winding. IEEE Trans. Power Electron. 2014, 29, 473–480. [Google Scholar] [CrossRef]

- Chen, G.; Deng, Y.; Dong, J.; Hu, Y.; Jiang, L.; He, X. Integrated multiple-output synchronous buck converter for electric vehicle power supply. IEEE Trans. Vehic. Technol. 2017, 66, 5752–5761. [Google Scholar] [CrossRef]

- Isaac, D.; Park, J.H. Independently-controlled single-PWM multiple-output narrow-band resonant converter. IEEE Trans. Power Electron. 2017, 33, 5042–5061. [Google Scholar]

- Meng, T.; Ben, H.; Song, Y.; Li, C. Analysis and design of an input-series two-transistor forward converter for high-input voltage multiple-output applications. IEEE Trans. Ind. Electron. 2018, 65, 270–279. [Google Scholar] [CrossRef]

- Wai, R.J.; Jheng, K.H. High-efficiency single-input multiple-output dc-dc Converter. IEEE Trans. Power Electron. 2013, 28, 886–898. [Google Scholar] [CrossRef]

- Krein, P.T.; Bentsman, J.; Bass, R.M.; Lesieutre, B.L. On the use of averaging for the analysis of power electronic systems. IEEE Trans. Power Electron. 1990, 5, 182–190. [Google Scholar] [CrossRef]

- Sun, J.; Mitchell, D.M.; Greuel, M.F.; Krein, P.T.; Bass, R.M. Averaged modeling of PWM converters operating in discontinuous conduction mode. IEEE Trans. Power Electron. 2001, 16, 482–492. [Google Scholar]

- Davoudi, A.; Jatskevich, J.; Rybel, T.D. Numerical state-space average-value modeling of PWM DC-DC converters operating in DCM and CCM. IEEE Trans. Power Electron. 2006, 21, 1003–1012. [Google Scholar] [CrossRef]

- Yeh, S.S.; Hsu, P.L. Theory and applications of the robust cross-coupled control design. J. Dyn. Syst. Meas. Control 1997, 1, 791–795. [Google Scholar] [CrossRef]

- Vaccaro, R.J. Digital Control: A State-Space Approach; McGraw-Hill College: New York, NY, USA, 1995. [Google Scholar]

- Schellekens, J.M. A Class of Robust Switched-Mode Power Amplifiers with Highly Linear Transfer Characteristics. Ph.D. Dissertation, Eindhoven University of Technology, Eindhoven, The Netherlands, 2014. [Google Scholar]

- Saggini, S.; Stefanutti, W.; Tedeschi, E.; Mattavelli, P. Digital deadbeat control tuning for DC-DC converters using error correlation. IEEE Trans. Power Electron. 2007, 22, 1566–1570. [Google Scholar] [CrossRef]

- Emadi, A.; Khaligh, A.; Nie, Z.; Lee, Y.J. Integrated Power Electronic Converters and Digital Control; CRC Press: Boca Raton, FL, USA, 2009. [Google Scholar]

- Craciun, A.V.; Nicolae, G. Settling Time Instant Detector for Steady State Transient Signals. Available online: http://etc.unitbv.ro/~craciun/SetTimeDet_intro.html#targetText=Settling (accessed on 17 September 2019).

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).